# MEASUREMENT AND MODELING OF 1/f NOISE IN MOSFET DEVICES WITH HIGH-κ MATERIAL AS THE GATE DIELECTRIC

by

# TANVIR HASAN MORSHED

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT ARLINGTON

December 2007

#### ACKNOWLEDGMENTS

All praises to Allah, the most merciful. Peace be upon Prophet Muhammad.

I would like to express my deepest respect for my advisor Professor Zeynep Çelik-Butler for her support and directions in this research and in times of need. It has been a remarkable experience to work with her, to learn and to flourish as a researcher. I am grateful to my advisor for her indispensable contributions in this research work.

I like to thank all my dissertation committee members; Dr. Donald Butler, Dr. Jung-Chih Chiao, Dr. Daniel Engels and Dr. Wiley Kirk for their precious time, advice and suggestions. I am especially thankful to Dr. Engels for his every effort to make my thesis a better written document as well as his insightful remarks. I appreciate Dr. Kirk for his discerning remarks on the experimental side of this work. I also like to thank Dr. Keith Green, Dr. Luigi Colombo and Dr. Ajit Shanware from Texas Instruments, for the devices used in this work and their valuable comments and suggestions. I like to express my gratitude to Semiconductor Research Corporation for the financial support.

I am grateful to Dr. Raymond Shoults for his kind favors in academic matters.

I am indebted to Dr. Aamer Mahmood and Dr. Mukti Rana for their support and encouragement. I like to thank all my friends, co-researchers and stuffs at NanoFab, especially Mazhar, Min, Siva, Shahriar, Shakhauat, Murali, Erkin, Vijay, Suraj and others. I thankfully acknowledge the excellent work environment we enjoy at the NanoFab.

I would like to especially mention the unconditional love and support from my wife Romana Zerin through our very difficult times, and the continuous encouragement from my parents Lt. Col. H. M. A. Gaffar (BU) and Hosne Ara Gaffar, my brother Tanjeer and my sisters Dr. Farzana and Farhana. I remember the blessings from my late grand father Abdul Karim Molla. I gratefully remember the cordial love from all our family members and friends in Dhaka and Toronto. This work was possible for me all

May Allah bless you all.

because of that.

November 20, 2007

## **ABSTRACT**

# MEASUREMENT AND MODELING OF 1/f NOISE IN MOSFET DEVICES WITH HIGH- $\kappa$ MATERIAL AS THE GATE DIELECTRIC

Publication No. \_\_\_\_\_

Tanvir Hasan Morshed, PhD.

The University of Texas at Arlington, 2007

Supervising Professor: Dr. Zeynep Çelik-Butler

A new 1/f noise model has been developed for MOSFET devices with high-κ gate stack. To investigate the impacts of nitridation, MOSFETs with nitrided high-κ dielectric was used. These devices were provided by Texas Instruments, having four different interfacial layer thicknesses with a stack composition of SiON/HfSiON.

The dominant mechanism affecting the noise behavior of these devices was experimentally determined to be correlated number and mobility fluctuation. The impact of remote phonon scattering was investigated in the temperature range of 172K

iv

to 300K. It has been observed that the mobility characteristics of these devices were significantly affected by remote phonon scattering. However, the impact of remote phonon scattering was not observed on the flicker noise characteristics. The new model was developed in the frame work of the original Unified Model incorporating two distinct features that distinguish high- $\kappa$  gate stacks from SiO<sub>2</sub>. The new model considers energy and spatial dependence of trap distribution in the dielectric, thus generates a more realistic trap profile. Furthermore, it incorporates the multi layered structure of the gate stack by considering tunneling of carriers through a double step cascaded barrier. The newly developed model is accordingly called MSUN (Multi Stack Unified Noise) Model, named after the original Unified Model.

MSUN Model has been successfully verified with data on MOSFETs having four different interfacial layer thicknesses, in the temperature range of 172K to 300K. The model predictions show very good agreement with data in the bias range of moderate to strong inversion. No specific impact due to nitridation was observed on these devices. The model has been successfully transformed into a compact form which is compatible with leading device simulation package used in the industry.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                                    | ii   |

|-------------------------------------------------------------------------------------|------|

| ABSTRACT                                                                            | iv   |

| LIST OF ILLUSTRATIONS                                                               | X    |

| LIST OF TABLES                                                                      | XV   |

| Chapter                                                                             | Page |

| 1. INTRODUCTION                                                                     | 1    |

| 1.1 Introduction                                                                    | 1    |

| 1.2 Scaling down of MOSFET devices and incorporation of high-κ materials            | 2    |

| 1.2.1 Role of SiO <sub>2</sub> in device scaling                                    | 3    |

| 1.2.2 Principle of using high-k materials as the alternate gate dielectric          | 4    |

| 1.2.3 Selection of suitable high-k materials                                        | 6    |

| 1.2.4 Effect of N <sub>2</sub> incorporation                                        | 8    |

| 1.2.5 Effects of incorporation of high-k materials                                  | 9    |

| 1.3 1/f Noise modeling_                                                             | 11   |

| 1.3.1 Flicker noise prediction with existing models                                 | 12   |

| 1.3.2 Application of Unified Model in noise prediction of high-k gate-stack MOSFETs | 13   |

|    | 1.3.3 Possible origins of the observed discrepancies      | 13 |

|----|-----------------------------------------------------------|----|

|    | 1.3.4 Theoretical basis of the new model                  | 15 |

|    | 1.3.5 Modifications in MSUN Model and implementation      | 15 |

|    | 1.3.6 MSUN Model performance verification                 | 16 |

|    | 1.4 Summary                                               | 17 |

| 2. | NOISE MEASUREMENTS                                        | 22 |

|    | 2.1 Introduction                                          | 22 |

|    | 2.1.1 Flicker noise measurement                           | 22 |

|    | 2.1.2 Variable temperature measurement                    | 23 |

|    | 2.2 The experimental setup                                | 24 |

|    | 2.3 Device specifications                                 | 26 |

|    | 2.4 Variable temperature measurement procedure            | 26 |

|    | 2.4.1 DC measurement procedure                            | 30 |

|    | 2.4.2 CV measurement procedure                            | 35 |

|    | 2.4.3 1/f noise measurement procedure                     | 42 |

|    | 2.5 Summary                                               | 47 |

| 3. | DEVELOPMENT OF MSUN MODEL                                 | 48 |

|    | 3.1 Introduction                                          | 48 |

|    | 3.2 The flicker noise theories for MOSFET devices         | 48 |

|    | 3.2.1 Carrier number and correlated mobility fluctuations | 48 |

|    | 3.2.2 Hooge mobility fluctuations                         | 50 |

|    | 3.3 Theoretical and experimental basis of the new model   | 52 |

|    | 3.4 Development of the MSUN Model                               | 53 |

|----|-----------------------------------------------------------------|----|

|    | 3.4.1 The Unified Model                                         | 53 |

|    | 3.4.2 Distinct features of the high-κ gate stack                | 57 |

|    | 3.4.2.1 The trap distribution function                          | 57 |

|    | 3.4.2.2 Multi layered gate stack                                | 60 |

|    | 3.5 Summary                                                     | 64 |

| 4. | RESULTS AND DISCUSSIONS                                         | 66 |

|    | 4.1 Introduction                                                | 66 |

|    | 4.2 Experiments, results and discussions                        | 67 |

|    | 4.2.1 The effect of remote phonon scattering                    | 67 |

|    | 4.2.1.1 The effect of phonon scattering on mobility degradation | 67 |

|    | 4.2.1.2 The effect of phonon scattering on 1/f noise            | 71 |

|    | 4.2.2 The dominant noise mechanism                              | 73 |

|    | 4.2.3 The model parameters                                      | 75 |

|    | 4.2.3.1 The effective number of parameters                      | 76 |

|    | 4.2.3.2 Extraction of model parameters                          | 78 |

|    | 4.2.3.3 Extracted model parameters                              | 81 |

|    | 4.2.4 Compact form of MSUN Model                                | 85 |

|    | 4.2.4.1 Compact form for the BSIM Model                         | 85 |

|    | 4.2.4.2 Compact form for the PSP Model                          | 87 |

|    | 4.2.5 Compact form of the integrals into the dielectric         | 89 |

|    | 4.3 Summary                                                     | 91 |

| 5. CONCLUSIONS                                      | 93  |

|-----------------------------------------------------|-----|

| Appendix                                            |     |

| A. MATHCAD IMPLEMENTATION OF MSUN MODEL             | 100 |

| B. DERIVATION OF THE COMPACT FORM FOR THE INTEGRALS | 111 |

| REFERENCES                                          | 142 |

| BIOGRAPHICAL INFORMATION                            |     |

# LIST OF ILLUSTRATIONS

| Figure |                                                                                                                                                                                                                                                                                         | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

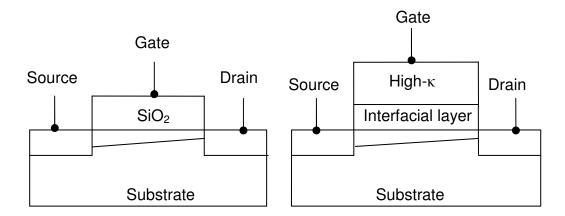

| 1.1    | MOSFET devices with SiO <sub>2</sub> and high-k stack as the gate dielectric                                                                                                                                                                                                            | 5    |

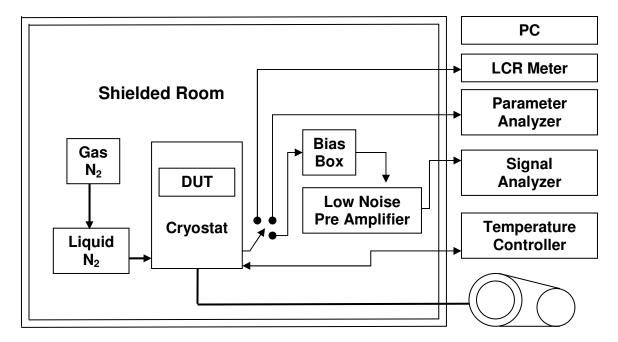

| 2.1    | The schematic diagram of the variable temperature measurement setup                                                                                                                                                                                                                     | 25   |

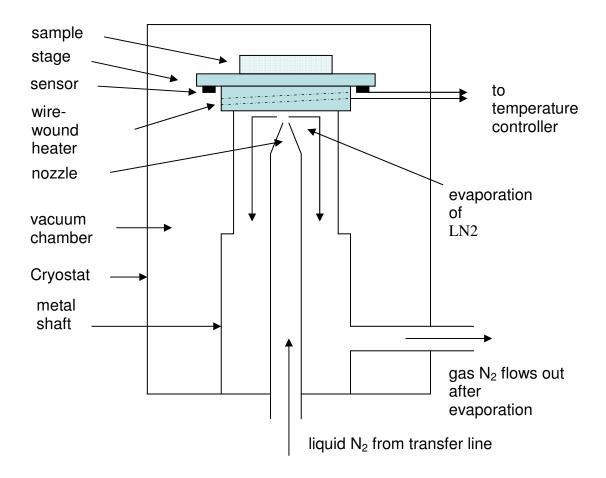

| 2.2    | The cryogenic temperature setup comprises of two isolated chamber. The vacuum chamber where the sample is mounted maintains thermal isolation between the sample and the environment. In the evaporation chamber LN2 is evaporated to lower the temperature of the stage and the sample | 29   |

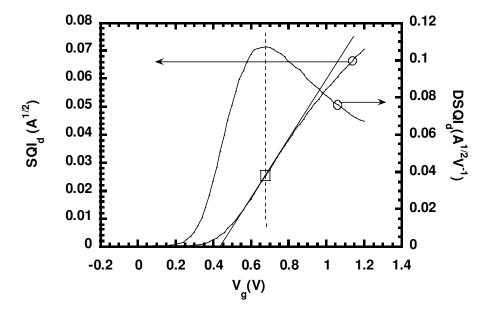

| 2.3    | Extraction of threshold voltage $V_t(V)$ is shown here. A tangent is drawn on the curve $SQI_d$ at $V_g$ corresponding to the maxima of $DSQI_d$ (marked by the square on the vertical line). The tangent intersects the $V_g$ axis at the threshold voltage $V_t$                      | 31   |

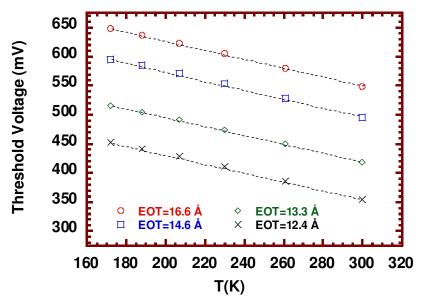

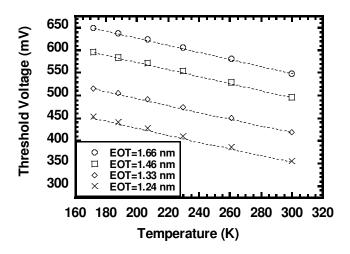

| 2.4    | The extracted threshold voltage $V_t$ is shown for four different interfacial layer thicknesses. A linear shift was observed in the threshold voltages irrespective of the interfacial layer thickness. The temperature dependence was observed to be identical for all devices         | 32   |

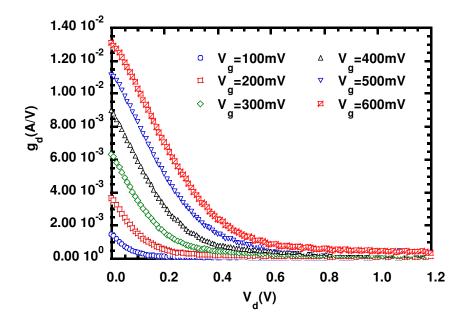

| 2.5    | Channel conductance $g_d$ as a function of drain voltage $V_d$ for different values of gate voltage ( $V_g = 100 \text{mV}$ to $V_g = 600 \text{mV}$ )                                                                                                                                  | 32   |

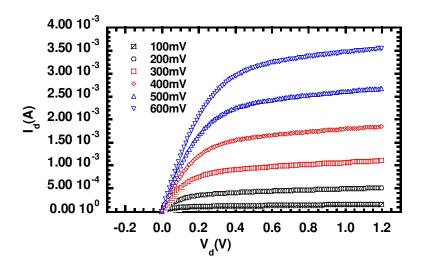

| 2.6    | Channel current $I_d$ as a function of $V_d$ at different gate voltages in the range of $V_g = 100 \text{mV}$ to $V_g = 600 \text{mV}$ .                                                                                                                                                | 33   |

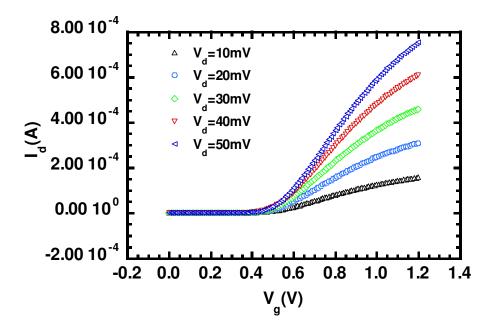

| 2.7    | Drain current $I_d$ as function of gate voltage $V_g$ at different values of drain voltage ( $V_d = 10 \text{mV}$ to $V_d = 50 \text{mV}$ )                                                                                                                                             | 33   |

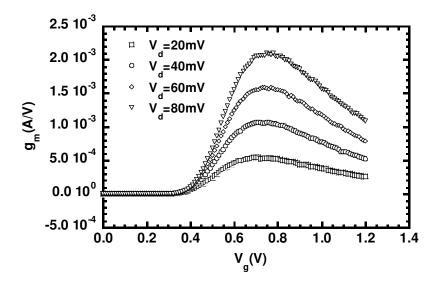

| 2.8  | The trans-conductance $g_m$ as a function of gate voltage $V_g$ at                                                                                                                                                                                                                                                                                                         |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | different drain voltages $V_d$                                                                                                                                                                                                                                                                                                                                             | 34 |

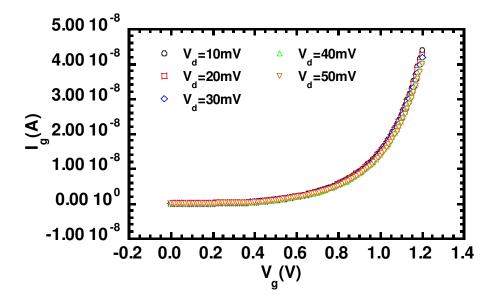

| 2.9  | Gate leakage current $I_g$ as a function of gate voltage $V_g$ at different                                                                                                                                                                                                                                                                                                |    |

|      | drain voltages ( $V_d = 10 \text{mV}$ to $V_d = 50 \text{mV}$ ). With the increase of $V_g$ , the gate leakage current increased exponentially                                                                                                                                                                                                                             | 34 |

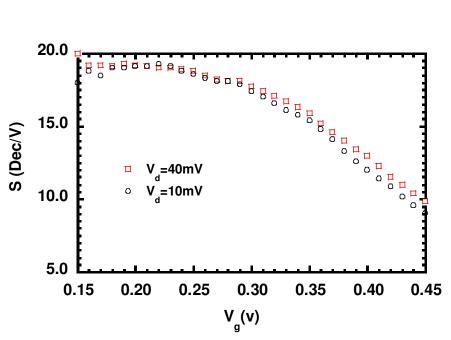

| 2.10 | Sub-threshold swing $S$ (Dec/V) shown as a function of gate voltage at drain voltages of $V_d = 10 \text{mV}$ and $V_d = 40 \text{mV}$                                                                                                                                                                                                                                     | 35 |

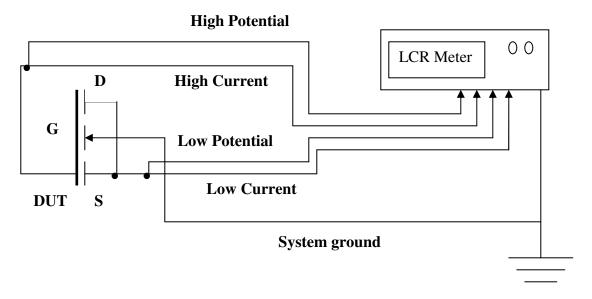

| 2.11 | The schematic diagram of Split CV measurement                                                                                                                                                                                                                                                                                                                              | 37 |

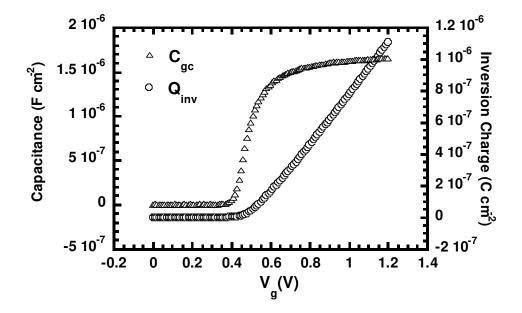

| 2.12 | The channel capacitance $C_{gc}$ is shown after correction. The calculated                                                                                                                                                                                                                                                                                                 |    |

|      | channel inversion charge $Q_{inv}$ is also shown here                                                                                                                                                                                                                                                                                                                      | 37 |

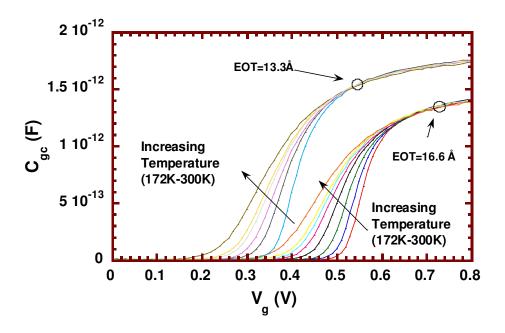

| 2.13 | The channel capacitance $C_{gc}$ is shown for two different interfacial layer thicknesses, with temperature as a parameter. At lower values of $V_g (\leq V_t)$ significant impact of temperature was observed. As temperature decreases the $C_{gc}$ increases more rapidly with increase                                                                                 |    |

|      | in $V_g$ . At higher $V_g$ (> $V_t$ ), $C_{gc}$ does not show dependence on temperature                                                                                                                                                                                                                                                                                    | 38 |

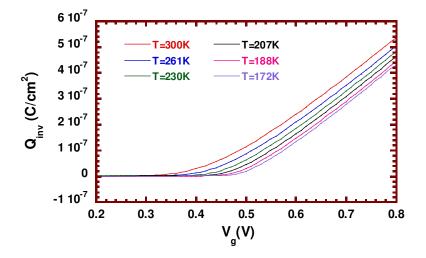

| 2.14 | The channel inversion charge $Q_{inv}$ is shown as a function of $V_g$ at different temperatures. The effect of threshold voltage shift is reflected in higher inversion charge and smoother transition in the higher temperature region                                                                                                                                   |    |

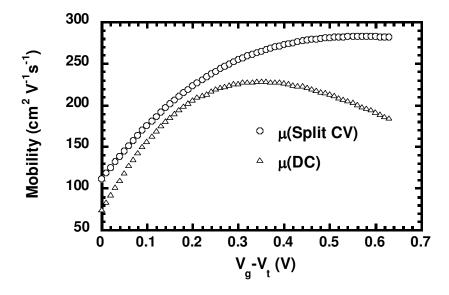

| 2.15 | Comparison of carrier mobility calculated by DC measurements and split CV measurements. At lower gate over-drive voltage $(V_g - V_t)$ the mobility values differ because of erroneous inversion charge estimation by DC measurements. At higher gate over-drive voltages, DC measurements yield lower mobility values due to underestimation of the gate leakage current. | 39 |

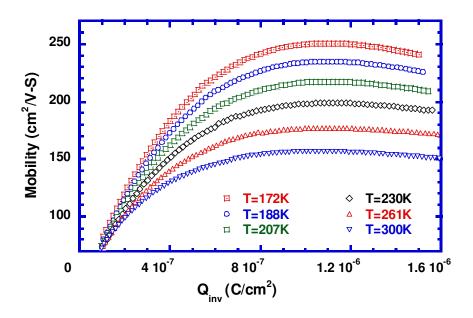

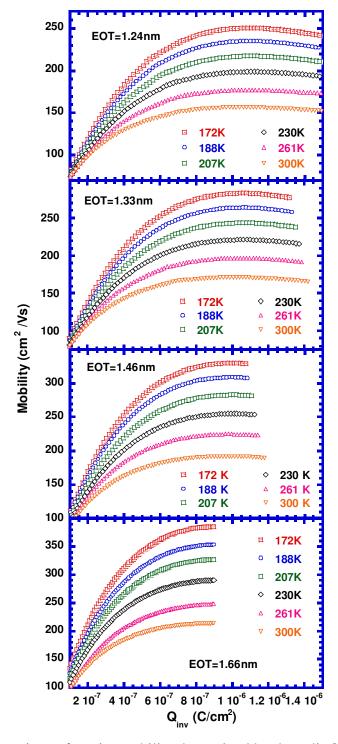

| 2.16 | Comparison of carrier mobility calculated by the split CV measurements at different temperatures as a function of $Q_{inv}$ . With the increase in temperature carrier mobility was observed to decrease                                                                                                                                                                   | 40 |

| 2.17 | Comparison of carrier mobility determined by the split CV measurements for different interfacial layer thicknesses. An inverse dependence of mobility on interfacial layer thickness was observed | . 41 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.18 | The MOSFET bias arrangement for low frequency noise measurements                                                                                                                                  | . 43 |

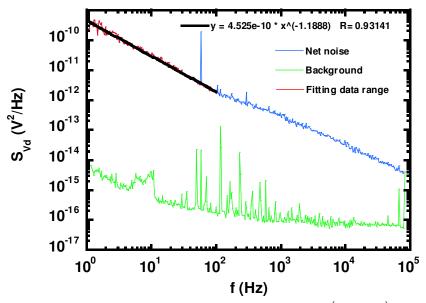

| 2.19 | Typical 1/f voltage noise spectral density $S_{V_d}(V^2Hz^{-1})$ is shown with the background. The data range (highlighted) used for                                                              |      |

|      | fitting and the fit equation are also shown. The 60Hz noise peak has been removed from the fitting data                                                                                           | . 45 |

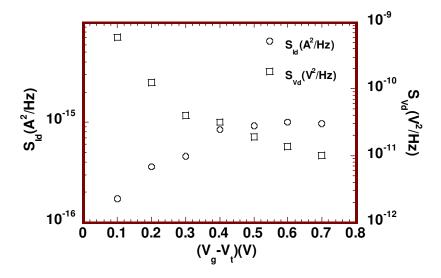

| 2.20 | The current noise spectral density $S_{I_d}$ is shown with the                                                                                                                                    |      |

|      | corresponding voltage noise spectral density $S_{V_d}$ . The $S_{V_d}$ at 1Hz                                                                                                                     |      |

|      | intercept point and $g_d$ have been used for the calculation of $S_{I_d}$                                                                                                                         | . 45 |

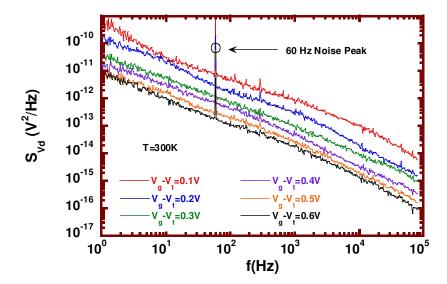

| 2.21 | The voltage noise spectral density $S_{V_d}$ is shown as a function of                                                                                                                            |      |

|      | frequency at different gate over-drive voltages. Increasing the gate over-drive voltage decreased flicker noise                                                                                   | . 46 |

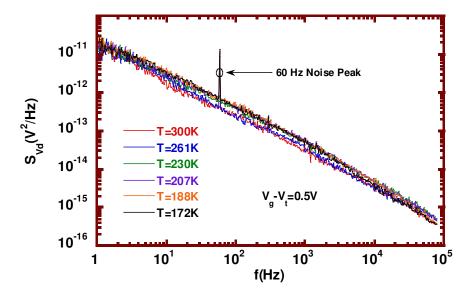

| 2.22 | The voltage noise spectral density $S_{V_d}$ is shown as a function of                                                                                                                            |      |

|      | frequency at a fixed gate over-drive voltage at different temperatures. $S_{V_d}$ does not show any noticeable dependence on temperature in the                                                   |      |

|      | experimental range of 172K to 300K                                                                                                                                                                | . 46 |

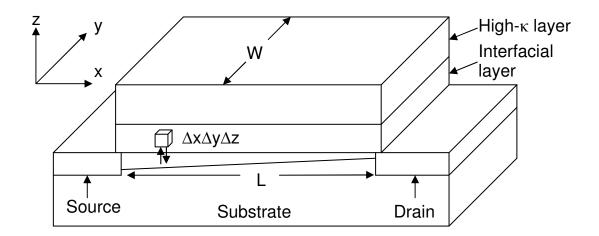

| 3.1  | The schematic diagram of a MOSFET with high-k material as the gate stack with a channel length of L and width of W                                                                                | . 54 |

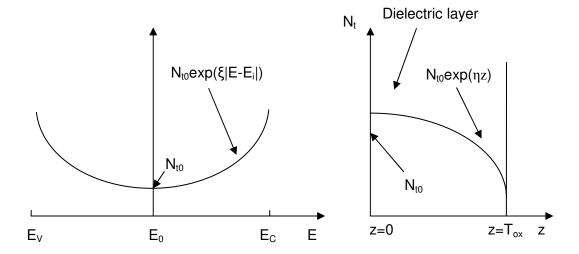

| 3.2  | The variation in the trap density due to energy (with positive $\xi$ ) and spatial distribution of traps ( $\eta$ is assumed negative                                                             | . 58 |

| 3.3  | Tunneling of carriers through a double step cascaded energy barrier assumed to represent the stacked dielectric structure in                                                                      |      |

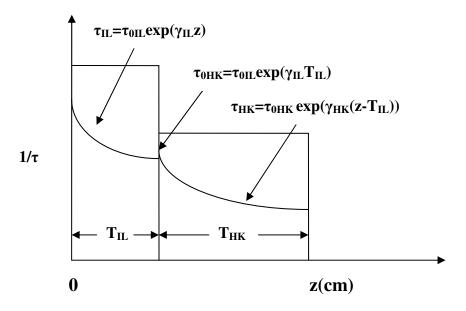

|      | the MSUN model                                                                                                                                                                                    | . 61 |

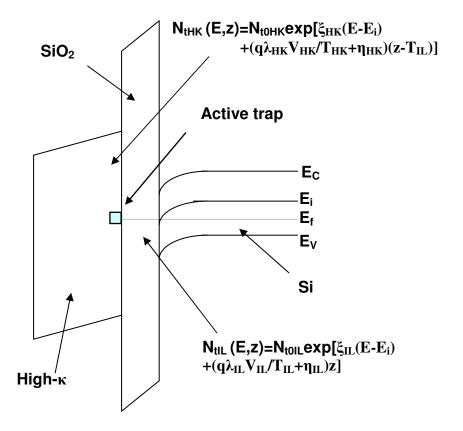

| 3.4  | The exponential dependence of the trap distribution on the carrier                                                                                                                                |      |

|      | energy and tunneling distance from the interface is shown here for<br>the interfacial layer and the high-k layer                                                                                  | . 62 |

| 4.1  | Threshold voltage shift with temperature for devices with                                                                                                                                         |      |

|      | different IL thickness                                                                                                                                                                            | . 67 |

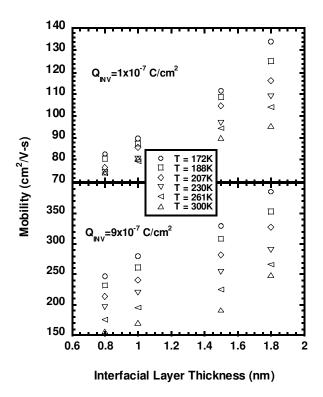

| 4.2  | Comparison of mobility as a function of IL thickness with temperature as a parameter. The mobility values are calculated at an inversion charge concentration of $1x10^{-7}$ C/cm <sup>2</sup> and $9x10^{-7}$ C/cm <sup>2</sup>                                                                                                |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

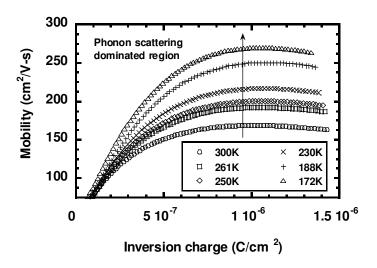

| 4.3  | Mobility values are shown as a function of inversion charge. $Q_{inv}$ $\sim 9 \times 10^{-7}$ C/cm <sup>2</sup> , LxW= $10 \times 10 \mu m^2$ and EOT= $1.33 nm$                                                                                                                                                               |

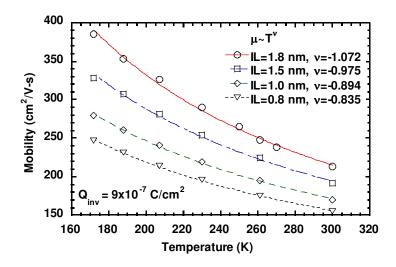

| 4.4  | Dependence of mobility on temperature, in the phonon scattering dominated $Q_{inv}$ region. As observed, $\mu \alpha T^{-\nu}$ with $\nu \sim 1.072$ -0.834                                                                                                                                                                     |

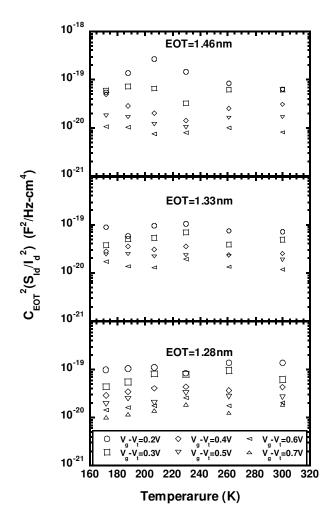

| 4.5  | Comparison of normalized current noise spectral density $ \left(C_{EOT}^2 \left(\frac{S_{I_d}}{I_d^2}\right) \left(F^2 H z^{-1} cm^{-4}\right)\right) \text{ at 1 Hz as a function of temperature for devices with different IL thicknesses}$                                                                                   |

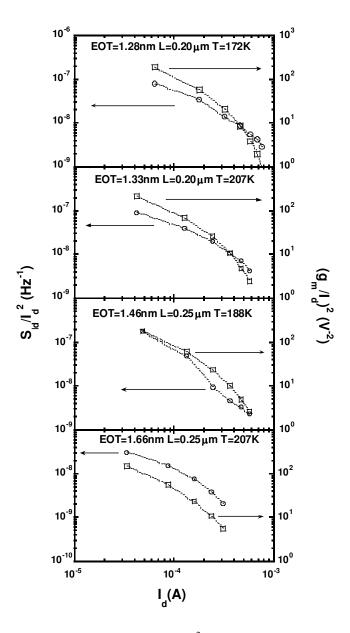

| 4.6  | $\frac{S_{I_d}}{I_d^2}$ shows dependence on $\left(\frac{g_m}{I_d}\right)^2$ at all temperatures for devices with all four different IL thicknesses at frequency of 1 Hz                                                                                                                                                        |

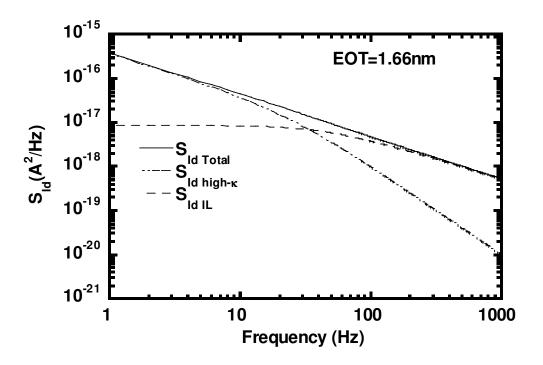

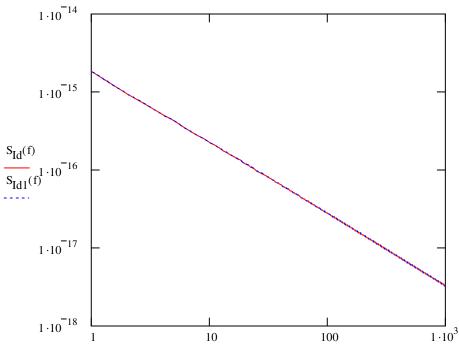

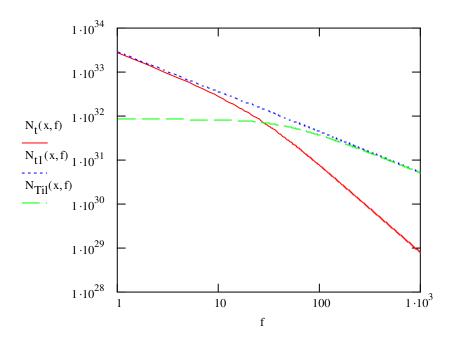

| 4.7  | Contributions from the interfacial layer and the high- $\kappa$ layer in the total $S_{I_d}$ (A <sup>2</sup> /Hz) for devices with $T_{IL}$ =1.8nm                                                                                                                                                                              |

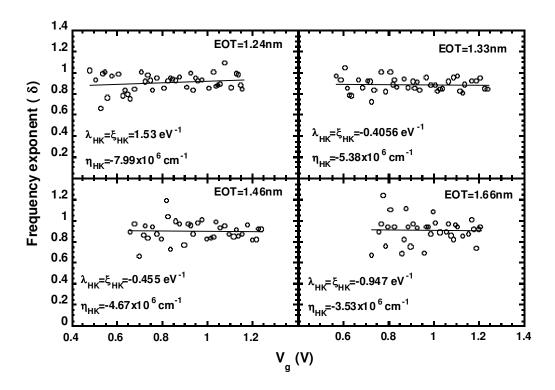

| 4.8  | The experimental values of frequency exponent $\delta$ is plotted as a function of gate voltage for T = 172K - 300K. Linear fitting to the data is obtained for all four wafers. Using these fitting coefficients $\lambda_{HK}$ , $\xi_{HK}$ and $\eta_{HK}$ parameters were calculated                                        |

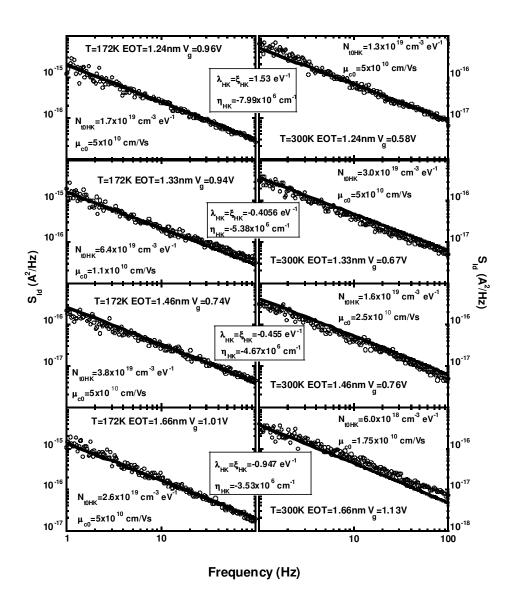

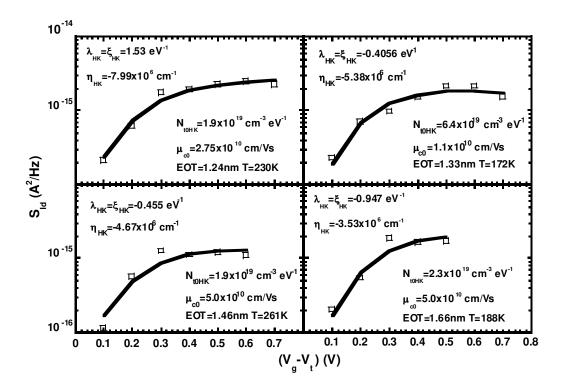

| 4.9  | Comparison of current noise spectrum $S_{I_d}$ calculated with MSUN Model to that obtained by experiment, shown at T=172K and T=300K. LxW=0.20x10 $\mu$ m <sup>2</sup> . $\lambda_{HK}$ , $\xi_{HK}$ and $\eta_{HK}$ values are the same for all temperatures for individual devices and correspond to the high- $\kappa$ layer |

| 4.10 | The current noise spectral density $S_{I_d}$ (A <sup>2</sup> /Hz) calculated at 1 Hz using MSUN Model is compared to experimental data. EOT = 1.28nm, 1.33nm, 1.46nm and 1.66nm from weak to strong inversion regions                                                                                                           |

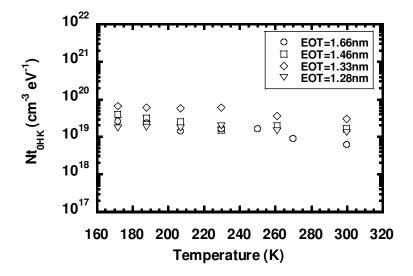

| 4.11 | Extracted values of $N_{t0HK}$ are plotted as a function of temperature for devices with different IL thicknesses                                                                                                                                                                                                               |

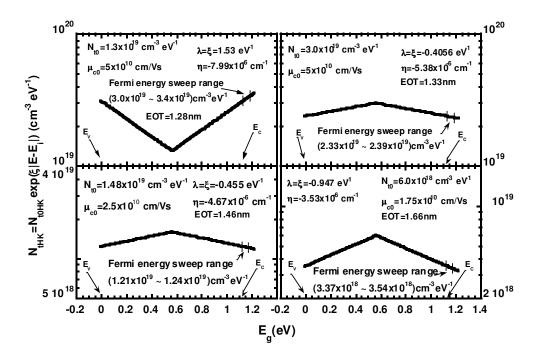

| 4.12 | The extracted HfSiON trap distribution using the MSUN Model and the experimental data obtained for each IL thickness. Also                                         |    |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

|      | imposed on each figure are the active trap levels probed by                                                                                                        |    |  |

|      | Quasi Fermi level                                                                                                                                                  | 84 |  |

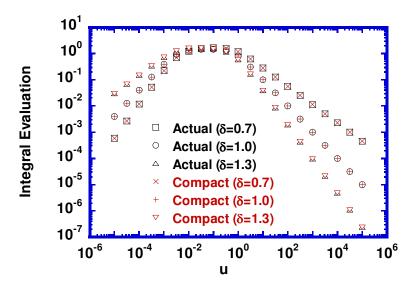

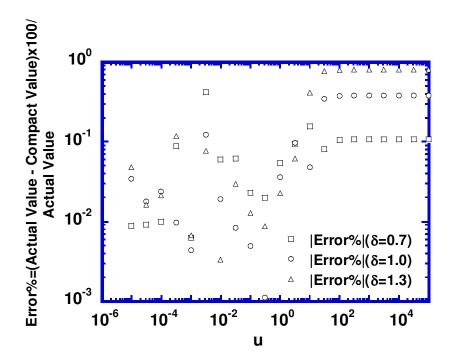

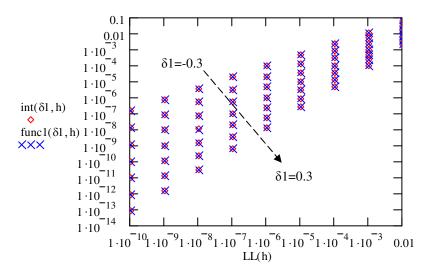

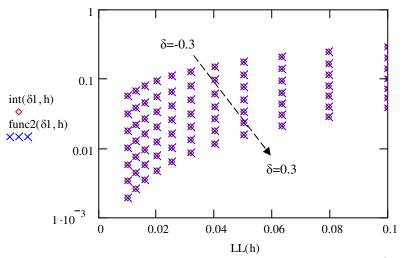

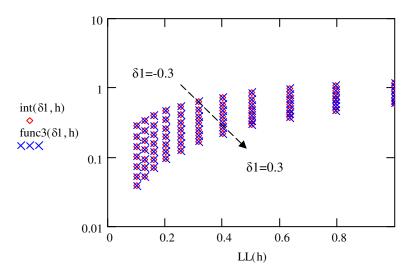

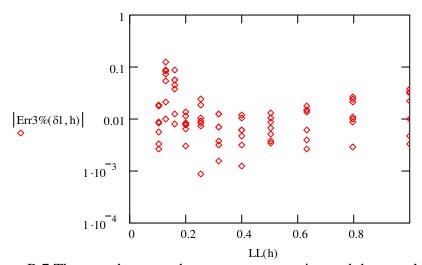

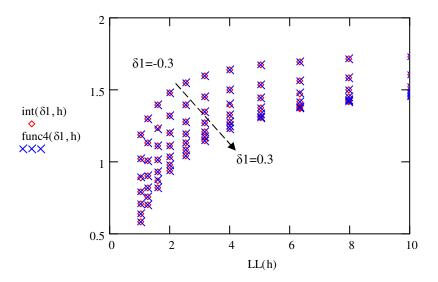

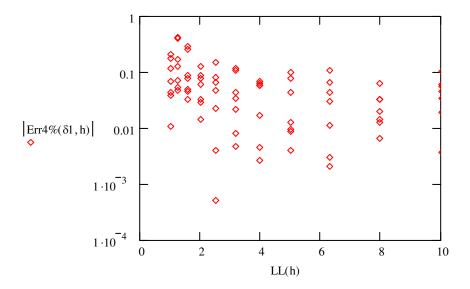

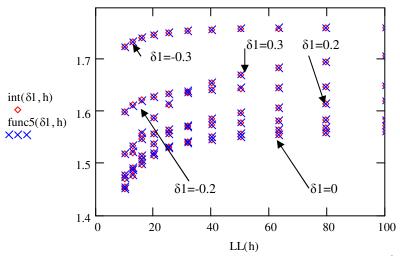

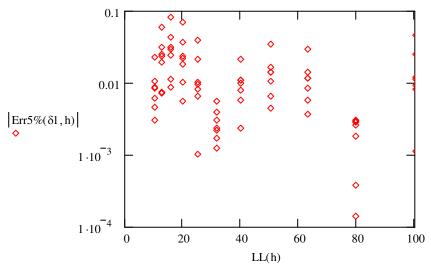

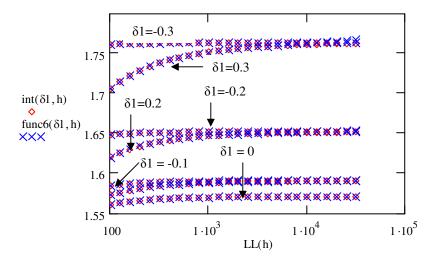

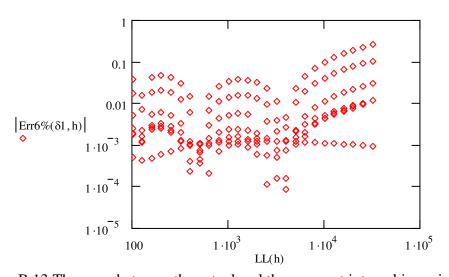

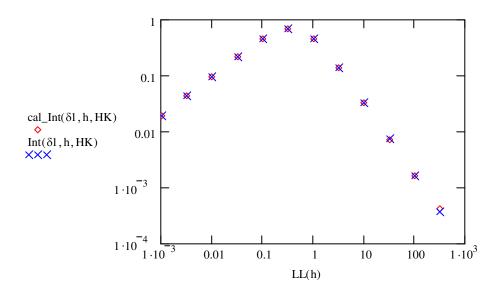

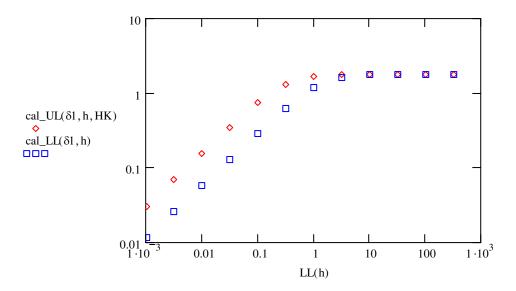

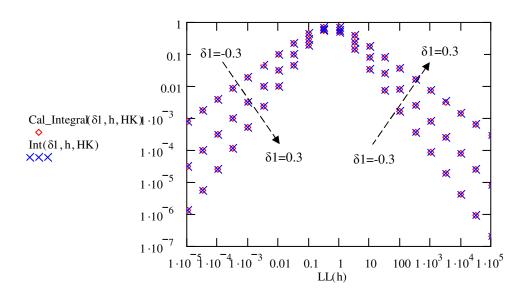

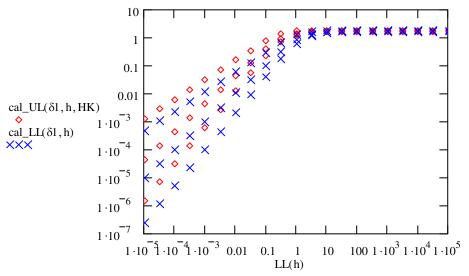

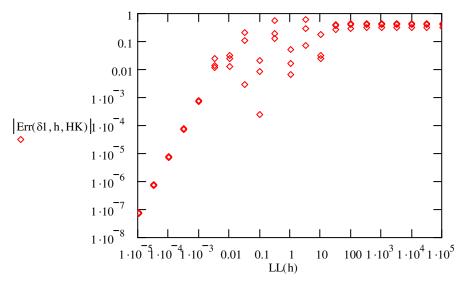

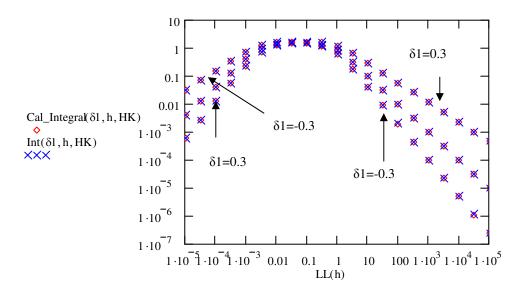

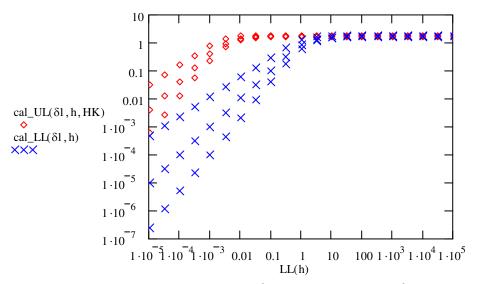

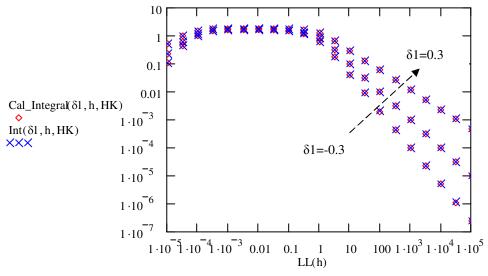

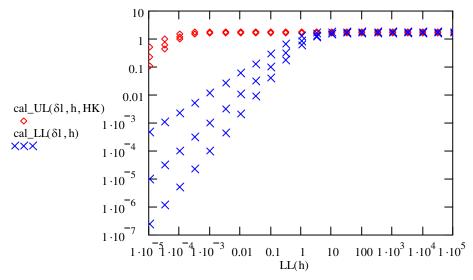

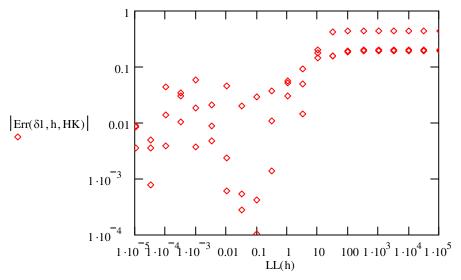

| 4.13 | Comparison between the actual integral and the values obtained using the compact form. Very good agreement was achieved                                            | 90 |  |

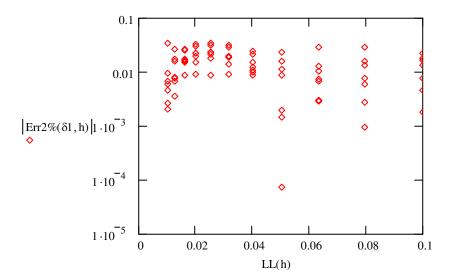

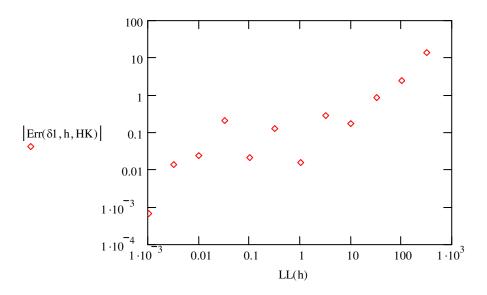

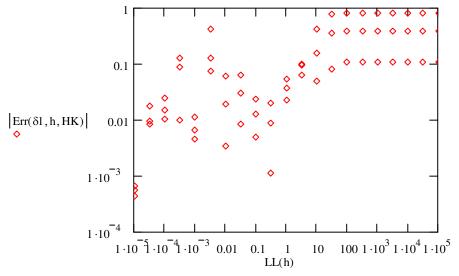

| 4.14 | The error between the actual integral and the compact form is shown for 3 different values of frequency exponent $\delta$ . In all cases the error was below $1\%$ | 90 |  |

# LIST OF TABLES

| Table |                                                          | Page |

|-------|----------------------------------------------------------|------|

| 2.1   | Devices used for flicker noise measurements              | . 26 |

| 4.1   | The list of extraction parameters used in the MSUN Model | . 75 |

| 4.2   | The extracted parameters using the MSUN Model            | . 82 |

#### CHAPTER 1

#### INTRODUCTION

### 1.1 Introduction

Aggressive downscaling of semiconductor devices has pushed the performance of SiO<sub>2</sub> to its limits as the ideal gate dielectric in CMOS technology. Introduction of high dielectric constant materials (referred to as high-k materials from here on) as the alternate dielectric for these MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistor) introduces some fundamental differences in the material properties and the structure of the gate stack. In addition, high-k incorporation affects some of the fundamental parameters of MOSFET devices, of which the carrier mobility degradation [1,2] and the low frequency noise behavior are of particular interest [3,4,5,6]. In this context, the Unified Model (the most successful flicker noise model developed for SiO<sub>2</sub> based MOSFET devices) shows significant discrepancies when applied to the analysis of noise in devices with high-k gate stacks. Flicker noise in semiconductor devices, characterized by  $f^{-\delta}$  (0.8< $\delta$ <1.2) in the lower frequency range (f<10kHz), is an important device performance criteria as it often sets the detection limits in device applications and its up-conversion affects higher frequency applications. Accurate prediction of flicker noise thus becomes an essential factor in device simulation. Most notable of the discrepancies mentioned above is the variation in the extracted trap density values by different research groups even on the same material. Moreover, the extracted values show a dependence on the interfacial layer thickness (IL). IL is not a model parameter in the Unified Model. The semiconductor industry is in need of a flicker noise model that is capable of accurately predicting the low frequency noise in MOSFETs with high-k dielectric materials.

The objective of this work is to develop a physics-based, scalable and compact model for the flicker noise prediction of high-k MOSFET devices. This work focuses on identifying the physical origin of flicker noise in MOSFET devices having high-k materials as the gate dielectric by extensive analysis of experimental data and developing a physics-based accurate flicker noise model that is compatible with industry standard device simulators such as BSIM (Berkeley Short-Channel IGFET Model) and PSP (surface-potential-based model). Thus, in the absence of any existing flicker noise model for high-k gate stack MOSFET devices, this work addresses a significant deficiency in the low frequency noise research area and makes an important contribution in device modeling and characterization industry by providing an accurate flicker noise model compatible with industrial applications.

### 1.2 Scaling down of MOSFET devices and incorporation of high-κ materials

In order to facilitate faster device operations and higher on chip device integration, ITRS (International Technology Roadmap for Semiconductors) [7] has set out a very aggressive route for device scaling. As Moore's law predicted, there has been

an exponential growth in the number of devices integrated on a single chip over the last few decades with transistor densities doubling approximately every 18 months.

# 1.2.1 Role of $SiO_2$ in device scaling

One of the most important factors in achieving such a high rate of continued device integration is the role of SiO<sub>2</sub> as an excellent dielectric material in the CMOS process technology [8]. Thermally grown amorphous SiO<sub>2</sub> has some outstanding material and electrical properties which include a very high quality substrate-dielectric interface that is stable both electrically and thermodynamically. In addition to providing low interface densities (10<sup>10</sup> cm<sup>-2</sup>) as well as low defect charge densities (10<sup>10</sup> cm<sup>-2</sup> eV<sup>-1</sup>), it results in very good electrical isolation between the channel and the gate with high breakdown fields (15 MVcm<sup>-1</sup>). As a consequence of such significant reduction in device sizes, the gate oxide thickness has been proportionally decreased in order to achieve a reasonable threshold voltage. Currently, ultra thin (~13Å) SiO<sub>2</sub> as the gate dielectric is routinely obtained in the industry with dielectric properties sufficient to ensure proper device operations. Further reduction of SiO<sub>2</sub> thickness approaches to within two mono layers of the conduction channel, where the O2 atoms can not have a full arrangement of O<sub>2</sub> neighbors and fail to form the full band gap compared to bulk SiO<sub>2</sub>. Consequently, dual mono layer SiO<sub>2</sub> fails to retain the same desirable dielectric properties in ultra thin MOSFET devices, with a consequence of high leakage currents and thereby causing undesirable power dissipations. The semiconductor industry must use alternate materials to continue the performance gains predicted by Moore's law.

# 1.2.2 Principle of using high-k materials as the alternate gate dielectric

The effect of the device dimensions and oxide layer thickness on MOSFET performance can be better understood in terms of the relations between the channel current and applied bias voltages. From the basic theory of MOSFET operations, the expression for the channel current in the linear region (Equation 1.1) and the saturation region (Equation 1.2) can be given as:

$$I_{d} = (W/L)\mu C_{inv} (V_{g} - V_{t} - V_{d}/2) V_{d}$$

(1.1)

$$I_d = (W/L)\mu C_{inv} (V_g - V_t)^2 / 2$$

(1.2)

Here,  $I_d$  is the channel current, W and L are width and length of the channel respectively,  $V_t$  is the threshold voltage,  $V_g$  and  $V_d$  are the voltages applied at the gate and the drain terminals respectively with respect to the source terminal.  $C_{inv}$  denotes the inverted channel capacitance, and  $\mu$  is the carrier mobility.

As is made clear by these expressions, for both the linear region and the saturation region the channel current increases (resulting faster device response) with either an increase in  $C_{inv}$ , a decrease in channel length L, or a decrease in threshold voltage  $V_t$ . The dielectric thickness of the device has an inverse effect on both the inversion capacitance and the threshold voltage. Thus, decreasing the dielectric thickness increases the channel current. To make sure  $V_t$  is not affected by thermal energy fluctuations around room temperatures,  $V_t$  is maintained at a minimum value of 200 mV.

Thicker dielectrics may be used to achieve the same drive current if they have higher dielectric constant. Considering any parallel plate capacitor, the relation between the channel capacitance and the dielectric thickness can be shown as:

$$C_{inv} = \kappa_{ox} \varepsilon_0 \, A/t_{ox} \tag{1.3}$$

Equation 1.3 directly shows the dependence of the device drive current on dielectric thickness and how it is related to dielectric constant of the material through  $C_{inv}$ . Here,

$\kappa_{ox}$  and  $t_{ox}$  are the dielectric constant and the thickness of SiO<sub>2</sub> respectively,  $\varepsilon_0$  is the permittivity of free space and A denotes the channel area. It is apparent from Eq. 1.3 that the same inversion capacitance  $C_{inv}$  and hence identical drive current  $I_d$  can be obtained using a thicker dielectric material with a physical thickness of  $t_{high-\kappa}$  as well as a higher dielectric constant of  $\varepsilon_{high-\kappa}$  following the relation

$$C_{inv} = \kappa_{high-\kappa} \varepsilon_0 \, A/t_{high-\kappa} \tag{1.4}$$

where,

$$\kappa_{high-\kappa}/t_{high-\kappa} = \kappa_{ox}/t_{ox}$$

(1.5)

The above relations provide the theoretical basis for using materials with higher dielectric constant to overcome the limitations imposed by physical thickness of the gate insulator. Figure 1.1 illustrates MOSFET devices with SiO<sub>2</sub> and high-k material stack as the gate dielectric.

Figure 1.1 MOSFET devices with SiO<sub>2</sub> and high-k stack as the gate dielectric.

# 1.2.3 Selection of suitable high-k materials

The choice of the ideal dielectric requires fulfillment of some crucial properties and a systematic approach in the ideal dielectric selection process. Such a systematic consideration of dielectric properties includes [8]:

- permittivity, band-gap and band offset between Si and dielectric conduction band (or valence band for p-type) edges.

- 2. thermodynamic stability

- 3. film morphology

- 4. interface quality

- 5. compatibility with materials used in current and future CMOS processes

- 6. process compatibility and

# 7. reliability

The significance of the above mentioned properties are briefly discussed here. Higher permittivity is required as a means to deposit dielectrics with higher physical thickness with the same current drive, as explained earlier. Large band gap ensures that the material has adequate insulating properties. A tradeoff should be under consideration at this point as permittivity and band gap show an inverse dependence on each other. The band offset between the dielectric and Si should be high, to ensure that the probability of tunneling into the dielectric from the conducting channel is low. The dielectric material needs to be thermodynamically stable, so that after deposition it does not react with the substrate and change the material properties. The resultant interface is expected to be low in interface states and defect states, to minimize Coulomb

interaction between carriers and charged interface traps which may lower the carrier mobility or increase the flicker noise in the device. Film morphology of the candidate dielectric is another important issue in the overall selection process. The dielectric is desired to be amorphous in nature as opposed to polycrystalline structures, as the grain boundaries in polycrystalline materials can act as current leakage paths and degrade the device performance. It is expected that the new dielectric material provides good performance with Si based gate materials and does not require special materials such as metal gates. Another important criteria in the dielectric selection process is its compatibility with the current and future fabrication process to ensure product quality, throughput and economic feasibility. The alternative material under consideration should also withstand the long term reliability benchmark test requirements of the industry to ensure product life.

Several high-κ compounds have been identified as promising candidates to replace SiO<sub>2</sub> as the gate dielectric [8, 9, 10]. Al<sub>2</sub>O<sub>3</sub> from Group IIIA in the periodic table, shows excellent thermodynamic stability; however, the lower κ value does not show much promise for the long term solution, as smaller technologies in the future will require lower effective thickness of the dielectric and hence higher dielectric coefficient. La, Pr and Y based oxides from group III B have shown higher k values compared to Al<sub>2</sub>O<sub>3</sub>. However, the voltage shift associated with these materials lie in the range of 300 - 700 mV, suggesting a high fixed charge density (10<sup>12</sup> cm<sup>-2</sup>). Thermodynamic stability is another big concern for group III B materials, the materials react with Si substrate after deposition which is not desirable. TiO<sub>2</sub>, ZrO<sub>2</sub> and HfO<sub>2</sub>

from group IV B have shown very good overall performance, with the exception of Ti based oxides. Ti based oxides show reduced oxide limitations having many oxygen vacancies that can act as carrier traps and high leakage current paths. A system of materials, called the pseudo-binary alloys having the forms such as  $(ZrO_2)_x(SiO_2)_{1-x}$  and  $(HfO_2)_x(SiO_2)_{1-x}$ , has emerged as a possible source of alternate dielectrics. This system enables retention of the desired characteristics of two different oxides and at the same time eliminates the undesired characteristics of the individual oxides.

## 1.2.4 Effect of $N_2$ incorporation

An important issue regarding the high- $\kappa$  dielectric characteristics is the role of  $N_2$  at the dielectric interface to improve the interface quality, which is explained in this section. Nitridation of gate dielectric materials is attractive as it provides advantages in terms of superior device performance when compared to MOSFETs with non-nitrided high- $\kappa$  dielectric gate stack. The diffusion of Boron from highly doped gate region across the thin oxide to the lower doped channel area is reduced by  $N_2$  incorporation; thus, it reduces the threshold voltage shift. Incorporation of  $N_2$  also increases the dielectric constant compared to  $SiO_2$  and helps to lower the leakage current [8]. The high- $\kappa$  dielectric used in this work, HfSiON, has been reported to result in two orders of magnitude lower gate leakage current compared to  $SiO_2$  [11]. Moreover, it shows good IV and CV stability under stress conditions with dielectric breakdown characteristics similar to that of  $SiO_2$  [11] and high carrier mobility [12]. The interface trap density and the defect states introduced by nitridation have been well researched in the industry, revealing a strong correlation between nitrogen induced defects and

oxygen vacancies as well as interstitials in the high- $\kappa$  gate stack [13]. The interface trap density is reported to be higher than that of SiO<sub>2</sub> but lower compared to other high- $\kappa$  gate materials [14]. Moreover, the trap density was observed to be a function of distance into the dielectric in the case of nitrided gate dielectrics compared to a somewhat uniform trap density for non-nitrided ones [13]. Thus, N<sub>2</sub> incorporation shows a significant impact on the interface quality and the low frequency noise behavior of the MOSFET, as these greatly depend on carrier trapping at the interface and the associated scattering mechanisms [15].

# 1.2.5 Effects of incorporation of high-k materials

In general, incorporation of high-k materials largely lowers the leakage current through the dielectric and thereby lowers the power dissipation of the devices. Nevertheless, there are some undesirable consequences of using high-k materials in MOSFETs. The primary disadvantage of high-k is that they often reduce the device performance. Some of the commonly encountered effects associated with using high-k materials as the gate dielectric are:

- 1. Charge trapping in the dielectric

- 2. Threshold voltage instability

- 3. Dielectric breakdown

- 4. Lower carrier mobility

- 5. Higher flicker noise and

- 6. Effects of remote optical phonon scattering on device performance.

At this point, we need to elaborate the distinction of the anticipated effects of remote optical phonon scattering on device performance from the other undesirable effects. While the device may be subjected to some additional processing steps in order to alleviate the above mentioned shortcomings, the effect of remote phonon scattering on device performance remains an unavoidable consequence of the gate dielectric material having a higher electric permittivity, as both originate from the same physical property of the high-k materials. The high dielectric constant stems from the fact that the atomic bonds in high-k dielectrics are ionic in nature as opposed to hard atomic bonds such as in SiO<sub>2</sub>. These so called soft bonds are flexible when subjected to electric fields that enable them to absorb higher electric fields compared to the rigid atomic bonds in SiO<sub>2</sub>. The effect of this absorption is a higher dielectric constant. These flexible bonds also can respond to the oscillations caused by the optical phonons present in these materials, whereas the hard inflexible bonds in SiO<sub>2</sub> do not respond to such oscillations. When the interface plasmons or the electron cloud at the channel interface couple with this vibration of the atomic bonds, an additional scattering of the carriers in the conduction channel is introduced. This scattering is expected to further degrade the device performance [16]. As the rigid SiO<sub>2</sub> bonds do not couple with atomic vibrations caused by remote phonons, the carriers in conventional MOSFET devices are free from the effects of remote phonon scattering. To date, the impact of remote phonon scattering on the low frequency noise characteristics of MOSFET devices has not been investigated. The verification of the effect of remote phonon scattering on high-k MOSFETs thus becomes essential in this work. Any significant impact of such an

additional mechanism on the low frequency noise characteristics will necessitate a means to include the effect of remote phonon scattering in the formulation of the new noise model.

# 1.3 1/f Noise modeling

It has been the focus of research for many scientists and engineers to establish a unique theory to describe the 1/f noise in MOSFET devices, although a definite conclusion is not yet reached. In general the flicker noise models for MOSFETs can be classified as originating from two different schools of thought. In the number fluctuations models, or  $\Delta N$  models, based on Mc.Whorter's [17] theory, it is assumed that fluctuations occur in the number of carriers in the channel as the carriers tunnel between the channel and the traps located in the dielectric. This fluctuation in the carrier number results in a fluctuation in the channel current which is responsible for the flicker noise. Thus, the  $\Delta N$  models assume that 1/f noise in MOSFET devices is a surface phenomena that is directly related to the quality of the Si-SiO<sub>2</sub> interface and the SiO<sub>2</sub>. On the other hand, the bulk mobility fluctuation models, or  $\Delta \mu$  models, based on Hooge's theory [18] predict that the fluctuations in the channel current are a result of fluctuations in the carrier mobility through variation in the scattering cross section associated with the collision. This is believed to be originating from bulk phonon scattering from the substrate. Thus,  $\Delta\mu$  models assume flicker noise is related to the total number of carriers in the channel. Instead of a surface origin of flicker noise as in  $\Delta N$  models,  $\Delta \mu$  models assume a volume origin in homogeneous semiconductors.

# 1.3.1 Flicker noise prediction with existing models

Both number fluctuation models and the bulk mobility fluctuation models have their advantages and disadvantages. The  $\Delta N$  model is strongly supported by the random telegraph signal (RTS) measurements [19], although the presence of some additional noise components are not explained [20]. This model is also supported by Reimbold's formulation [21], valid over the bias range of weak inversion to strong inversion [20]. In Reimbold's model, McWhorter's model is further developed, taking into consideration all the capacitive components of small signal device model. The  $\Delta\mu$  model, although showing better predictions for p-type devices in the strong inversion region, fails to explain the weak inversion mobility behavior. This model lacks from a strong theoretical definition of the noise coefficient α<sub>H</sub> as well and thus remains an empirical model [20]. The so called Unified Model [22]; based on the correlated number and surface mobility fluctuations theory [22, 23]; shows a better agreement with the experimental data for both n and p type MOSFETs over a wide temperature range and thus has become the most successful theory adopted for low frequency noise modeling and analysis [20,24,25,26,27,28,29,30]. This model is derived from the number fluctuation theory, assuming that the carriers are trapped or detrapped by the traps in the dielectric. Therefore, along with the number of carriers in the channel, the number of trapped carriers also fluctuates. The fluctuation of the latter causes a fluctuation in the coulomb potential existing between the charged traps and the carriers in the channel, which in turn induces a correlated fluctuation in the mobility of the carriers at the channel interface. According to the Unified Model, this correlated number and mobility fluctuation is responsible for the fluctuations in the drain current and hence the current noise spectrum  $S_{I_d}$ . The model is further modified according to Koga's [31] observation of Coulomb potential screening by higher density of channel carriers.

# 1.3.2 Application of Unified Model in noise prediction of high-k gate-stack MOSFETs

Although the Unified Model is the most successful low frequency 1/f noise model for the conventional gate dielectric devices, the extracted parameter values using this model show noticeable discrepancies when applied to devices using high-κ materials as the gate dielectric [32]. Most notable of them is the lack of agreement in the extracted trap density values by different research groups even for the same material. Furthermore, significant dependence on the interfacial layer thickness has been observed in the extracted trap density values, although interfacial layer thickness is not a model parameter in the original Unified Model.

# 1.3.3 Possible origins of the observed discrepancies

The original Unified Model was developed for conventional  $SiO_2$  based MOSFET devices which differ from their high- $\kappa$  gate stack counter parts both structurally and in material properties. In the former type, a single layer of  $SiO_2$  is used as the gate dielectric material whereas the high- $\kappa$  gate stack usually comprises of a single or multiple layers of high- $\kappa$  materials over a thin interfacial layer (typically of  $SiO_2$ ).  $SiO_2$  is regarded as an ideal dielectric material as it provides a superior interface with Si substrate in terms of lower interfacial trap density as well as a much cleaner dielectric bulk. Compared to that, high- $\kappa$  materials provide an interface with higher

interface trap density [33] and a bulk that is inherently phonon scattering prone due to its material properties having soft ionic bonds [16].

The processing of SiO<sub>2</sub> is a mature technology in the semiconductor industry and the trap profile in the SiO<sub>2</sub> is a thoroughly studied research topic [34, 35]. Unlike SiO<sub>2</sub>, high-κ materials processing is still under development, with atomic layer deposition (ALD) being considered a promising process technology [36]. The estimated interface trap density by different research groups, which lacks an agreement with each other, are believed to represent an average value, as they appear to be dependent on the interfacial layer thickness as well as the process technology [32]. This disagreement in the extracted trap density, based on the original Unified Model, may be attributed to the fact that the original model accounts for only the noise contribution of the single layer of conventional dielectric material but not that of the high-k layer, as this layer is absent in devices with SiO<sub>2</sub>. Moreover, as the exact trap density profile for the high-κ materials is yet to be established, the trap profile model used for the high-κ layer needs to provide a great deal of flexibility to simulate realistic trap profiles. Energy dependence of trap density in SiO<sub>2</sub> based MOSFETs is well documented [37]. For highk gate-stacks it has been reported that the effective trap density values inside the dielectric show spatial variation as well [13]. Thus, the use of a single valued trap density, as adopted in the original Unified Model, may prove to be inaccurate when applied to high-κ gate stack MOSFET devices.

# 1.3.4 Theoretical basis of the new model

The underlying mechanism affecting the low frequency noise characteristics of high-k MOSFETs used in this work was experimentally verified. Irrespective of temperature or interfacial layer thickness, the correlated number and surface mobility fluctuation model was determined as the dominant mechanism responsible for the observed noise behavior. Consequently, the new model was developed in the framework of the Unified Model based upon the same theory by implementing the above mentioned distinctive high-k features. The new model is named after the Unified Model as the MSUN (Multi Stack Unified Noise) Model [38, 39, 40].

# 1.3.5 Modifications in MSUN Model and implementation

First, the effect of remote phonon scattering was experimentally tested to identify any additional noise mechanisms originating from the high-k layer. No observable impact of remote phonon scattering was found on the flicker noise and its effect was not separately included in the MSUN Model. In this work, special attention was paid to the incorporation of the contribution of the high- $\kappa$  layer in the total low frequency noise of the device, along with that of the interfacial layer. This was lacking in the original Unified Model. Tunneling of carriers through a double step cascaded barrier was considered instead of a single step, to incorporate the double layered structure of the gate stack, resulting in the required modification in the expression of  $S_{\Delta N_r}(Hz^{-1})$ ; the power spectral density resulting from the fluctuations of trapped charge carriers. Instead of using a single average experimental value, the trap density profiles for the interfacial layer as well as the high- $\kappa$  layer were implemented using a more

flexible and comprehensive expression [34], which incorporates the dependence of the effective trap density on the energy and spatial distribution of traps, along with the band bending inside the dielectric.

# 1.3.6 MSUN Model performance verification

The theoretical model was experimentally verified on MOSFET devices having HfSiON as the high-k dielectric material on four different interfacial layer thicknesses of SiON. Verification of remote phonon scattering was done in the temperature range of 172K to 300K. Although the carrier mobility was affected by remote phonon scattering, the low frequency noise was not. The model predictions were found to be in very good agreement with the experimental data at all temperatures irrespective of interfacial layer thicknesses. The predicted current noise spectral density  $S_{I_d}$  at 1Hz showed very good agreement with the experimental data in the bias range of weak inversion to strong inversion. The extracted trap density values were observed to be consistent with respect to temperature or interfacial layer thicknesses. The working theoretical model verified with experimental data was transformed into a compact form to comply with industry requirements. The compact form was further expressed in various forms compatible with industry standard device simulation software packages.

# 1.4 Summary

The importance of this work is evident from the fact that, it represents research which deals with contemporary issues arising directly from the semiconductor industry, involving a novel technology, such as the incorporation of high-k materials for new generation of MOSFETs. The analysis of the technical complications posed by the inherent material properties of the high-k dielectric and the dynamics of the carrier tunneling in the multilayer gate-stack involve novel theories such as the effect of remote optical phonon scattering in high-k materials. The work involves verification of the theoretical predictions with massive amount of experimental data; taken on a meaningful array of samples using a customized experimental setup.

The key accomplishments of this work may be summarized as follows:

• In this work, we have developed the first ever physics-based compact flicker noise model for MOSFET devices with high-k dielectric materials. The lack of such model for prediction and analysis of low frequency noise with adequate accuracy is recognized as a large deficiency in the semiconductor noise research area. In this work, we have addressed that deficiency to its entirety. From a systematic analysis of the problem to the development of a new physics based model and its experimental verification, all the necessary steps were completed in this work. Finally, the model was expressed in an accurate compact form, and converted to formats compatible with leading device simulation packages in the industry, such as, PSP and BSIM.

- A systematic study on the failure of the Unified Model in flicker noise prediction of high-k dielectric MOSFETs was carried out and the possible origins of these failures were identified. Before this work, the fundamental discrepancies in the Unified Model predictions were reported. However a systematic study like this and identification of the root causes were lacking.

- The experimental verification of remote phonon scattering on the same samples were done considering two different aspects of device characteristics. The importance of this experimental findings lie in the fact that for the first time it has been established remote phonon scattering does not affect flicker noise characteristics, while its presence is confirmed through the observed effects on the mobility characteristics.

- Our experimental finding that the remote phonon scattering bears no effect on noise carries great significance from industrial application point of view. It indicates that the expected detrimental effects of phonon scattering on MOSFET characteristics need not be overly generalized. It may as well indicate to special application areas where high-k MOSFETs may be utilized more efficiently.

- A more realistic trap density profile is implemented in the new model showing exponential dependence on energy and spatial distribution of traps. This incorporation of energy and spatial dependence proves to be essential for modeling of noise in high-k dielectric MOSFETs.

- Multi layer structure of the gate dielectric was implemented by considering tunneling of carriers through a double step barrier. Thus, the dynamics of tunneling through stacked dielectric is incorporated in the model, which is essential in description of high-k MOSFET noise characteristics and lacking in the Unified Model.

- The crucial impact of the interfacial layer on the overall noise is very well explained by the MSUN Model. It also explains the interfacial layer dependence and variation in the extracted trap density values observed in the application of Unified Model on high-k MOSFETs. Tunneling of carriers through a single dielectric layer does not have the ability to take into account the variation in physical thicknesses of individual layer for the same effective physical thickness of the dielectric, which the MSUN Model is capable of.

- Physical thickness of each individual dielectric layer is taken into consideration, compared to assumption of infinitely thick dielectric in the Unified Model. Experimental verification shows, the interfacial layer dependence of flicker noise is correctly incorporated in this model, which was a major drawback in the application of the Unified Model.

- A physics based expression for the frequency exponent  $\delta$ , of the noise spectrum  $1/f^{\delta}$  has been obtained in MSUN Model. The resulting expression shows dependence on the trap density profile in the corresponding dielectric layer as well as on its material properties through the carrier tunneling coefficient. In contrast,

the frequency exponent in the Unified Model is always assumed to be 1, which has been experimentally proven wrong.

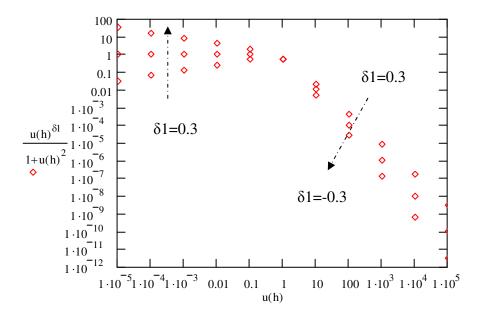

• The integrals  $\int_{LL}^{UL} \frac{u^{\delta'}}{1+u^2} du$  representing the summation of noise in the

dielectric were expressed in a compact form, within 1% of the actual integral. For noise predictions, this accuracy is quite satisfactory, as statistical nature of noise shows significant variation in successive measurements on the same sample. The main challenge in preserving the accuracy comes from the large range of values the integral limits can take (LL= $10^{-10}$  to  $10^3$  and UL= $10^{-6}$  to  $10^{23}$ ) along with a range of values for  $\delta$ ' (-0.3 to 0.3).

The dissertation is organized in the following way. This chapter provides the background, goals and achievements of this work. The necessity of incorporation of high-k materials in scaled MOSFET devices and its consequences on the application of available flicker noise models on devices with high-k dielectrics are briefly explained. The fundamental factors contributing to the observed discrepancies are discussed and possible remedies are mentioned. The implementation of the newly proposed MSUN Model to high-k MOSFETs and the experimental verifications are also briefly discussed.

Chapter 2 provides the details of the experimental setup and procedures used in this work. The variable temperature measurement system as well as its measurement capabilities is discussed.

Chapter 3 provides a brief overview of the dominant flicker noise theories. Then a detailed derivation of the MSUN Model is given in the framework of the original Unified Model.

Chapter 4 explains the results obtained in this work. The verification of remote phonon scattering, identification of the dominant noise mechanism responsible for the observed noise behavior and comparison of the theory and experiment are presented along with experimental data on MOSFETs having four different interfacial layers in a wide temperature and bias range.

Chapter 5 evaluates the overall work considering the importance of the work from industrial application point of view, the goals set originally as the outcome of this work and the achievements made in meeting these goals.

Appendix A describes the Mathcad implementation of the theoretical model.

Appendix B presents the compact form of the MSUN Model and its derivation.

#### CHAPTER 2

#### NOISE MEASUREMENTS

### 2.1 Introduction

#### 2.1.1 Flicker noise measurement

Flicker noise is a well established diagnostic tool for semiconductor device characterization and reliability prediction. Advantages of flicker noise measurements include its non destructive nature as well as ability to be performed on devices with small dimensions, which makes it particularly suitable for characterization of submicron MOSFET devices. The disadvantages of this measurement technique are possible electromagnetic interference from the environment, the sophistication of the experimental assembly and, as a consequence, the requirement of expertise skills to conduct the experimental procedures to acquire noise data.

In this work, flicker noise measurement have been performed on MOSFETs with four different interfacial layer thicknesses to determine the underlying physical mechanisms affecting the low frequency noise mechanism. Statistically meaningful amount of noise data has been acquired to experimentally validate the newly proposed noise model.

## 2.1.2 Variable temperature measurement

Variable temperature measurements provide a tool to evaluate carrier transport properties in semiconductor devices. A combination of several variable temperature procedures can be effectively used as a powerful characterization technique for the extraction of many temperature dependent device parameters. With the advent of high-  $\kappa$  based submicron MOSFETs, variable temperature measurements find an important application in the characterization of carrier mobility and low frequency noise characteristics of these devices. Remote optical phonon scattering is predicted to be a potential carrier scattering mechanism as an inherent property of high- $\kappa$  dielectric materials. Temperature dependent nature of the phonon scattering mechanism is the key to this applicability of variable temperature measurements on high- $\kappa$  gate stack devices.

In this work, a variable temperature measurement setup has been built and used for the characterization of submicron high-κ gate MOSFET devices, incorporating the split CV and 1/f noise measurement procedures. The experimental validation of remote phonon scattering was done in the temperature range of 172K to 300K. Determination of any such additional underlying physical mechanism specific to these materials affecting the low frequency noise characteristics will require consideration in the noise formulation as well.

Two different aspects of device characteristics were considered for the investigation of remote phonon scattering effects:

- 1. Degradation of carrier mobility and

- 2. Low frequency noise characteristics.

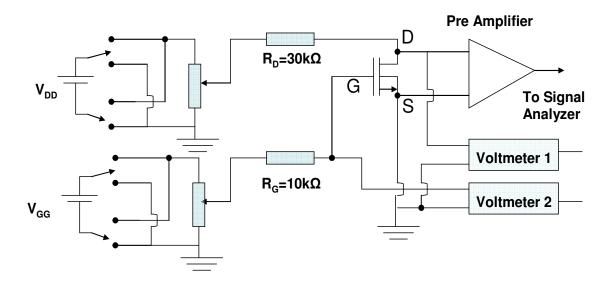

## 2.2 The experimental setup

Providing a low noise ambient for the DUT is essential in this experiment, as low frequency noise measurements are sensitive to external electromagnetic interferences. To ensure precise control of temperature, good thermal isolation from the surrounding is required to minimize heat exchange by convection and conduction. For low temperature operations, controlling the humidity of the ambient of the DUT becomes an additional requirement, as condensation at lower temperatures can damage the device. The above mentioned requirements are fulfilled by placing the DUT inside a cryostat located in a metallic shielded chamber which minimizes the effect of noise from the surrounding. The cryostat is evacuated to thermally isolate the DUT from its surroundings as well as to minimize the humidity in the DUT ambient.

The following measurement facilities are utilized for characterization:

- DC measurements using a parameter analyzer

- Split CV measurements using a LCR meter and

- Low frequency noise measurements with a customized experimental setup

In this system we have used the cryostat Model RC-110 by CRYO Industries of America, Inc [41]. The cryostat was evacuated using an oil-sealed rotary pump. Welch DUOSEAL vacuum pump, Model 1376 [42] was used in this setup. The bias box was custom made and like the low noise pre amplifier it was low noise battery operated. Low noise preamplifier, Model 113, by EG&G Princeton Applied Research [43] was used in this setup. A HP 4284A LCR meter was utilized for the CV measurements, HP 4155B Parameter Analyzer measured the DC characteristics and the noise spectrum was

captured using a HP3562A Dynamic Signal Analyzer. A schematic diagram of the variable temperature measurement set up is shown in Figure 2.1.

Some of the special features of this setup are as follows:

- Less susceptibility to electromagnetic radiation

- Minimizing heat exchange and humidity

- Precise control of temperature

- Special switching method between the device terminals and the CV, DC and noise measurement setups to ensure device safety from electrostatic discharge effects.

The details of the experimental setup and its special features are available in the cited report [44] by Tanvir Hasan Morshed. The measurement procedures will be explained in latter sections in this chapter.

Figure 2.1 The schematic diagram of the variable temperature measurement setup.

## 2.3 Device specifications

The devices used in this work were provided by Texas Instruments. HfSiON was used as the high- $\kappa$  gate dielectric material, with a uniform thickness of 3.0 nm on four different wafers. SiON was the interfacial layer (IL) between the dielectric layer and the silicon substrate with thicknesses of 0.8nm, 1.2nm, 1.5nm and 1.8nm; which resulted in effective oxide thicknesses (EOT) of 1.28nm, 1.33nm, 1.46nm and 1.66nm respectively. The lengths of these devices were chosen between 0.20 $\mu$ m and 0.25 $\mu$ m with a width of 10 $\mu$ m. Variable temperature flicker noise measurements were performed on these devices in the temperature range of 172K to 300K. For split CV measurements, larger devices with the dimensions of 10x10  $\mu$ m<sup>2</sup> (LxW) were used in the same temperature range. Table 2.1 shows the devices used for variable temperature noise measurements.

Table 2.1 Devices used for flicker noise measurements

| high-κ material | EOT (nm) | IL(nm) | Length(µm) | Width(µm) |

|-----------------|----------|--------|------------|-----------|

|                 |          |        |            |           |

| HfSiON          | 1.24     | 0.8    | 0.20       | 10        |

| HfSiON          | 1.33     | 1.0    | 0.20,0.25  | 10        |

| HfSiON          | 1.46     | 1.5    | 0.20,0.25  | 10        |

| HfSiON          | 1.66     | 1.8    | 0.14~0.25  | 10        |

#### 2.4 Variable temperature measurement procedure

The experimental procedure was structured keeping in mind the differences in the material properties of high-k dielectrics from SiO<sub>2</sub> that might affect the flicker noise behavior of the devices. The first step was to verify the applicability of any existing flicker noise theory. This step was necessary to identify and establish the underlying physical mechanism that is responsible for the observed noise behavior. The correlated

number and mobility fluctuation model was given emphasis in this verification process for its applicability on both n and p type devices over a wide temperature range. The next step was to verify the effects of remote phonon scattering on these devices to incorporate any significant experimental findings in the formulation of the new noise model. As a part of this step, variable temperature split CV measurement was done to determine the carrier mobility for two purposes: (i) to use in fitting noise data to the predictions of the model, as carrier mobility is needed for the procedure and also (ii) to investigate the effects of remote phonon scattering on carrier mobility. Prior to noise and CV measurements, DC characteristics were taken to make sure the devices work properly in different operating regions of interest.

The overall procedure begins with locating the desired device on the wafer and a careful packaging of the device on a ceramic Leaded Chip Carrier (LDCC) [45] package. The device is then carefully bonded with an ultrasonic wire bonder. Prior to wire bonding a set of DC characteristics is recorded and the package leads are shorted. The bonded device is then mounted on the stage and connected to the wires extending to the ports at the base of the cryostat.

At the base of the cryostat, coaxial T connections were arranged in such a way that, a set of connection ports was always available connecting the device leads, parallel to the other set used for shorting the input ports. This is essential when dealing with nano-scale MOSFET devices, since electrostatic discharge (ESD) due to triboelectric charge formation on semiconductor devices is a well known phenomenon having detrimental effects on device life and performance. Sub-micron MOSFET devices are

especially sensitive to ESD, as charge buildup across the extremely thin dielectric results in very high electric fields and causes gate leakage or in severe cases gate dielectric breakdown. Shorting of the gate and substrate input leads together eliminates the possibility of charge buildup across the gate dielectric and ensures device safety. Thus, the provision of shorting the device inputs was required in any event of physically touching the setup, especially in switching between different experimental setups. To avoid electrostatic charging or discharging through the device or inducing charge on device surface, the operator should be carefully strapped to ground, as human body is very prone to electrostatic charge buildup by simple movements.

One set of ports of the T-connectors at the base of the cryostat is then shorted while the other set is available for any procedure specific setup. As the leads are shorted at the base of the cryostat in parallel, the shorting of the leads on the package can now be removed without harming the device.

After bonding the device, a careful examination of the DC characteristics is done to check for the threshold voltage shift and change in the gate leakage current, to make sure the device is not degraded due to bonding as well as the quality of the electronic contact of the bond is satisfactory. In case of device failure a new device is bonded and the procedure is repeated. The device is then mounted on the cryostat.

The desired temperature is set at the temperature controller, when the vacuum level goes down to 80 mTorr or lower. The PID coefficients are set accordingly. The buffer maintains 10 psi of pressure inside the Dewar when not in use, through its own regulators. As soon as liquid nitrogen flow is started to lower the sample temperature, the

pressure inside the Dewar also starts to fall gradually. The pressure inside the Dewar is used to transfer LN2 through the transfer line from the Dewar to the evaporation chamber. At the beginning, LN2 evaporates very fast even before reaching the evaporation chamber to cool off the transfer line all the way, which ends at the nozzle as shown in Figure 2.2.

Figure 2.2 The cryogenic temperature setup comprises of two isolated chamber. The vacuum chamber where the sample is mounted maintains thermal isolation between the sample and the environment. In the evaporation chamber LN2 is evaporated to lower the temperature of the stage and the sample.

The evaporation chamber is completely isolated from the vacuum chamber. When the nozzle reaches cryogenic temperatures, LN2 passes through the nozzle tip and evaporates just underneath the stage where the sample is mounted. The evaporation of LN2 lowers down the stage temperature. As the sample maintains very good thermal contact with the stage, the sample temperature goes down as well. The gas N<sub>2</sub>, as an outcome of the evaporation, flows out of the system which is not further recycled. When the pressure inside the Dewar goes down to about 4 psi, the gas nitrogen cylinder is turned on and the pressure inside the Dewar is kept constant using the regulator. A higher pressure causes shorter liquid nitrogen life time. A lower pressure is found difficult to maintain at a stable level, causing poor temperature control. The PID coefficient values can be fine tuned at this stage for precise control. A value of P=350, I=50 and D=0 was found a good setup for a temperature range of 300K down to 172K. The experimental procedures were started when the temperature was stable at the desired set point.

#### 2.4.1 DC measurement procedure

The Force/Sense ports from the parameter analyzer HP 4155B were connected to the available ports in parallel to the shorted ones, eliminating the possibility of creating any potential difference across the connecting leads. The Force/Sense ports were set to be maintained at the same potential when idle. In this condition it was possible to safely open the shorted ports without risking the device to static electric charge development across the device inputs.

The basic device parameters such as lead currents  $I_d$ ,  $I_s$ ,  $I_g$  and  $I_{sub}$  as well as the terminal voltages were recorded. User defined functions to obtain the square root of

drain current  $SQI_d(A^{1/2}) = I_d^{1/2}$  and its derivative with respect to gate terminal voltage  $DSQI_d(A^{1/2}/V) = \frac{dSQI_d}{dV_g}$  were evaluated to determine the threshold voltage. The transconductance  $g_m(A/V) = \frac{dI_d}{dV_g}$ , channel conductance  $g_d(A/V) = \frac{dI_d}{dV_d}$  and the subthreshold swing S(Dec/V) of the device were also obtained. Details of the setup, extraction procedure and user defined function implementations can be found in the reference [46].

The experimental data acquired in the DC parameter extraction process are illustrated in the following figures.

Figure 2.3 Extraction of threshold voltage  $V_t(V)$  is shown here. A tangent is drawn on the curve  $SQI_d$  at  $V_g$  corresponding to the maxima of  $DSQI_d$  (marked by the square on the vertical line). The tangent intersects the  $V_g$  axis at the threshold voltage  $V_t$ .

Figure 2.4 The extracted threshold voltage  $V_t$  is shown for four different interfacial layer thicknesses. A linear shift was observed in the threshold voltages irrespective of the interfacial layer thickness. The temperature dependence was observed to be identical for all devices.

Figure 2.5 Channel conductance  $g_d$  as a function of drain voltage  $V_d$  for different values of gate voltage ( $V_g = 100 \text{mV}$  to  $V_g = 600 \text{mV}$ ).

Figure 2.6 Channel current  $I_d$  as a function of  $V_d$  at different gate voltages in the range of  $V_g = 100 \text{mV}$  to  $V_g = 600 \text{mV}$ .

Figure 2.7 Drain current  $I_d$  as function of gate voltage  $V_g$  at different values of drain voltage ( $V_d = 10 \text{mV}$  to  $V_d = 50 \text{mV}$ ).

Figure 2.8 The trans-conductance  $\,g_{\,m}\,$  as a function of gate voltage  $\,V_{\,g}\,$  at different drain voltages  $V_{\,d}\,$  .

Figure 2.9 Gate leakage current  $I_g$  as a function of gate voltage  $V_g$  at different drain voltages ( $V_d = 10 \,\mathrm{mV}$  to  $V_d = 50 \,\mathrm{mV}$ ). With the increase of  $V_g$ , the gate leakage current increased exponentially.

Figure 2.10 Sub-threshold swing S (Dec/V) shown as a function of gate voltage at drain voltages of  $V_d = 10 \text{mV}$  and  $V_d = 40 \text{mV}$ .

# 2.4.2 C-V measurement procedure

The C-V measurements were taken after the completion of DC parameter extraction. When idle, all the Force/Sense ports of the parameter analyzer are maintained at the same potential, as mentioned earlier. As a result, the ports can now be safely shorted using the parallel connections and the Force/Sense connections can be removed. The device was then connected to the LCR meter HP 4284A and the shorting wires in the parallel ports removed. For better estimation of the experimental data, an average of 8 measurements was taken. The operating frequency was chosen to be 1 MHz, to ensure the capacitance due to interface traps did not contribute to channel capacitance. As the channel capacitance was small (~1pf), parallel circuit mode (C<sub>p</sub>-D) was selected. Both open and short corrections have been tested, no significant difference was observed in the