# DESIGN AND FUNCTIONALITY ANALYSIS OF OPERATIONAL AMPLIFIERS WITH RAIL-TO-RAIL INPUT AND OUTPUT CAPABILITY

by

# MINGSHENG PENG

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

# DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT ARLINGTON

December 2007

Copyright © by Mingsheng Peng 2007

All Rights Reserved

Dedicated to My Family

#### ACKNOWLEDGEMENTS

My appreciation goes to many people who helped me make this dissertation possible.

First of all, my deepest appreciation goes to my supervising professors, Dr. W. Alan Davis and Dr. Ronald L. Carter, for their guidance, encouragement, and support. It is my great honor to study and do research under their guidance. I gladly express my gratitude to Dr. Howard T. Russell, Jr., who has many years experience in semiconductor industry, for his help and serving on my committee.

My gratitude also goes to Dr. Enjun Xiao and Dr. Jung-Chih Chiao for their precious time to serve on my committee. I would also like to thank the faculty and staff in The University of Texas at Arlington who helped me.

I would also like to thank my colleagues at Analog IC Design Research Group for their helpful discussion and cooperation. I would like to especially thank Ms. Mei-Ping Pua for her help with the circuit layout.

Finally, I would like to express my gratitude to my family and friends for their support and encouragement. Most of all, I would like to thank my wife, Jie Liu, for her unconditional support and love. I also want to thank my son and daughter for the joy and happiness they bring to me.

November 6, 2007

#### ABSTRACT

# DESIGN AND FUNCTIONALITY ANALYSIS OF OPERATIONAL AMPLIFIERS WITH RAIL-TO-RAIL INPUT AND OUTPUT CAPABILITY

Publication No.

Mingsheng Peng, Ph.D.

The University of Texas at Arlington, 2007

Supervising Professors: W. Alan Davis and Ronald L. Carter

The operational amplifier (op amp) is a fundamental building block in analog integrated circuit design. For low power-supply voltages, the common-mode input voltage and the output voltage of op amps are always required to be able to swing from the negative power-supply rail to the positive power-supply rail, i.e., rail-to-rail. In this dissertation, op amps with rail-to-rail input and output capability are investigated. This dissertation mainly focuses on the rail-to-rail input stage design. Two different rail-torail input stages with a single differential pair and a common-mode adapter are presented. The common-mode adapter is used to shift the common-mode input voltage. Two new common-mode adapters for the input stage with a single differential pair are developed. The first common-mode adapter is based on a pseudo-differential pair, and the second one is based on current subtraction. Three bipolar and two CMOS op amps with rail-to-rail input and output capability are designed. The circuit simulation and chip test results are given in this dissertation. There are many aspects of performance for op amps. With different topologies, op amps may have different performance. One certain op amp may be good at some aspects but poor at others. The General System Performance Theory is a systematic method for system performance analysis. In order to get a single figure of merit, the General System Performance Theory is applied to compare the overall performance of the designed three different bipolar rail-to-rail op amps.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                                    | iv  |

|-------------------------------------------------------------------------------------|-----|

| ABSTRACT                                                                            | v   |

| LIST OF ILLUSTRATIONS                                                               | x   |

| LIST OF TABLES                                                                      | xvi |

| Chapter                                                                             |     |

| 1. INTRODUCTION                                                                     | 1   |

| 1.1 Background and Motivation                                                       | 1   |

| 1.2 Organization of the Dissertation                                                | 3   |

| 2. INPUT STAGE                                                                      | 5   |

| 2.1 Differential Pair                                                               | 5   |

| 2.2 Rail-to-Rail Input Stage with Complementary Differential Pairs                  | 8   |

| 2.2.1 Simple Complementary Input Stage                                              | 8   |

| 2.2.2 Constant-Gm Complementary Input Stage                                         | 11  |

| 2.2.3 Constant-Gm Complementary Input Stage<br>with Improved CMRR                   | 17  |

| 2.3 Rail-to-Rail Input Stage with a Single Differential Pair                        | 20  |

| 2.3.1 Common-Mode Adapter                                                           | 22  |

| 2.3.2 Input Stage with a Common-Mode Adapter<br>Based on a Pseudo-Differential Pair | 25  |

|    | 2.3.3 Input Stage with a Common-Mode Adapter<br>Based on Current Subtraction                             | 3  |

|----|----------------------------------------------------------------------------------------------------------|----|

|    | 2.4 Summary                                                                                              | 33 |

| 3. | OTHER CIRCUIT PARTS AND FREQUENCY COMPENSATION                                                           | 35 |

|    | 3.1 Output Stage                                                                                         | 3: |

|    | 3.1.1 Class-AB Output Stage                                                                              | 3  |

|    | 3.1.2 Rail-to-Rail Class-AB Output Stage                                                                 | 3  |

|    | 3.2 Intermediate Stage                                                                                   | 4  |

|    | 3.3 Current Reference Circuit                                                                            | 4  |

|    | 3.4 Output Protection Circuit                                                                            | 4  |

|    | 3.5 Frequency Compensation                                                                               | 4  |

|    | 3.5.1 Miller Compensation                                                                                | 4  |

|    | 3.5.2 Nested-Miller Compensation                                                                         | 4  |

|    | 3.6 Summary                                                                                              | 5  |

| 4. | OVERALL OPERATIOANAL AMPLIFER CIRCUIT                                                                    | 5  |

|    | 4.1 UTA242: Three-Stage Bipolar Op Amp with a<br>Constant-Gm Complementary Input Stage                   | 5  |

|    | 4.2 UTA243: Three-Stage Bipolar Op Amp with a Constant-Gm<br>CMRR-Improved Complementary Input Stage     | 6  |

|    | 4.3 UTA244: Three-Stage Bipolar Op Amp with a Common-Mode<br>Adapter Based on a Pseudo-Differential Pair | 7  |

|    | 4.4 OPA004: Two-Stage CMOS Op Amp with a Common-Mode<br>Adapter Based on a Pseudo-Differential Pair      | 7  |

|    | 4.5 OPA005: Two-Stage CMOS Op Amp with a Common-Mode<br>Adapter Based on Current Subtraction             | 8  |

| 4.6 Summary                                        | 88  |

|----------------------------------------------------|-----|

| 5. FUNCTIONALITY ANALYSIS OF OPERATIONAL AMPLIFERS | 89  |

| 5.1 General System Performance Theory              | 89  |

| 5.2 Functionality Analysis of Op Amps              | 94  |

| 5.2.1 Common-Mode Input Range                      | 94  |

| 5.2.2 Slew Rate                                    | 95  |

| 5.2.3 Power-Supply Rejection Ratio                 | 95  |

| 5.2.4 Input Offset Voltage                         | 96  |

| 5.2.5 Common-Mode Rejection Ratio                  | 97  |

| 5.2.6 Quiescent Supply Current                     | 99  |

| 5.2.7 Composite Performance Capacity               | 100 |

| 5.3 Summary                                        | 100 |

| 6. CONCLUSION AND FUTURE WORK                      | 101 |

| 6.1 Conclusion                                     | 101 |

| 6.2 Future Work                                    | 103 |

| Appendix                                           |     |

| A. BIPOLAR TRANSISTOR SPICE MODELS                 | 104 |

| B. CMOS TRANSISTOR SPICE MODELS                    | 106 |

| REFERENCES                                         | 111 |

| BIOGRAPHICAL INFORMATION                           | 117 |

# LIST OF ILLUSTRATIONS

| Figure |                                                                                                                      | Page |

|--------|----------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Inverting gain amplifier configuration.                                                                              | . 2  |

| 1.2    | Non-inverting gain amplifier configuration.                                                                          | . 3  |

| 2.1    | Common-mode input voltage range for (a) an npn<br>differential pair and (b) a pnp differential pair                  | . 7  |

| 2.2    | Common-mode input voltage range for (a) an NMOS differential pair and (b) a PMOS differential pair                   | . 8  |

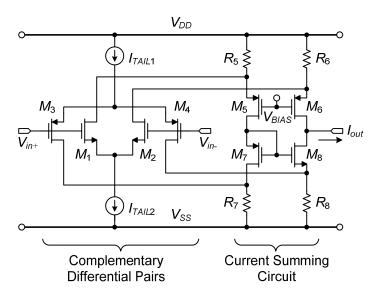

| 2.3    | Bipolar rail-to-rail complementary input stage.                                                                      | .9   |

| 2.4    | CMOS rail-to-rail complementary input stage                                                                          | . 10 |

| 2.5    | Normalized tail current versus the common-mode input voltage for pnp and npn pairs in the input stage of Figure 2.3. | . 11 |

| 2.6    | Normalized transconductance versus the common-mode input voltage for the input stage of Figure 2.3.                  | . 11 |

| 2.7    | Rail-to-rail constant-Gm complementary input stage.                                                                  | . 13 |

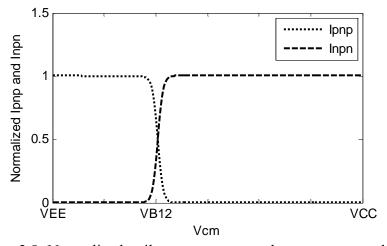

| 2.8    | Normalized tail current versus the common-mode input voltage for pnp and npn pairs in the input stage of Figure 2.7. | . 14 |

| 2.9    | Normalized transconductance versus the common-mode input voltage for the input stage of Figure 2.7.                  | . 14 |

| 2.10   | Offset voltage versus the common-mode input voltage                                                                  | . 16 |

| 2.11   | CMRR versus the common-mode input voltage                                                                            | . 17 |

| 2.12   | Rail-to-rail constant-Gm complementary input stage with improved CMRR.                                               | . 18 |

| 2.13 Normalized tail current versus the common-mode input voltage for pnp and npn pairs in the input stage of Figure 2.12. | 18 |

|----------------------------------------------------------------------------------------------------------------------------|----|

| 2.14 Normalized transconductance versus the common-mode input voltage for the input stage of Figure 2.12.                  | 19 |

| 2.15 Offset voltage versus the common-mode input voltage                                                                   | 20 |

| 2.16 CMRR versus the common-mode input voltage.                                                                            | 20 |

| 2.17 Histogram of the k'n/k'p ratio for TSMC 0.18 µm CMOS technology                                                       | 21 |

| 2.18 Two-stage op amp with a common-mode adapter.                                                                          | 23 |

| 2.19 Diagram of the operation of a common-mode adapter.                                                                    | 24 |

| 2.20 CMOS rail-to-rail input stage with a common-mode adapter based on a pseudo-differential pair.                         | 26 |

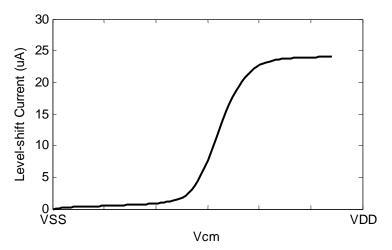

| 2.21 Level-shift current versus the common-mode input voltage                                                              | 28 |

| 2.22 Corresponding common-mode voltages.                                                                                   | 28 |

| 2.23 Normalized transconductance versus the common-mode input voltage for the input stage of Figure 2.20.                  | 28 |

| 2.24 Bipolar rail-to-rail input stage with a common-mode adapter based on a pseudo-differential pair.                      | 29 |

| 2.25 Level-shift current versus the common-mode input voltage                                                              | 30 |

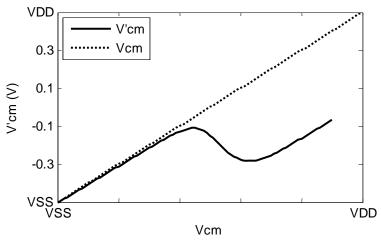

| 2.26 Corresponding common-mode voltages.                                                                                   | 30 |

| 2.27 Normalized transconductance versus the common-mode input voltage for the input stage of Figure 2.24.                  | 30 |

| 2.28 CMOS rail-to-rail input stage with a common-mode adapter based on current subtraction                                 | 31 |

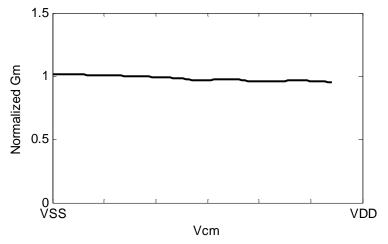

| 2.29 Level-shift current versus the common-mode input voltage                                                              | 32 |

| 2.30 Corresponding common-mode voltages.                                                                                   | 33 |

| 2.31 | Normalized transconductance versus the common-mode input voltage for the input stage of Figure 2.28.                                                                                    | 33 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

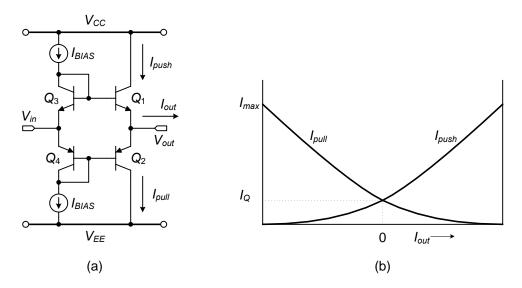

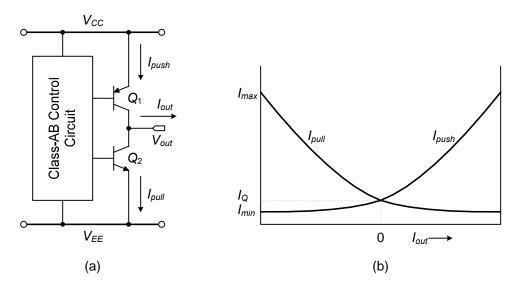

| 3.1  | (a) Voltage follower class-AB output stage with complementary bipolar transistors and (b) the push current and pull current as a function of the output current.                        | 37 |

| 3.2  | (a) Common-emitter rail-to-rail class-AB output stage with<br>complementary bipolar transistors and (b) the ideal push current<br>and pull current as a function of the output current. | 38 |

| 3.3  | Rail-to-rail class-AB output stage with Darlington output transistors                                                                                                                   | 39 |

| 3.4  | Intermediate stage.                                                                                                                                                                     | 42 |

| 3.5  | Current reference circuit                                                                                                                                                               | 43 |

| 3.6  | Saturation protection circuit for a Darlington output stage                                                                                                                             | 44 |

| 3.7  | Current limiting circuit                                                                                                                                                                | 44 |

| 3.8  | Block diagram for a two-stage op amp with Miller compensation                                                                                                                           | 46 |

| 3.9  | Small-signal model of the two-stage op amp in Figure 3.8.                                                                                                                               | 46 |

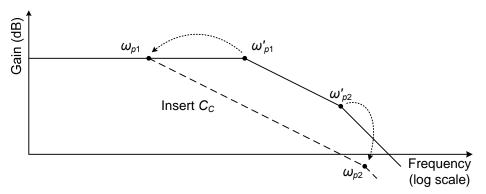

| 3.10 | Frequency response of the circuit in Figure 3.9 before and after inserting compensation capacitor                                                                                       | 48 |

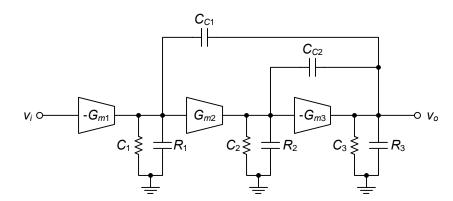

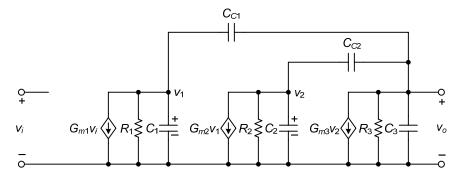

| 3.11 | Block diagram for a three-stage op amp<br>with nested-Miller compensation.                                                                                                              | 49 |

| 3.12 | Small-signal model of the three-stage op amp in Figure 3.11.                                                                                                                            | 50 |

| 4.1  | Rail-to-rail constant-Gm complementary input stage.                                                                                                                                     | 54 |

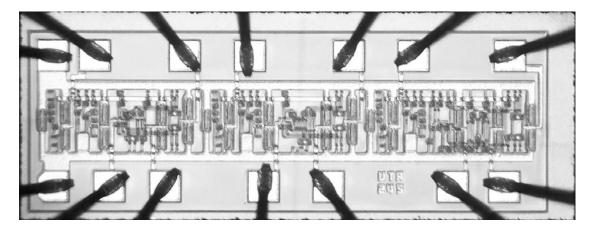

| 4.2  | Micrograph of the three different rail-to-rail input stages                                                                                                                             | 55 |

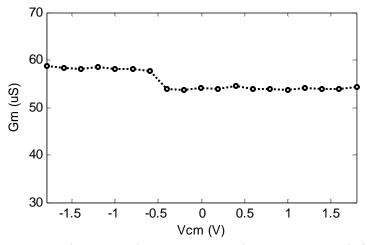

| 4.3  | Measured transconductance versus the common-mode input voltage                                                                                                                          | 56 |

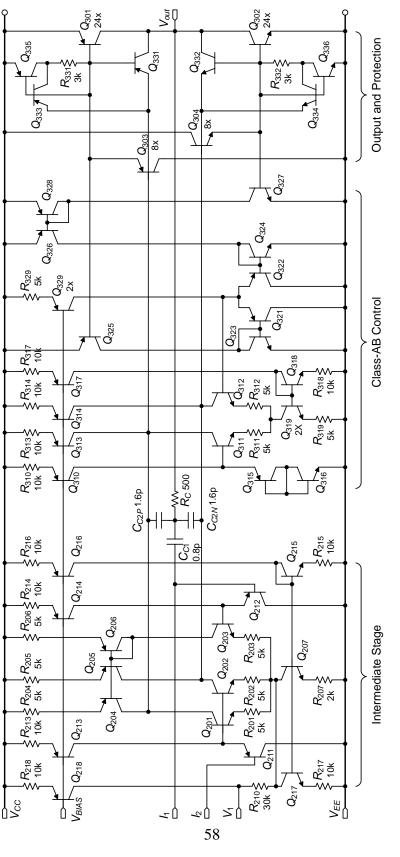

| 4.4  | Intermediate and output stages                                                                                                                                                          | 58 |

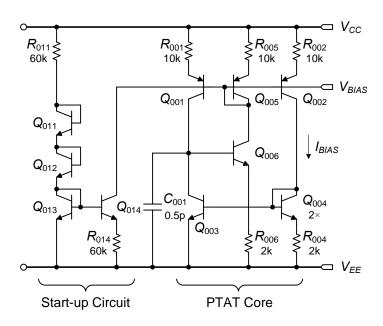

| 4.5  | Current reference with start-up circuit.                                                                                                                                                | 59 |

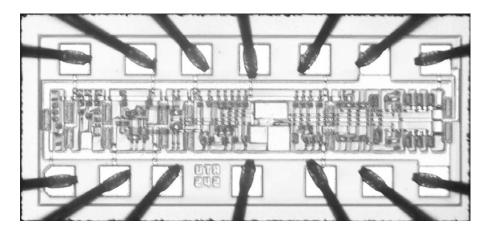

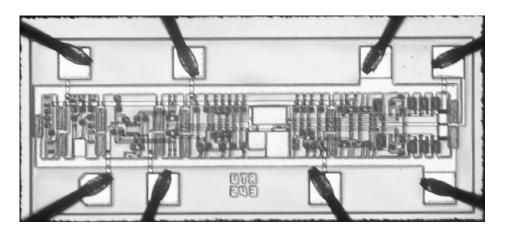

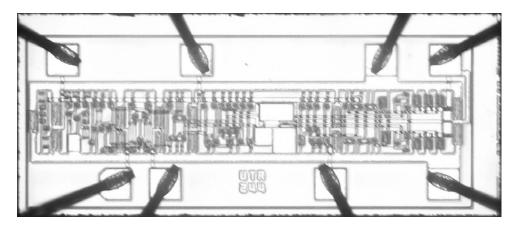

| 4.6  | Micrograph of UTA242.                                                                                                                                                                   | 59 |

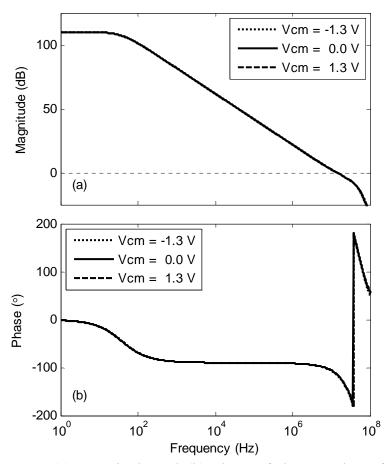

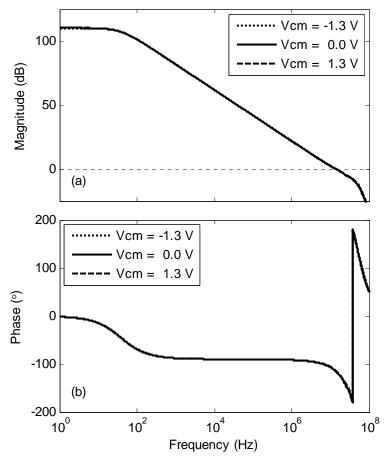

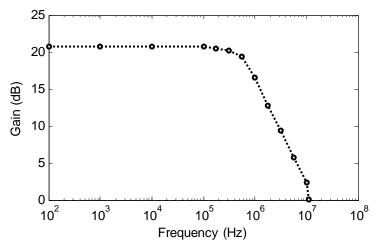

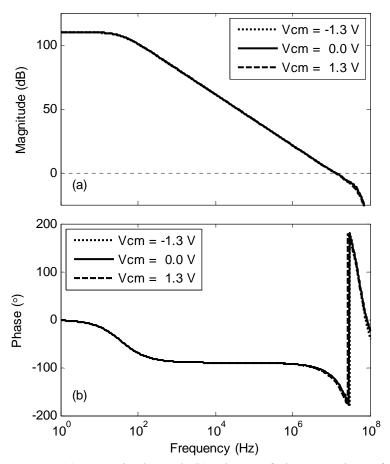

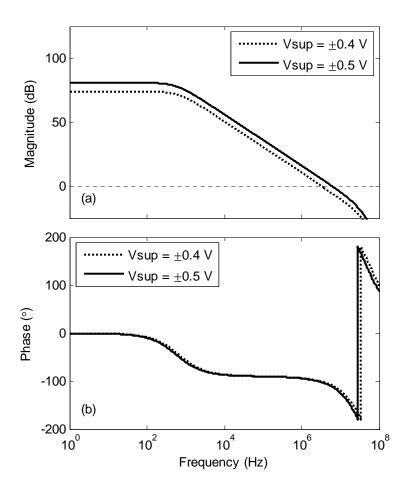

| 4.7  | (a) Magnitude and (b) phase of the open-loop frequency response<br>for UTA242 with different common-mode input voltages. | . 61 |

|------|--------------------------------------------------------------------------------------------------------------------------|------|

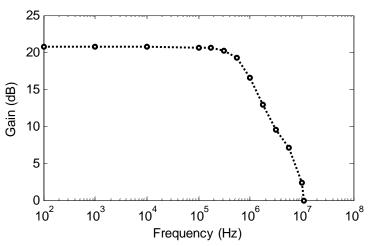

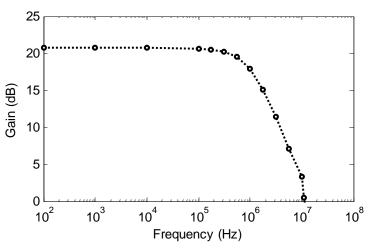

| 4.8  | Measured closed-loop gain of UTA242<br>with a non-inverting amplifier configuration                                      | . 61 |

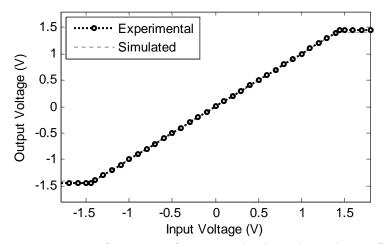

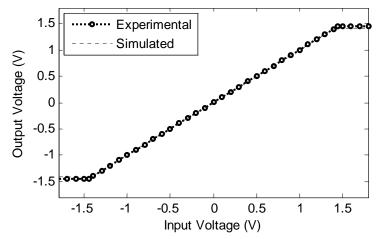

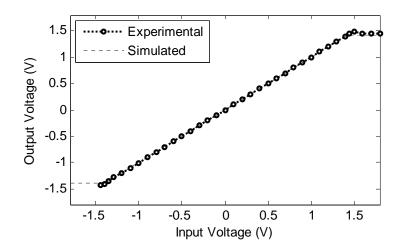

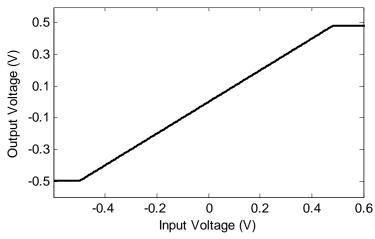

| 4.9  | DC transfer curve of UTA242 in the unity-gain configuration                                                              | . 62 |

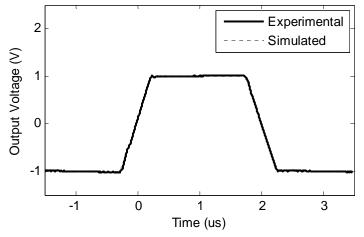

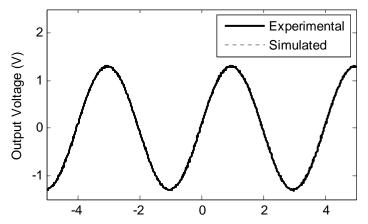

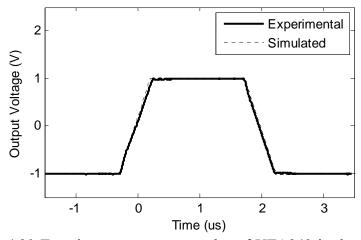

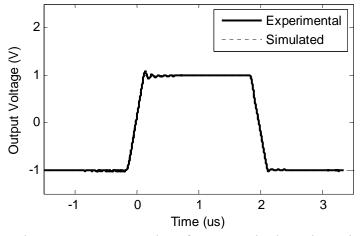

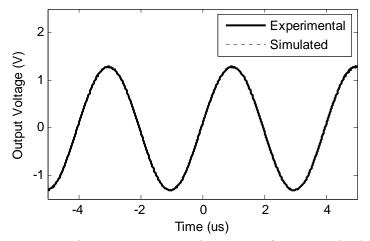

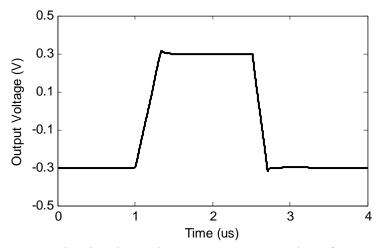

| 4.10 | Transient response to a pulse of UTA242 in the unity-gain configuration                                                  | . 62 |

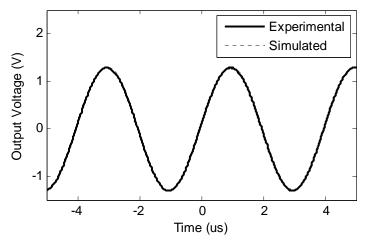

| 4.11 | Transient response to a sine wave of UTA242<br>in the unity-gain configuration                                           | . 63 |

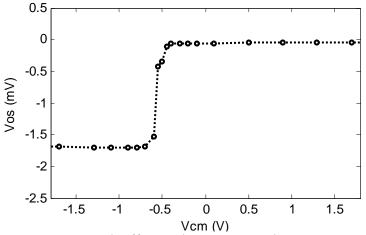

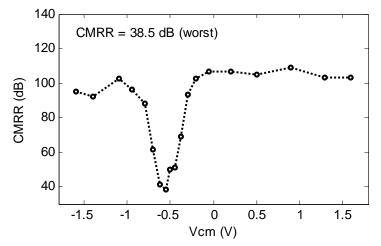

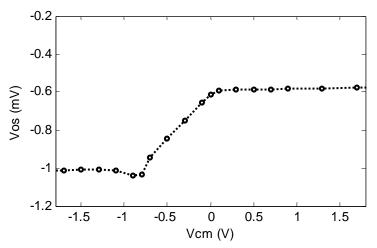

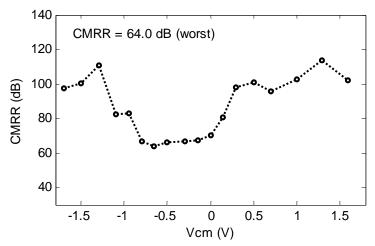

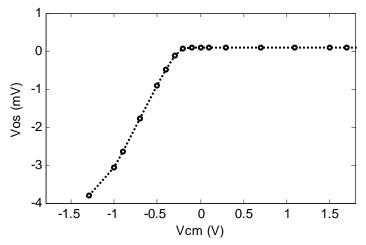

| 4.12 | Measured offset voltage versus the common-mode input voltage for UTA242.                                                 | . 63 |

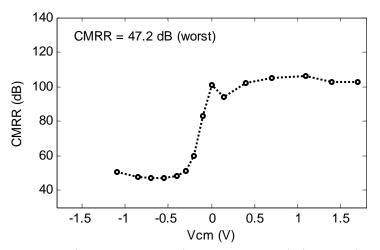

| 4.13 | Measured CMRR versus the common-monde input voltage for UTA242.                                                          | . 64 |

| 4.14 | Rail-to-rail constant-Gm complementary input stage<br>with improved CMRR                                                 | . 65 |

| 4.15 | Measured transconductance versus the common-mode input voltage                                                           | . 66 |

| 4.16 | Micrograph of UTA243.                                                                                                    | . 66 |

| 4.17 | (a) Magnitude and (b) phase of the open-loop frequency response<br>for UTA243 with different common-mode input voltages. | . 67 |

| 4.18 | Measured closed-loop gain of UTA243<br>in a non-inverting amplifier configuration                                        | . 68 |

| 4.19 | DC transfer curve of UTA243 in the unity-gain configuration                                                              | . 68 |

| 4.20 | Transient response to a pulse of UTA243 in the unity-gain configuration                                                  | . 69 |

| 4.21 | Transient response to a sine wave of UTA243 in the unity-gain configuration.                                             | . 69 |

| 4.22 | Measured offset voltage versus the common-mode input voltage for UTA243.                                                 | . 70 |

| 4.23 | Measured CMRR versus the common-mode input voltage for UTA243                                                            | . 70 |

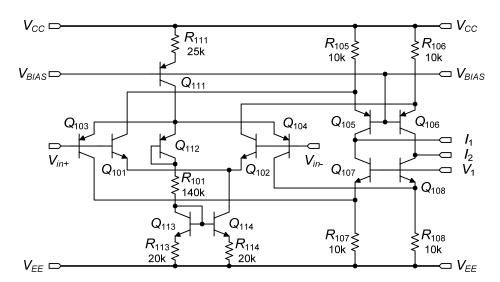

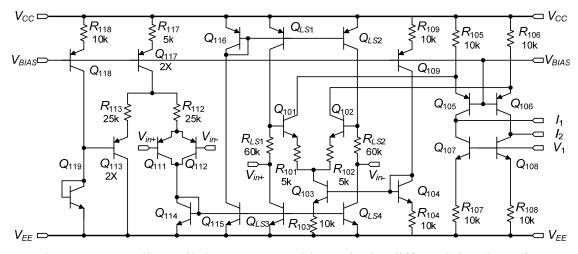

| 4.24 Rail-to-rail input stage with a single differential pair<br>and a common-mode adapter based on a pseudo-differential pair | 71   |

|--------------------------------------------------------------------------------------------------------------------------------|------|

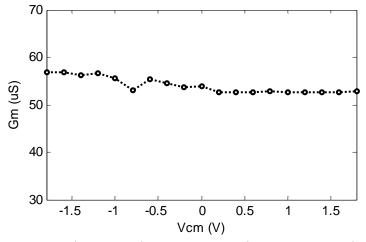

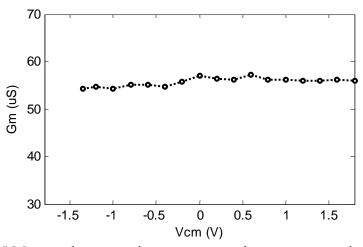

| 4.25 Measured transconductance versus the common-mode input voltage                                                            | 73   |

| 4.26 Micrograph of UTA244.                                                                                                     | 73   |

| 4.27 (a) Magnitude and (b) phase of the open-loop frequency response<br>for UTA244 with different common-mode input voltages.  | 74   |

| 4.28 Measured closed-loop gain of UTA244<br>in a non-inverting amplifier configuration                                         | 74   |

| 4.29 DC transfer curve of UTA244 in the unity-gain configuration                                                               | 75   |

| 4.30 Transient response to a pulse of UTA244 in the unity-gain configuration                                                   | 75   |

| 4.31 Transient response to a sine wave of UTA244<br>in the unity-gain configuration                                            | 76   |

| 4.32 Measured offset voltage versus the common-mode input voltage for UTA244.                                                  | 77   |

| 4.33 Measured CMRR versus the common-mode input voltage for UTA244                                                             | . 77 |

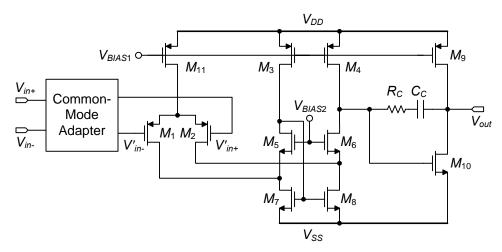

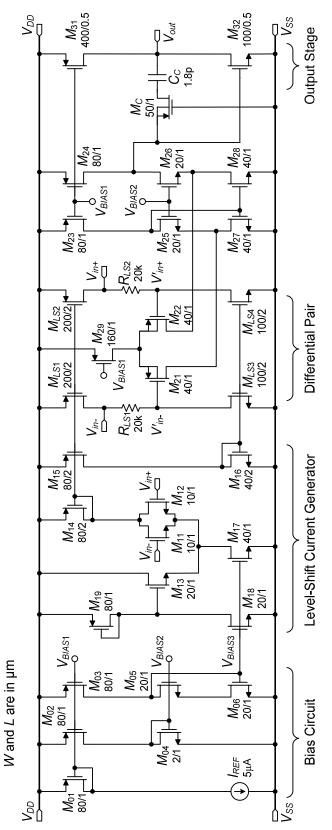

| 4.34 Complete circuit schematic of OPA004                                                                                      | 79   |

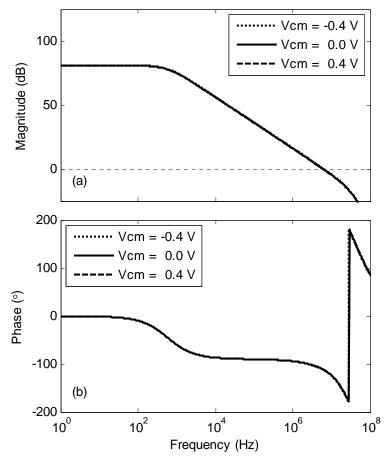

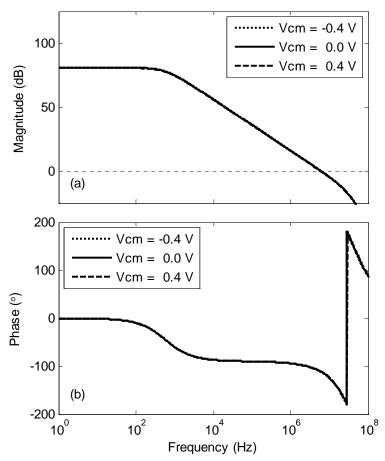

| 4.35 (a) Magnitude and (b) phase of the open-loop frequency response<br>for OPA004 with different common-mode input voltages.  | 80   |

| 4.36 (a) Magnitude and (b) phase of the open-loop frequency response<br>for OPA004 with different supply voltages.             | 81   |

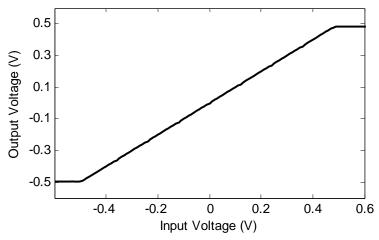

| 4.37 Simulated DC transfer curve of OPA004 in the unity-gain configuration                                                     | 82   |

| 4.38 Simulated transient response to a pulse of OPA004<br>in the unity-gain configuration.                                     | 82   |

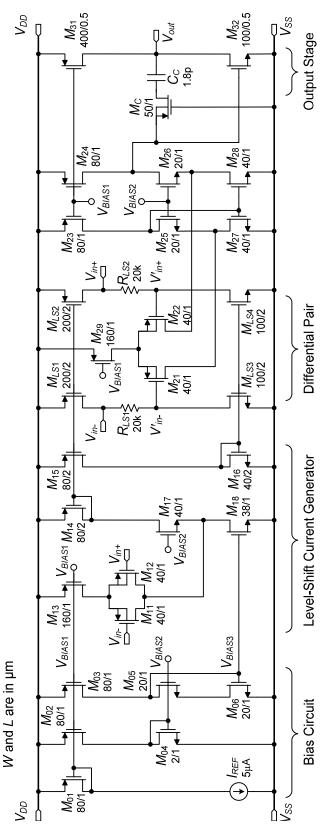

| 4.39 Complete circuit schematic of OPA005                                                                                      | 84   |

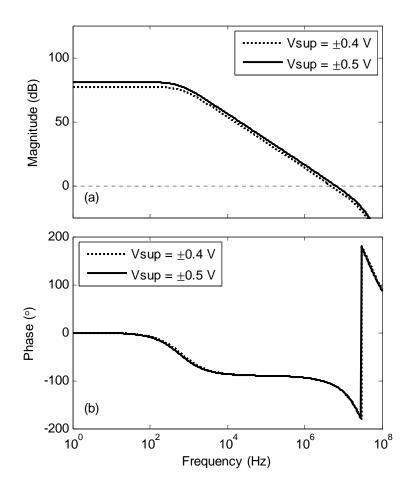

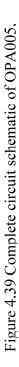

| 4.40 (a) Magnitude and (b) phase of the open-loop frequency response<br>for OPA005 with different common-mode input voltages   | 85   |

| 4.41 | (a) Magnitude and (b) phase of the open-loop frequency response<br>for OPA005 with different supply voltages.                                                                                              | 86 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.42 | 2 Simulated DC transfer curve of OPA005 in the unity-gain configuration                                                                                                                                    | 87 |

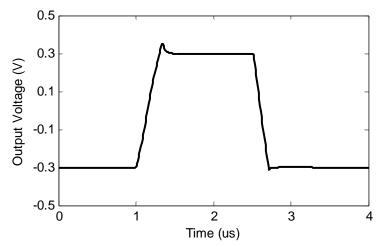

| 4.43 | Simulated transient response to a pulse of OPA005<br>in the unity-gain configuration                                                                                                                       | 87 |

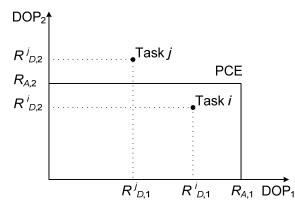

| 5.1  | Representation of "success" and "fail" of a system<br>in two-dimensional idealized system-task interface                                                                                                   | 91 |

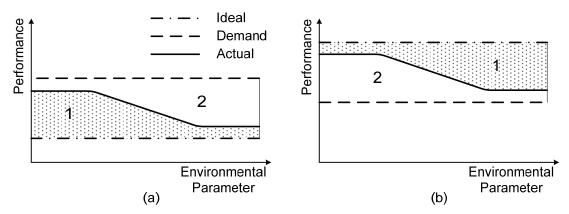

| 5.2  | Performance versus an environmental parameter when task demands are<br>met at all operating points. (a) Performance is the-lower-the-better case,<br>and (b) performance is the-higher-the-better case     | 92 |

| 5.3  | Performance versus an environmental parameter when task demands are<br>not met at all operating points. (a) Performance is the-lower-the-better<br>case, and (b) performance is the-higher-the-better case | 92 |

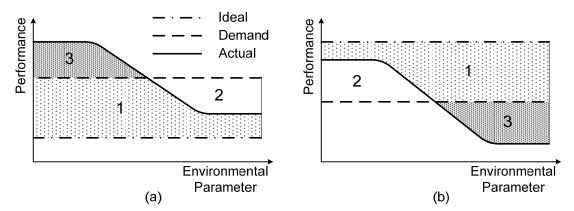

| 5.4  | Ideal, task demand, and actual performance of the offset voltages for (a) UTA242, (b) UTA243, and (c) UTA244.                                                                                              | 97 |

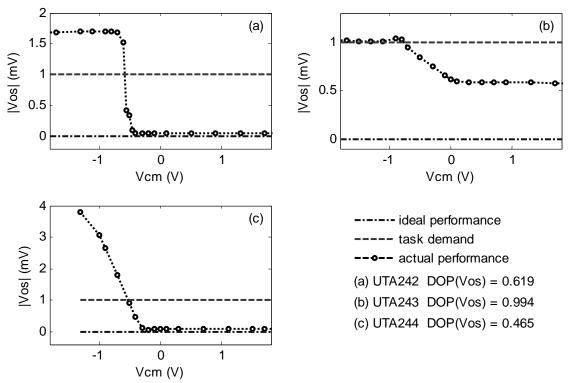

| 5.5  | Ideal, task demand, and actual performance of the CMRR for (a) UTA242, (b) UTA243, and (c) UTA244.                                                                                                         | 98 |

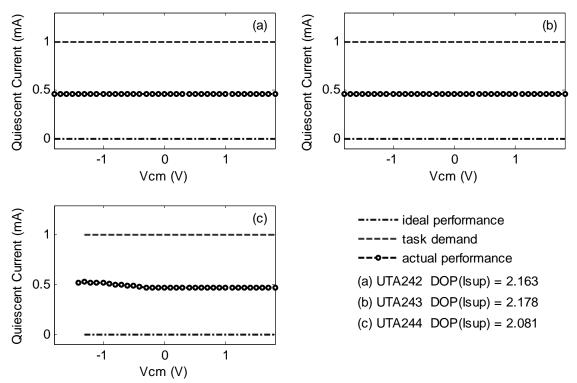

| 5.6  | Ideal, task demand, and actual performance of the quiescent supply current for (a) UTA242, (b) UTA243, and (c) UTA244                                                                                      | 99 |

# LIST OF TABLES

| Table |                                      | Page  |

|-------|--------------------------------------|-------|

| 4.1   | Performance Summary of UTA242.       | . 64  |

| 4.2   | Performance Summary of UTA243.       | . 71  |

| 4.3   | Performance Summary of UTA244.       | . 77  |

| 4.4   | Performance Summary of OPA004.       | . 83  |

| 4.5   | Performance Summary of OPA005.       | . 87  |

| 5.1   | CMIR and the Corresponding DOP.      | . 95  |

| 5.2   | Slew Rate and the Corresponding DOP. | . 95  |

| 5.3   | PSRR and the Corresponding DOP       | . 96  |

| 5.4   | Functionality Comparison of Op Amps. | . 100 |

## CHAPTER 1

#### INTRODUCTION

The operational amplifier (op amp) was originally designed to perform mathematical operations like addition, subtraction, integration, and differentiation. However, the op amp has become one of the most versatile and important building blocks in analog integrated circuit design. It has numerous applications such as active filters, buffers, digital-to-analog converters, analog-to-digital converters, audio amplifiers, voltage regulator, and so on [1-7].

#### 1.1 Background and Motivation

There is a trend toward lower power-supply voltage for integrated circuits [8]. Why low supply voltage? [4]. First, due to the scaling down, the integrated devices become smaller and smaller. A component with a smaller dimension is subjected to breakdown at a lower voltage, so it requires low supply voltage for device reliability. Second, it is due to the demand of battery-powered portable systems. For one single regular battery cell, the voltage is about 1.5 volts. The third reason is for low power consumption. For digital circuits, a low supply voltage always means low power consumption. It is not always true for analog circuits. Usually, in a system, the analog circuit is only a small part compared to the digital circuit part. Thus the lower supply voltage means the lower power consumption for the overall system.

With a lower supply voltage, the common-mode input range (CMIR) and the output voltage swing range of op amps are always reduced. In order to obtain a high signal-to-noise ratio and a large dynamic range, the output signal needs to be as large as possible [2]. The largest output signal swing is from the negative power-supply rail to the positive power-supply rail, i.e., rail-to-rail. This is true for either non-inverting gain amplifiers.

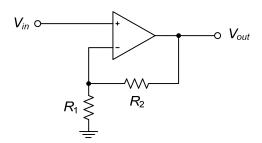

Figure 1.1 shows an inverting gain amplifier configuration. Generally, the openloop gain of an op amp is very high, so the voltages at the two input terminals are forced to have nearly the same value. This value or more precisely the average of the voltages at the two inputs is called the common-mode input voltage [9]. In this configuration, the non-inverting terminal is biased at a fixed voltage, so the requirement for the CMIR of the op amp in an inverting gain amplifier configuration is not high.

Figure 1.1 Inverting gain amplifier configuration.

Figure 1.2 shows a non-inverting gain amplifier configuration. The commonmode voltage at the input terminals of the op amp changes with the changing of the input signal voltage. If the input voltage swing is large, then requirement of the CMIR of the op amp in a non-inverting gain amplifier configuration is high.

Figure 1.2 Non-inverting gain amplifier configuration.

For applications like a voltage buffer, the large common-mode input voltage range and output voltage swing are preferred. The best CMIR and output swing are from rail to rail. An output stage with a rail-to-rail swing is relatively easy to design with class-A or class-AB topology [10]. The key problem is to design a rail-to-rail input stage with constant transconductance over the CMIR.

For rail-to-rail op amps, there are many different kinds of input stages and output stages [3, 11-15]. For example, the rail-to-rail input stage can have complementary differential pairs or a single differential pair with a common-mode adapter. One topology may be good at some aspects of performance but poor at others. The question is "which op amp is the best in overall performance?" The General System Performance Theory (GSPT) [16-18] is a systematic method for system performance analysis. The GSPT can be used to compare the performance of op amps and obtain a single-valued figure of merit.

#### 1.2 Organization of the Dissertation

This dissertation is divided into six chapters. Following this introduction, the design of rail-to-rail input stages is described in Chapter 2. Two types of rail-to-rail input stages are discussed. The first type of input stages use complementary differential

pairs, and the second type of input stages use a single differential pair with a commonmode adapter. In this chapter, a rail-to-rail bipolar complementary input stage with improved CMRR is presented, and two rail-to-rail input stages with a single differential pair and a common-mode adapter are designed. Two new common-mode adapters are developed. The first common-mode adapter is based on a pseudo-differential pair, and the second one is based on current subtraction.

Other circuit parts needed to complete the design of op amps are discussed in Chapter 3. It includes the output stage, the intermediate stage, and the output protection circuit. The frequency compensation for stability is also discussed in this chapter.

In Chapter 4, the overall operational amplifier circuits are discussed. Three different three-stage bipolar and two different two-stage CMOS rail-to-rail input and output op amps are designed. The simulation results and chip testing results are given in this chapter.

In Chapter 5, the General System Performance Theory is applied on the functionality analysis and comparison of the designed three bipolar rail-to-rail op amps.

Finally, the conclusion and future work are given in Chapter 6.

# CHAPTER 2

# INPUT STAGE

The task of the input stage of an op amp is to amplify the differential-mode input signals but to reject the common-mode input signals. One important specification of the input stage is the common-mode input range (CMIR). The CMIR is defined as the valid range of the common-mode input voltage that maintains the normal operation of the input stage. Other important specifications of an input stage are the input offset voltage, common-mode rejection ratio, and input referred noise. To some degree, the input stage also determines the gain-bandwidth product, phase margin, and slew rate [19].

In this chapter, rail-to-rail input stages are discussed. Section 2.1 describes differential pairs for input stages. Section 2.2 discusses rail-to-rail input stages with complimentary differential pairs. Section 2.3 discusses rail-to-rail input stages with a single differential pair and a common-mode adapter.

#### 2.1 Differential Pair

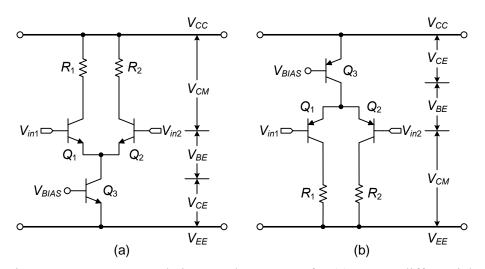

The differential pair is commonly used in the input stage of op amps. It can be either an n-type or a p-type differential pair as shown in Figure 2.1 and Figure 2.2.

Figure 2.1(a) shows an npn bipolar differential pair. When the common-mode voltage is too high, both  $Q_1$  and  $Q_2$  go to the saturation region; when the common-mode

voltage is too low,  $Q_3$  goes into the saturation region. The upper limit of the CMIR,  $V_{CM(\max)}$ , is the maximum common-mode input voltage to keep  $Q_1$  and  $Q_2$  in the forward active region. The condition to keep  $Q_1$  and  $Q_2$  in the forward active region can be expressed as

$$V_{CB} + V_{BE} = V_{CE} \ge V_{CE(sat)} \Longrightarrow V_{CB} \ge V_{CE(sat)} - V_{BE}$$

(2.1)

where  $V_{CE(\text{sat})}$  is the saturation voltage for  $Q_1$  and  $Q_2$ , which is the minimum collectoremitter voltage to keep  $Q_1$  and  $Q_2$  in the forward active region. Assuming that the voltage across  $R_1$  or  $R_2$  is  $V_{R1,2}$ , then

$$V_{CM(\max)} = V_{CC} + V_{BE} - V_{CE(\operatorname{sat})} - V_{R1,2}$$

(2.2)

where  $V_{CC}$  is the positive power-supply voltage. With proper values of resistors  $R_1$  and  $R_2$ ,  $V_{CM(\text{max})}$  can exceeds  $V_{CC}$  by  $V_{BE} - V_{CE(\text{sat})} - V_{R1,2}$ . The lower limit of the CMIR,  $V_{CM(\text{min})}$ , is the minimum input voltage to keep  $Q_1$ ,  $Q_2$ , and  $Q_3$  in the forward active region. So it must be  $V_{BE}$  of  $Q_1$  and  $Q_2$  plus  $V_{CE(\text{sat})}$  of  $Q_3$  above the negative power-power supply voltage,  $V_{EE}$ . It can be express as

$$V_{CM(\min)} = V_{EE} + V_{BE} + V_{CE(\text{sat})}$$

(2.3)

From (2.2) and (2.3), the CMIR of the npn differential pair can be represented as

$$V_{EE} + V_{BE} + V_{CE(sat)} \le V_{CM} \le V_{CC} + V_{BE} - V_{CE(sat)} - V_{R1,2}$$

(2.4)

Figure 2.1(b) shows a pnp bipolar differential pair. Similarly, the CMIR can be represented as

$$V_{EE} - V_{BE} + V_{CE(sat)} + V_{R1,2} \le V_{CM} \le V_{CC} - V_{BE} - V_{CE(sat)}$$

(2.5)

The common-mode input voltage cannot reach  $V_{CC}$ . The lower limit of the commonmode voltage can exceed  $V_{EE}$  by  $V_{BE} - V_{CE(sat)} - V_{R1,2}$ .

Figure 2.1 Common-mode input voltage range for (a) an npn differential pair and (b) a pnp differential pair.

CMOS differential pairs are shown in Figure 2.2. The CMIR for CMOS differential pairs are similar to the bipolar counterparts. For the NMOS differential pair in Figure 2.2(a), the CMIR is given by

$$V_{SS} + V_{GS} + V_{DS(sat)} < V_{CM} < V_{DD} + V_{TH} - V_{R1,2}$$

(2.6)

where  $V_{TH}$  is the threshold voltage of the MOS transistor, and  $V_{DS(sat)}$  is the saturation voltage. For the PMOS differential pair shown in Figure 2.2(b), the CMIR is given by

$$V_{SS} - V_{TH} + V_{R1,2} < V_{CM} < V_{DD} - V_{GS} - V_{DS(sat)}$$

(2.7)

In Figure 2.1 and Figure 2.2, the loads for the differential pair are resistors. They could be active loads [20]. For the active load case, the CMIR of the differential pair is similar.

Figure 2.2 Common-mode input voltage range for (a) an NMOS differential pair and (b) a PMOS differential pair.

## 2.2 Rail-to-Rail Input Stage with Complementary Differential Pairs

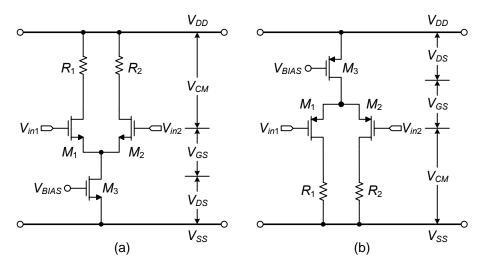

As shown in previous section, for a single differential pair, the common-mode input voltage cannot be rail-to-rail. One popular way to implement a rail-to-rail input stage is to use complementary differential pairs by placing a p-type differential pair and an n-type pair in parallel [3, 11], which is shown in Figure 2.3 and Figure 2.4.

### 2.2.1 Simple Complementary Input Stage

By placing an n-type differential pair and a p-type differential pair in parallel [3, 11], when common-mode voltage is high, the n-type pair conducts, and when common-mode voltage is low, p-type pair conducts.

Figure 2.3 shows a bipolar rail-to-rail complementary input stage; Figure 2.4 shows a CMOS rail-to-rail complementary input stage. In Figure 2.3 and Figure 2.4, the right-hand part is the current summing circuit [11]. The folded cascode transistors sum

the n-type and p-type differential pair currents into one output current.  $V_{BLAS}$  provides a bias voltage for  $Q_5$  and  $Q_6$ .

Figure 2.3 Bipolar rail-to-rail complementary input stage.

For the circuit in Figure 2.3, in order to obtain a rail-to-rail common-mode input range, at least one of the differential pairs should conduct for any common-mode input voltage. To avoid a forbidden voltage range in the middle between the negative and positive power-supply rails, the supply voltage should have a minimum value [3, 21] of

$$V_{SUP(\min)} = 2V_{BE} + 2V_{CE(sat)}$$

(2.8)

For the CMOS rail-to-rail input stage with complementary differential pairs as shown in Figure 2.4, the minimum supply voltage is

$$V_{SUP(\min)} = 2V_{GS} + 2V_{DS(\text{sat})}$$

(2.9)

A drawback of the simple complementary input stage in Figure 2.3 or Figure 2.4 is that the transconductance,  $G_m$ , varies as the common-mode input voltage changes. In

Chapter 3, it will be shown that the non-constant- $G_m$  input stage impedes an optimal frequency compensation and introduces distortion [11, 22, 23].

Figure 2.4 CMOS rail-to-rail complementary input stage.

Figure 2.5 shows the simulation result of the normalized tail current for the npn and pnp pairs over the common-mode input range of the input stage in Figure 2.3. The bipolar transistor SPICE models [24] for the simulation are given in Appendix A. Because the current through the differential pairs and the total transconductance of the input stage is a function of  $I_{TAIL1}$  and  $I_{TAIL2}$ , the simulated results are normalized [25]. Figure 2.5 shows when the  $V_{CM}$  is low, the pnp pair is on, the npn pair is off, and the tail current through the npn pair is zero; when the  $V_{CM}$  is high, the npn pair is on, the pnp pair is off, and the tail current through the npn pair is zero; when the  $V_{CM}$  is in the middle of the power-supply rails, both npn and pnp pairs are on, and the transconductance of the input stage doubles in this range, which is shown in Figure 2.6.

Figure 2.5 Normalized tail current versus the common-mode input voltage for pnp and npn pairs in the input stage of Figure 2.3.

Figure 2.6 Normalized transconductance versus the common-mode input voltage for the input stage of Figure 2.3.

# 2.2.2 Constant-G<sub>m</sub> Complementary Input Stage

In the saturation region, the transconductance of a MOS transistor is proportional to the square root of the drain current. It can be expressed as

$$g_m = \sqrt{2k' \left(\frac{W}{L}\right) I_D}$$

(2.10)

where k' is the transconductance parameters [20] for the MOS transistor, which equals the product of the carrier mobility and the oxide capacitance density; W/L is the channel width to length ratio;  $I_D$  is the drain current.

The constant transconductance of a CMOS complementary input stage is realized by developing a bias circuit, which produces the tail current  $I_n$  for the NMOS pair and the tail current  $I_p$  for the PMOS pair, so that the total transconductance is constant over the entire common-mode input range. It can be expressed as

$$\sqrt{2k_n'\left(\frac{W}{L}\right)_n I_n} + \sqrt{2k_p'\left(\frac{W}{L}\right)_p I_p} = \text{constant}$$

(2.11)

where  $k'_n$  and  $k'_p$  are the transconductance parameters for the NMOS and PMOS transistors, respectively;  $(W/L)_n$  and  $(W/L)_p$  are the channel width to length ratios for the NMOS and PMOS transistors, respectively.

There are many ways to implement CMOS rail-to-rail constant- $G_m$  complementary input stages [10, 12, 21, 25-30]. In this section, bipolar rail-to-rail constant- $G_m$  complementary input stages will be discussed in detail. For the bipolar technology, the transconductance of a transistor is proportional to the collector current [20], which can be described as

$$g_m = \frac{I_C}{V_T} \tag{2.12}$$

where  $I_C$  is the collector current, and  $V_T$  is the thermal voltage. A bipolar constant- $G_m$  complementary input stage can be realized by keeping the sum of the tail current

through the npn pair,  $I_{npn}$ , and the tail current through the pnp pair,  $I_{pnp}$ , constant. It can be expressed as

$$I_{non} + I_{pnp} = \text{constant}$$

(2.13)

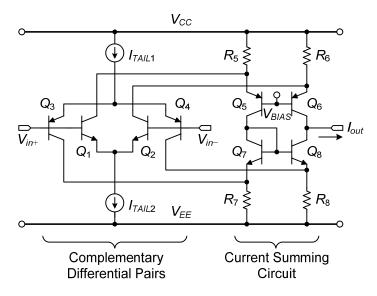

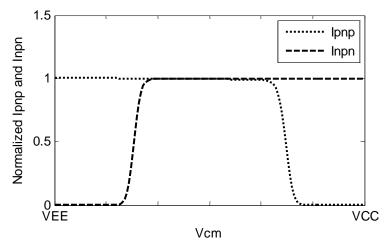

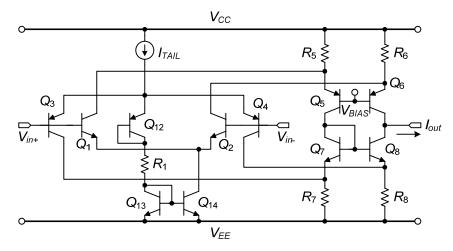

A realization of a bipolar constant- $G_m$  complementary input stage is shown in Figure 2.7 [11].  $V_{REF}$  is used to set the base voltage of  $Q_{12}$ ,  $V_{B12}$ , i.e., to set the base voltage of  $Q_{12}$  at  $V_{EE} + V_{REF}$ . The npn differential pair,  $Q_1$  and  $Q_2$ , is normally activated by the current source  $I_{TAIL}$  via  $Q_{12}$  and the current mirror,  $Q_{13}$  and  $Q_{14}$ , while the pnp differential pair is not operating. When  $V_{CM}$  decreases through  $V_{B12}$ , the emitter current is gradually steered from the emitter of  $Q_{12}$  to the pnp pair,  $Q_3$  and  $Q_4$ , removing current from the npn pair. A turn over between 10 to 90 percent of the current takes place in a voltage turnover range of about 120 mV [11], centered at  $V_{B12}$ . The total current through the npn and pnp differential pairs is  $I_{TAIL}$ . Since the total current is constant, the transconductance of the combination of the pnp and npn differential pairs is constant.

Figure 2.7 Rail-to-rail constant- $G_m$  complementary input stage.

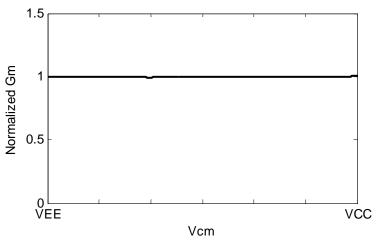

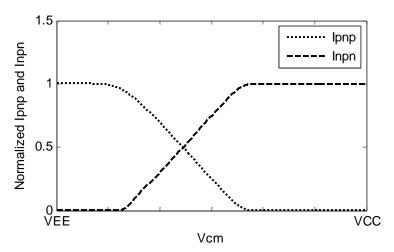

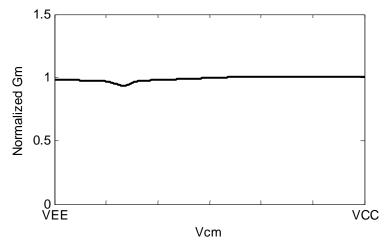

Figure 2.8 shows the simulation results of the normalized tail current of the npn and pnp pairs. When  $V_{CM}$  is a little bit smaller than base voltage of  $Q_{12}$ ,  $V_{B12}$ , the pnp pair conducts, and the npn pair is off; when the  $V_{CM}$  is a little bit greater than  $V_{B12}$ , the npn pair conducts, and the pnp pair is off. The normalized transconductance of the whole input stage is shown in Figure 2.9. The transconductance is almost constant over the common-mode input voltage range.

Figure 2.8 Normalized tail current versus the common-mode input voltage for pnp and npn pairs in the input stage of Figure 2.7.

Figure 2.9 Normalized transconductance versus the common-mode input voltage for the input stage of Figure 2.7.

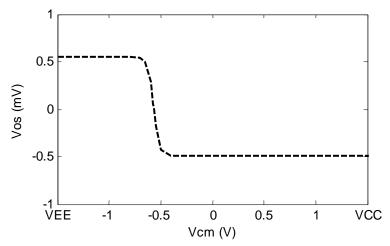

One disadvantage of this kind of input stage is that the offset voltage may vary for different common-mode input voltages, and this causes a low common-mode rejection ratio (CMRR) [31]. When the npn differential pair conducts, the offset voltage is shown to be [4]

$$V_{OS(npn)} = V_T \cdot \left( 2 \frac{\Delta R_{5,6}}{R_{5,6}} + \frac{\Delta R_{7,8}}{R_{7,8}} + \frac{\Delta I_{S1,2}}{I_{S1,2}} \right)$$

(2.14)

where  $\Delta R_{5,6}$  and  $R_{5,6}$  are the difference and average of  $R_5$  and  $R_6$ , respectively;  $\Delta R_{7,8}$  and  $R_{7,8}$  are the difference and the average of  $R_7$  and  $R_8$ , respectively;  $\Delta I_{S1,2}$  and  $I_{S1,2}$  are the difference and the average of the saturation current of  $Q_1$  and  $Q_2$ . Similarly, when the pnp differential pair conducts, the offset voltage is shown to be [4]

$$V_{OS(pnp)} = V_T \cdot \left(\frac{\Delta R_{5,6}}{R_{5,6}} + 2\frac{\Delta R_{7,8}}{R_{7,8}} + \frac{\Delta I_{S3,4}}{I_{S3,4}}\right)$$

(2.15)

where  $\Delta I_{S3,4}$  and  $I_{S3,4}$  are the difference and the average of the saturation current of  $Q_3$ and  $Q_4$ .

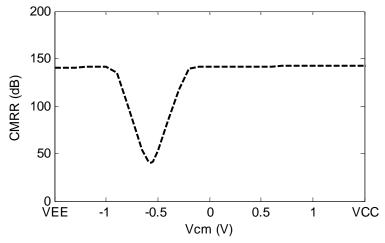

The CMRR is defined as the ratio of the differential-mode gain to the commonmode gain. From an application point of view, the CMRR can be considered as the change in the input offset voltage results from the change in the common-mode input voltage [20]. It can be expressed as

$$CMRR = \left(\frac{\Delta V_{OS}}{\Delta V_{CM}}\right)^{-1}$$

(2.16)

In the case of perfect match, the offset voltage and the variation of the offset voltages are very small over the common-mode voltage range. According to (2.16), the CMRR is

very high. In reality, the component mismatch is a statistical process, and the offset voltages may be different when the different pair conducts.

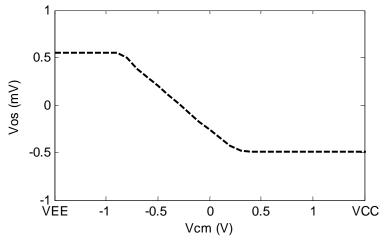

Figure 2.10 shows the simulated offset voltage over the common-mode input voltage range for the op amp of UTA242, which uses the input stage in Figure 2.7. The details of UTA242 will be discussed in Section 4.1. A 2% emitter error mismatch between the transistors of the differential pairs is assumed. When the pnp pair is on, the offset voltage is about 0.5 mV; when the npn pair is on, the offset voltage is about -0.5 mV.

Figure 2.10 Offset voltage versus the common-mode input voltage.

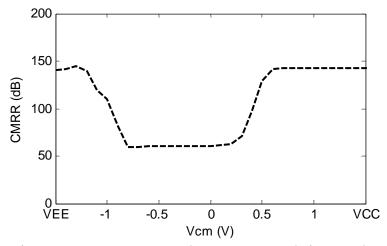

The simulated CMRR over the common-mode voltage range is shown in Figure 2.11. From this figure, it can be seen that the CMRR is very poor at the transition range between the pnp and npn pairs. The minimum value of the CMRR is about 40 dB which is at around the  $V_{REF}$  above  $V_{EE}$ . The poor CMRR dues to the short transition range and the large offset voltage difference between the pnp and npn pairs.

Figure 2.11 CMRR versus the common-mode input voltage.

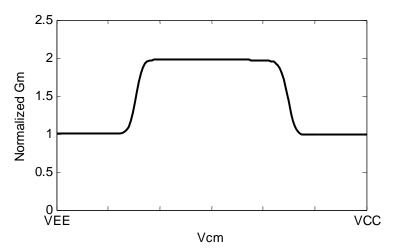

## 2.2.3 Constant-G<sub>m</sub> Complementary Input Stage with Improved CMRR

As mentioned in previous subsection, for a complementary input stage, the CMRR is poor in the transition region between the pnp and npn differential pairs. One solution to improve the CMRR is to increase the transition range [32-34]. Figure 2.12 shows a bipolar input stage with improved CMRR. The difference from the input stage in Figure 2.3 is that  $Q_{12}$  is diode connected, and a resistor  $R_1$  is inserted between  $Q_{12}$  and  $Q_{13}$ . Resistor  $R_1$  and transistor  $Q_{12}$  pull a current almost proportional to the common-mode input voltage and hence distribute  $I_{TAIL}$  over the two differential pairs. When the common-mode input voltage changes, the tail current of one pair gradually increases, and the tail current of the other differential pair gradually decreases. So it increase the transition region between the pnp pair to the npn pair. The offset voltage changes progressively, which improves the CMRR according to (2.16).

Figure 2.12 Rail-to-rail constant- $G_m$  complementary input stage with improved CMRR.

The simulated normalized tail current of the npn and pnp pairs is shown in Figure 2.13. It can be seen that the transition region between the pnp and npn pairs is increased compared to the results in Figure 2.8. The size of the transition range is determined by the value of the resistor  $R_1$ .

Figure 2.13 Normalized tail current versus the common-mode input voltage for pnp and npn pairs in the input stage of Figure 2.12.

The simulation result of the normalized transconductance of the whole input stage is shown in Figure 2.14. The transconductance is almost constant over the common-mode input voltage range. There is a small variation when transition is made between the npn and pnp pairs.

Figure 2.14 Normalized transconductance versus the common-mode input voltage for the input stage of Figure 2.12.

Figure 2.15 shows the simulated offset voltage over the common-mode voltage range for the op amp of UTA243, which uses the input stage in Figure 2.12. UTA243 will be discussed in Section 4.2. As in the previous section, a 2% emitter area mismatch between the transistors of the differential pair is assumed. The simulated CMRR over the common-mode input voltage range is shown in Figure 2.16. Figure 2.16 shows the minimum CMRR is about 60 dB, which is about 20 dB higher than the result of the input stage in Figure 2.7.

Figure 2.15 Offset voltage versus the common-mode input voltage.

Figure 2.16 CMRR versus the common-mode input voltage.

# 2.3 Rail-to-Rail Input Stage with a Single Differential Pair

For a CMOS complementary input stage, the required minimum supply voltage is  $2V_{GS} + 2V_{DS(sat)}$ , and for the bipolar counterpart, it is  $2V_{BE} + 2V_{CE(sat)}$ . When the supply voltage is less than the minimum voltage, there is a forbidden common-mode region [35], in which both n-type and p-type differential pairs are off.

For a CMOS complementary input stage, to obtain a constant transconductance over the common-mode input voltage range, the NMOS and PMOS transistors should be matched, which can be expressed as

$$k_n'\left(\frac{W}{L}\right)_n = k_p'\left(\frac{W}{L}\right)_p \tag{2.17}$$

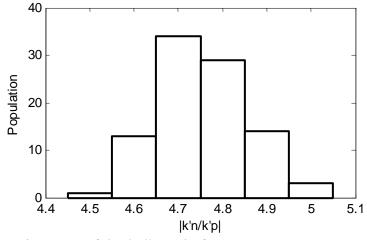

The matching can be achieved by sizing the NMOS and PMOS transistors properly [23] with the knowledge of  $k'_n/k'_p$  ratio. In general, the values of  $k'_n/k'_p$  ratio are different for different processes. Even for the same process, the ratio can change significantly from run to run [23]. Figure 2.17 shows the histogram of the  $k'_n/k'_p$  ratio for TSMC 0.18 µm CMOS technology [36]. It can be seen that the variation of  $k'_n/k'_p$  ratio is about 10%.

Figure 2.17 Histogram of the  $k'_n/k'_p$  ratio for TSMC 0.18 µm CMOS technology.

If only a single differential pair is used, the required minimum supply voltage is about  $V_{GS} + 2V_{DS(sat)}$ , which is one  $V_{GS}$  less than that of a complementary input stage. As long as the tail current through the differential pair does not change, the transconductance is constant over the common-mode input range.

For a conventional differential pair, as seen from Section 2.1, the commonmode input voltage range cannot be rail-to-rail. Some solutions have been proposed. A bulk-driven CMOS differential pair was proposed [14, 37]. The disadvantage of the bulk-driven CMOS differential pair is the small transconductance and poor high frequency response. In [38], a floating gate transistor input stage was proposed. The floating-gate transistor needs special process steps [39], which is costly. In [40], a local charge pump was designed to provide a higher local supply voltage for the input differential pair. Recently, common-mode adapters were proposed to extend the common-mode input range [13, 41, 42].

In this section, the operation of the common-mode adapter is described. Then two new input stages with common-mode adapters are introduced. The first commonmode adapter is based on a pseudo-differential pair, and the second one is based on current subtraction.

#### 2.3.1 Common-Mode Adapter

For an op amp with a PMOS differential pair input stage, the common-mode voltage cannot be near the positive power supply rail. Otherwise the tail current source transistor goes into the triode region. In order to solve this problem, a common-mode voltage adapter can be used. A two-stage op amp with a common-mode adapter [13] is shown in Figure 2.18. The common-mode adapter is placed in front of the input differential pair. The adapter circuit shifts the common-mode signal voltage, and keeps the differential-mode signal voltage unchanged.

Figure 2.18 Two-stage op amp with a common-mode adapter.

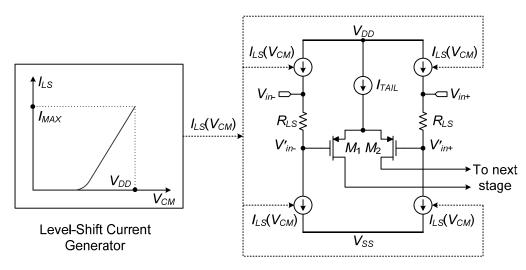

According to (2.7), the common-mode voltage at the gates of the differential pair  $M_1$  and  $M_2$ ,  $V'_{CM}$ , should be at least  $V_{GS} + V_{DS(sat)}$  below  $V_{DD}$ . The common-mode adapter is used to shift the common-mode input voltage to a lower value when the input common-mode input voltage,  $V_{CM}$ , is too high.

Figure 2.19 illustrates the operation of a common-mode adapter. The commonmode adapter is implemented by inserting level-shift resistors between the input terminals, which are labeled as  $V_{in+}$  and  $V_{in-}$ , and the gates of the differential pair of  $M_1$ and  $M_2$ , which are labeled as  $V'_{in+}$  and  $V'_{in-}$ , respectively. The current through the levelshift resistors is controlled by level-shift current sources,  $I_{LS}$ , which is a function of  $V_{CM}$ .  $I_{LS}$  should have the shape as in Figure 2.19.

From the common-mode adapter circuit in Figure 2.19, the relationship between the corresponding input voltages can be expressed as

$$V'_{in+} = V_{in+} - R_{LS}I_{LS}$$

(2.18)

$$V'_{in-} = V_{in-} - R_{LS} I_{LS}$$

(2.19)

Figure 2.19 Diagram of the operation of a common-mode adapter.

If the components are perfect matched, the differential-mode signal is unchanged, and the common-mode voltage is shifted to a lower value, which can be described by

$$V_{CM}' = (V_{in+}' + V_{in-}')/2 = V_{CM} - R_{LS}I_{LS}$$

(2.20)

$$V'_{dm} = V'_{in+} + V'_{in-} = V_{dm}$$

(2.21)

where  $V_{CM}$  and  $V_{dm}$  are the common-mode voltage and differential-mode voltage at the input terminals, respectively;  $V'_{CM}$  and  $V'_{dm}$  are the common-mode voltage and differential-mode at the gates of the differential pair, respectively;  $R_{LS}$  is value of the level-shift resistors;  $I_{LS}$  is the level-shift current, which is a function of  $V_{CM}$ .

For the PMOS differential pair in Figure 2.19, when  $V_{CM}$  is lower than  $V_{DD} - V_{GS} - V_{DS(sat)}$ , it is low enough for the PMOS differential pair to work even without a common-mode adapter. In this range, the common-mode adapter is not active, and almost no current goes through the level-shift resistors. When  $V_{CM}$  is higher than

$V_{DD} - V_{GS} - V_{DS(sat)}$ , the adapter circuit starts to be active, and the current  $I_{LS}$  starts to go through the level-shift resistors. If  $V_{CM}$  increases more, then more current goes through the level-shift resistors. It reaches the highest level-shift current  $I_{MAX}$  when  $V_{CM}$  is near the positive power supply rail. So the maximum common-mode voltage can be shifted is  $R_{LS} \cdot I_{MAX}$ . This value should be equal or greater than  $V_{GS} + V_{DS(sat)}$ .

For an ideal case, there is no mismatch between components, so the offset voltage is low, and the CMRR is high. For a practical case, a mismatch exists in the current sources or level-shift resistors between the left and the right branches. The extra offset voltage of  $\Delta(R_{LS}I_{LS})$  is introduced. Because  $I_{LS}$  is a strong function of the common-mode input voltage, according to (2.16), the CMRR may be very low when the adapter circuit is active. Another drawback of this input stage with adapter circuit is that the level-shift resisters introduce extra noise. The value  $R_{LS}$  and  $I_{MAX}$  must be chosen as the best tradeoff among the noise, die area, and power consumption.

In [13] and [42], the authors proposed two common-mode adapters based on common-mode feedback. With the feedback loop, it could cause stability problems. In this section, two new common-mode adapters for single differential pair input stages are presented. The first one is based on a pseudo-differential pair, and the second one is based on current subtraction.

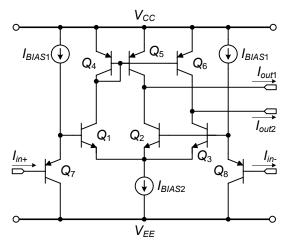

2.3.2 Input Stage with a Common-Mode Adapter Based on a Pseudo-Differential Pair

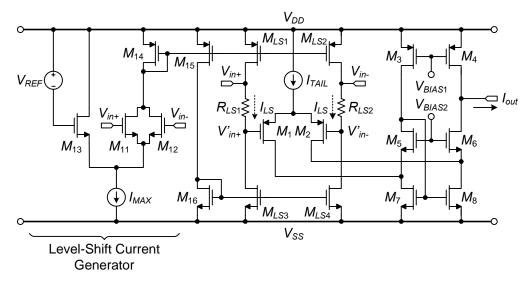

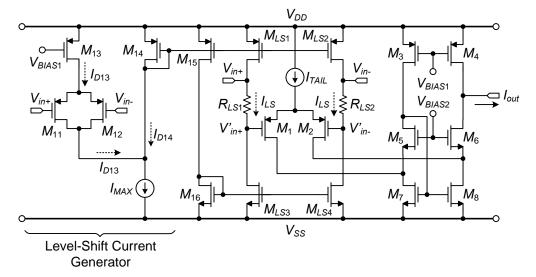

Figure 2.20 shows a rail-to-rail input stage with a new common-mode adapter [43].  $M_{LS1}$ ,  $M_{LS2}$ ,  $M_{LS3}$ , and  $M_{LS4}$  are the level-shift current sources.  $R_{LS1}$  and  $R_{LS2}$  are the

level-shift resistors, which have the same value.  $M_{15}$  and  $M_{16}$  are used to transfer the level-shift current to the NMOS level-shift current source transistors. The level-shift current is controlled by the level-shift current generator on the left part of Figure 2.20.

Figure 2.20 CMOS rail-to-rail input stage with a common-mode adapter based on a pseudo-differential pair.

The input signals  $V_{in+}$  and  $V_{in-}$  are applied on the gates of  $M_{11}$  and  $M_{12}$ . The sources of  $M_{11}$  and  $M_{12}$  are connected together, and the drains are also connected together. Because the open-loop gain of an op amp is usually very large, the differential-mode voltage,  $V_{dm}$ , is very small. So the effect of  $V_{dm}$  on the adapter circuit can be neglected. Thus  $M_{11}$  and  $M_{12}$  can be considered as one double-sized transistor. Transistor  $M_{13}$  and the combination of  $M_{11}$  and  $M_{12}$  form a differential pair structure. It is not a true differential pair, so this common-mode adapter is named as common-mode adapter based on a pseudo-differential pair. The tail current of the pseudo-differential pair is  $I_{MAX}$ . The gate voltage of  $M_{13}$ ,  $V_{G13}$ , is fixed by the voltage at the gate of the differential input voltage, the voltage at the gate of the

equivalent transistor of  $M_{11}$  and  $M_{12}$  is  $V_{CM}$ . Suppose  $M_{11}$  and  $M_{12}$  have the same size, and the size of  $M_{13}$  is W/L, which is twice the size of  $M_{11}$  or  $M_{12}$ , then the current through  $M_{11}$  and  $M_{12}$  can be approximately expressed as [20]

$$I(V_{CM}) = \frac{1}{2}I_{MAX} + \frac{k'_n}{4}\frac{W}{L}\left(V_{CM} - V_{G13}\right) \cdot \sqrt{\frac{4I_{MAX}}{k'_n(W/L)} - \left(V_{CM} - V_{G13}\right)^2}$$

(2.22)

If  $V_{CM}$  equals to  $V_{G13}$ , then the current though  $M_{14}$  is  $I_{MAX}/2$ , and the current is mirrored to the level-shift transistors; if  $V_{CM}$  is high then  $V_{G13}$ , then there is more current goes through  $M_{14}$ ; if  $V_{CM}$  is lower then  $V_{G13}$ , then there is less current goes through  $M_{14}$ . The W/L ratio of the transistors controls the slop of the curve [20].

It should be pointed out that the common-mode voltage cannot be higher than  $V_{DD} - V_{DS(sat)}$ . When  $V_{CM}$  is between  $V_{DD} - V_{DS(sat)}$  and  $V_{DD}$ , the level-shift current source transistors  $M_{LS1}$  and  $M_{LS2}$  operate in the triode region. So strictly speaking, it is not a true rail-to-rail input stage but quasi-rail-to-rail input stage [42].

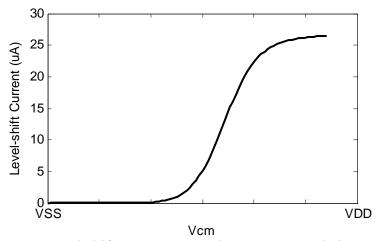

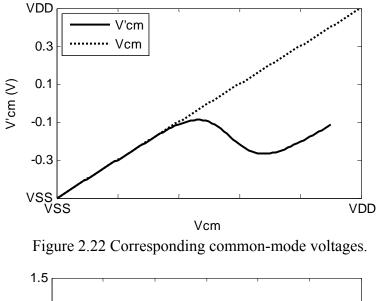

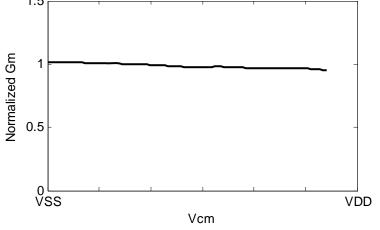

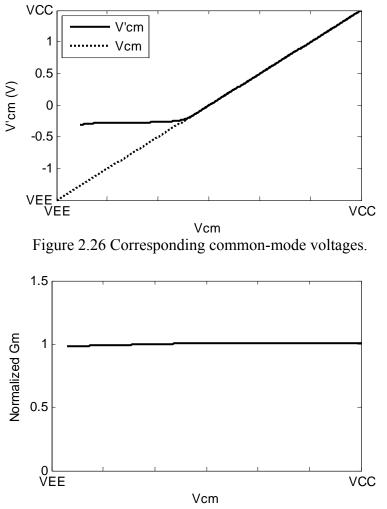

The level-shift current versus the common-mode input voltage is shown in Figure 2.21, which is similar to the curve in Figure 2.19. Figure 2.22 shows common-mode voltage on the gates of the differential pairs,  $V'_{CM}$ , for different  $V_{CM}$  at the input. This figure shows the common-mode voltage is adapted to a lower value when the  $V_{CM}$  is large. The values of the level-shift current and  $V'_{CM}$  in Figure 2.21 and Figure 2.22 may be different for different cases. The normalized transconductance of the input stage is shown in Figure 2.23. It shows the transconductance is almost constant over the common-mode voltage range. The common-mode input voltage can reach within  $V_{DS(sat)}$  of the positive power-supply rail,  $V_{DD}$ .

Figure 2.21 Level-shift current versus the common-mode input voltage.

Figure 2.23 Normalized transconductance versus the common-mode input voltage for the input stage of Figure 2.20.

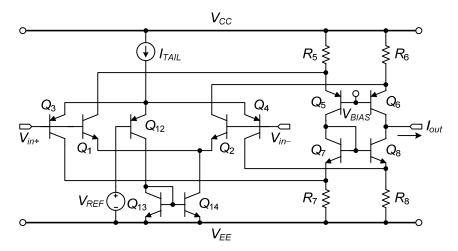

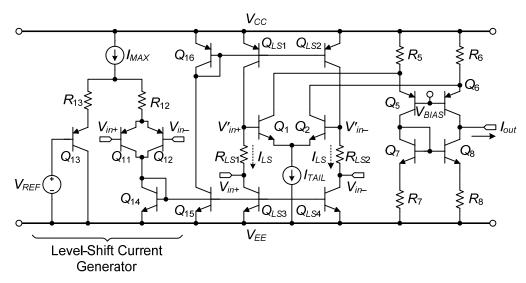

The input stage with a common-mode adapter in Figure 2.20 can also be transformed to a bipolar version, which is shown in Figure 2.24. In Figure 2.20, the PMOS differential pair is used. Here the npn differential pair is used. The operation of the input stage in Figure 2.24 is similar to the input stage in Figure 2.20. In Figure 2.24, the two emitter degeneration resistors  $R_{12}$  and  $R_{13}$  are used to increase the linearity of the level-shift current as a function of the common-mode input voltage.

Figure 2.24 Bipolar rail-to-rail input stage with a common-mode adapter based on a pseudo-differential pair.

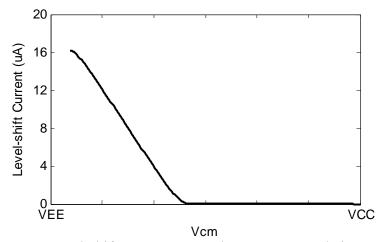

Figure 2.25 shows the level-shift current versus the common-mode input voltage. It shows that when the common-mode voltage is low, the level-shift current is high; when the common-mode voltage is high, the level-shift current is low. Figure 2.26 shows the common-mode voltage at the bases of the differential pair,  $V'_{CM}$ , versus the common-mode input voltage. Figure 2.27 shows the normalized transconductance of the input stage versus the common-mode input voltage.

Figure 2.25 Level-shift current versus the common-mode input voltage.

Figure 2.27 Normalized transconductance versus the common-mode input voltage for the input stage of Figure 2.24.

#### 2.2.3 Input Stage with a Common-Mode Adapter Based on Current Subtraction

Figure 2.28 shows a rail-to-rail input stage with a single differential pair and a new common-mode adapter based on current subtraction. In Figure 2.28, the sources of  $M_{11}$  and  $M_{12}$  are connected, and the drains are also connected together. The input voltages are also applied at the gates of  $M_{11}$  and  $M_{12}$ . The current through  $M_{11}$  and  $M_{12}$  are controlled by the current source transistor  $M_{13}$ , and the maximum current through  $M_{13}$  is  $I_{MAX}$  when it is working is the saturation region. The sum of the drain current of  $D_{13}$ ,  $I_{D13}$ , and the drain current of  $M_{14}$ ,  $I_{D14}$ , is  $I_{MAX}$ , i.e.,  $I_{D14}$  is the difference of  $I_{MAX}$  and  $I_{D13}$ . It can be expressed as

$$I_{D14} = I_{MAX} - I_{D13} \tag{2.23}$$

Figure 2.28 CMOS rail-to-rail input stage with a common-mode adapter based on current subtraction.

$I_{D14}$  is then mirrored to the level-shift currents mirrors. When the common-mode input voltage,  $V_{CM}$ , is lower than  $V_{DD} - V_{DS13(sat)} - V_{GS11}$ ,  $M_{13}$  is in saturation region.  $I_{D13}$  equals

$I_{MAX}$ . According to (2.23),  $I_{D14}$  is zero. So the level shift current,  $I_{LS}$ , is also zero. When  $V_{CM}$  increases from  $V_{DD} - V_{DS13(sat)} - V_{GS11}$  toward  $V_{DD}$ ,  $M_{13}$  starts going into triode region, and  $I_{D13}$  starts decreasing, so  $I_{D14}$  starts increasing until  $I_{D13}$  equals to zero. The minimum value of  $I_{D13}$  is zero, so the maximum value of  $I_{D14}$  is  $I_{MAX}$ . Because of the current subtraction operation, this common-mode adapter is named the common-mode adapter based on current subtraction.

Figure 2.29 shows the level-shift current versus the common-mode voltage. Figure 2.30 shows the common-mode input voltage at the gates of the differential pair,  $V'_{CM}$ , versus the common-mode input voltage. Figure 2.31 shows the normalized transconductance of the input stage versus the common-mode input voltage. The transconductance is almost constant over the input common-mode voltage.

This input stage can also be transformed to a bipolar version. The schematic of the bipolar input stage are not given here.

Figure 2.29 Level-shift current versus the common-mode input voltage.

Figure 2.30 Corresponding common-mode voltages.

Figure 2.31 Normalized transconductance versus the common-mode input voltage for the input stage of Figure 2.28.

## 2.4 Summary

Two types of rail-to-rail input stages have been discussed in this chapter. The first one is based on complementary differential pairs, and the second one is based on a single differential pair and a common-mode adapter. One disadvantage of complementary input stages is the required minimum supply voltage is about

$2V_{BE} + 2V_{CE(sat)}$  for bipolar technologies or  $2V_{GS} + 2V_{DS(sat)}$  for CMOS technologies. Another disadvantage is the CMRR is poor at the transition region between the p-type and n-type differential pairs. The CMRR was improved by means of increasing the transition region between the pnp and npn pairs. In this chapter, a bipolar constant- $G_m$ complementary input stage with improved CMRR was designed. The required minimum supply voltage for the input stage with a single differential pair is about  $V_{BE} + 2V_{CE(sat)}$  for bipolar technologies or  $V_{GS} + 2V_{DS(sat)}$  for CMOS technologies. The disadvantage of the input stage with single differential pair is that the common-mode adapter increases the power consumption, and introduces extra noise and offset voltage. Two different rail-to-rail input stages with a single differential pair and common-mode adapter were presented. Two new common-mode adapters were introduced. The first one is based on a pseudo- differential pair, and the second one is based on current subtraction.

# CHAPTER 3

## OTHER CIRCUIT PARTS AND FREQUENCY COMPENSATION

The design of the rail-to-rail input stages have been discussed in Chapter 2. An op amp can have only one gain stage. Usually a one-stage op amp does not have enough open-loop gain for typical applications. In order to obtain enough open-loop gain, two or more gain stages are required for an op amp. The rail-to-rail output stage is discussed in Section 3.1; the intermediate stage is discussed in Section 3.2; the current reference circuit is discussed in Section 3.3; the output protection circuit is discussed in Section 3.4. For two-stage or three-stage op amps, compensation circuits are needed for stability. The Miller compensation and nested-Miller compensation methods are discussed in Section 3.5.

#### 3.1 Output Stage

The purpose of the output stage is to deliver power into the load. The most important specifications of output stages are the output voltage swing range, power efficiency, and distortion. To obtain better power efficiency, a class-AB output stage should be used. The ideal output voltage swing is from rail to rail. To obtain a rail-torail output swing, the conventional emitter-follower or source-follower configuration is not suitable. The output transistors must be in a common-emitter or common-source configuration.

#### 3.1.1 Class-AB Output Stage

The voltage follower, common-emitter or common-source configuration, is the most popular class-AB biasing topology because of the simplicity, low output impedance, and good linearity. Figure 3.1(a) shows a voltage-follower class-AB output stage configuration with complementary bipolar transistors. In Figure 3.1(a),  $Q_1$ ,  $Q_2$ ,  $Q_3$ , and  $Q_4$  form a translinear loop [44]. It yields

$$V_{BE1} + V_{BE2} = V_{BE3} + V_{BE4} \tag{3.1}$$

Assuming that  $Q_1$ ,  $Q_2$ ,  $Q_3$ , and  $Q_4$  transistors have the same size, because of the logarithmic relationship between the base-emitter voltage and the collector current of a bipolar transistor, the product of the push and pull currents is constant. It can be expressed as

$$I_{push} \cdot I_{pull} = I_{BIAS}^2 \tag{3.2}$$

where  $I_{push}$  is the push current through the pnp output transistor  $Q_1$ , and  $I_{pull}$  is the pull current through the npn output transistor  $Q_2$ .

The load for the output stage is not shown in Figure 3.1(a). The output current is the difference between  $I_{push}$  and  $I_{pull}$ . The quiescent current,  $I_Q$ , is the current through the output transistors when the output current is zero. According to (3.2),  $I_Q$  equals to  $I_{BIAS}$ . The push current and pull current versus output current relationship is shown in Figure 3.1(b).

One drawback of the voltage follower class-AB bias scheme is the output voltage swing cannot be from rail to rail. The maximum output voltage is  $V_{BE} + V_{CE(sat)}$  below  $V_{CC}$ , and the minimum output voltage is  $V_{BE} + V_{CE(sat)}$  above  $V_{EE}$ . So the conventional voltage-follower configuration is not suitable for low voltage design. In order to have rail-to-rail output voltage swing, common-emitter configuration is often used, as shown in Figure 3.2(a).

Figure 3.1 (a) Voltage follower class-AB output stage with complementary bipolar transistors and (b) the push current and pull current as a function of the output current.

An efficient class-AB biasing must satisfy following four requirements [21, 45]: (a) the ratio of maximum current,  $I_{max}$ , to the quiescent current,  $I_Q$ , must be high for high efficiency; (b) the minimum current,  $I_{min}$ , should not be much smaller than the quiescent current to avoid high-frequency distortion; (c) the class-AB transition must be smooth to avoid low-frequency distortion; (d) The output transistors must be driven by a preceding stage directly without delay from the class-AB control circuit. Figure 3.2(b) shows the push current and pull current for an ideal class-AB biasing.

Figure 3.2 (a) Common-emitter rail-to-rail class-AB output stage with complementary bipolar transistors and (b) the ideal push current and pull current as a function of the output current.

#### 3.1.2 Rail-to-Rail Class-AB Output Stage

Both class-A and class-AB circuits can be used to implement rail-to-rail output stages [10]. The class-A output stage has good linearity, but poor current efficiency. A class-AB output stage is commonly used to obtain good current efficiency.

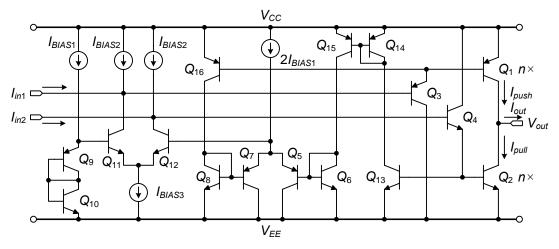

In order to obtain a rail-to-rail output voltage swing, a common-emitter or common-source output stage must be used. Many rail-to-rail class-AB output stage topologies have been proposed. They are classified into two categories – the feedforward class-AB output stage [28, 46, 47] and the feedback class-AB output stage [11, 25, 26, 45, 48]. In [48], the authors proposed a feedback-controlled class-AB rail-to-rail output stage. Figure 3.3 is a modified class-AB rail-to-rail output stage based on the output stage in [48].

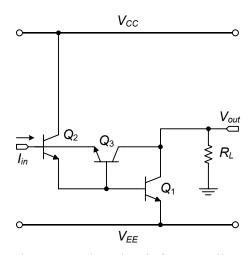

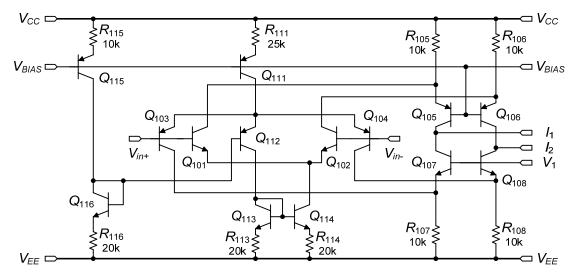

Figure 3.3 Rail-to-rail class-AB output stage with Darlington output transistors.

There are two inputs for this output stage, which drive the output Darlington pairs directly. They are in-phase signals, which have the same amplitude and polarity. In Figure 3.3,  $Q_1$  and  $Q_3$  are the pnp Darlington pair output transistors, and  $Q_2$  and  $Q_4$  are the npn Darlington pair output transistors. The Darlington topology is used to increase the gain [20]. The collector current of the pnp output transistor,  $I_{push}$ , is sensed by  $Q_{16}$ , and then transferred to  $Q_8$ . The collect current of npn output transistor,  $I_{puull}$ , is sensed by  $Q_{13}$ , and then transferred to  $Q_{14}$ ,  $Q_{15}$ , and  $Q_6$ .

$Q_{11}$  and  $Q_{12}$  form a differential pair, which compares the emitter voltage of  $Q_5$ and  $Q_7$  to the reference voltage of the two diode-connected transistors,  $Q_9$  and  $Q_{10}$ . If the voltages are unequal, a correction signal is steered to both Darlington pairs by the feedback amplifier  $Q_{11}$  and  $Q_{12}$ , until the two voltages are equal.  $Q_5$  and  $Q_7$  form a minimum selector [3, 21, 49]. Suppose npn output transistor  $Q_1$  is driven hard, the baseemitter voltage of  $Q_8$  is higher than the base-emitter voltage of  $Q_6$ . Then all the tail current  $2I_{BLAS1}$  flows to  $Q_5$ . So the  $Q_6$  base-emitter voltage is fixed by the differential feedback amplifier  $Q_{11}$  and  $Q_{12}$ . Then the collector current through  $Q_6$  is fixed, and the pull current is fixed at a nonzero value. In a similar way, if pnp output transistor  $Q_2$  is driven hard, the push current is fixed to a nonzero value.

The sizes of the output transistors are *n* times the size of the sensor transistors,  $Q_{13}, Q_{14}, Q_{15}, Q_6, Q_{16}$ , and  $Q_8$ , so the pull current is *n* times the collector current of  $Q_6$ , and the push current is *n* times the collector current of  $Q_8$ . It can be expressed as

$$I_{C6} = \frac{1}{n} I_{pull} \tag{3.3}$$

$$I_{C8} = \frac{1}{n} I_{push} \tag{3.4}$$

Transistors  $Q_5$ ,  $Q_6$ ,  $Q_7$ , and  $Q_8$  form a translinear loop, therefore

$$I_{C5} \cdot I_{C6} = I_{C7} \cdot I_{C8} \tag{3.5}$$

The tail current for the differential pair  $Q_5$  and  $Q_7$  is  $2I_{BLAS1}$ . It yields

$$I_{C5} + I_{C7} = 2I_{BIAS1} \tag{3.6}$$

Because of the differential feedback amplifier  $Q_{11}$  and  $Q_{12}$ , the sum of the base-emitter voltages of  $Q_9$  and  $Q_{10}$  is equal to the sum of the base emitter voltage  $Q_7$  and  $Q_8$ . So

$$I_{C7} \cdot I_{C8} = I_{C9} \cdot I_{C10} = I_{BIAS1}^{2}$$

(3.7)

From (3.3) through (3.7), we have

$$\frac{1}{I_{pull}} + \frac{1}{I_{push}} = \frac{2}{n \cdot I_{BIAS1}}$$

(3.8)

The quiescent current through the output transistors,  $I_Q$ , can be obtained by equaling  $I_{pull}$ and  $I_{push}$  in (3.8). It yields

$$I_{Q} = n \cdot I_{BIAS1} \tag{3.9}$$

The minimum value of  $I_{pull}$  and  $I_{push}$  can also be shown to be

$$I_{min} = \frac{1}{2} \cdot n \cdot I_{BIAS1} = \frac{1}{2} I_Q$$

(3.10)

Equation (3.8) can be rewritten as

$$\left(I_{push} - \frac{1}{2}I_{Q}\right) \cdot \left(I_{pull} - \frac{1}{2}I_{Q}\right) = \left(\frac{1}{2}I_{Q}\right)^{2} = \left(\frac{1}{2}n \cdot I_{BLAS1}\right)^{2}$$

(3.11)

The relationship among the push, pull, and output currents is similar to the curve in Figure 3.2(b).

One drawback of the feedback-controlled class-AB Darlington output stage is the minimum supply voltage is high. From the path of  $Q_1$ ,  $Q_3$ ,  $Q_{11}$ ,  $Q_9$ , and  $Q_{10}$ , it can be observed that the minimum supply voltage for this output stage is about  $3V_{BE} + V_{CE(sat)}$ .

#### 3.2 Intermediate Stage

So far, the input and output stages have been discussed. A two-stage op amp only has an input stage and an output stage. However, if a high open-loop gain is required, then an additional intermediate stage is needed. An extra stage may cause a stability problem. Thus it requires a more complicated compensation scheme.

Figure 3.4 shows a differential intermediate stage [4]. The purpose of this intermediate stage is to amplify the current signal. The inputs are differential signals, and the outputs are two in-phase signals, which are required by the output stage in Figure 3.3.  $Q_7$  and  $Q_8$  are in an emitter-follower configuration with no voltage gain but with current gain, which increases the overall op amp gain.

Figure 3.4 Intermediate stage.

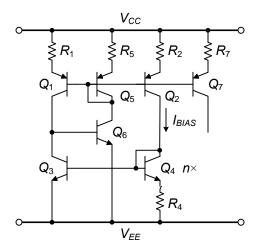

#### 3.3 Current Reference Circuit

A bias circuit is used as a reference current source for the biasing current of an op amp. The reference current source should be independent of the supply voltage. Figure 3.5 shows a current reference circuit [50].

In Figure 3.5,  $Q_1$  and  $Q_2$  are two identical current sources, which are controlled by a loop amplifier [50]. In this way, the equal bias conditions are maintained for different supply voltages, and the influence of the finite early voltage is eliminated. The emitter area ratio of  $Q_4$  to  $Q_3$  is *n*. From the above current reference configuration, the bias current [20] is given by

$$I_{BLAS} = \frac{V_T}{R_4} \ln\left(n\right) \tag{3.12}$$

where  $V_T$  is the thermal voltage. From (3.12), the bias current is independent of the supply voltage, and it is proportional to the absolute temperature. So it is called a proportional to absolute temperature (PTAT) current source.

Figure 3.5 Current reference circuit.

There are two possible stable operating points in this circuit. A start-up circuit is needed to avoid the zero current state. In Figure 3.5, the start-up circuit is not shown. The reference circuit with a start-up circuit will be discussed in Chapter 4.

#### 3.4 Output Protection Circuit

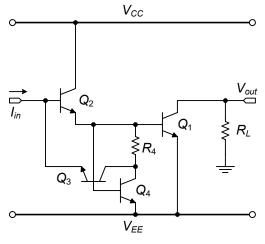

For a rail-to-rail output stage, the output transistors are very easy get into the saturation region. In order to avoid this, an output saturation protection circuit is needed. Figure 3.6 shows the npn half of a Darlington output stage,  $Q_1$  and  $Q_2$ , driving a load,  $R_L$  [51]. If a large current is drawn by  $R_L$ , then the collector-emitter voltage of  $Q_1$  is very small, and it gets into the saturate region. Heavy saturation of the output transistor should be avoided because it takes time to get rid of the charge stored in the base of the output transistor. In Figure 3.6, transistor  $Q_3$  is used to measure base-collector voltage of  $Q_1$ . When  $Q_1$  is in heavy saturation, the base-collector junction is forward biased, and  $Q_3$  is in the reverse active region. There is current that flows

through  $Q_3$ , which reduce the current driving  $Q_2$ . The ratio of the emitter areas of  $Q_1$  to the emitter area of  $Q_3$  controls the amount of saturation allowed.

Figure 3.6 Saturation protection circuit for a Darlington output stage.

If the output stage is driven hard, then there is large current that flows through the output transistor. It dissipates lots of power, which may destroy the op amp. In order to prevent this from happening, an output current limiting circuit is needed. Figure 3.7 is the current limiting circuit for a npn Darlington pair of the output stage [4, 51].

Figure 3.7 Current limiting circuit.

Transistor  $Q_4$  is used to sense the current through the output transistor  $Q_1$ . If  $Q_1$  is driven hard, then the current through  $Q_4$  will be large. Because of a voltage drop over  $R_4$ , it causes  $Q_4$  to go into the saturation region. Then  $Q_3$  goes into the reverse active region. Some current goes through  $Q_3$ , which reduces input current through  $Q_2$ . Therefore it prevents a further increase in the current through the output transistor.

## 3.5 Frequency Compensation

The input stage, intermediate stage, and output stage have been discussed so far. When the signal passes through an op amp, it causes phase lag. When the phase shift exceeds 180° at a certain frequency, the open-loop gain must drop below unity. Otherwise, the closed-loop system oscillates. Furthermore, a phase margin must be large enough to avoid a peaking in the frequency domain or overshooting in the time domain [52]. For every common-emitter or common-source stage, it introduces a dominant pole, and every pole causes a 90° phase shift. If there are two or more dominant poles in an op amp, it may cause stability problems. In this case, frequency compensation is required. For a two-stage op amp, the Miller compensation is needed. For a three-stage op amp, the simple Miller compensation cannot remove the third pole. To stabilize three-stage op amps, nested-Miller compensation can be used [11, 22, 53].

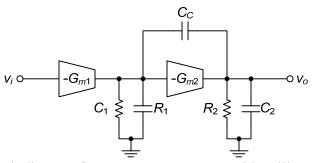

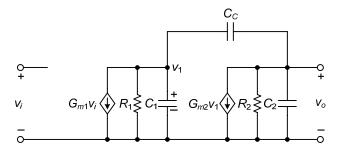

#### 3.5.1 Miller Compensation

Figure 3.8 shows a block diagram of a two-stage op amp with a Miller compensation capacitor,  $C_c$ . Each gain stage is assumed to have a high output resistance, and it is labeled as a transconductance block.  $C_1$ ,  $C_2$ ,  $R_1$ , and  $R_2$  are the

capacitance and resistance associated with gain stages.  $C_2$  and  $R_2$  include load capacitance and load resistance, respectively.

Figure 3.8 Block diagram for a two-stage op amp with Miller compensation.

The small-signal equivalent circuit of the two-stage op amp in Figure 3.8 is illustrated in Figure 3.9. Obviously, without compensation capacitor  $C_C$ , there are two poles in this circuit. They are

$$\omega_{p1}' = -\frac{1}{R_1 C_1} \tag{3.13}$$

$$\omega_{p2}' = -\frac{1}{R_2 C_2} \tag{3.14}$$

Figure 3.9 Small-signal model of the two-stage op amp in Figure 3.8.

By nodal analysis, the exact transfer function from the input  $v_i$  to the output  $v_o$  can be expressed as [54]