# 1/f NOISE IN HAFNIUM BASED HIGH-k GATE DIELECTRIC MOSFETS AND A REVIEW OF MODELING

by

# SIVA PRASAD DEVIREDDY

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

# DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT ARLINGTON

August 2007

#### ACKNOWLEDGEMENTS

In surviving the seemingly eternal dissertation years it is essential to receive professional and personal support from those surrounding us. I am grateful to all those people who helped me, directly or passively, in pursuing this incredible journey of mine. Most importantly, I thank my academic advisor, Dr. Zeynep Çelik-Butler, for providing me with this opportunity to work with her and evolve professionally. Her constant nudging and prodding was very critical in the completion of this work.

I would like to thank Dr. Wiley Kirk, Dr. Donald Butler, Dr. Seong Jin Koh, and Dr. Weidong Zhou who were kind to serve as members on my committee.

I am grateful to Dr. Hsing-Huang Tseng, Dr. Ania Zlotnicka, Dr. Philip Tobin and Fang Wang for their timely support/suggestions and devices used in this study.

Thanks to my fellow researchers - Dr. Bigang Min, Ashutosh Dave, Dr. Mukti Rana, Dr. Mazhar-Ul-Hoque, Tanvir Morshed, Shakhauat Hossain, Suraj Patil, Murali Chitteboyina; and close friends - Tapan Gautam, Niraj /Hetal Thacker, Ketan Thakkar, Naveen Siddareddy, Surendra Sridhara, Shashikanth Sena, and Ravi Kumar Sirka.

Finally, I express my deepest gratitude to my parents Ankamma Rao, Parvathi Devi and my sister Lakshmi Lavanya, who are the principal source of motivation and nothing would have been possible without their love and support.

August 02, 2007

### ABSTRACT

# 1/f NOISE IN HAFNIUM BASED HIGH-k GATE DIELECTRIC MOSFETS AND A REVIEW OF MODELING

Publication No.

Siva Prasad Devireddy, PhD.

The University of Texas at Arlington, 2007

Supervising Professor: Zeynep Çelik-Butler

For next generation MOSFETs, the constant field scaling rule dictates a reduction in the gate oxide thickness among other parameters. Consequently, gate leakage current becomes a serious issue with very thin SiO<sub>2</sub> that is conventionally used as gate dielectric since it is the native oxide for Si substrate. This has driven an industry wide search for suitable alternate 'high-k' gate dielectric that has a high value of relative permittivity compared to SiO<sub>2</sub> thereby presenting a physically thicker barrier for tunneling carriers while providing a high gate capacitance. Consequently, it is essential to study the properties of these novel materials and the interfaces that they form with the substrate, gate or other dielectrics in a multi-level stack.

The main focus of this work is the 1/f noise that is specifically used as a characterization tool to evaluate the performance of high-k MOSFETs. Nevertheless, DC and split C-V characterization are done as well to obtain device performance parameters that are used in the noise analysis.

At first, the room temperature 1/f noise characteristics are presented for n- and p-channel poly-Si gated MOSFETs with three different gate dielectrics-  $HfO_2$ ,  $Al_2O_3$  (top layer)/ $HfO_2$  (bottom layer),  $HfAlO_x$ . The devices had either 1 nm or 4 nm SiO<sub>2</sub> interfacial layer, thus presenting an opportunity to understand the effects of interfacial layer thickness on noise and carrier mobility. In the initial study, the analysis of noise is done based on the Unified Flicker Noise Model. Next, a comparative study of 1/f noise behavior is presented for TaSiN (NMOS) and TiN (PMOS) gated MOSFETs with  $HfO_2$  gate dielectric and their poly-Si gated counterparts. Additionally, in TaSiN MOSFETs, the effect of the different deposition methods employed for interfacial layer formation on the overall device performance is studied.

Finally, the 'Multi-Stack Unified Noise' model (MSUN) is proposed to better model/characterize the 1/f noise in multi-layered high-k MOSFETs. This model takes the non-uniform trap density profile and other physical properties of the constituent gate dielectrics into account. The MSUN model is shown to be in excellent agreement with the experimental data obtained on TaSiN/HfO<sub>2</sub>/SiO<sub>2</sub> MOSFETs in the 78-350 K range. Additionally, the MSUN model is expressed in terms of surface potential based parameters for inclusion in to the circuit simulators.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                           | ii   |

|------------------------------------------------------------|------|

| ABSTRACT                                                   | iii  |

| LIST OF ILLUSTRATIONS                                      | vii  |

| LIST OF TABLES                                             | xii  |

| LIST OF SYMBOLS                                            | xiii |

| Chapter                                                    |      |

| 1.INTRODUCTION                                             | 1    |

| 1.1 High Dielectric Constant Materials as Gate Dielectrics | 1    |

| 1.2 Noise Classification in MOSFETs                        | 12   |

| 2. 1/f NOISE IN MOSFETs                                    | 21   |

| 2.1 Introduction                                           | 21   |

| 2.2 General MOSFET Noise Theory                            | 21   |

| 2.3 1/f Noise Models                                       | 24   |

| 2.4 Experimental Procedure                                 | 32   |

| 2.5 Summary                                                | 45   |

| 3. 1/f NOISE IN POLY-Si /HIGH-k MOSFETs                    | 46   |

| 3.1 Introduction                                           | 46   |

| 3.2 MOSFET Device Information and Experiments              | 46   |

| 3.3 Physical Mechanism for Noise                                                | 49  |

|---------------------------------------------------------------------------------|-----|

| 3.4 Discussion on Noise in High-k MOSFETs                                       | 54  |

| 3.5 Interface of High-k with Poly-Si Gate                                       | 63  |

| 3.6 Summary                                                                     | 65  |

| 4. 1/f NOISE IN METAL GATED MOSFETs<br>WITH HfO <sub>2</sub> AS GATE DIELECTRIC | 66  |

| 4.1 Introduction                                                                | 66  |

| 4.2 TaSiN Metal Gate for N-Type MOSFETs                                         | 67  |

| 4.3 TiN Metal Gate for P-Type MOSFETs                                           | 79  |

| 4.4 Summary                                                                     | 82  |

| 5. NOISE MODELING REVISITED                                                     | 83  |

| 5.1 Introduction                                                                | 83  |

| 5.2 Multi-Stack Unified Noise (MSUN) Model Derivation                           | 84  |

| 5.3 Experimental Verification for MSUN Model                                    | 94  |

| 5.4 MSUN Model for Circuit Simulators                                           | 104 |

| 5.5 Summary                                                                     | 113 |

| 6. SUMMARY AND CONCLUSIONS                                                      | 114 |

| Appendix                                                                        |     |

| A. SET-UP FOR GATE TO BULK AND TOTAL GATE<br>CAPACITANCE MEASUREMENTS           | 117 |

| REFERENCES                                                                      | 121 |

| BIOGRAPHICAL INFORMATION                                                        | 138 |

# LIST OF ILLUSTRATIONS

| Figure |                                                                                                                                                                                                                                                                     | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

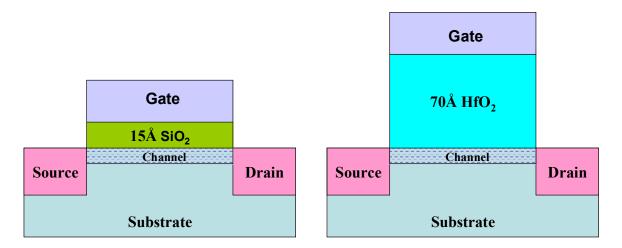

| 1.1    | MOSFET gate stacks with 7 nm $HfO_2$ (k~18) and<br>1.5 nm $SiO_2$ (k~3.9) yield the same gate capacitance.<br>However, device with $HfO_2$ exhibits lower gate<br>leakage currents                                                                                  | . 2  |

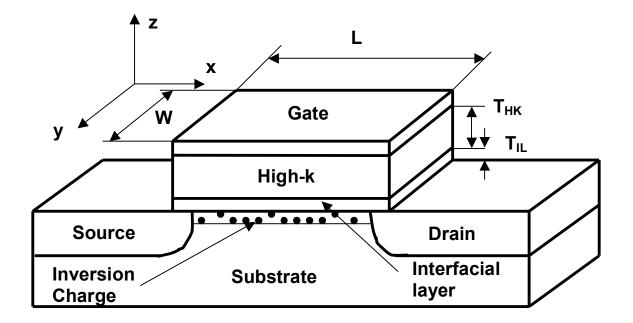

| 1.2    | Cross section of MOSFET with high-k and interfacial layers                                                                                                                                                                                                          | . 4  |

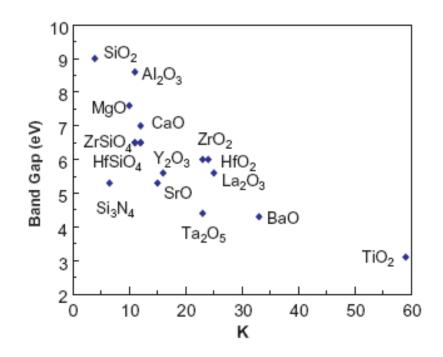

| 1.3    | Plot of dielectric constant vs. band gap for few<br>potential high-k dielectric materials. Reprinted from [16]<br>with permission from Elsevier                                                                                                                     | . 7  |

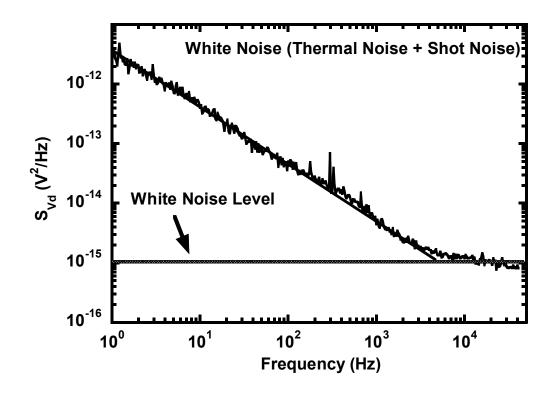

| 1.4    | Typical MOSFET white noise at high frequencies.<br>The device here is a TaSiN/HfO <sub>2</sub> /SiO <sub>2</sub> MOSFET<br>biased at $V_g = 1.13$ V and $V_d = 0.05$ V and at T = 100 K                                                                             | . 13 |

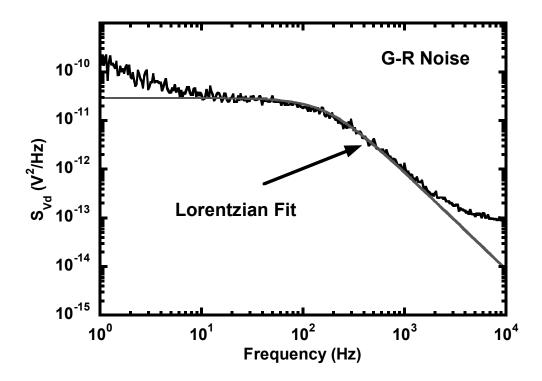

| 1.5    | G-R noise in TaSiN/HfO <sub>2</sub> /SiO <sub>2</sub> MOSFET biased at $V_g = 0.5$ V and $V_d = 0.05$ V and at T = 125 K. The Lorentzian approximation is provided for reference                                                                                    | . 16 |

| 1.6    | Voltage noise power spectrum of small area SiO <sub>2</sub><br>MOSFET biased at $V_g = 1.3$ V and $V_d = 0.05$ V along with<br>a Lorentzian fitting [46]                                                                                                            | . 17 |

| 1.7    | 1/f noise in TaSiN/HfO <sub>2</sub> /SiO <sub>2</sub> MOSFET biased at $V_g = 1.13$ V and $V_d = 0.05$ V and at T = 100 K                                                                                                                                           | . 18 |

| 2.1    | Cross section of a MOSFET showing trapping/de-trapping<br>of inversion layer carriers by traps in the gate oxide                                                                                                                                                    | . 27 |

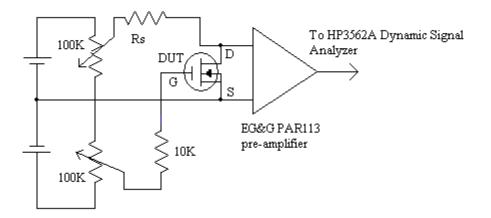

| 2.2    | Typical bias arrangement for an n-MOSFET.<br>The series resistance $(R_s)$ in the drain circuit is chosen<br>to be 10 times the channel resistance. This ensures a constant<br>voltage source providing the drain bias so that only<br>device noise gets amplified. | . 34 |

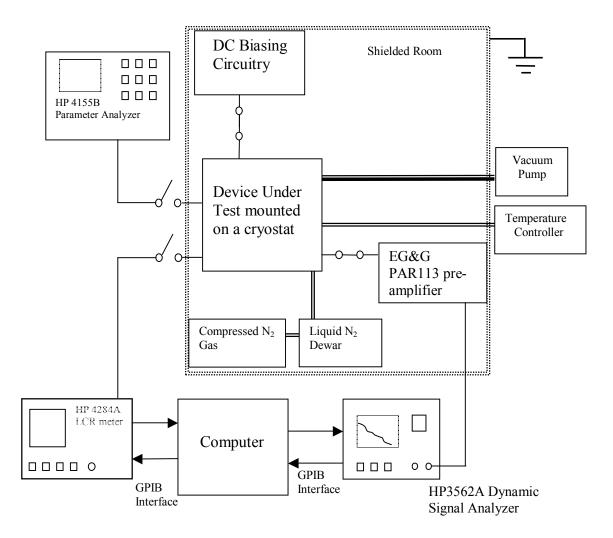

| 2.3    | An overview of variable temperature measurement                                                                                                                                                                                                                     |      |

|     | system. The DUT is placed in the shielded room<br>enclosure to minimize interference from stray noise sources                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

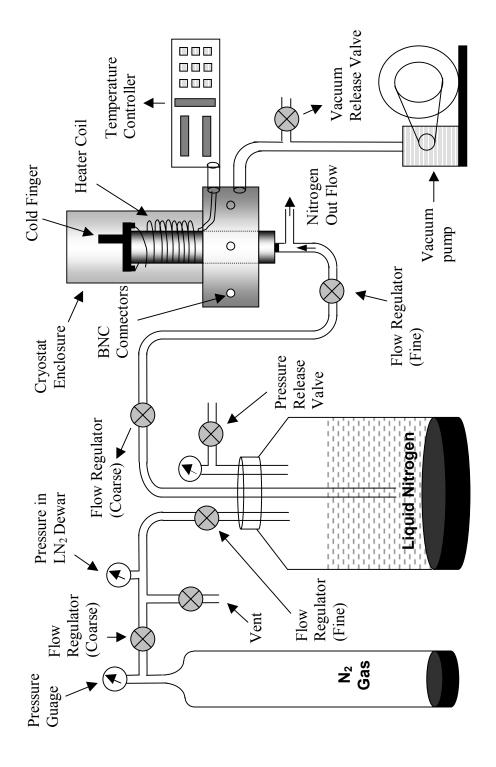

| 2.4 | Schematic of the variable temperature measurement set-up                                                                                                                                                                                                                                                                                                                                                                                                                         |

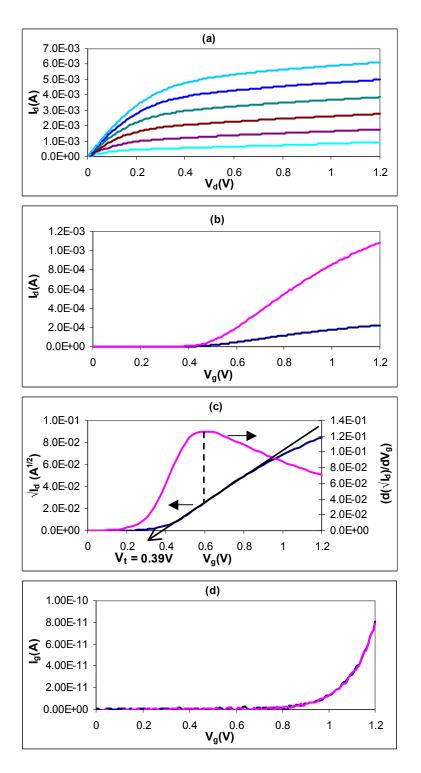

| 2.5 | <ul> <li>(a) I<sub>d</sub>-V<sub>d</sub> curve for V<sub>g</sub> varying from 0.6 to 1.1 V in 0.1 V steps.</li> <li>(b) I<sub>d</sub>-V<sub>g</sub> curve for V<sub>d</sub> =10 mV and 50 mV.</li> <li>(c) Plot for threshold voltage extraction.</li> <li>(d) Gate leakage current vs. V<sub>g</sub> for V<sub>d</sub> =10 mV and 50 mV</li></ul>                                                                                                                               |

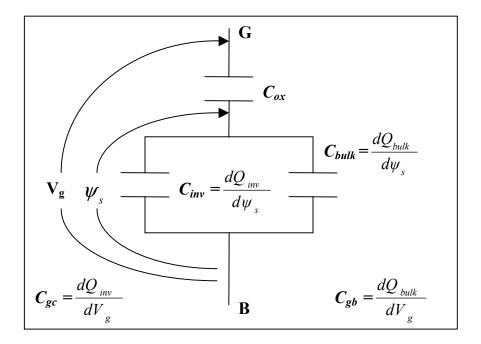

| 2.6 | MOSFET capacitances. $C_{inv}$ , $C_{bulk}$ are given as<br>the derivative of inversion and bulk charges, respectively,<br>with respect to surface potential while $C_{gc}$ , $C_{gb}$ are obtained<br>from the derivative of the inversion and bulk charges with<br>respect to the applied gate potential [67]                                                                                                                                                                  |

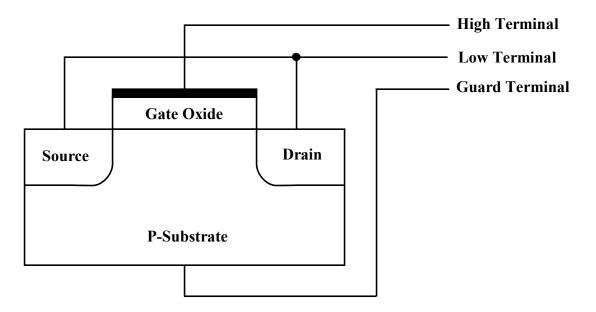

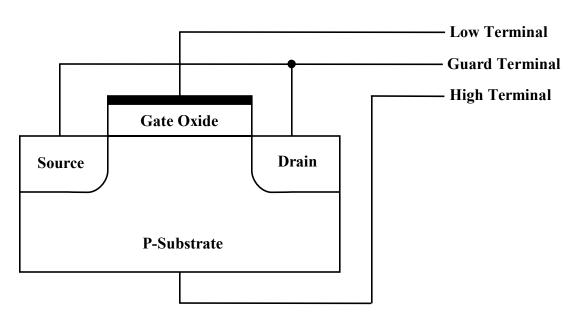

| 2.7 | Set-up for gate to channel capacitance measurement ( $C_{gc}$ ).<br>The High terminal of the LCR meter was connected to<br>the gate while source and drain were shorted to the Low end<br>of HP4284A. The substrate response to the applied bias<br>was bypassed (from the internal ammeter) to the<br>guard/ground terminal [67]                                                                                                                                                |

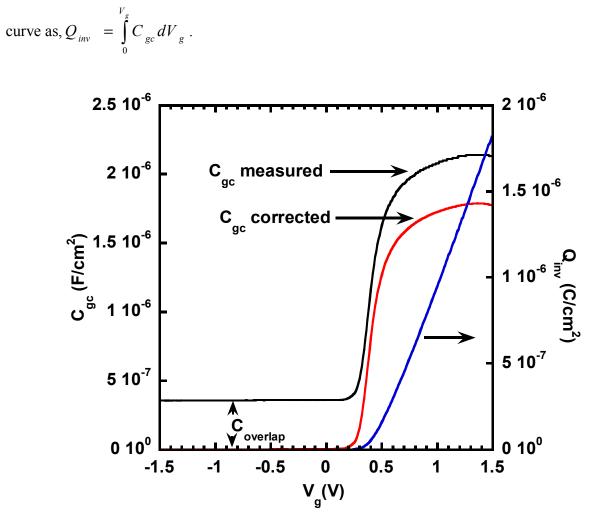

| 2.8 | Gate to channel capacitance of TaSiN/HfO <sub>2</sub> /SiO <sub>2</sub> MOSFET<br>(n-channel) from conventional split C-V measurement that<br>is corrected for overlap capacitance and inversion layer<br>charge density                                                                                                                                                                                                                                                         |

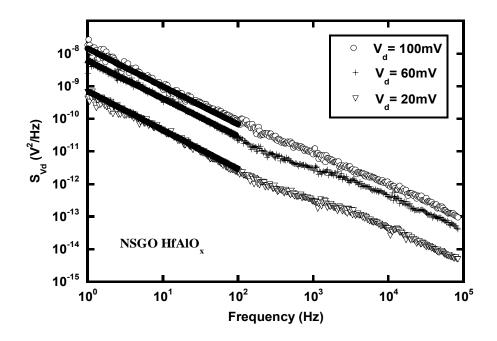

| 3.1 | Drain voltage noise power spectral density $S_{Vd}$ (V <sup>2</sup> Hz <sup>-1</sup> )<br>vs. frequency in log-log scale for an NSGO with HfAlO <sub>x</sub><br>( $W/L = 10.02 \mu m/0.165 \mu m$ ). The gate overdrive was 0.1 V<br>with $V_d = 20/60/100 \text{ mV}$ . The device exhibited $1/f^{\sigma}$ noise<br>with $1 < \sigma < 1.2$ . Here, $\sigma$ was obtained as the slope of the<br>straight line fit in the 1-100 Hz region as depicted by the<br>solid line. 48 |

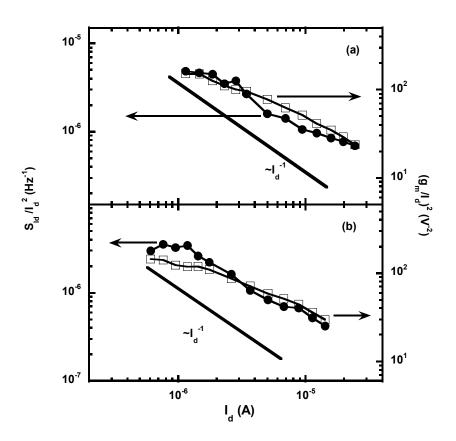

| 3.2 | The trends for $S_{Id}/I_d^2$ and $(g_m/I_d)^2$ plotted against drain<br>current in the log-log scale are the same. Thus,<br>Unified Model can better explain the observed noise.<br>The solid reference line is drawn to check for the $1/I_d$<br>dependence predicted by Hooge's Model. Here<br>(a) Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> NSGO and (b) Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> PSGO                                                        |

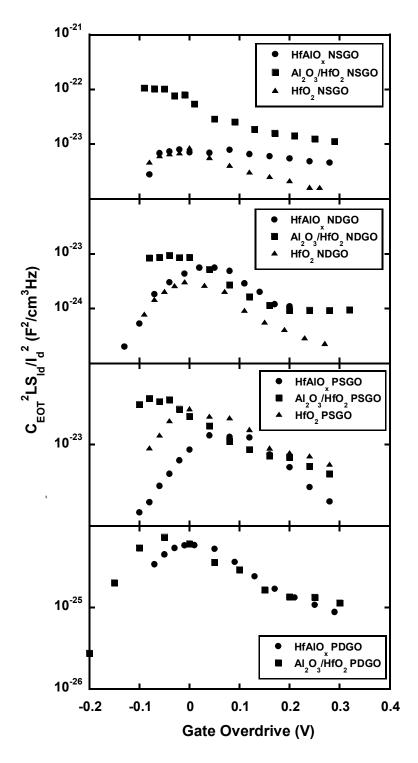

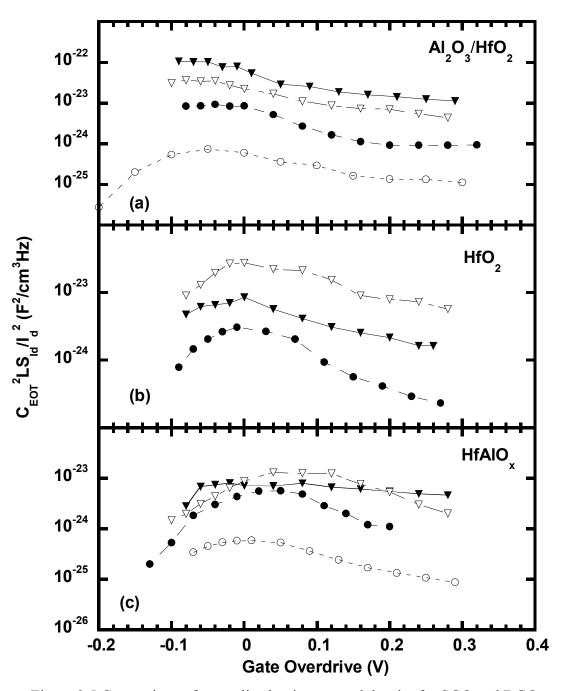

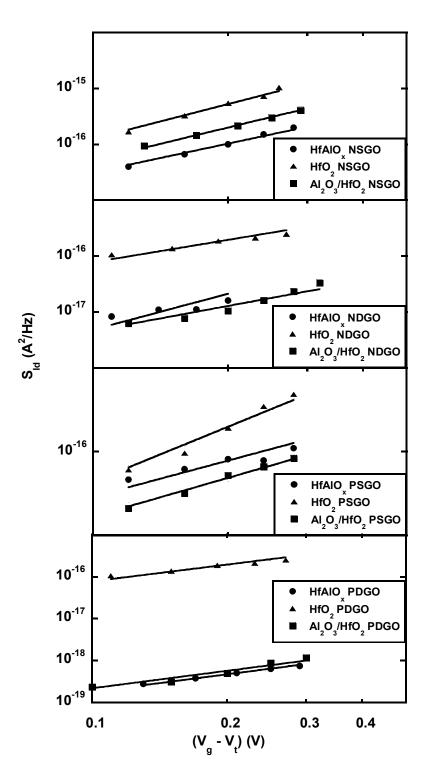

| 3.3 | Comparison of normalized noise spectral density<br>among different gate stack devices with the same<br>interfacial oxide thickness. $\checkmark$ HfO <sub>2</sub> , $\bullet$ HfAlO <sub>x</sub> ,<br>$\blacksquare$ Al <sub>2</sub> O <sub>3</sub> / HfO <sub>2</sub> . $V_d = \pm 40/\pm 50$ mV                                      | 56 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

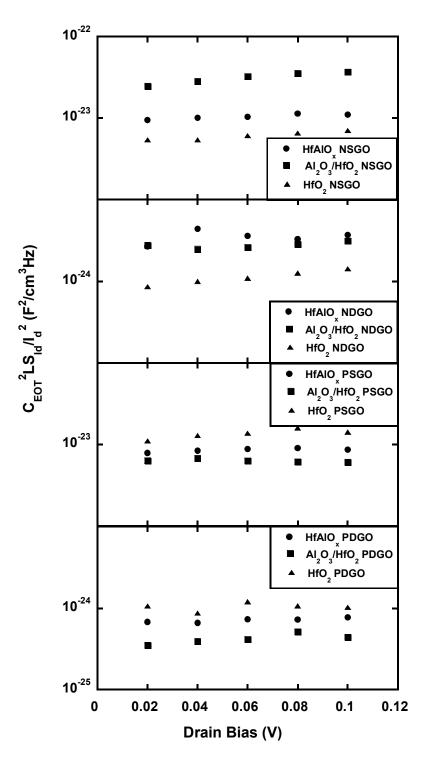

| 3.4 | Comparison of normalized $S_{Id}$ plotted as a function $V_d$ . Symbols $\nabla$ , $\bullet$ and $\blacksquare$ represent HfO <sub>2</sub> , HfAlO <sub>x</sub> and Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> , respectively. A gate overdrive of 0.1 V was used.                                                               |    |

| 3.5 | Comparison of normalized noise spectral density for SGO and DGO MOSFETs with Al <sub>2</sub> O <sub>3</sub> / HfO <sub>2</sub> , HfO <sub>2</sub> , and HfAlO <sub>x</sub> . Symbols $\mathbf{\nabla}, \mathbf{\nabla}, \mathbf{\bullet}$ , and $\circ$ represent NSGO, PSGO, NDGO and PDGO, respectively. Lines are guide to the eye. | 58 |

| 3.6 | Good fit to the data was obtained (solid lines) by<br>using appropriate $\mu_{c0}$ and $N_t$ values in the Unified<br>Noise Model expressions.                                                                                                                                                                                         |    |

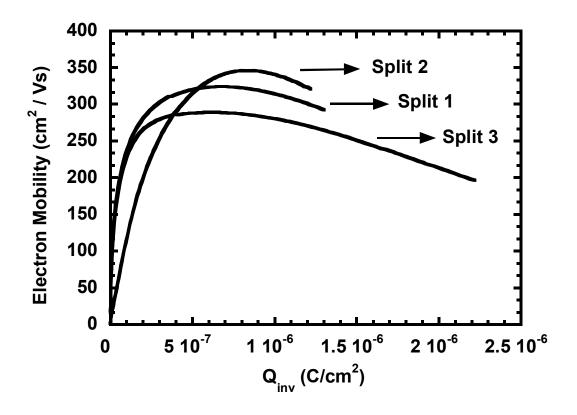

| 4.1 | Effective electron mobility as a function of inversion layer charge. Generally, SRPO devices exhibited higher mobility compared to RCA devices                                                                                                                                                                                         | 68 |

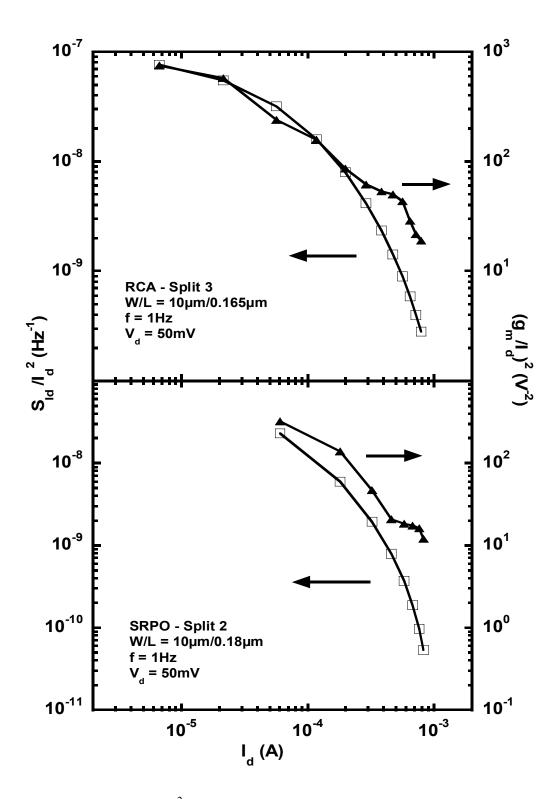

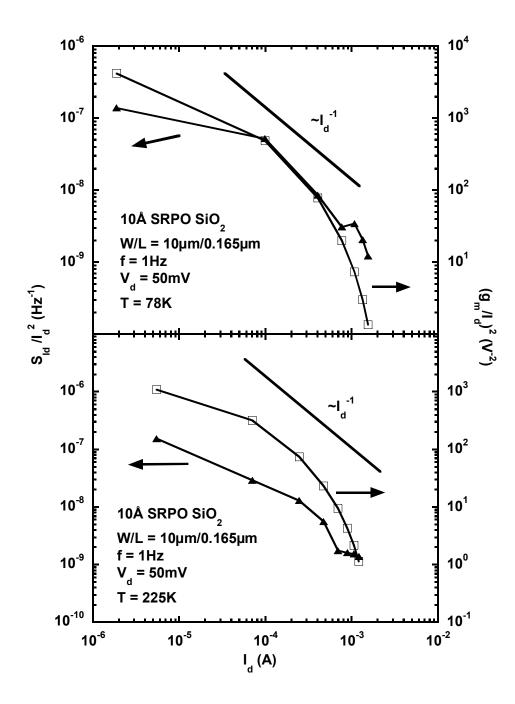

| 4.2 | $S_{Id}$ and $(g_m/I_d)^2$ follow the same trend implying that number fluctuations is the main noise causing mechanism.                                                                                                                                                                                                                |    |

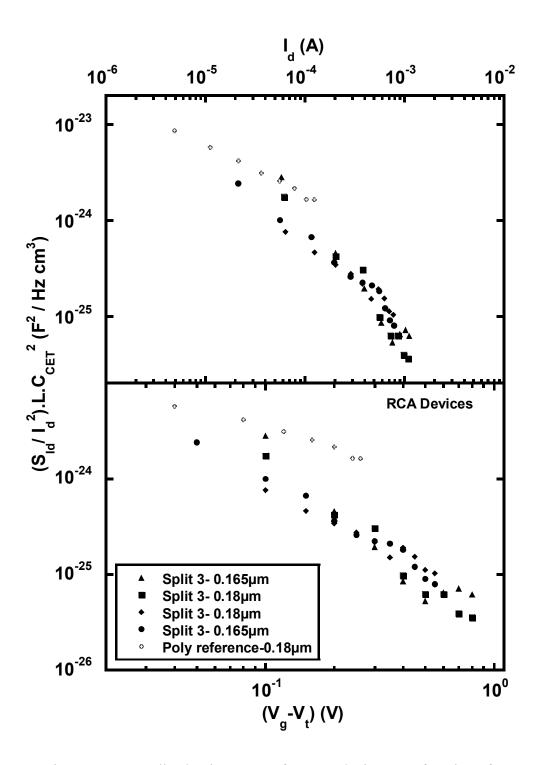

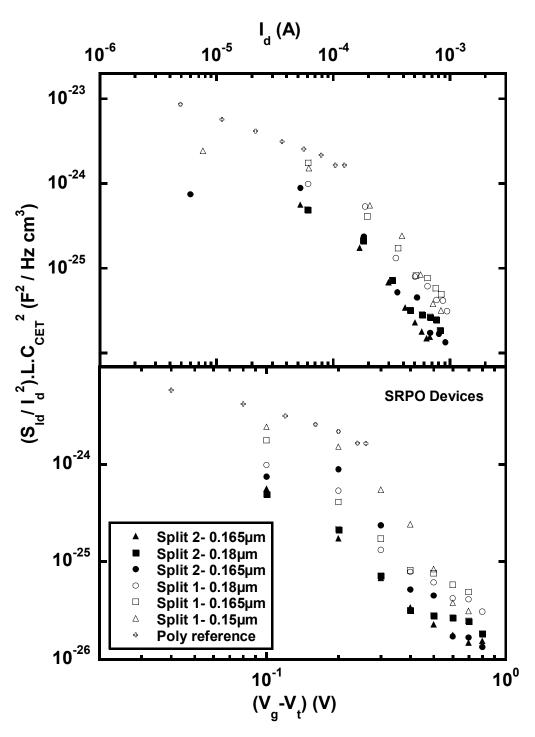

| 4.3 | Normalized noise spectra for RCA devices as<br>a function of gate overdrive and drain current,<br>in comparison to poly-Si reference device.                                                                                                                                                                                           |    |

| 4.4 | Normalized noise power spectral density of<br>SRPO devices for $V_d = 50$ mV. For all drain<br>currents, the devices with thinner interfacial oxide<br>layer showed slightly higher magnitude. Reference<br>poly-Si device showed highest overall.                                                                                     |    |

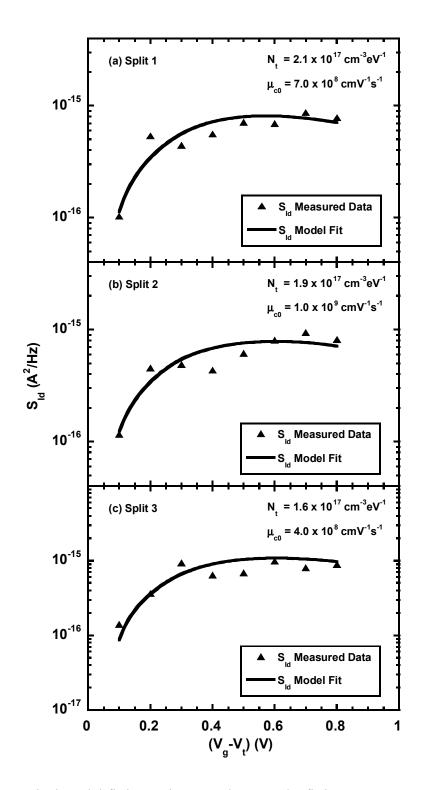

| 4.5 | Typical model fitting, using $N_t$ and $\mu_{c0}$ as<br>the fitting parameters, to the noise data on<br>0.18µm length devices from (a) Split1<br>(b) Split 2 and (c) Split 3                                                                                                                                                           |    |

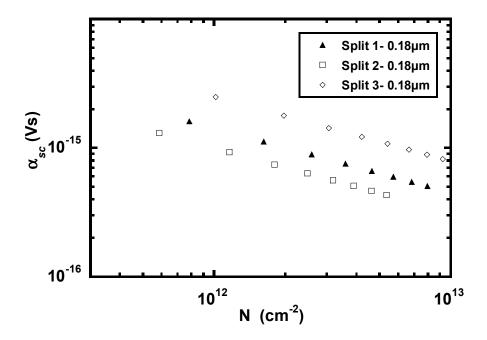

| 4.6  | Comparison of the extracted Coulomb                                                                                                                                                                                            | 77  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | scattering coefficient ( $\alpha_{sc}$ )                                                                                                                                                                                       | / / |

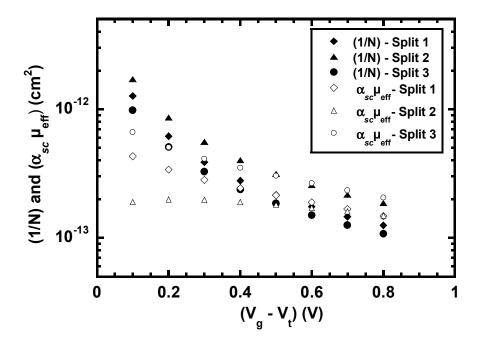

| 4.7  | The number fluctuations (1/N) and the mobility fluctuations ( $\alpha_{sc} \mu_{eff}$ ) components of noise.                                                                                                                   | 77  |

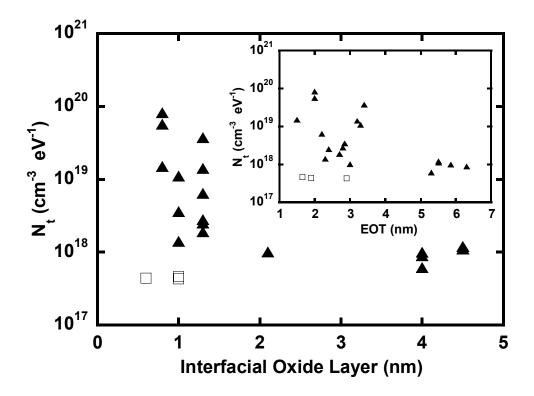

| 4.8  | The comparison for the extracted overall effective trap density values of metal gate devices under discussion ( $\circ$ ) to those reported in literature for comparable high-k stacks ( $\blacktriangle$ ) compiled by [106]. | 78  |

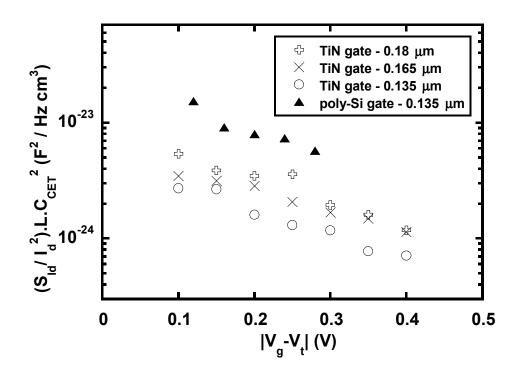

| 4.9  | Normalized noise level is higher for reference<br>poly-Si MOSFETs compared to TiN gate MOSFETs<br>indicating a better high-k in the latter.                                                                                    | 80  |

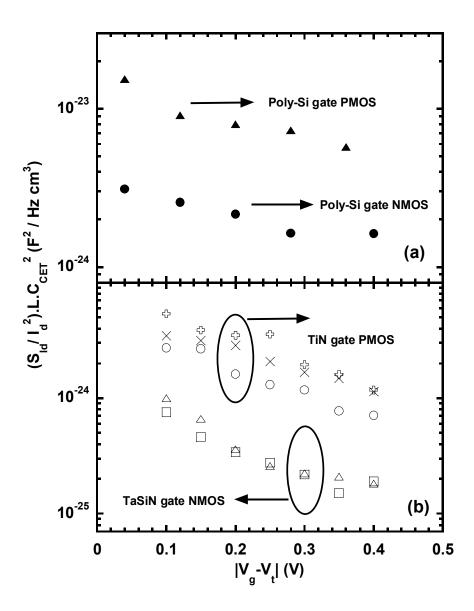

| 4.10 | Inherent device noise comparison among<br>n- & p-type MOSFETs with HfO <sub>2</sub> gate dielectric<br>and (a) poly-Si gate (b) metal gates.                                                                                   | 81  |

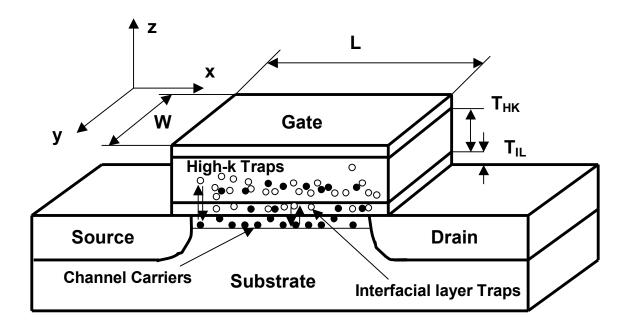

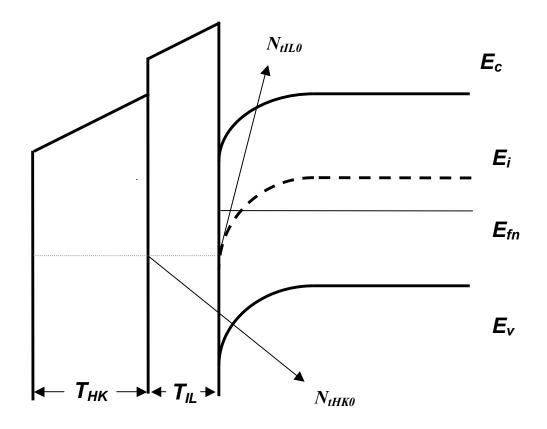

| 5.1  | Typical structure of MOSFET with high-k/interfacial layer gate stack                                                                                                                                                           | 85  |

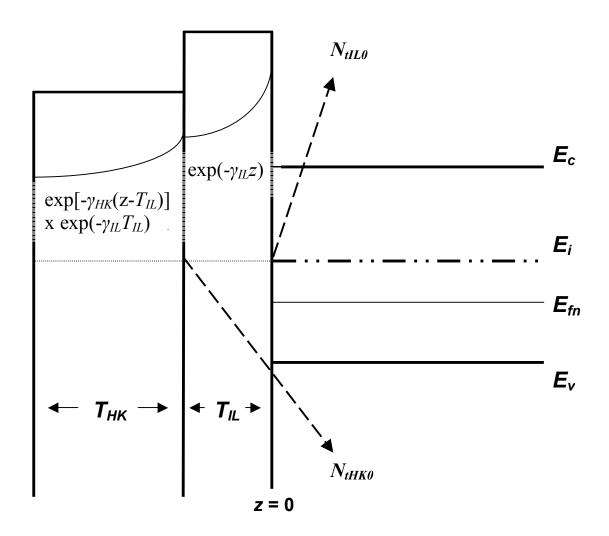

| 5.2  | General band structure for high-k MOSFETs.                                                                                                                                                                                     | 87  |

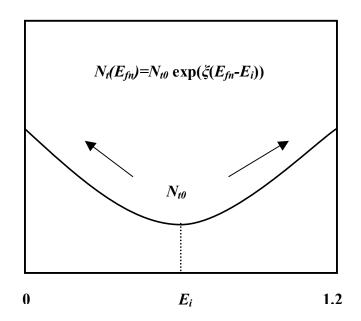

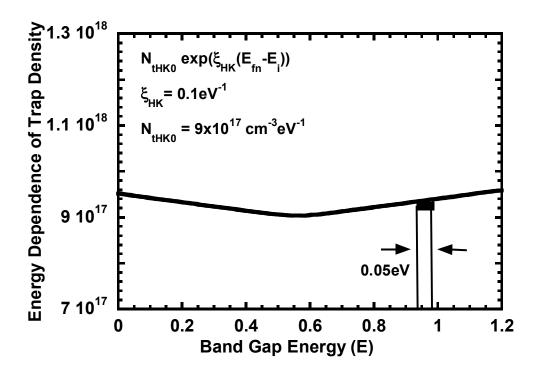

| 5.3  | Dielectric trap density variation with respect to energy for a positive value $\xi$ (Illustration only. Not a real profile).                                                                                                   | 88  |

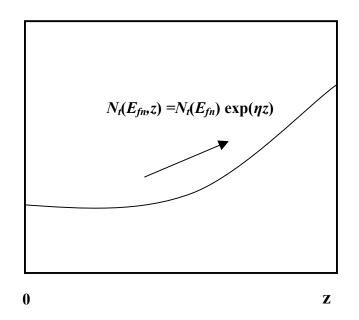

| 5.4  | Trap density profile into the gate dielectric for a positive value of $\eta$ (Illustration only. Not an actual profile)                                                                                                        | 88  |

| 5.5  | The band bending caused by the applied bias<br>modifies the trap profile at any location in<br>the dielectric stack.                                                                                                           | 89  |

| 5.6  | Plot to confirm the validity of number-correlated<br>mobility fluctuations as the physical mechanism<br>for noise at low temperatures                                                                                          | 95  |

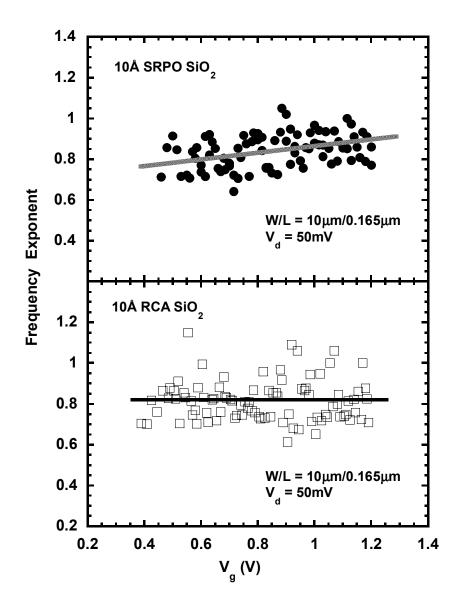

| 5.7  | The frequency exponent $\alpha$ of noise in the 1-100 Hz region is plotted for applied gate bias. A straight                                                                                                                   |     |

|      | line fit is made to the data from which parameters $\eta_{HK}$ , $\lambda_{HK}$ are extracted                                                                                                                                                                                                                                                                      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

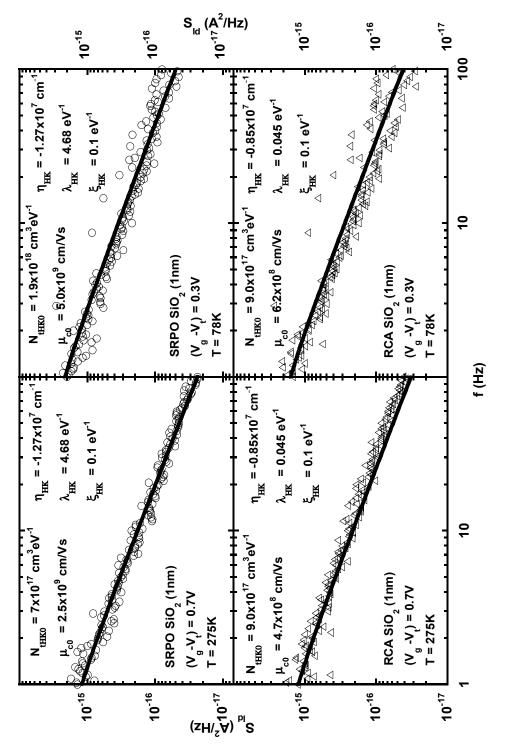

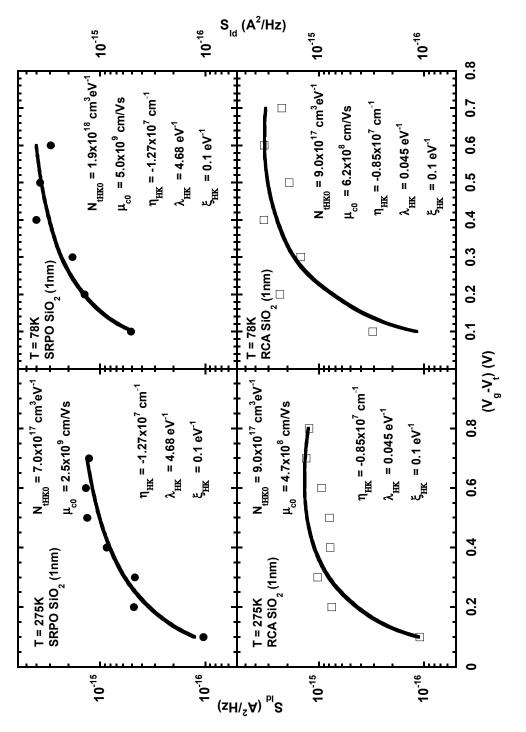

| 5.8  | The solid line depicts the MSUN model fitting<br>to the experimental noise data. Good agreement is<br>observed at all temperatures and for all devices                                                                                                                                                                                                             |

| 5.9  | The MSUN model fitting is in excellent agreement<br>with the actual noise data at all bias points. Here,<br>the 1 Hz value of the current noise power<br>spectral density is plotted for different gate bias values                                                                                                                                                |

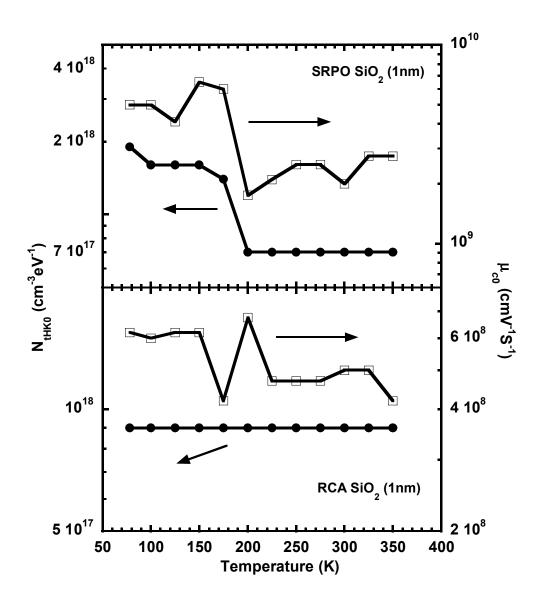

| 5.10 | The mid-gap trap density at HfO <sub>2</sub> /SiO <sub>2</sub> (SRPO or RCA) interface along with the fitting parameter $\mu_{c0}$ extracted from the noise data by using the MSUN model                                                                                                                                                                           |

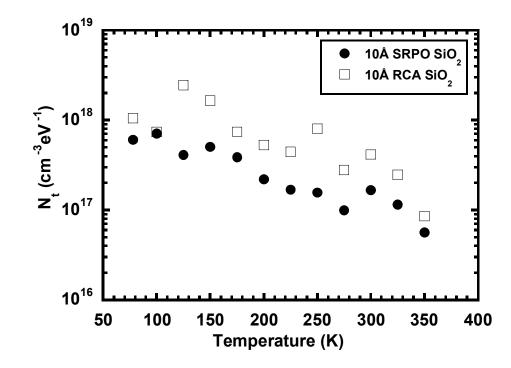

| 5.11 | The effective trap density values calculated<br>at each temperature set-point using the<br>Unified flicker noise model                                                                                                                                                                                                                                             |

| 5.12 | The energy interval swept by the quasi-Fermi level<br>for the temperature and bias range considered                                                                                                                                                                                                                                                                |

| A-1  | Set-up for gate to bulk capacitance measurement $(C_{gb})$ .<br>The Low end of the LCR meter must be connected to<br>the gate terminal. The High end is connected to the substrate<br>while drain and source terminals were shorted to the ground<br>so that only bulk charge was counted. Again, the gate is<br>biased from accumulation to inversion region [67] |

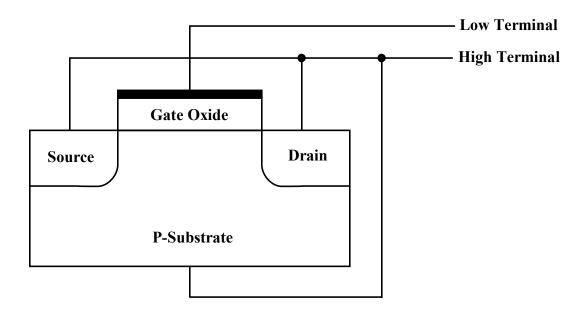

| A-2  | Set-up for total gate capacitance measurement ( $C_g$ ).<br>The gate was connected to the Low terminal in this configuration<br>to minimize chuck related noise in the measurement [116]119                                                                                                                                                                        |

# LIST OF TABLES

| Table |                                                                                                                                                         | Page |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1   | A few potential high-k dielectrics for CMOS applications<br>with approximate dielectric constant and band gap<br>values [4]                             | 3    |

| 1.2   | A few CMOS metal gates with approximate work functions [23,24,25,26,27]                                                                                 | 9    |

| 3.1   | Summary of devices and extracted parameters.<br>*Reference device data for NMOS [72] and PMOS [73]                                                      | 52   |

| 4.1   | Summary of the gate stacks considered along with the extracted effective trap density and $\mu_{c0}$ values. * Poly-Silicon gated device from Chapter 3 | 74   |

| 4.2   | The extracted noise parameters.<br>* Poly-Silicon gated device from Chapter 3                                                                           | 80   |

# LIST OF SYMBOLS

| $C_{B}$        | Si bulk capacitance at maximum depletion (Fcm <sup>-2</sup> )               |

|----------------|-----------------------------------------------------------------------------|

| $C_{CET}$      | capacitance equivalent oxide capacitance of MOSFET ( $Fcm^{-2}$ )           |

| $C_D$          | depletion capacitance (Fcm <sup>-2</sup> )                                  |

| $C_{EOT}$      | equivalent oxide capacitance of MOSFET (Fcm <sup>-2</sup> )                 |

| $C_g$          | total gate capacitance of MOSFET (Fcm <sup>-2</sup> )                       |

| $C_{gb}$       | gate to bulk capacitance of MOSFET (Fcm <sup>-2</sup> )                     |

| $C_{gc}$       | gate to channel capacitance of MOSFET (Fcm <sup>-2</sup> )                  |

| $C_{it}$       | interface trap charge (Fcm <sup>-2</sup> )                                  |

| $C_{ox}$       | gate oxide capacitance of MOSFET (Fcm <sup>-2</sup> )                       |

| $C_{overlap}$  | overlap capacitance (Fcm <sup>-2</sup> )                                    |

| $D_{it}$       | interface trap density from sub-threshold measurements ( $eV^{-1}cm^{-2}$ ) |

| Ε              | energy level (eV)                                                           |

| EOT            | equivalent oxide thickness (nm)                                             |

| E <sub>c</sub> | conduction band edge (eV)                                                   |

| $E_{fn}$       | quasi Fermi level (eV)                                                      |

| $E_g$          | energy Gap (eV)                                                             |

| $E_i$          | intrinsic Fermi level (eV)                                                  |

| $E_{v}$                 | valence band edge (eV)                                     |

|-------------------------|------------------------------------------------------------|

| $E_x$                   | field along the channel $(Vcm^{-1})$                       |

| f                       | frequency (Hz)                                             |

| $f_t$                   | trap occupancy function                                    |

| $g_d$                   | Conductance (A $V^{-1}$ )                                  |

| $g_m$                   | transconductance (A V <sup>-1</sup> )                      |

| h                       | Planck's constant (eV-s)                                   |

| $I_d$                   | drain current (A)                                          |

| k                       | dielectric constant                                        |

| k                       | Boltzmann's constant (eV K <sup>-1</sup> )                 |

| L                       | MOSFET channel length (µm)                                 |

| $\Delta L$              | length of pinch-off/velocity saturation region ( $\mu m$ ) |

| <i>m</i> *              | electron effective mass (kg)                               |

| <i>m<sub>HK</sub></i> * | carrier effective mass in the high-k dielectric (kg)       |

| $m_{IL}^{*}$            | carrier effective mass in the interfacial layer (kg)       |

| N                       | inversion layer charge density (cm <sup>-2</sup> )         |

| $N_{0}$                 | source end charge density $(cm^{-2})$                      |

| $N_{f}$                 | fixed charge density $(cm^{-2})$                           |

| $N_I$                         | substrate doping concentration (cm <sup>-3</sup> )                          |

|-------------------------------|-----------------------------------------------------------------------------|

| $N_L$                         | drain end charge density (cm <sup>-2</sup> )                                |

| $N_m$                         | charge density corresponding to surface potential mid-point $(cm^{-2})$     |

| N(x)                          | inversion layer charge density at distance x from the source $(cm^{-2})$    |

| $N_t$                         | oxide trap density ( $cm^{-3} eV^{-1}$ )                                    |

| Not                           | occupied traps per unit area (cm <sup>-2</sup> )                            |

| N <sub>tHK0</sub>             | trap density at the intrinsic Fermi level, at the high-k dielectric -       |

|                               | interfacial layer interface $(cm^{-3} eV^{-1})$                             |

| $N_{tHK}(E, x, y, z)$         | trap density distribution over space and energy in the high- $k$ layer      |

|                               | $(cm^{-3} eV^{-1})$                                                         |

| $N_{tHK}(E_{fn}, z)$          | trap density distribution in the high- $k$ layer at the quasi Fermi level   |

|                               | $(cm^{-3} eV^{-1})$                                                         |

| N <sub>tIL0</sub>             | trap density at the intrinsic Fermi level and at the interfacial layer - Si |

|                               | interface (cm <sup><math>-3</math></sup> eV <sup><math>-1</math></sup> )    |

| N <sub>tIL</sub> (E, x, y, z) | trap density distribution over space and energy in the interfacial layer    |

|                               | $(cm^{-3} eV^{-1})$                                                         |

| $N_{tIL}(E_{fn}, z)$          | trap density distribution in the interfacial layer at the quasi Fermi level |

|                               | $(cm^{-3} eV^{-1})$                                                         |

| $\Delta N$                    | inversion charge in the $W\Delta x$ area                                    |

| $\Delta N_{ot}$               | number of occupied traps in the gate oxide ( $W\Delta x$ area)              |

| q                     | electronic charge (C)                                                      |

|-----------------------|----------------------------------------------------------------------------|

| $Q_{bulk}$            | bulk charge (Ccm <sup>-2</sup> )                                           |

| $Q_D$                 | depletion charge (Ccm <sup>-2</sup> )                                      |

| $Q_G$                 | gate charge (Ccm <sup>-2</sup> )                                           |

| $Q_{inv}$             | inversion layer charge (Ccm <sup>-2</sup> )                                |

| $Q_{it}$              | interface trap charge (Ccm <sup>-2</sup> )                                 |

| $Q_{sc}$              | semiconductor charge (Ccm <sup>-2</sup> )                                  |

| $Q_t$                 | oxide trap charge (Ccm <sup>-2</sup> )                                     |

| R                     | coupling coefficient between fluctuations in the channel charge and in     |

|                       | the gate oxide trapped charge                                              |

| S                     | subthreshold slope $(V^{-1})$                                              |

| $S_{Id}(f)$           | total drain current noise power spectral density $(A^2 Hz^{-1})$           |

| $S_{\Delta Id}(x,f)$  | power spectral density of the local current fluctuations ( $A^2 Hz^{-1}$ ) |

| $S_{\Delta Nt}(x, f)$ | power spectral density of the mean square fluctuations in the trapped      |

|                       | charge carriers over the area $W\Delta x$ (Hz <sup>-1</sup> )              |

| $S_{V_d}$             | voltage noise power spectral density ( $V^2 Hz^{-1}$ )                     |

| $S_{_{V\!f\!b}}$      | flat band voltage noise power spectral density ( $V^2 Hz^{-1}$ )           |

| $S_{_{V_g}}$          | input referred noise $(V^2 Hz^{-1})$                                       |

| Т                     | temperature (K)                                                            |

| t <sub>CET</sub>  | capacitance equivalent thickness (nm)                                  |

|-------------------|------------------------------------------------------------------------|

| $T_{EOT}$         | equivalent oxide thickness (cm)                                        |

| $T_{HK}$          | high-k dielectric thickness (cm)                                       |

| $T_{IL}$          | thickness of interfacial layer (cm)                                    |

| $T_{ox}$          | thickness of gate oxide (cm)                                           |

| $T_{SiO_2}$       | thickness of SiO <sub>2</sub> (cm)                                     |

| V                 | channel quasi-Fermi potential (V)                                      |

| V <sub>d</sub>    | drain to source voltage (V)                                            |

| V <sub>dsat</sub> | drain to source voltage at pinch-off/velocity saturation point (V)     |

| $V_{FB}^{0}$      | gate-substrate work function difference (V)                            |

| $V_g$             | gate to source voltage (V)                                             |

| V <sub>gHK</sub>  | band bending in the high-k layer (V)                                   |

| V <sub>gIL</sub>  | band bending in the interfacial layer (V)                              |

| V <sub>ox</sub>   | potential across gate oxide (V)                                        |

| V <sub>t</sub>    | threshold voltage (V)                                                  |

| V(x)              | horizontal channel potential in the channel at a distance $x$ from the |

|                   | source (V)                                                             |

| W                 | MOSFET channel width of (µm)                                           |

| x                 | distance in the channel from source towards drain(cm)                  |

| У                                    | distance in the width dimension (cm)                                     |  |

|--------------------------------------|--------------------------------------------------------------------------|--|

| Z                                    | distance into the gate dielectric stack (cm)                             |  |

| $\Delta x$                           | infinitesimal length in the gate dielectric (cm)                         |  |

| $\Delta y$                           | infinitesimal width in the gate dielectric (cm)                          |  |

| $\Delta z$                           | infinitesimal thickness in the gate dielectric (cm)                      |  |

| α                                    | surface potential based screened coulomb scattering coefficient (V s)    |  |

| $lpha_{H}$                           | Hooge's Coefficient                                                      |  |

| $lpha_{sc}$                          | screened coulomb scattering coefficient (V s)                            |  |

| γ                                    | carrier tunneling coefficient in the gate dielectric (cm <sup>-1</sup> ) |  |

| $\gamma_{_{HK}}$                     | carrier tunneling coefficient in the high-k gate dielectric $(cm^{-1})$  |  |

| $\gamma_{{\scriptscriptstyle I\!L}}$ | carrier tunneling coefficient in the interfacial layer $(cm^{-1})$       |  |

| ${\cal E}_0^{}$                      | permittivity of free space (Fcm <sup>-1</sup> )                          |  |

| ${\cal E}_{HK}$                      | dielectric constant of high-k material (Fcm <sup>-1</sup> )              |  |

| ${\cal E}_{_{I\!L}}$                 | dielectric constant of interfacial layer (Fcm <sup>-1</sup> )            |  |

| $\mathcal{E}_{Si}$                   | permittivity of silicon (Fcm <sup>-1</sup> )                             |  |

| $\boldsymbol{\mathcal{E}}_{SiO_2}$   | permittivity of silicon oxide (Fcm <sup>-1</sup> )                       |  |

| $\pmb{\eta}_{\scriptscriptstyle H\!K}$ | fitting parameter that determines the high-k dielectric trap density           |

|----------------------------------------|--------------------------------------------------------------------------------|

|                                        | distribution as a function of $z$ (cm <sup>-1</sup> )                          |

| $\eta_{_{I\!L}}$                       | fitting parameter that determines the interfacial layer trap density           |

|                                        | distribution as a function of $z$ (cm <sup>-1</sup> )                          |

| $\lambda_{_{HK}}$                      | fitting parameter that defines the effect of dielectric band-bending on        |

|                                        | the trap density that the tunneling electron encounters in the high-k          |

|                                        | dielectric layer $(eV^{-1})$                                                   |

| $\lambda_{_{I\!L}}$                    | fitting parameter that defines the effect of dielectric band-bending on        |

|                                        | the trap density that the tunneling electron encounters in the interfacial     |

|                                        | layer $(eV^{-1})$                                                              |

| μ                                      | surface potential based effective carrier mobility (cm <sup>2</sup> /Vs)       |

| $\mu_{c0}$                             | mobility fitting parameter (cm/Vs)                                             |

| $\mu_{e\!f\!f}$                        | effective carrier mobility (cm <sup>2</sup> /Vs)                               |

| $\mu_{imp}$                            | mobility due to impurity scattering $(cm^2V^{-1}s^{-1})$                       |

| μlatt                                  | mobility due to lattice scattering $(cm^2V^{-1}s^{-1})$                        |

| $\mu_{others}$                         | mobility due to other scattering phenomena (cm <sup>2</sup> /Vs)               |

| $\mu_{ox}$                             | mobility due to oxide charge scattering (cm <sup>2</sup> /Vs)                  |

| ζнк                                    | fitting parameter for energy dependence of high-k traps ( $eV^{-1}$ )          |

| ξıl                                    | fitting parameter for energy dependence of interfacial layer traps $(eV^{-1})$ |

| $\tau(E, x, y, z)$     | trapping time constant in the gate dielectric (s)            |  |

|------------------------|--------------------------------------------------------------|--|

| τ                      | trapping time constant (s)                                   |  |

| $	au_0$                | trapping time constant at the $Si/SiO_2$ interface (s)       |  |

| $\Phi$                 | barrier height (eV)                                          |  |

| $\pmb{\phi}_{_F}$      | bulk potential (V)                                           |  |

| $arPsi_{_{H\!K}}$      | high-k barrier height for tunneling carriers (eV)            |  |

| $arPsi_{_{I\!L}}$      | interfacial layer barrier height for tunneling carriers (eV) |  |

| σ                      | frequency exponent as in $1/f^{\sigma}$                      |  |

| ω                      | angular frequency (radians/s)                                |  |

| $\psi_m$               | surface potential mid-point (V)                              |  |

| $\psi_s$               | surface potential (V)                                        |  |

| $\Psi_{sat}$           | surface potential at pinch-off/velocity saturation point (V) |  |

| $\psi_{ss}$            | source side surface potential (V)                            |  |

| $oldsymbol{\psi}_{sd}$ | drain side surface potential (V)                             |  |

# CHAPTER 1

### INTRODUCTION

#### 1.1 High Dielectric Constant Materials as Gate Dielectrics

The current scaling trend in CMOS devices is the motivation for research in high dielectric constant films. Applications demanding low power consumption, low off-state leakage, and faster response require the devices to shrink. As the device dimensions scale down, the conventional SiO<sub>2</sub> gate dielectric is no longer viable below the 1.5 nm thickness due to prohibitively high gate leakage currents (>1  $A/cm^{2}$ ) caused by quantum mechanical tunneling of electrons/holes [1,2,3]. This results in the loss of inversion layer charge and an increase in standby power consumption. In theory, high dielectric constant or high-k materials offer an attractive solution in that they provide low leakage currents owing to a thicker physical layer for the same electrical thickness as their SiO<sub>2</sub> counterparts. For example, the MOSFETs in Figure 1.1 provide the same gate capacitance ( $\varepsilon_0 k/T_{ox}$ ) of ~2.3  $\mu$ Fcm<sup>-2</sup> so that their electrical thicknesses are equal. However, the device with 7 nm HfO<sub>2</sub> results in much lower gate leakage currents due to its larger physical thickness compared to 1.5 nm SiO<sub>2</sub>. Thus, high-k materials are advantageous in this context as they can be much thicker physically to block the tunneling current and yet have a thinner electrical thickness. While this seems to solve the quantum-tunneling problem, primary issues regarding the properties of high-k

materials and incorporation of these novel dielectrics into the standard CMOS process flow need to be dealt with.

Figure 1.1 MOSFET gate stacks with 7 nm  $HfO_2$  (k~18) and 1.5 nm  $SiO_2$  (k~3.9) yield the same gate capacitance. However, device with  $HfO_2$  exhibits lower gate leakage currents.

There are several materials that can be used as high-k dielectrics as shown in Table 1.1, which can be can be broadly classified as-

- Metal oxides

- Silicates (metal oxides doped with silicon)

- Aluminates (metal oxides doped with aluminum)

In the following, the fundamental issues with high-k materials and the various factors affecting the choice of these dielectrics for incorporation in to the standard CMOS processes are briefly discussed.

| Material                       | Dielectric  | Band gap, $E_g$ |

|--------------------------------|-------------|-----------------|

|                                | constant, k | (eV)            |

| HfO <sub>2</sub>               | 19          | 5.8             |

| ZrO <sub>2</sub>               | 25          | 7.8             |

| Al <sub>2</sub> O <sub>3</sub> | 9           | 8.7             |

| Si <sub>3</sub> N <sub>4</sub> | 7           | 5.1             |

| TiO <sub>2</sub>               | 80          | 3.5             |

| Ta <sub>2</sub> O <sub>5</sub> | 26          | 4.5             |

| La <sub>2</sub> O <sub>3</sub> | 30          | 4.3             |

| Y <sub>2</sub> O <sub>3</sub>  | 15          | 5.6             |

| HfSiON                         | 8           | -               |

| HfAlO <sub>x</sub>             | -           | 6.5             |

Table 1.1 A few potential high-k dielectrics for CMOS applications with approximate dielectric constant and band gap values [4].

# Formation of Interfacial Layer:

The most fundamental advantage of  $SiO_2$  is the quality of its interface with Si bulk. Most of the high-k materials considered so far have unstable interfaces with Si and an unintentional interfacial layer is formed at the Si surface due to oxygen diffusion through high-k or reactions at the Si/high-k interface. Although it is possible to control the interfacial formation by means of careful interface engineering, the presence of this interfacial layer limits the maximum achievable gate capacitance. This can be explained by considering the resulting structure with the interfacial layer as shown in Figure 1.2. From MOSFET theory, the total applied gate voltage is distributed across the gate

Figure 1.2 Cross section of MOSFET with high-k and interfacial layers.

dielectric and the substrate. If the gate dielectric has multiple layers, they form a series combination so that the total voltage across the stack is divided among the layers. Hence, the overall gate dielectric capacitance is given by

$$1/C_{eq} = 1/C_{HK} + 1/C_{IL}$$

Clearly, the interfacial layer with a lower capacitance dominates the overall capacitance thereby compromising the maximum capacitance that can be obtained with the high-k alone. To understand how this reduction in capacitance limits the overall equivalent oxide thickness, consider the equivalent oxide thickness of high-k dielectric without any interfacial layer, which is given by-

$$T_{EOT} = 3.9 \times \left(\frac{T_{HK}}{\varepsilon_{HK}}\right)$$

Here,  $T_{EOT}$  represents the equivalent physical thickness of SiO<sub>2</sub> that would provide the same gate capacitance as the dielectric under consideration and without any regards to leakage or reliability issues. Assuming SiO<sub>2</sub> interfacial layer for simplicity, the equivalent oxide thickness of the resulting stack is given as

$$T_{EOT} = T_{SiO_2} + 3.9 \times \left(\frac{T_{HK}}{\varepsilon_{HK}}\right)$$

Therefore, the thickness of the interfacial layer sets the lower limit to the gate dielectric scaling.

It should be noted that conventional SiO<sub>2</sub> gate dielectrics had an interface state density of about  $1 \times 10^{10}$  cm<sup>-2</sup>. High-k materials investigated by charge pumping measurements showed higher interface trap density values [5,6]. Consequently, there is degradation in mobility in addition to substantial fixed charges and flatband/ threshold voltage shifts [7,8,9,10,11,12,13]. It has been shown in this work that the overall electrical behavior and reliability of high-k dielectric MOSFETs would strongly depend on the material properties of the interfacial layer that exists between the high-k and the substrate.

### *Trade-off between permittivity* (k) *and band gap* $(E_g)$ :

High permittivity dielectrics can provide high gate capacitance for good channel control in conjunction with larger physical thickness, thereby avoiding the unintentional conduction paths from the channel to the gate. However, the band gap of the dielectric plays an equally important role in warding off the leakage currents. The band gap of SiO<sub>2</sub> is ~9 eV with 3.5 eV and 4.4 eV as conduction and valence band offsets with Si. This means that the electrons in the NMOS inversion layer have to cross a barrier of 3.5 eV to tunnel through the oxide. Similarly, the holes need to overcome a barrier of 4.4 eV to contribute to the gate tunneling currents. In both Fowler-Nordheim and direct tunneling mechanisms, tunneling current density has an exponential dependence on the barrier height [14,15]. Thus, the potential high-k dielectric is required to present an appropriate barrier height to the channel carriers to prevent carrier tunneling and in turn check the gate leakage. Among the several high-k materials investigated for gate dielectric application, the dielectric constant generally exhibited an inverse relationship to the band gap [4]. Therefore, a compromise has to be made between the permittivity and band gap values so that a high enough k value can be chosen to obtain the desired performance while having a large tunneling barrier. Figure 1.3 gives a plot of dielectric constant vs. band gap for a few potential high-k dielectric materials [16].

It can be noted that  $HfO_2$  and  $ZrO_2$  have reasonably high values for both k and  $E_g$ . Al<sub>2</sub>O<sub>3</sub> has a low value of k but a higher band gap ensuring low leakage currents. Other materials with high values of k have low barrier heights making them unsuitable for low power applications. Additionally, fringing or field induced barrier lowering (FIBL) is seen as an anomalous degradation in turn-on/off characteristics in sub-micron devices, especially involving dielectrics with very high permittivity values. FIBL shows similar effects as the drain induced barrier lowering (DIBL) but has a slightly different mechanism. While in DIBL, the electric fields from the drain junction terminate directly

on the channel and/or source regions causing a reduction in the drain/source barrier. For FIBL, the drain is coupled to the channel via through the gate dielectric in turn causing lowered threshold voltage, increased off-state leakage and a deteriorated sub-threshold

Figure 1.3 Plot of dielectric constant vs. band gap for few potential high-k dielectric materials. Reprinted from [16] with permission from Elsevier.

swing. FIBL effect is not as conspicuous in SiO<sub>2</sub> MOSFETs as in high-k devices owing to the physical thickness and permittivity values. FIBL is gate length and permittivity dependent worsening for short channel devices and higher permittivity dielectrics. The choice of dielectrics with low dielectric constant values compared to Al<sub>2</sub>O<sub>3</sub> is limited due to other factors like stable interfaces, ability to withstand high CMOS process temperatures etc.

#### *Crystallization temperature/Film microstructure:*

In the past, amorphous SiO<sub>2</sub> films were preferred over single crystal or polycrystalline films. The grain boundaries in polycrystalline films are dominant in causing high leakage currents besides yielding non-uniformities in the permittivity values owing to the localized variations in grain size and orientation. Oxygen and dopant atoms diffuse much faster in polycrystalline structures and triple points generate defects or voids. Amorphous films on the other hand, exhibit better insulation properties, less severe oxygen and dopant diffusion resulting in lower defect density. Hence, the high-k films need to have high crystallization temperatures to endure the high temperature processing steps involved. Al<sub>2</sub>O<sub>3</sub> fares well compared to other high-k materials in this regard [4].

#### *Compatibility with the gate electrode:*

Gate compatibility is another integration issue for high-k dielectric materials. In the past, poly-silicon gates were the preferred choice, as their integration schemes were well established and they offered precise control of threshold voltages for both n-MOS and p-MOS structures by simply varying the doping concentrations of the poly-Si. However, it has been shown recently, that Fermi level pinning occurs at HfO<sub>2</sub>/poly-Si gate interface due to the interface states originating from the reactions between HfO<sub>2</sub> and poly-Si [17,18]. This sets a lower limit on the threshold voltage and necessitates the use of alternative gates. Besides, additional problems posed by poly-Si gate such as depletion effects in strong inversion, large sheet resistance and high activation temperatures can be avoided using metal gates [19,20,21,22], which might otherwise result in dopant penetration into the high-k causing significant fixed charges, traps, flatband and threshold voltage shifts. Table 1.2 lists a few potential metal gates that can be used in CMOS processes. Some of the main criteria concerning the metal gate selection are -

- Single mid-gap metal gate or dual metal gates

- Thermal, chemical and mechanical stability with gate dielectric/surrounding materials

- Low sheet resistance

- Compatibility with process integration

Table1.2 A few CMOS metal gates with approximate work functions [23,24,25,26,27].

| Gate Material     | Work Function (eV) |  |

|-------------------|--------------------|--|

| Ti                | 4.0                |  |

| TiN               | 4.8-5.3            |  |

| Ru                | 5.1                |  |

| Та                | 4.2                |  |

| TaSi <sub>2</sub> | 4.7-4.8            |  |

| TaSiN             | 4.4                |  |

| Мо                | 5.0                |  |

| RuO <sub>2</sub>  | 5.1                |  |

Metal work function is an important parameter in selecting the gate material because of the fact that threshold voltage of MOS device depends on it. If a single metal gate is needed for both PMOS and NMOS, a midgap metal with its Fermi level at the mid gap of the silicon substrate can be used. Although this simplifies the processing steps, the major disadvantage with this approach is that the threshold voltages for both NMOS and PMOS would be the range of 0.5 V, which is high for next generation devices. Alternatively, the dual metal gate approach can be made where in two different metals with work functions near the conduction and valence band of Si could be chosen as electrodes for n and p type MOSFETs. The integration process is complicated as extra masking and depositions steps would be necessary. Recently, stable alloys with varying compositions of Ru and Ta have been indicated to provide a range of work functions to be used as dual CMOS gates [28]. In this work, the evaluation of low frequency noise and mobility are presented for MOSFETs with TiN (pMOS) and TaSiN (nMOS) as metal gates.

### Deposition Techniques:

The choice of deposition technique is yet another key factor in determining the properties and final quality of the dielectric film. A few deposition techniques that could be employed for high-k dielectrics are listed below-

- Physical Vapor deposition (PVD)

- Metal Organic Chemical Vapor Deposition (MOCVD)

- Molecular Beam Epitaxy (MBE)

- Atomic Layer Deposition (ALD)

- Jet Vapor Deposition (JVD)

MOSFETs with HfO<sub>2</sub> gate dielectric made by MOCVD and ALD techniques have been evaluated for device performance parameters in this work.

Recent studies addressing the various integration issues and band gap considerations put HfO<sub>2</sub> at the forefront, followed by Hf-based dielectrics [9,29,30,31,32]. However, problems persist concerning the interfaces formed by these novel gate dielectrics with the substrate and the gate, mobility degradation, fixed charges, threshold shifts etc. Although, metal gates like TiN, TaN, TaSiN, Mo, Ru are suggested replacements for poly-Si gate towards a better high-k/gate interface, mobility degradation exists due to the traps in the high-k and the interface it forms with the substrate. In any case, an in-depth characterization study of charge trapping in these alternative gate dielectric materials and the interface they form with the substrate or interfacial layer is a subject of interest. Few widely used characterization tools are-

- 1. Quasi-static C-V technique

- 2. Conductance technique

- 3. Charge pumping measurements

- 4. Charge injection scheme

- 5. Low frequency noise method (1/f noise)

Quasi-static C-V measurements are routinely performed to obtain plethora of information regarding the MOS device parameters. Although it is easy to employ this method for interface trap characterization, it presents a limitation concerning the area of devices as it is difficult to obtain reliable/usable data in sub-micron MOSFETs due to parasitic capacitances. While charge pumping and charge injection techniques are used

for short channel devices, the analysis is limited to mid-gap range and the methods are destructive. Flicker or 1/f noise, is the predominant source of noise in the low frequency region, typically 1-100 kHz for a MOSFET. Low frequency noise (1/f noise) method can offer dielectric trap characteristics over a wide range of energies around the band edges for MOSFETs with dimensions in the sub-micron range, and is non-destructive in nature [33]. Further, the study of 1/f noise is significant for several reasons. It is an important design constraint for RF/microwave and analog applications, as it can get up-converted to phase noise thus causing a degradation in circuit/system performance [34,35,36,37]. In this work, the 1/f noise characterization is done to evaluate the performance of novel high-k materials as MOSFET gate dielectrics.

The next section gives a general categorization of different types of noise in MOSFETs to help identify 1/f noise that is the subject of interest, along with the underlying physical mechanisms that cause this particular noise.

#### <u>1.2 Noise Classification in MOSFETs</u>

Noise intrinsic to a device or circuit is a consequence of minute current or voltage fluctuations that are fundamentally associated with the discrete nature of electron charge transfer or motion of the charge carriers. Several mechanisms exist that generate noise in semiconductors leading to a unique spectral power distribution in the frequency domain. This section gives a brief overview of the types of noise encountered in MOSFETs.

## Thermal Noise:

This type of noise is intrinsic to all resistors and is found in MOSFETs due to the resistive nature of the channel. It is also known as Johnson-Nyquist or thermal agitation noise and is caused by the random thermal motion of charge carriers. Its magnitude depends on the temperature but is independent of frequency or the current through the resistor as long as the thermal equilibrium is maintained. In general, the power spectral density of such a noise is given based on Nyquist theorem as [38]:

$$S_{\nu}(f) = 4kTR \tag{1.1}$$

where, k is the Boltzman constant, T is the equilibrium temperature, and R represents the linear resistor.

Figure 1.4 Typical MOSFET white noise at high frequencies. The device here is a TaSiN/HfO<sub>2</sub>/SiO<sub>2</sub> MOSFET biased at  $V_g = 1.13$  V and  $V_d = 0.05$  V and at T = 100 K.

In case of a MOSFET, the resistance of the channel is not a constant and depends on the operating point i.e., gate and drain voltages.

In most circuit simulators the thermal noise model for a MOSFET in the saturation region is given as [39]

$$S_{I}(f) = 4kT(\frac{2}{3}g_{m})$$

(1.2)

where,  $g_m$  is the device transconductance at a particular operating point. This noise is a major contributor to total noise at high frequencies in a MOSFET. Figure 1.4 depicts white noise in a MOSFET that constitutes thermal noise as well as shot noise that is described next.

### Shot Noise:

In semiconductor devices, shot noise is a bias dependent component that is present whenever there is a DC flow due to random movement of charge carriers across a potential barrier. This is in view of the fact that the average current appearing as DC is actually a summation of discrete random independent pulses of electron charge flow. The time-domain mean squared deviation from the mean DC value is known as shot noise. The expression for shot noise power spectral density takes the following form [38,40]:

$$S_I(f) = 2qI \tag{1.3}$$

Due to the flat nature of its frequency spectrum, shot noise qualifies as another source of white noise and is indistinguishable from the thermal noise (Figure 1.4) as far as the spectral form is concerned. In a MOSFET, shot noise is generally associated with substrate to channel leakage currents that cause drain current fluctuations. In addition, the high gate leakage currents in ultra-thin MOSFETs can be a source of shot noise [41,42,43].

#### Generation-Recombination Noise:

As the name suggests, this noise is associated with the fluctuations in the generation and recombination of carriers by localized centers that can be seen as fluctuations in the current passing through the semiconductor. In a MOSFET, the localized defect states may exist in the semiconductor bulk or the gate dielectric that cause trapping/detrapping of inversion layer carriers and exhibiting a predominant characteristic trapping time constant,  $\tau$ . The general expression for G-R noise is given as [38],

$$S(f) = 4\overline{\Delta N^2} \frac{\tau}{1 + (2\pi f\tau)^2}$$

(1.4)

where,  $\overline{\Delta N^2}$  represents the variance of the charge carriers, f is the frequency and  $\tau$  is the characteristic time constant of the defect band. The power spectral density plot of pure G-R noise is that of a Lorentzian spectrum, which is constant at low frequencies and drops down as f<sup>-2</sup> above the corner frequency defined by the characteristic time constant as  $f_c = 1/2\pi\tau$ . Figure 1.5 depicts an example of G-R noise component in a MOSFET noise spectrum.

Figure 1.5 G-R noise in TaSiN/HfO<sub>2</sub>/SiO<sub>2</sub> MOSFET biased at  $V_g = 0.5$  V and  $V_d = 0.05$  V and at T = 125 K. The Lorentzian approximation is provided for reference.

RTS Noise:

RTS stands for Random Telegraph Signal. This kind of noise is observed in small area devices appearing in time domain as discrete random voltage or current pulses. In frequency domain, RTS is characterized by a Lorentzian spectrum given by [44,45]:

$$S_{I_d}(f) = \frac{4(\Delta I_d)^2}{(\bar{\tau}_0 + \bar{\tau}_1)[(1/\bar{\tau}_0 + 1/\bar{\tau}_1)^2 + (2\pi f)^2]}$$

(1.5)

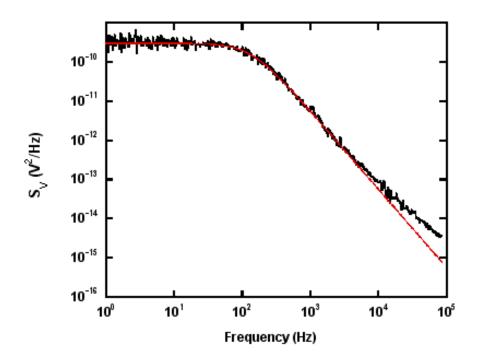

where,  $\bar{\tau}_0$  and  $\bar{\tau}_1$  have a Poisson distribution and they represent the mean capture and emission times. Alternatively, they can be considered as the average time durations in low and high states. However, unlike G-R noise, the amplitude spectrum of a well defined RTS does not have a Gaussian distribution. In MOSFETs, RTS noise can be found in high quality small area SiO<sub>2</sub>/Si systems where the oxide can have a single defect state causing trapping/de-trapping of a single channel carrier resulting in a Lorentzian spectrum as shown in Figure 1.6. When the number of traps is higher, the resulting Lorentzians can correspond to a unique or distributed time constants. Consequently, when summed up, the resulting spectrum can be one of G-R noise or can yield a 1/f like spectrum as discussed in the next section.

Figure 1.6 Voltage noise power spectrum of small area SiO<sub>2</sub> MOSFET biased at  $V_g$  = 1.3 V and  $V_d$  = 0.05 V along with a Lorentzian fitting [46].

Flicker Noise:

This is a major source of noise at low frequencies and is found in almost all electronic materials and semiconductor devices like metal films, Ionic Solutions, MOSFETs, BJTs, JFETs, MESFETs and junction diodes [38,47, 48,49, 50]. It is also known as 1/f noise since the noise power spectral density is inversely proportional to frequency that can be typically expressed as [38]:

$$\frac{S_I(f)}{I^2} = \frac{C}{f^{\sigma}}$$

(1.6)

where, I is the current flowing through the device, C is a constant typical of the device

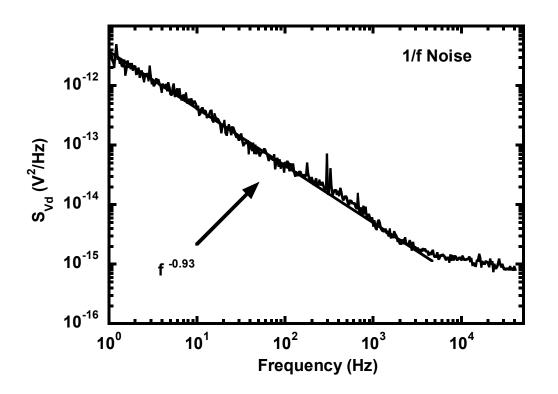

Figure 1.7 1/f noise in TaSiN/HfO<sub>2</sub>/SiO<sub>2</sub> MOSFET biased at  $V_g = 1.13$  V and  $V_d = 0.05$  V and at T = 100 K.

and  $\sigma$  ranges from 0.7 to 1.4, in general. A typical spectrum of 1/f noise is plotted in Figure 1.7 for a MOSFET.

Although this noise is a universal phenomenon in active devices, several mechanisms cause 1/f noise. Bulk mobility fluctuations and inversion carrier number fluctuations are the two popular approaches to explain the occurrence of flicker noise in MOSFETs. According to the Hooge's model, low frequency noise is a bulk phenomenon resulting from the fluctuations in the mobility of channel carriers.

It was shown that flicker noise and RTS share a common origin in that the summation of several RTS with distributed characteristic time constants can result in 1/f noise [45,51,52]. According to McWhorter's theory [53], flicker noise is a surface phenomenon caused by the fluctuations in the number of charge carriers in the inversion layer due to capture and emission by traps in the gate insulator. Although experimental data exists to support both the models, the universality of either model is often debatable. However, the Unified Flicker Noise model that is based on Mc Whorter's theory is widely used in circuit simulators today [54].

The aforementioned models are discussed in detail following the general noise theory in Chapter 2. Additionally, the measurement procedure for obtaining 1/f noise, I-V and split C-V data is explained.

In Chapter 3, the data, analysis and discussion of 1/f noise in n,p-channel poly-Si gated MOSFETs with three different gate dielectrics- HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>, HfAlO<sub>x</sub> are presented. The devices had either 1 nm or 4 nm SiO<sub>2</sub> interfacial layer thus giving us an opportunity to understand the effects of interfacial layer thickness. Chapter 4 deals with 1/f noise in TaSiN and TiN gated MOSFETs with HfO<sub>2</sub> gate dielectric. A comparative study of 1/f noise behavior is presented for metal and poly-Si gated devices. In addition, the effect of the deposition method on interfacial layer quality and thus the overall device performance is studied.

In Chapter 5, 1/f noise modeling is revisited in view of the multi-layered gate stack in high-k MOSFETs. The 'Multi-Stack Unified Noise' model (MSUN) is derived to better model/characterize the 1/f noise in high-k MOSFETs by taking the non-uniform trap density profile and other physical properties of the constituent gate dielectrics in to account. Experimental data is presented for TaSiN/HfO<sub>2</sub>/SiO<sub>2</sub> gate stack in the 78-350 K range to validate the MSUN model. Finally, the MSUN model is expressed in terms of surface potential based parameters for inclusion in to the circuit simulators.

Chapter 6 provides a summary of conclusions of this dissertation work.

## CHAPTER 2

## 1/f NOISE IN MOSFETs

#### 2.1 Introduction

The random voltage or current fluctuations at the device terminals can arise from noise sources that are intrinsic to the device or by extraneous means like equipment and environmental interferences. The MOSFET intrinsic noise, specifically 1/f noise, is the main object of this work. In this chapter, a relationship between the microscopic noise sources in the channel and the current fluctuations that they cause at the MOSFET terminals is deduced at first. Subsequently, a general noise power spectral density expression is derived that can be used to calculate thermal, 1/f or gate induced noise [55,56,57,58]. Later, the Hooge's mobility fluctuations and Unified Flicker Noise models are introduced. The final model expressions for these are arrived at by using the noise power spectral density expression mentioned before. Finally, details are provided about the measurement set-up and the experimental procedure used to perform low frequency noise, split C-V and DC characterization.

## 2.2 General MOSFET Noise Theory

Noise that is intrinsic to a semiconductor device is associated with the locally occurring random fluctuations of carrier density or velocity that cause voltage or current fluctuations at the device terminals. In a MOSFET, there can be several local noise

sources in the channel that contribute to the variations in the drain current. In the following, the derivation of the general expression for the current noise power spectral density at the MOSFET output terminals from all the microscopic noise sources in the channel, is presented [55,56,59].

The drain current expression for a MOSFET can be given as,

$$I_d = g(x)\frac{dV}{dx}$$

(2.1)

where,  $g(x) = -W\mu_{eff}(qN(x))$ , *W* is the width (cm),  $\mu_{eff}$  is the carrier mobility (cm<sup>2</sup>/Vs), *q* is the electronic charge (C), *N(x)* is the channel carrier density per unit area at point *x* along the length (cm<sup>-2</sup>) and *V* is the channel quasi-Fermi potential (V).

Considering that a current noise source h(x,t) that is present at a position xalong the channel would cause a flow of noise current  $\Delta I_d(t)$  in the external leads, the total terminal current would be  $I_d + \Delta I_d(t)$ . Then the quasi-Fermi potential is  $V + \Delta V(t)$ , where  $\Delta V(t)$  is the fluctuating potential along the channel. Noting that both the conductance g(x) and V are functions of x, g(x) can be represented as a function of V, so that g(x)=g(V). The terminal drain current that includes the noise current can now be written as,

$$I_d + \Delta I_d(t) = g(V + \Delta V(t)) \frac{d(V + \Delta V(t))}{dx} + h(x, t)$$

(2.2)

For small fluctuations, the right hand side of (2.2) can be expanded using Taylor series and by neglecting the second order terms we have,

$$I_{d} + \Delta I_{d}(t) \approx g(V) \frac{dV}{dx} + g(V) \frac{d\Delta V(t)}{dx} + \frac{dg}{dV} \frac{dV}{dx} \Delta V(t) + h(x,t)$$

$$= g(V) \frac{dV}{dx} + \frac{d}{dx} (g(V) \Delta V(t)) + h(x,t)$$

(2.3)

In (2.3),  $g(V)\frac{dV}{dx} = I_d$  so that,

$$\Delta I_d(t) = \frac{d}{dx}(g(V)\Delta V(t)) + h(x,t)$$

(2.4)

Integrating (2.4) with respect to x and applying the short circuit boundary condition that  $\Delta V(t) = 0$  at x=0 and x=L,

$$\Delta I_{d}(t) = \frac{1}{L} \int_{0}^{L} h(x, t) dx$$

(2.5)

Equation (2.5) gives the relation between the current noise sources in the channel and the current fluctuation at the device terminals. The next step would be to find the autocorrelation function of the drain terminal noise current which is given as,

$$\overline{\Delta I}_{d}(t)\Delta I_{d}(t+s) = \overline{\frac{1}{L}\int_{0}^{L}h(x,t)dx\frac{1}{L}\int_{0}^{L}h(x',t+s)dx'} = \frac{1}{L^{2}}\int_{0}^{L}\overline{\int_{0}^{L}h(x,t)h(x',t+s)}dxdx' \quad (2.6)$$

From Wiener-Khintchine theorem [60, 61], the drain current noise power spectral density can be obtained as the Fourier transform of the autocorrelation function in (2.6) and is written as,

$$S_{I_d}(f) = \frac{1}{L^2} \int_{0}^{L} \int_{0}^{L} S_h(x, x', f) dx dx'$$

(2.7)

where,  $S_h(x, x', f)$  is the cross power spectral density between noise at points x and x' in the channel. Here, the noise sources are assumed to be spatially uncorrelated so

that,  $S_h(x, x', f)$  is a Dirac impulse located at the point (x' - x) and can be represented as,

$$S_{h}(x, x', f) = F(x', f)\delta(x' - x)$$

(2.8)

Using (2.8) in (2.7) gives,

$$S_{I_d}(f) = \frac{1}{L^2} \int_0^L F(x, f) dx$$

(2.9)

Evaluating (2.9) in an elemental section between x and  $x+\Delta x$ , the power spectral density of the local current fluctuations can be obtained as,

$$S_{\Delta I_d}(x,f) = \frac{1}{\Delta x^2} \int_0^{\Delta x} F(x,f) dx = \frac{F(x,f)}{\Delta x}$$

(2.10)

Therefore,

$$F(x, f) = S_{\Delta I_{\perp}}(x, f)\Delta x \tag{2.11}$$

Finally, the total drain current noise spectral density is given by,

$$S_{I_d}(f) = \frac{1}{L^2} \int_0^L S_{\Delta I_d}(x, f) \Delta x dx$$

(2.12)

Eq. (2.12) would be used in deriving the 1/f noise expressions in the next section.

#### 2.3 1/f Noise Models

1/f noise in MOSFETs has been studied for over a few decades now. The exact physical origin responsible for this kind of noise is not completely understood and is still open to debate. In the following, description is provided for the two widely popular models that are used to explain the 1/f noise in MOSFETS namely- Hooge's Bulk Mobility Fluctuation Model and the Unified Flicker Noise Model.

#### Hooge's Model:

According to Hooge's theory, low frequency noise is a bulk phenomenon originating from the fluctuations in the carrier mobility due to lattice scattering in the semiconductor bulk [62, 63]. The empirical formula takes the following form [48]:

$$\frac{S_{I_d}}{I_d^2} = \frac{\alpha_H}{fWLN}$$

(2.13)

Here,  $S_{Id}$  is the power spectral density,  $I_d$  is the drain current,  $\alpha_H$  is Hooge's parameter that is a dimensionless universal constant (~2x10<sup>-3</sup>), N is the inversion carrier density per unit area, f is the frequency, L and W are the MOSFET channel length and width, respectively.

In the case of a MOSFET, the final expression for current noise power spectral density is derived as follows. Considering an infinitesimal channel length  $\Delta x$  with  $\Delta N = NW\Delta x$  carriers, the spectral density for the local current fluctuations is given using (2.13) as [57],

$$S_{\Delta I_d}(x,f) = \frac{\alpha_H}{fW\Delta xN} I_d^2$$

(2.14)

The total current noise spectral density is then obtained by integrating  $S_{\Delta I_d}(x, f)$  along the channel according to (2.12) and can written as,

$$S_{I_d}(f) = \frac{\alpha_H I_d}{fL^2} \int_0^L \left( \frac{I_d}{W \Delta x N} \right) \Delta x dx$$

(2.15)

Using  $I_d = -W\mu_{eff}(qN(x))\frac{dV}{dx}$ ,

$$S_{I_d}(f) = \left(\frac{\alpha_H q \mu_{eff} I_d}{fL^2}\right)_0^L dV$$

(2.16)

Considering  $V_d$  as the drain to source voltage, the Hooge's model expression for the total current noise spectral density is given by,

$$S_{I_{d}}(f) = \frac{\alpha_{H} q \mu_{eff} I_{d} V_{d}}{fL^{2}}$$

(2.17)

It should be noted that although  $\alpha_H$  was a constant in the original Hooge's formula, it was later observed by many researchers that  $\alpha_H$  was lower than  $2 \times 10^{-3}$  and had a weak gate bias dependence. This prompted a modification to the original model allowing  $\alpha_H$ to assume lower values when other scattering mechanisms are present according to [64],

$$\alpha_{H} = 2 \times 10^{-3} \left(\frac{\mu_{eff}}{\mu_{latt}}\right)^{2}$$

(2.18)

where, the total mobility is given by Matthiessen's rule as,

$$\frac{1}{\mu_{eff}} = \frac{1}{\mu_{latt}} + \frac{1}{\mu_{imp}}$$

(2.19)

In (2.19)  $\mu_{latt}$  and  $\mu_{imp}$  represent the mobility due to lattice scattering and impurity scattering, respectively.

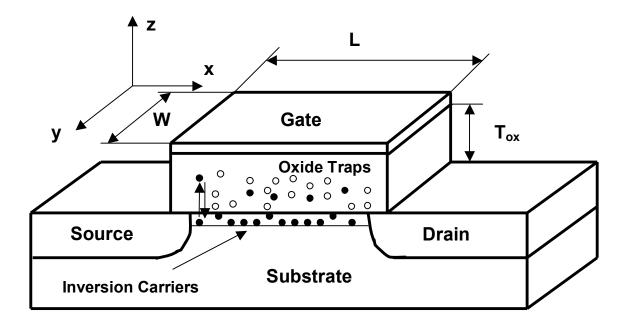

## Unified Flicker Noise Model:

According to the "Unified Flicker Noise Model" [54], the traps in the gate oxide cause trapping and de-trapping of charge carriers establishing communication with the channel as shown in Figure 2.1. The two-fold effect that arises is the fluctuations in the channel carrier number and the fluctuations in the mobility due to the Coulombic

interactions between the charged trap sites and the channel carriers. These fluctuations in the carrier number along with the correlated mobility fluctuations cause 1/f noise.

Figure 2.1 Cross section of a MOSFET showing trapping/de-trapping of inversion layer carriers by traps in the gate oxide.

To derive the model expression, we begin with the drain current in a MOSFET that is given as,

$$I_d = W\mu_{eff}(qN)E_x \tag{2.20}$$

where W is the width (cm),  $\mu_{eff}$  is the carrier mobility (cm<sup>2</sup>/Vs), q is the electronic charge (C), N is the channel carrier density per unit area (cm<sup>-2</sup>) and  $E_x$  is the field along the channel (V/cm). The coordinates considered here are as follows: x is along the channel from source to drain; y is along the width of the device; z is into the gate oxide.

Considering an infinitesimal channel length  $\Delta x$ , the fractional change in the local drain current can be written as [54],

$$\frac{\delta I_{d}}{I_{d}} = -\left(\frac{1}{\Delta N}\frac{\delta\Delta N}{\delta\Delta N_{ot}} \pm \frac{1}{\mu_{eff}}\frac{\delta\mu_{eff}}{\delta\Delta N_{ot}}\right)\delta\Delta N_{ot}$$

(2.21)

where,  $\Delta N = NW\Delta x$  is the inversion charge in the area,  $W\Delta x$ ,  $\Delta N_{ot} = N_{ot}W\Delta x$  is the number of occupied traps in the corresponding area in the gate oxide  $(W\Delta x)$ ,

$$R = \left| \frac{\delta \Delta N}{\delta \Delta N_{ot}} \right|$$

is the coupling coefficient between the fluctuations in the channel charge