# CMOS VCO & LNA IMPLEMENTED BY AIR-SUSPENDED ON-CHIP RF MEMS INDUCTORS

by

## VARUN K SHENOY

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

THE UNIVERSITY OF TEXAS AT ARLINGTON

AUGUST 2007

### **ACKNOWLEDGEMENTS**

I am deeply grateful to my research advisor Professor Sungyong Jung for his guidance. His insights have been a constant inspiration for me.

I would also like to thank all the members of the AMIC lab: Tim, Shin-Chih, Ju-Ching, Prasanna, Ritesh and David.

Finally I would like to thank my parents, my sisters, and God. They are the source of strength and reason for my endeavor.

July 19, 2007

#### **ABSTRACT**

# CMOS VCO & LNA IMPLEMENTED BY AIR-SUSPENDED ON-CHIP RF MEMS INDUCTORS

Publication No. \_\_\_\_\_

Varun K Shenoy, M.S.

The University of Texas at Arlington, 2007

Supervising Professor: Dr. Sungyong Jung

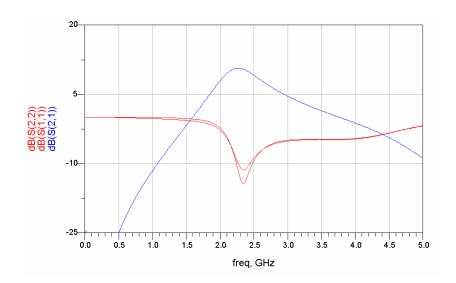

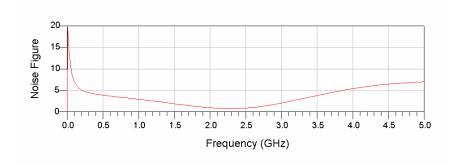

In this thesis, a CMOS 2.4 GHz Low noise amplifier (LNA) and Voltage-controlled oscillator (VCO) was designed and simulated. These circuits were designed to operate in the 2.4GHz Industrial Scientific Medicine (ISM) band and to achieve Bluetooth and Wifi standard specifications. High-Q RF MEMS air-suspended circular spiral inductors are used in both circuits. High-Q inductors give the circuit better performance parameters including higher gain, lower noise figure and narrower bandwidth. The integration of these RF MEMS inductors onto RF circuit chips was carried out using the UV-LIGA technique and an additive pattern transfer technique such as electroplating. The LNA maintains a gain of 10dB and noise figure of 0.8dB at 2.4 GHz. With an input reflection coefficient of -10.8dB and output reflection

coefficient of -12.93dB, the LNA matches successfully with  $50\Omega$  load at 2.4 GHz. The VCO maintains an average output swing of 1.95V in a frequency range of 2.94GHz to 2.2GHz achieving a 740GHz of tuning range.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                       | ii   |

|----------------------------------------|------|

| ABSTRACT                               | iii  |

| LIST OF ILLUSTRATIONS                  | viii |

| LIST OF TABLES                         | xi   |

| Chapter                                |      |

| 1. INTRODUCTION                        | 1    |

| 2. BACKGROUND                          | 5    |

| 2.1 Wireless Narrowband systems        | 5    |

| 2.1.1 Bluetooth                        | 7    |

| 2.1.1.1 Bluetooth Modulation format    | 9    |

| 2.1.1.2 Frequency Band                 | 10   |

| 2.1.2 IEEE 802.11b                     | 12   |

| 2.1.2.1 IEEE 802.11b modulation format | 13   |

| 2.1.2.2 Frequency band                 | 14   |

| 2.3 LNA topologies and analysis        | 14   |

| 2.3.1 Resistive Termination            | 15   |

| 2.3.2 Shunt-Series Feedback            | 16   |

| 2.3.3 Common Gate                      | 16   |

| 2.3.4 Inductive Degeneration                     | 17 |

|--------------------------------------------------|----|

| 2.3.5 Transformer Feedback                       | 21 |

| 2.4 VCO Topologies                               | 22 |

| 2.4.1 Oscillator Classification                  | 22 |

| 2.4.2 Oscillator models                          | 23 |

| 2.4.2.1 Feedback Model of oscillators            | 23 |

| 2.4.2.2 Negative Resistance model of oscillators | 24 |

| 2.4.3 Ring Oscillator                            | 26 |

| 2.4.4 LC based Oscillator                        | 27 |

| 2.4.5 LC Oscillator Topologies                   | 28 |

| 2.4.6 Phase noise fundamentals                   | 32 |

| 2.4.6.1 Definition of phase noise                | 32 |

| 2.4.6.2 Effects of phase noise                   | 33 |

| 3. IMPLEMENTATION                                | 36 |

| 3.1 RF MEMS Inductors                            | 36 |

| 3.1.1 Fabrication                                | 37 |

| 3.1.2 Modeling of Spiral inductor                | 39 |

| 3.1.2.1 Inductance                               | 40 |

| 3.1.2.2 Resistance                               | 40 |

| 3.1.2.3 Series Capacitance                       | 41 |

| 3.1.3.4 Substrate parasitics                     | 41 |

| 3.1.3 Inductor parameter extraction42                               |

|---------------------------------------------------------------------|

| 3.1.4 Comparison: RF MEMS inductor vs.  Monolithic on-chip Inductor |

| 3.2 Low Noise Amplifier Design                                      |

| 3.2.1 Design Procedure                                              |

| 3.2.2 Simulation Results                                            |

| 3.2.2.1 LNA with RF MEMS inductor                                   |

| 3.2.2.2 LNA with Planar monolithic inductor54                       |

| 3.2.3 Layout & Chip Photo                                           |

| 3.3 Voltage Controlled Oscillator Design                            |

| 3.3.1 Design Procedure 60                                           |

| 3.3.1.1 Resonator tank design60                                     |

| 3.3.1.2 Varactor Design60                                           |

| 3.3.1.3 Buffer design 63                                            |

| 3.3.1.4 Cross-coupled transistor and current source design65        |

| 3.3.2 Simulation Results                                            |

| 3.3.2.1 VCO with RF MEMS inductor                                   |

| 3.3.2.1 VCO with planar monolithic inductor68                       |

| 3.3.3 Layout and Chip photo                                         |

| 4. CONCLUSION73                                                     |

| REFERENCES75                                                        |

| BIOGRAPHICAL INFORMATION79                                          |

# LIST OF ILLUSTRATIONS

| Fig | gure                                                                                                                                          | Page |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

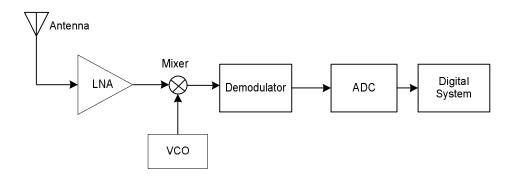

|     | 1.1 Block diagram of generic analog RF receiver.                                                                                              | 2    |

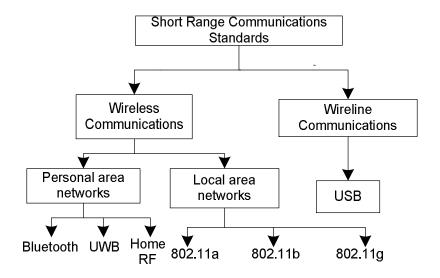

|     | 2.1 Short-range communication standards                                                                                                       | 7    |

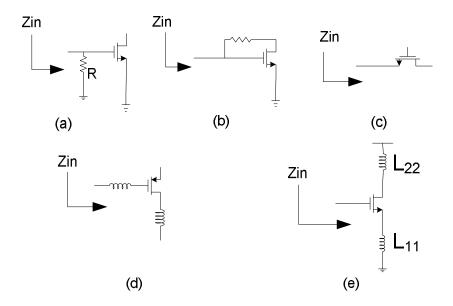

|     | 2.2 LNA architectures (a) Resistive termination (b) Shunt-series feedback (c) Common gate (d) Inductive degeneration (e) Transformer feedback | 15   |

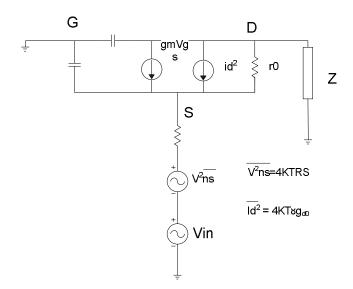

|     | 2.3 Small-signal model of a common gate LNA                                                                                                   | 17   |

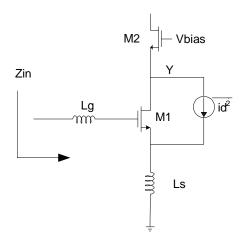

|     | 2.4 Common source cascode LNA                                                                                                                 | 18   |

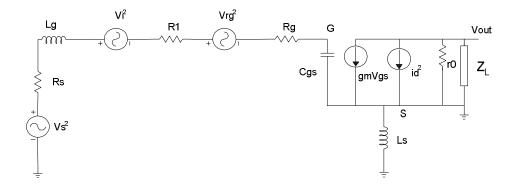

|     | 2.5 Small signal equivalent model of Inductive degeneration LNA                                                                               | 19   |

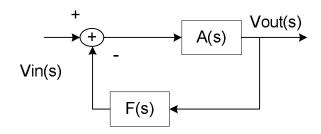

|     | 2.6 Block diagram of negative feedback systems                                                                                                | 23   |

|     | 2.7 a simple negative gm oscillator block diagram                                                                                             | 24   |

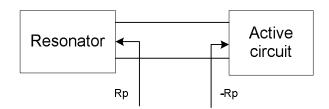

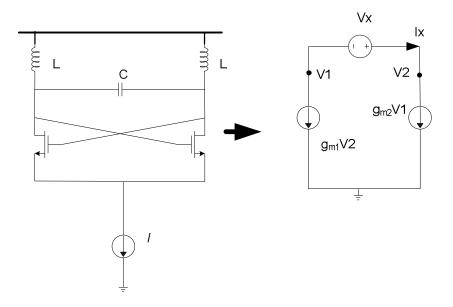

|     | 2.8 Negative resistance provided by cross coupled transistors in LC oscillators.                                                              | 25   |

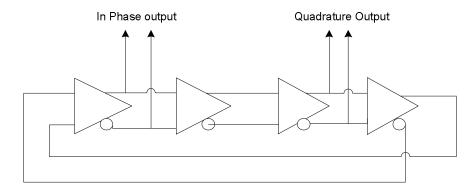

|     | 2.9 Differential 4-stage ring oscillator with quadrature output                                                                               | 27   |

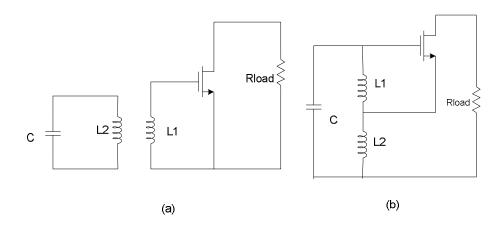

|     | 2.10 (a) A simple Armstrong oscillator (b) A simple Hartley oscillator                                                                        | 29   |

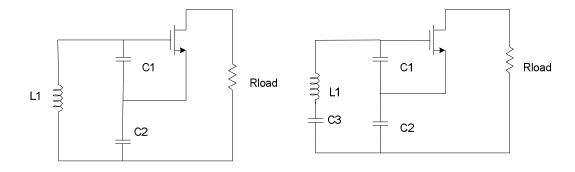

|     | 2.11 (a) A simple Colpitts oscillator (b) A simple Clapp oscillator                                                                           | 29   |

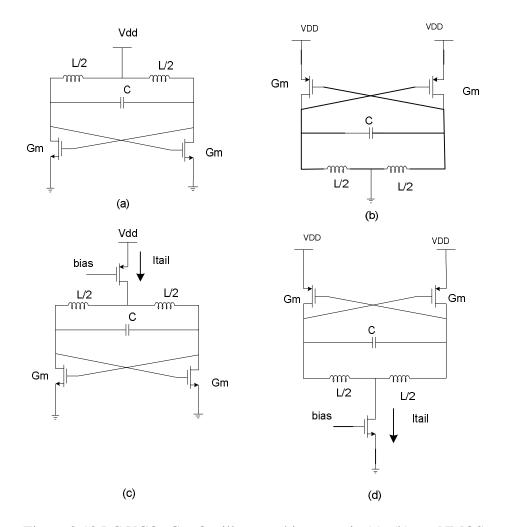

|     | 2.12 LC VCO -Gm Oscillator architectures in (a), (b) are NMOS implementations and (c), (d) PMOS implementations                               | 31   |

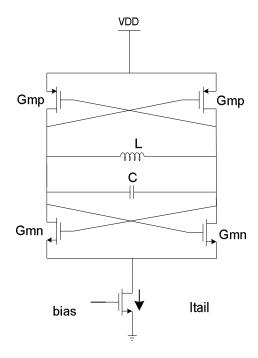

|     | 2.13 LC VCO -Gm oscillator in complementary implementation                                                                                    | 32   |

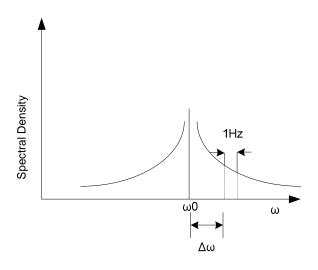

|     | 2.14 Definition of phase noise                                                                                                                | 33   |

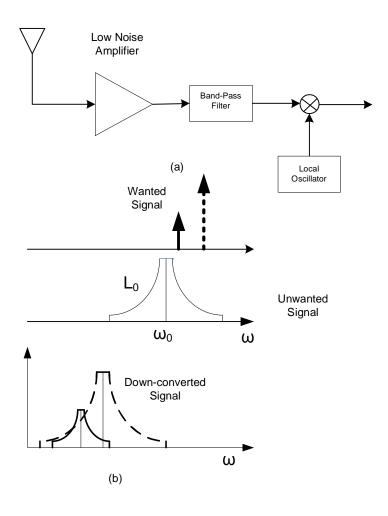

|     | 2.15 (a)Block diagram of wireless receiver (b)Effect of phase noise on receive path                                                           | 34   |

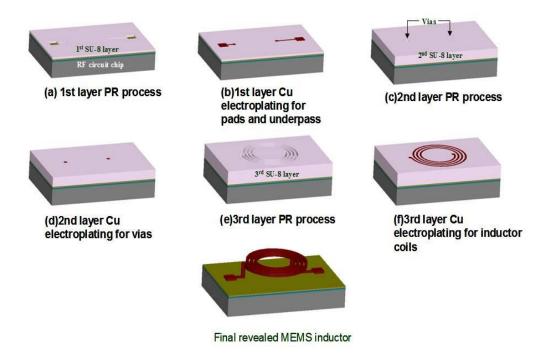

| 3.1 Process sequence for post-IC integration of RF MEMS inductors                              | 38 |

|------------------------------------------------------------------------------------------------|----|

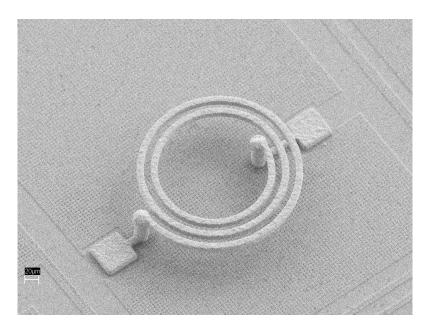

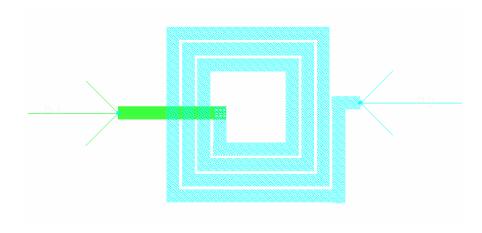

| 3.2 SEM microphotograph of micro-machined air-suspended circular spiral inductor               | 39 |

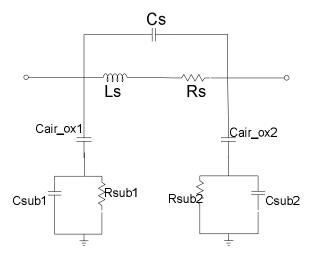

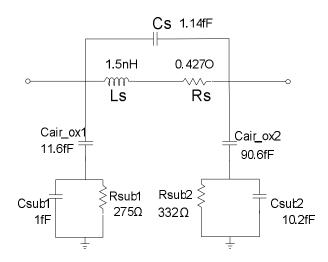

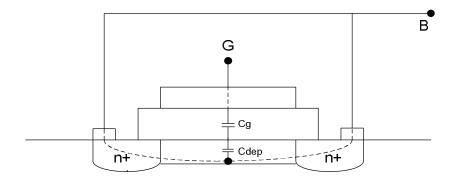

| 3.3 Lumped equivalent model of an on-chip inductor                                             | 40 |

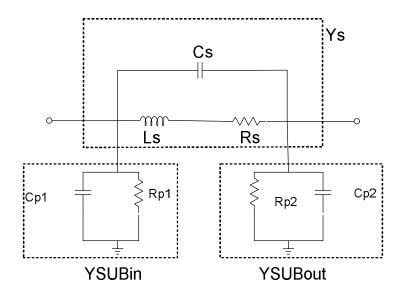

| 3.4 Pi-network inductor model                                                                  | 43 |

| 3.6 MEMS inductor model with extracted parameters                                              | 45 |

| 3.7 Monolithic planar inductor layout in ADS                                                   | 46 |

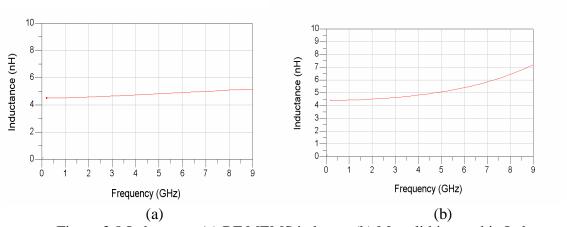

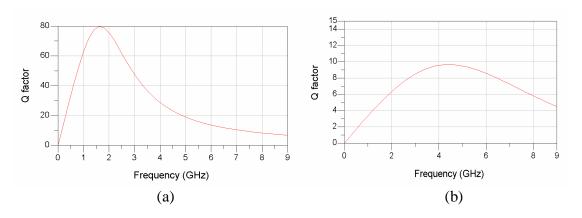

| 3.8 Inductance (a) RF MEMS inductor (b) Monolithic on-chip Inductor                            | 46 |

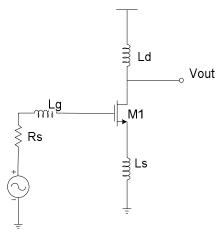

| 3.10 Low noise amplifier topology                                                              | 48 |

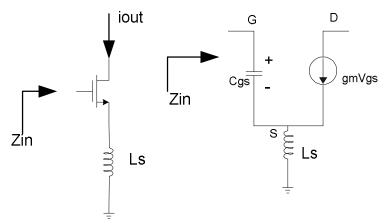

| 3.11 Input impedance of low noise amplifier and its small signal equivalent circuit            | 50 |

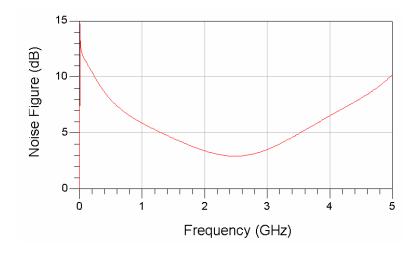

| 3.13 Noise Figure of LNA with RF MEMS inductor.                                                | 52 |

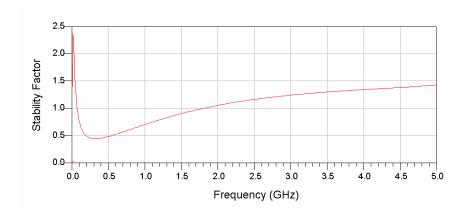

| 3.14 Stability factor of LNA with RF MEMS inductor                                             | 53 |

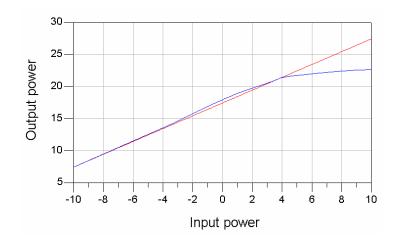

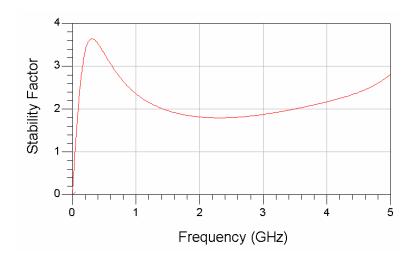

| 3.15 Output power versus Input power at 2.4 GHz                                                | 53 |

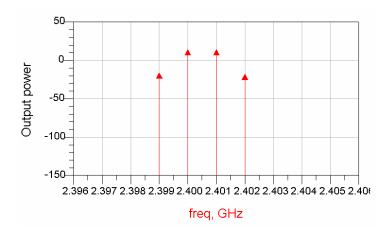

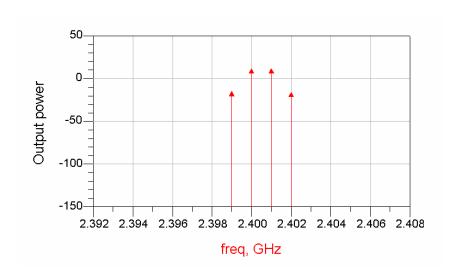

| 3.16 Third order inter-modulation components at the output                                     | 54 |

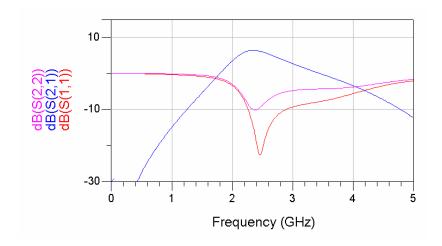

| 3.17 S parameter simulation result of LNA with planar monolithic inductor                      | 54 |

| 3.18 Noise Figure of LNA with planar monolithic inductor                                       | 55 |

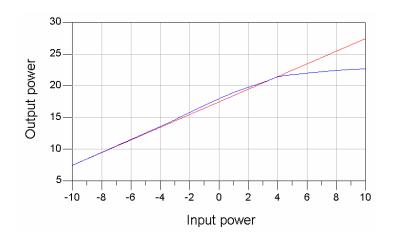

| 3.19 Stability Factor of LNA with planar monolithic inductor                                   | 55 |

| 3.20 Output power versus Input power at 2.4 GHz                                                | 56 |

| 3.21 Third order inter-modulation components at the output                                     | 56 |

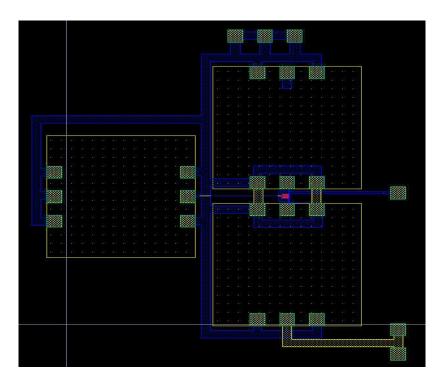

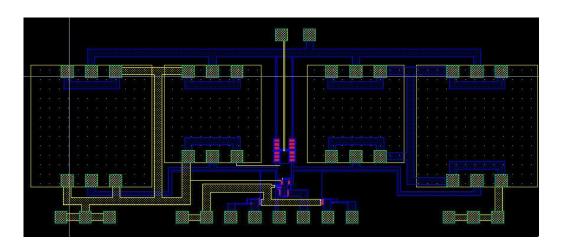

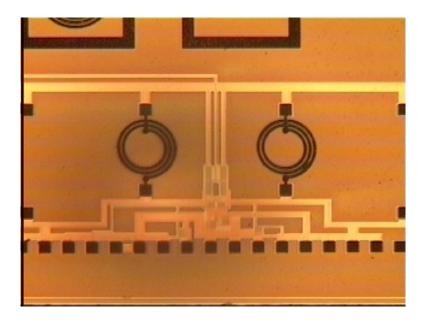

| 3.22 Layout for the LNA with RF MEMS inductors                                                 | 58 |

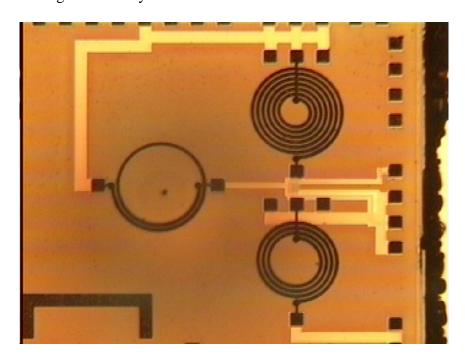

| 3.23 SEM microphotograph of the LNA after post-integration of micro-machined RF MEMS Inductors | 58 |

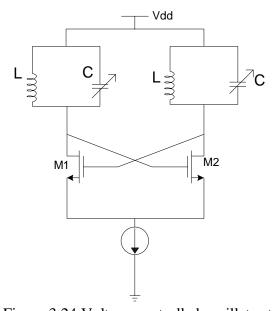

| 3.24 Voltage controlled oscillator topology                                                    | 59 |

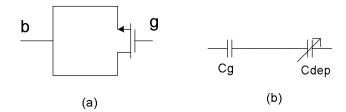

| 3.25 (a) MOS varactor (b) simplified MOS varactor model                                        | 61 |

|------------------------------------------------------------------------------------------------|----|

| 3.26 simplified MOS varactor model                                                             | 62 |

| 3.27 MOS varactor implemented in the VCO in this work                                          | 62 |

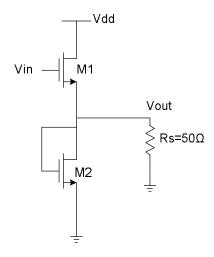

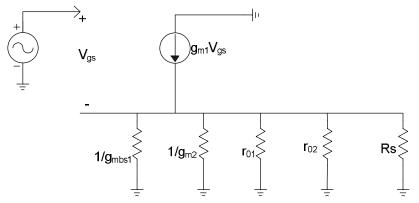

| 3.28 Source follower buffer                                                                    | 64 |

| 3.29 Small signal equivalent circuit of the source-follower                                    | 64 |

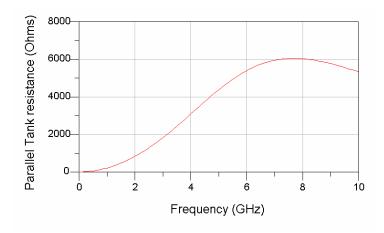

| 3.30 parallel resistance of resonant tank vs frequency                                         | 65 |

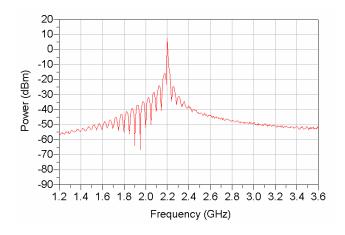

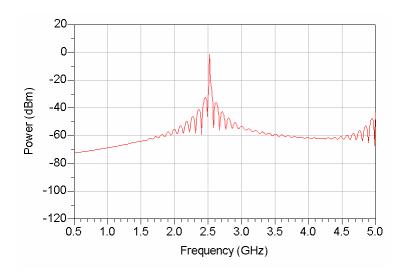

| 3.31 Power spectral density of VCO with RF MEMS inductor (Vcont=5V)                            | 67 |

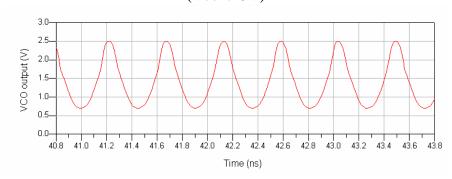

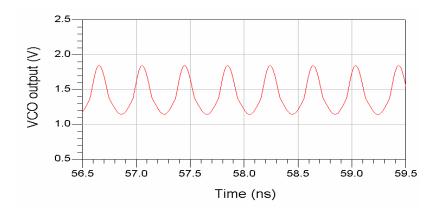

| 3.32 Transient output of VCO with RF MEMS inductor (Vcont=5V)                                  | 67 |

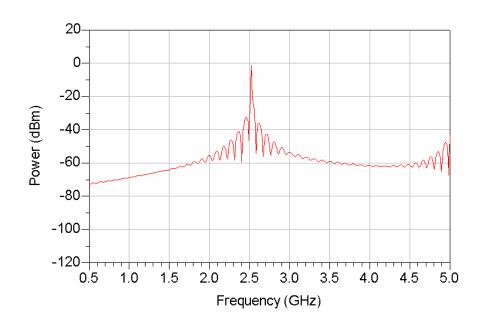

| 3.33 Power spectral density of VCO with RF MEMS inductor (Vcont=0V)                            | 68 |

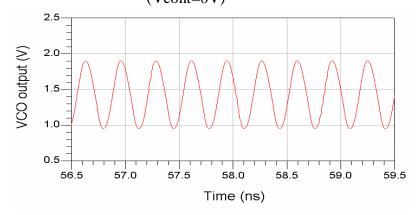

| 3.34 Transient output of VCO with RF MEMS inductor (Vcont=0V)                                  | 68 |

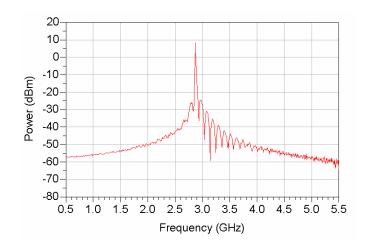

| 3.35 Power spectral density of VCO with RF MEMS inductor (Vcont=5V)                            | 69 |

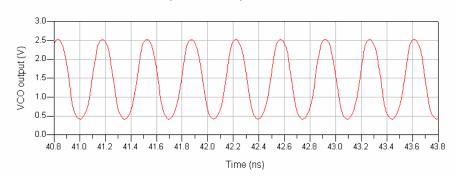

| 3.36 Transient output of VCO with RF MEMS inductor (Vcont=5V)                                  | 69 |

| 3.37 Power spectral density of VCO with RF MEMS inductor (Vcont=0V)                            | 70 |

| 3.38 Transient output of VCO with RF MEMS inductor (Vcont=0V)                                  | 70 |

| 3.39 Layout of VCO                                                                             | 71 |

| 3.40 SEM microphotograph of the VCO after post-integration of micro-machined RF MEMS Inductors | 72 |

# LIST OF TABLES

| T | able 2.1 Overall system specifications for Bluetooth and WLAN | Page |

|---|---------------------------------------------------------------|------|

|   | 2.1 Overall system specifications for Bluetooth and WLAN      | 11   |

|   | 3.1 Target Specifications                                     | 48   |

|   | 3.2 TSMC 0.35µm process technology parameters                 | 48   |

|   | 3.3 Component values used in design of LNA                    | 51   |

|   | 3.4 LNA performance                                           | 57   |

|   | 3.5 Performance comparison with recent 2.4 GHz LNAs           | 57   |

|   | 3.6 Target specifications for VCO                             | 60   |

|   | 3.7 Minimum and Maximum capacitance of Varactor               | 63   |

|   | 3.8 Tuning range of VCO with RF MEMS inductor                 | 68   |

|   | 3.9 Tuning range of VCO with planar monolithic inductors      | 70   |

|   | 3.10 Performance comparison with recent VCOs                  | 71   |

#### CHAPTER 1

#### INTRODUCTION

With increase in demand for wireless communication applications, the wireless circuit design technologies and techniques have made remarkable progress in recent years. Technology scaling has brought both advantages and disadvantages in design of RF transceivers for portable wireless devices. Introduction of wireless communication standards has been a driving force in continual research and development. The two most widespread short-range communication standards are Bluetooth and IEEE802.11b.

Bluetooth has been introduced to connect any home or office appliances such as personal computers, printers with data rate at 1 Mbps. It is aimed to operate in even the smallest battery-powered devices, the Bluetooth specification calls for a small form factor, low power consumption and low cost. The range and speed of the technology is kept low to ensure maximum battery life and minimum incremental cost for devices incorporating the technology. Bluetooth creates a Wireless Personal Area Network (WPAN) consisting of all the Bluetooth-enabled electronic devices immediately surrounding a user, wherever that user may be located.

IEEE 802.11b (popularly known as Wifi) proliferated due to explosive growth of internet users, providing high data rate wireless communications up to 11 Mbps. IEEE 802.11 a/b uses the unlicensed spectrum for transmission and thus it must use spread spectrum techniques. This process increases the communication channel's interference immunity or the processing gain, decreases interference between multiple

users and increases the ability to re-use the spectrum. 802.11b uses the 2.400 GHz to 2.483 GHz spectrum. 802.11 is the wireless extension of 802.3 and supports all the underlying protocols that Ethernet uses.

Figure 1.1 Block diagram of generic analog RF receiver.

Both Bluetooth and IEEE 802.11 operate at RF frequency 2.4 GHz. A simple RF receiver architecture is shown in Figure 1.1. The signal received at the antenna, is amplified by a Low-noise amplifier (LNA), the spectrum is translated to a lower frequency by a Mixer to facilitate subsequent demodulation. The lower frequency is decided by the Voltage-controlled oscillator (VCO). The demodulated signal is then converted to a digital signal by an Analog to Digital converter (ADC) which is then processed by the digital system.

The VCOs and LNAs are critical components in RF systems. The cost effective CMOS VCOs and LNAs are very attractive to be used for recent wireless communication systems in CMOS technology.

For VCOs, an inductor – capacitor resonator (LC tank) determines the center frequency of oscillation. Designing this LC tank is the most critical factor for the whole performance of VCOs. Performance of these energy storage components directly relate

to the quality of outputs such as phase noise and noise factor. Then, the high phase noise cause poor signal detection at receiver part. In order to minimize the phase noise, using high-Q inductors and capacitors is very encouraged for VCO studying.

For LNAs, at high frequency, CMOS technology has a problem of signal loss through conducting silicon substrate. The signal loss through drain or source to substrate parasitics degrades the noise factor and gain. Also impedance matching is an important issue for maximum power transfer. Use of inductors in LNA topologies is common and effective for input impedance matching. The noise contributed by the parasitics of the inductors degrades the noise factor and gain. In order to minimize noise factor and maximize gain high-Q inductors are required.

The inductors obtained from standard silicon processes cannot provide high-Q factors sufficient for high-performance VCOs and LNAs. The reasons for low-Q factors come from thin metal layers (ohmic loss) and high substrate coupling (eddy-current loss) in standard silicon processes. High resistive loss of these layers plays an important role in determining the Qs in lower frequency regions below a peak-Q frequency.

Integration of MEMS and radio-frequency (RF) microelectronics, called RF-MEMS, has been rapidly gaining a great interest as an enabling technology to realize high-performance on-chip RF-MEMS passives by replacing off-chip passives in communication systems. In order to reduce such resistive loss, low-resistivity material is used and the metal layers are much thicker than the skin depth in RF-MEMS inductors. And because the substrate loss is caused by the electromagnetic coupling of passive devices residing right on top of the conductive silicon substrate, air-suspended

inductors from the substrate realized by RF MEMS technique can significantly reduce such substrate coupling loss and obtain a high-Q inductor.

In chapter 2, there is a brief description of Bluetooth and Wifi standards. This is followed by analysis of common LNA and VCO topologies. In chapter 3, detailed design procedure of LNA and VCO is discussed, with respective simulation results, layout and chip photos. Tables comparing the results of LNAs and VCOs designed with air-suspended RF MEMS inductors and monolithic planar inductors are shown. Chapter 4 concludes the thesis work.

#### CHAPTER 2

### **BACKGROUND**

In recent years mobile digital devices such as personal digital assistants, mobile phones, digital cameras, and laptops have entered the consumer market with high demand. These devices require powerful short-range communication methods for data exchange between each other and connections with printers or local area network (LAN) access. The communication methods can be based on cable connections, radio links, or infrared links. Each has its individual strengths and weaknesses. Each technology found its way into various products.

### 2.1 Wireless Narrowband systems

Infrared transmission based on the Infrared Data Association (IrDA) standard enables fast connection establishment due to its point-and-shoot characteristic. With the high baud rates of up to 16Mb/s, it is well suited to applications that require high performance as hoc point-to-point connections. Examples include downloading of pictures from digital camera to laptop or paying for meal in a company's cafeteria with your mobile phone via IrDA port. IrDA standards have been widely implemented in laptops, computers and PDAs. Recently, due to high cost, the technology was difficult to implement.

Radio-based short-range wireless (SRW) communication is an alternative class of technologies designed primarily for indoor use over very short distances. It provides fast (10-100Mb/s) and low cost, cable-free connections to the internet. SRW communication has transmission powers of several microwatts up to milliwatts yielding a communication range between 10 and 100 meter. SRW provides connectivity to portable devices such as laptops, PDAs, cell phones and others. Short-range communications standards fall into two broad but overlapping categories: personal area networks (PAN) and local area networks (LAN).

Wireless PAN Technologies emphasize low cost and low power consumption, at the expense of range and peak speed. In a typical wireless PAN application, a short wireless link less than 10 meters, replaces a computer serial cable or USB cable. Standards, such as Bluetooth and Home-RF, have been created to regulate short-range wireless communications. Bluetooth has been implemented in most of the mobile devices used today. Bluetooth transmits data through solid nonmetal objects and supports a nominal link range of 10cm-10m at a moderate baud rate up to 720kb/s (raw data rate is 1Mb/s) [1]. An optional high power mode in the current specifications allows for ranges up to 100m. Bluetooth is a point to multipoint communication system. It supports connections of two devices as well as ad hoc networking between several devices. To prevent unauthorized access, Bluetooth requires authentication and encryption mechanisms, which hampers speed of establishing a connection. It is good for applications where mobility is a key requirement.

Wireless LAN technologies emphasize a higher peak speed and longer range at the expense of cost and power consumption. Typically, wireless LANs provides links from portable laptops to a wired LAN access point. To date, 802.11b has gained acceptance rapidly as a wireless LAN standard. Its nominal open-space range is 100m and peak over-the-air speed is 11Mb/s. Users get maximum available speeds of about 5.5Mb/s. Other communication standards offer even higher data rates, like 802.11a and 802.11g.

Figure 2.1 Short-range communication standards

#### 2.1.1 Bluetooth

Bluetooth technology was developed to serve as a short-range wireless voice and data link between electronic devices such as PCs, notebook computers, handhelds and PDAs, mobile phones and digital cameras. It is aimed to operate in even the smallest battery-powered devices, the Bluetooth specification calls for a small form factor, low power consumption and low cost. The range and speed of the technology is

kept low to ensure maximum battery life and minimum incremental cost for devices incorporating the technology. Bluetooth is creates a Wireless Personal Area Network (WPAN) consisting of all the Bluetooth-enabled electronic devices immediately surrounding a user, wherever that user may be located. This project is supported by a special interest group formed by several companies that lead technological development.

Specifications of Bluetooth give its limitations and possibilities. Bluetooth operates in the 2.4GHz frequency range which is free for use to everyone globally. This frequency provides an effective data rate of 720 Kbit/s. There are multiple categories of transmission strengths which decide the use and the energy efficiency of these devices. Bluetooth achieves its functionality through its modulation and packet scheme. This is also known as Gaussian Frequency Shift Keying (GFSK).

Bluetooth hops to one of 79 different channels (US and Europe) with a repetitive process that keeps errors to a minimum. This packet hopping technique leads to interference with 802.11b technology. The channel hopping feature of Bluetooth is the main cause of its low power consumption, error correction and the distinct topology that it can support. Bluetooth divides the data to be sent into packets. Each packet is sent within a 625us slot. A frame is includes a transmit slot and a receive slot, providing full duplex communication between a master and a slave in one time frame. To avoid noise and other interferences, Bluetooth hops to one of 79 different channels each time frame. The channel that it hops to is determined by a Master ID and the previous channel number. This algorithm repeats. If there is severe noise between 2.408GHz and

2.410GHz, it is avoided the most of the time. There is little to no time contention between masters within reach of each other which might result in the masters picking up the same channels simultaneously. Due to the channel hopping mechanism, interference is kept to a minimum despite the highly dense network.

Bluetooth was originally conceived by Ericsson in 1994, during a study to examine alternatives to cables that linked mobile phone accessories. Ericsson has a strong history in short range wireless, being a key pioneer of the European DECT cordless telecommunications standard, which is largely based on their earlier proprietary DCT900 technology. In February 1998, the Bluetooth SIG (Special Interest Group) was founded by a small core of major companies - IBM, Intel, Nokia, Toshiba and Ericsson - to work together to develop the technology and to subsequently promote its widespread commercial acceptance [1].

## 2.1.1.1 Bluetooth Modulation format

The modulation format is Gaussian Frequency Shift Keying (GFSK) with a bandwidth\*bit-time product (BT) of 0.5. The modulation index is between 0.28 and 0.35. For the 1Mbps data rate in Bluetooth, frequency deviation is from 140 to 175kHz. The data signal is passed through a Gaussian filter. The Gaussian filtered signal is modulates with the carrier signal with frequency shift keying. The BT specification of 0.5 in the Bluetooth standard is chosen by keeping the trade-off between minimizing the inter-symbol interference while maximizing the bandwidth.

#### 2.1.1.2 Frequency Band

Bluetooth operates in the 2.4GHz Industrial Scientific Medicine (ISM) band. The range of this frequency band is 2400MHz – 2483.5MHz. With Time Division Duplex (TDD), transmitter and receiver share the same frequency band. To regulate the use of the same spectrum simultaneously by several devices, the device needs to spread the power of its transmissions across the ISM band. Two methods used for spreading out the power are: direct sequence spread spectrum (DSSS) and frequency-hopping spread spectrum (FHSS). DSSS smears a transmission across a wide range of frequencies at low power. FHSS spectrum uses a small bandwidth but changes (or hops) frequency after each packet.

Bluetooth uses frequency-hopping spread spectrum. The spectrum is split into 79 channels of 1MHz each. Transmitters change frequencies 1,600 times every second. To prevent two linked pairs to collide on the same channel, one pair hops off to a new frequency and re-transmits any lost data. This technique also minimizes the risk that portable phones or baby monitors will disrupt Bluetooth services, since the effect of any interferer on a particular frequency will last only a tiny fraction of a second. Bluetooth uses the master's device ID to algorithmically determine the frequency hopping pattern. This algorithm generates a unique pattern that is quite random and exhibits an extremely long repeat cycle.

Table 2.1 Overall system specifications for Bluetooth and WLAN

| oscillator 1MHz -80dBc/Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Table 2.1 Overall system specifications for Diuctooth and WLAN |                |                     |                       |                    |            |           |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------|---------------------|-----------------------|--------------------|------------|-----------|--|

| Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                |                | •                   |                       | 2.11b              |            |           |  |

| Channel Spacing         1MHz         5MHz           NO. of Channels         79*         13**           Modulation Scheme         GFSK         DBPSK (1Mbps)           Multiple Access         FHSS         DQPSK (1 Mbps)           Multiple Access         FHSS         DSSS           CCK         Duplexing         TDD         TDD           Minimum Sensitivity         -70dBm         ≥ -76dBm           Maximum Sensitivity         -20dBm         -10dBm           QoS         BER 10-4         FER = 8 * 10-2 (≈ BER 10-3)           Input Noise         -114dBm         -100.6dBm           Input SNR         44dB         24.6dB           Required SNR         23dB         10.4dB)           1.6dB (2Mbps, PG *** of 7.4dB)         11dB (5.5Mbps)           1.1dB (11Mbps)         23dB (2Mbps)           Overall System NF (NF system)         21dB         23dB (2Mbps)           13.6dB (5.5Mbps)         10.6dB (11Mbps)           Overall System IIP3 system         -17.5dBm         -30.5dBm (1Mbps)           -22.5dBm (11Mbps)         -22.5dBm (11Mbps)           Phase noise of local oscillator         Offset Phase Noise         Offset Phase Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Frequency Bands                                                |                |                     | 2.4 ~ 2.4835GHz       |                    |            |           |  |

| NO. of Channels         79*         13**           Modulation Scheme         GFSK         DBPSK (1Mbps)           Multiple Access         FHSS         DQPSK (2 & 5.5Mbps)           QPSK (11 Mbps)         DSSS         CCK           Duplexing         TDD         TDD           Minimum Sensitivity         -70dBm         ≥ -76dBm           Maximum Sensitivity         -20dBm         -10dBm           QoS         BER 10-4         FER = 8 * 10-2 (≈ BER 10-3)           Input Noise         -114dBm         -100.6dBm           Input SNR         44dB         24.6dB           Required SNR         23dB         10.4dB)           1.6dB (2Mbps, PG *** of 7.4dB)         1.6dB (2Mbps, PG *** of 7.4dB)           11dB (5.5Mbps)         14dB (11Mbps)           Overall System NF (NF system)         21dB         23dB (2Mbps)           13.6dB (2Mbps)         13.6dB (5.5Mbps)           10.6dB (11Mbps)         -30.5dBm (1Mbps)           Overall System IIP3 system         -17.5dBm         -30.5dBm (2Mbps)           IIP3 system         -17.5dBm         -22.5dBm (11Mbps)           Phase noise of local oscillator         Offset         Phase Noise         Offset         Phase Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bandwidth                                                      | 1MHz           |                     | 22MHz                 |                    |            |           |  |

| Modulation Scheme         GFSK         DBPSK (1Mbps) DQPSK (2 & 5.5Mbps) QPSK (11 Mbps)           Multiple Access         FHSS         DSSS CCK           Duplexing         TDD         TDD           Minimum Sensitivity         -70dBm         ≥ -76dBm           Maximum Sensitivity         -20dBm         -10dBm           QoS         BER 10-4         FER = 8 * 10-2 (≈ BER 10-3)           Input Noise         -114dBm         -100.6dBm           Input SNR         44dB         24.6dB           Required SNR         23dB         1.6dB (1Mbps, PG *** of 10.4dB)           1.6dB (2Mbps, PG*** of 7.4dB)         11dB (5.5Mbps)           14dB (11Mbps)         26.6dB (1Mbps)           23dB (2Mbps)         13.6dB (5.5Mbps)           10.6dB (11Mbps)         -29dBm (2Mbps)           0verall System         -17.5dBm         -29dBm (2Mbps)           IIP3 system         -17.5dBm         -29dBm (2Mbps)           -24dBm (5.5Mbps)         -22.5dBm (11Mbps)           Phase noise of local oscillator         Offset         Phase Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Channel Spacing                                                | 1MHz           |                     | 5MHz                  |                    |            |           |  |

| Modulation Scheme         GFSK         DQPSK (2 & 5.5Mbps) QPSK (11 Mbps)           Multiple Access         FHSS         DSSS CCK           Duplexing         TDD         TDD           Minimum Sensitivity         -70dBm         ≥ -76dBm           Maximum Sensitivity         -20dBm         -10dBm           QoS         BER 10 <sup>-4</sup> FER = 8 * 10 <sup>-2</sup> (≈ BER 10 <sup>-3</sup> )           Input Noise         -114dBm         -100.6dBm           Input SNR         44dB         24.6dB           Required SNR         23dB         1.6dB (1Mbps, PG *** of 7.4dB)           11dB (5.5Mbps)         11dB (5.5Mbps)           11dB (5.5Mbps)         13.6dB (11Mbps)           Overall System NF (NF system)         21dB         23dB (2Mbps)           13.6dB (11Mbps)         -29dBm (2Mbps)           10.6dB (11Mbps)         -29dBm (2Mbps)           -24dBm (5.5Mbps)         -22.5dBm (11Mbps)           Phase noise of local oscillator         Offset         Phase Noise           Offset         Phase Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NO. of Channels                                                | 79*            |                     | 13**                  |                    |            |           |  |

| Multiple Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                | GFSK           |                     | DBPSK (1Mbps)         |                    |            |           |  |

| Multiple Access         FHSS         DSSS CCK           Duplexing         TDD         TDD           Minimum Sensitivity         -70dBm         ≥ -76dBm           Maximum Sensitivity         -20dBm         -10dBm           QoS         BER 10 <sup>-4</sup> FER = 8 * 10 <sup>-2</sup> (≈ BER 10 <sup>-3</sup> )           Input Noise         -114dBm         -100.6dBm           Input SNR         44dB         24.6dB           Required SNR         23dB         -2dB (1Mbps, PG *** of 10.4dB)           1.6dB (2Mbps, PG *** of 7.4dB)         11dB (5.5Mbps)           14dB (11Mbps)         26.6dB (1Mbps)           23dB (2Mbps)         13.6dB (5.5Mbps)           10.6dB (11Mbps)         -29dBm (2Mbps)           -29dBm (2Mbps)         -29dBm (2Mbps)           -24dBm (5.5Mbps)         -22.5dBm (11Mbps)           Phase noise of local oscillator         Offset Phase Noise Offset Phase Noise         Offset Phase Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Modulation Scheme                                              |                |                     | ` <u>*</u> /          |                    |            |           |  |

| Duplexing         TDD         TDD           Minimum Sensitivity         -70dBm         ≥ -76dBm           Maximum Sensitivity         -20dBm         -10dBm           QoS         BER 10 <sup>-4</sup> FER = 8 * 10 <sup>-2</sup> (≈ BER 10 <sup>-3</sup> )           Input Noise         -114dBm         -100.6dBm           Input SNR         44dB         24.6dB           Required SNR         23dB         -2dB ( 1Mbps, PG *** of 10.4dB)           1.6dB ( 2Mbps, PG*** of 7.4dB)         11dB ( 5.5Mbps)           11dB ( 5.5Mbps)         14dB ( 11Mbps)           Overall System NF (NF system)         23dB ( 2Mbps)           13.6dB ( 5.5Mbps)         10.6dB ( 11Mbps)           Overall System IIP3 system         -17.5dBm         -30.5dBm ( 1Mbps)           Overall System IIP3 system         -17.5dBm         -29dBm ( 2Mbps)           Phase noise of local oscillator         Offset Phase Noise Offset Phase Noise Offset Phase Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                |                |                     |                       | Mbps)              |            |           |  |

| Duplexing         TDD         TDD           Minimum Sensitivity         -70dBm         ≥ -76dBm           Maximum Sensitivity         -20dBm         -10dBm           QoS         BER 10⁴         FER = 8 * 10²           (≈ BER 10³)         (≈ BER 10³)           Input Noise         -114dBm         -100.6dBm           Input SNR         44dB         24.6dB           Required SNR         23dB         10.4dB)           1.6dB ( 2Mbps, PG *** of 7.4dB)         11dB ( 5.5Mbps)           11dB ( 5.5Mbps)         14dB ( 11Mbps)           Overall System NF (NF system)         21dB         23dB (2Mbps)           13.6dB (5.5Mbps)         13.6dB (5.5Mbps)           10.6dB (11Mbps)         -29dBm (2Mbps)           11P3 system         -17.5dBm         -30.5dBm (1Mbps)           Overall System         -17.5dBm (2.5Mbps)         -29dBm (2.5Mbps)           10.6dB (11Mbps)         -24dBm (5.5Mbps)           -22.5dBm (11Mbps)         -22.5dBm (11Mbps)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Multiple Access                                                | F              | FHSS                | DSS                   | S                  |            |           |  |

| Minimum Sensitivity         -70dBm         ≥ -76dBm           Maximum Sensitivity         -20dBm         -10dBm           QoS         BER 10⁴         FER = 8 * 10²           (≈ BER 10³)         (≈ BER 10³)           Input Noise         -114dBm         -100.6dBm           Input SNR         44dB         24.6dB           Required SNR         23dB         10.4dB           1.6dB (2Mbps, PG *** of 7.4dB)         11dB (5.5Mbps)           11dB (5.5Mbps)         14dB (11Mbps)           26.6dB (1Mbps)         23dB (2Mbps)           13.6dB (5.5Mbps)         10.6dB (11Mbps)           Overall System IIP3 system         -17.5dBm         -30.5dBm (1Mbps)           IIP3 system         -17.5dBm         -29dBm (2Mbps)           IIP3 system         -24dBm (5.5Mbps)         -22.5dBm (11Mbps)           Phase noise of local oscillator         Offset         Phase Noise         Offset         Phase Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                |                |                     | CCI                   | K                  |            |           |  |

| Maximum Sensitivity         -20dBm         -10dBm           QoS         BER $10^4$ FER = $8*10^2$ (≈ BER $10^3$ )           Input Noise         -114dBm         -100.6dBm           Input SNR         44dB         24.6dB           Required SNR         23dB         -2dB (1Mbps, PG *** of 10.4dB)           1.6dB (2Mbps, PG *** of 7.4dB)         11dB (5.5Mbps)           11dB (5.5Mbps)         14dB (11Mbps)           Overall System NF (NF system)         21dB         23dB (2Mbps)           13.6dB (5.5Mbps)         10.6dB (11Mbps)           Overall System IIP3 system         -17.5dBm         -30.5dBm (1Mbps)           IIP3 system         -17.5dBm         -29dBm (2Mbps)           IIP3 system         -17.5dBm         -29dBm (5.5Mbps)           -22.5dBm (11Mbps)         -22.5dBm (11Mbps)           Phase noise of local oscillator         Offset         Phase Noise         Offset         Phase Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Duplexing                                                      | r              | ΓDD                 | TDI                   | O                  |            |           |  |

| QoS       BER $10^{-4}$ FER = $8*10^{-2}$ (≈ BER $10^{-3}$ )         Input Noise       -114dBm       -100.6dBm         Input SNR       44dB       24.6dB         Required SNR       23dB       -2dB ( 1Mbps, PG *** of 10.4dB)         1.6dB ( 2Mbps, PG *** of 7.4dB)       11dB ( 5.5Mbps)         11dB ( 5.5Mbps)       14dB ( 11Mbps)         26.6dB (1Mbps)       23dB (2Mbps)         (NF system)       13.6dB (5.5Mbps)         10.6dB (11Mbps)       10.6dB (11Mbps)         -29dBm (2Mbps)       -24dBm (5.5Mbps)         -22.5dBm (11Mbps)       -22.5dBm (11Mbps)         Phase noise of local oscillator       Offset Phase Noise Offset Pha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Minimum Sensitivity                                            | -7             | 0dBm                | ≥ -76d                | Bm                 |            |           |  |

| Input Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Maximum Sensitivity                                            | -2             | 0dBm                |                       |                    |            |           |  |

| Input Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | QoS                                                            | BE             | ER 10 <sup>-4</sup> | FER = 8               | * 10 <sup>-2</sup> |            |           |  |

| Input SNR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                |                |                     | $(\approx BER$        | $10^{-3}$ )        |            |           |  |

| Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Input Noise                                                    | -11            | 14dBm               | -100.6                | dBm                |            |           |  |

| Required SNR   23dB   10.4dB   1.6dB ( 2Mbps,PG*** of 7.4dB )   11dB ( 5.5Mbps )   14dB ( 11Mbps )   14dB ( 11Mbps )   26.6dB ( 1Mbps )   23dB ( 2Mbps )   13.6dB ( 5.5Mbps )   10.6dB ( 11Mbps )   10.6dB (  | Input SNR                                                      | 44dB           |                     | 24.6dB                |                    |            |           |  |

| 1.6dB ( 2Mbps,PG*** of 7.4dB)   11dB ( 5.5Mbps)   14dB ( 11Mbps)   14dB ( 11Mbps)   26.6dB ( 1Mbps)   23dB ( 2Mbps)   13.6dB ( 5.5Mbps)   10.6dB ( 11Mbps)   10.6dB  |                                                                | uired SNR 23dB |                     | -2dB (1Mbps           | , PG *** of        |            |           |  |

| 7.4dB    11dB ( 5.5Mbps)   14dB ( 11Mbps)   26.6dB ( 11Mbps)   26.6dB ( 11Mbps)   23dB ( 2Mbps)   13.6dB ( 5.5Mbps)   10.6dB ( 11Mbps)   10.6dB   | Required SNR                                                   |                |                     | 10.4dB)               |                    |            |           |  |

| 11dB ( 5.5Mbps)   14dB ( 11Mbps)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                |                |                     | 1.6dB ( 2Mbp          | s,PG*** of         |            |           |  |

| 14dB ( 11Mbps)   26.6dB (1Mbps)   23dB (2Mbps)   13.6dB (5.5Mbps)   10.6dB (11Mbps)   10.6dB (11Mbps  |                                                                |                |                     |                       | ,                  |            |           |  |

| Overall System NF (NF system)         21dB         26.6dB (1Mbps)           13.6dB (2Mbps)         13.6dB (5.5Mbps)           10.6dB (11Mbps)         10.6dB (11Mbps)           Overall System         -17.5dBm         -29dBm (2Mbps)           IIP3 system         -24dBm (5.5Mbps)         -24dBm (5.5Mbps)           Phase noise of local oscillator         Offset         Phase Noise         Offset         Phase Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                |                |                     | ,                     | * '                |            |           |  |

| Overall System NF (NF system)         21dB         23dB (2Mbps)           13.6dB (5.5Mbps)         10.6dB (11Mbps)           Overall System         -17.5dBm         -30.5dBm (1Mbps)           IIP3 system         -29dBm (2Mbps)         -24dBm (5.5Mbps)           -24dBm (5.5Mbps)         -22.5dBm (11Mbps)           Phase noise of local oscillator         Offset         Phase Noise         Offset         Phase Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                |                |                     | -                     |                    |            |           |  |

| ( NF system)  Overall System  IIP3 system  Phase noise of local oscillator  OVERAGE (NF system)  -30.5dBm (1Mbps)  -30.5dBm (1Mbps)  -29dBm (2Mbps)  -24dBm (5.5Mbps)  -24dBm (5.5Mbps)  -22.5dBm (11Mbps)  Offset Phase Noise Offset Phase Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                |                |                     |                       | <b>.</b>           |            |           |  |