# A FRAMEWORK FOR IMPROVING THE PERFORMANCE OF APPLICATION SERVERS IN NEXT GENERATION NETWORKS

by

SUMANTRA RAJ KUNDU

Presented to the Faculty of the Graduate School of The University of Texas at Arlington in Partial Fulfillment of the Requirements for the Degree of

DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT ARLINGTON August 2007

# Copyright $\bigodot$ by SUMANTRA RAJ KUNDU ~2007

All Rights Reserved

#### ACKNOWLEDGEMENTS

During my four years at the University of Texas at Arlington, I had the opportunity to interact and work with many people. Foremost I would like to thank my Ph.D. mentors, Dr. Sajal Das and Mr. Kalyan Basu. The constant suggestions and feedback I received from Dr. Das during the research and writing of this thesis greatly influenced the quality of the work. Most of the experiments in networking and operating systems would not have been possible without his excellent support and encouragement. Throughout my Ph.D. studies it has been an intellectual challenge to work with Mr. Kalyan Basu. Much of my interest and problem abstraction skills in performance analysis and queuing theory concepts I owe to him. His incisive technical comments, encouragement, and unflagging enthusiasm have been a constant driving force in many of the projects we have worked during the course of the Ph.D.

I would also like to thank my thesis committee members, Dr. Hao Che, Dr. Mohan Kumar, and Dr. Yonghe Liu for taking the time to learn about my work. During the summer of 2006 and aftermath I had the chance to work with Mr. Bill Stouder-Studenmund and Mr. Thor Lancet Simon of NetBSD foundation. Their clear thinking and guidance about I/O schedulers and the virtual memory (VM) helped me define the stochastic algorithms we have implemented inside the NetBSD OS. It has always been a pleasure to work with them. I am grateful for the assistance from all the members of our research group at Center for Research in Wireless Mobility and Networking (CReWMaN) lab, especially Sourav Pal.

I would like to thank my fiancee, Indrani, for always being there with me. Her patience and bearing has been astounding. Finally, I would like to say a big 'thank-you' to my parents, sisters, and all my relatives for giving me the courage to follow my dreams. This work has been supported by the National Science Foundation (NSF) under grant IIS-0326505 and from Google Summer of Code, 2006.

July 18, 2007

#### ABSTRACT

# A FRAMEWORK FOR IMPROVING THE PERFORMANCE OF APPLICATION SERVERS IN NEXT GENERATION NETWORKS

Publication No. \_\_\_\_\_

SUMANTRA RAJ KUNDU, Ph.D. The University of Texas at Arlington, 2007

Supervising Professors: Sajal K. Das and Kalyan Basu

Next generation networks (NGNs) such as IP Multimedia Subsystem (IMS) are completely built on the Internet Protocol (IP) suite. This has made IP the de facto standard for data networking, voice over IP (VoIP), and media rich applications such as streaming multimedia, ringtones, multi-player gaming, and high-definition video conferencing for remote interaction. A primary feature of such converged networks is that they use the same IP-based network for simultaneously delivering voice, video, and data. Such services are provided on application servers built using industry standard Advanced Telecom Computing Architecture (ATCA) based blade computing units with various flavors of commodity open source operating systems like Linux, xBSD, and OpenSolaris.

However, real-time and latency sensitive applications such as streaming multimedia require that the entire network path of packet delivery from the originating server to the end host be properly and appropriately configured so as to avoid unnecessary delay and jitter in the data transfer mechanisms. With the ease of deployment comes the challenge of delivering such rich multimedia applications in NGNs since there exists no separate paths for voice and data as present in existing circuit-switched public switched telephone network (PSTN). Packet delivery in such converged architectures involves interaction between the storage disks, operating system (OS), network interface cards (NICs), and the various switches and routers - each of which is independently capable of introducting delay in the data transfer mechanism.

In this dissertation, we focus on understanding and improving the performance of application servers present in high traffic content delivery networks (CDNs) and hoisting latency sensitive applications with heavy I/O requirements. We start by identifying an architectural framework for traffic characterization that is expected to provide insights about the composition and dynamics (e.g., average packet size and data rate, protocol composition) of network traffic present in CDNs. Once the nature and type of network traffic arriving at the NICs have been identified, we attempt to identify packet processing bottlenecks due to the interaction between the NICs, OS, and the underlying hardware. We propose a closed form queuing model that aims to understand the packet processing capabilities of the NICs based on the available computing resources. We have shown that there exist limits beyond which a computing unit cannot process packets without overloading the CPU. Since the performance of latency sensitive processes can be negatively impacted by delays of the storage network and by the dynamics of the OS, we present solutions for prioritizing the reader processes and tweaking the pagedaemon in open source OS. Based on our implementation in the NetBSD kernel, we have observed an approximate 15%-20% improvement in the transactions per second (TPS) of latency sensitive applications. Finally, we believe that our framework and approach of identifying the basic components in network data transfer mechanisms are for most part generic and can be used for performance tuning and deploying application servers in NGNs with a variety of different services.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS iii |        |         |                                                                  |    |  |

|----------------------|--------|---------|------------------------------------------------------------------|----|--|

| ABSTRACT v           |        |         |                                                                  |    |  |

| LIST OF FIGURES      |        |         |                                                                  |    |  |

| LΙ                   | ST O   | F TAB   | LES                                                              | XV |  |

| Cł                   | napter |         |                                                                  |    |  |

| 1.                   | INT    | RODU    | CTION                                                            | 1  |  |

|                      | 1.1    | Motiva  | ation                                                            | 3  |  |

|                      | 1.2    | The P   | $\operatorname{roblem}$                                          | 4  |  |

|                      | 1.3    | Overv   | iew of Our Novel Approach                                        | 7  |  |

|                      | 1.4    | Contri  | butions of The Dissertation                                      | 9  |  |

|                      | 1.5    | Outlin  | e of the Dissertation                                            | 12 |  |

| 2.                   |        |         | TECTURAL FRAMEWORK FOR ACCURATE CHARACTERI-<br>F NETWORK TRAFFIC | 14 |  |

|                      | 2.1    | Comp    | onents of Traffic Characterization                               | 15 |  |

|                      |        | 2.1.1   | Existing Approaches for Traffic Characterization                 | 16 |  |

|                      |        | 2.1.2   | Salient Features of Our Approach to Traffic Characterization     | 17 |  |

|                      | 2.2    | Defini  | tions                                                            | 18 |  |

|                      |        | 2.2.1   | A Motivating Example                                             | 20 |  |

|                      | 2.3    | Traffic | Characterization: Problem Statement                              | 21 |  |

|                      | 2.4    | Measu   | rement Framework: Architecture, Algorithms, and Modeling         | 22 |  |

|                      |        | 2.4.1   | Flow Collection Unit (FCU)                                       | 24 |  |

|                      |        | 2.4.2   | How to Distinguish SLF FlowID from LLF FlowID?                   | 25 |  |

|                      |        | 2.4.3   | Storing and Accessing FlowIDs of SLFs                            | 26 |  |

|                      |        |         |                                                                  |    |  |

|    |      | 2.4.4   | Determining the Parameters of Flow Collection Unit (FCU) $\ldots$                                    | 28 |

|----|------|---------|------------------------------------------------------------------------------------------------------|----|

|    |      | 2.4.5   | Flow Management Unit (FMU)                                                                           | 34 |

|    | 2.5  | An On   | line Framework for Identifying LLFs                                                                  | 36 |

|    | 2.6  | Offline | Estimation Using Kernel Density Estimator                                                            | 39 |

|    |      | 2.6.1   | Estimating the PDF of Sampled Data                                                                   | 39 |

|    | 2.7  | Experi  | mental Results                                                                                       | 41 |

|    |      | 2.7.1   | Identifying the LLFs                                                                                 | 42 |

|    |      | 2.7.2   | Entropy Distribution: LLFs and SLFs                                                                  | 44 |

|    |      | 2.7.3   | Estimating the Volume of Original Traffic                                                            | 45 |

|    |      | 2.7.4   | Estimating the Density Function of Underlying Traffic                                                | 46 |

|    | 2.8  | Summ    | ary                                                                                                  | 47 |

| 3. | AN . | ANALY   | TICAL MODEL OF POLLING DEVICE DRIVERS                                                                | 49 |

|    | 3.1  | Packet  | Processing in Commodity OS                                                                           | 50 |

|    |      | 3.1.1   | Packet Processing in Polling Device Drivers                                                          | 51 |

|    |      | 3.1.2   | NIC Device Driver Configurable Parameters                                                            | 54 |

|    | 3.2  | Relate  | d Work                                                                                               | 54 |

|    | 3.3  | Polling | g Device Drivers: Analytical Model                                                                   | 56 |

|    | 3.4  | Mome    | nts of Overflow Traffic                                                                              | 58 |

|    |      | 3.4.1   | Queuing Model of the I/O Bus $\hfill \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 60 |

|    | 3.5  | Estima  | ating the Service Time of PCI Bus $(\mu_{pci})$                                                      | 61 |

|    | 3.6  | Dynan   | nics of the Polling Process                                                                          | 62 |

|    |      | 3.6.1   | Equilibrium Equations                                                                                | 63 |

|    |      | 3.6.2   | Bulk Size Distribution                                                                               | 64 |

|    |      | 3.6.3   | Constant Bulk Size                                                                                   | 65 |

|    |      | 3.6.4   | Varying Bulk Size                                                                                    | 67 |

|    |      | 3.6.5   | Average Packet Service Time $(\mu_e)$                                                                | 68 |

|    |      |         | •••                                                                                                  |    |

|    | 3.7 | Perfor | mance Evaluation                                                       | 69  |

|----|-----|--------|------------------------------------------------------------------------|-----|

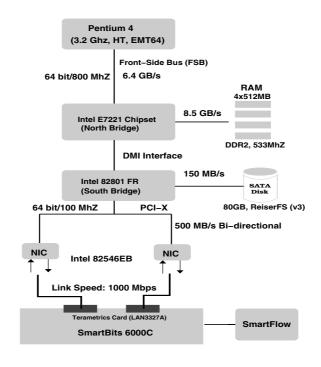

|    |     | 3.7.1  | Experimental Platform                                                  | 69  |

|    |     | 3.7.2  | Testing Methodology                                                    | 70  |

|    | 3.8 | Experi | imental Results                                                        | 72  |

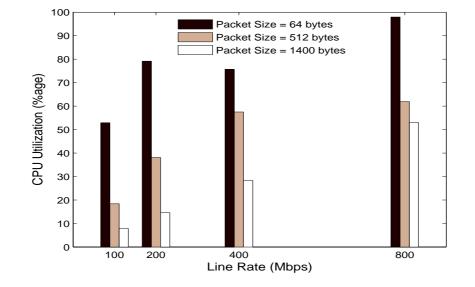

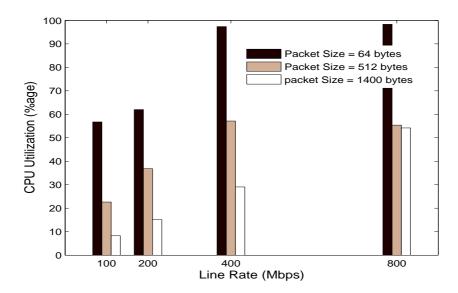

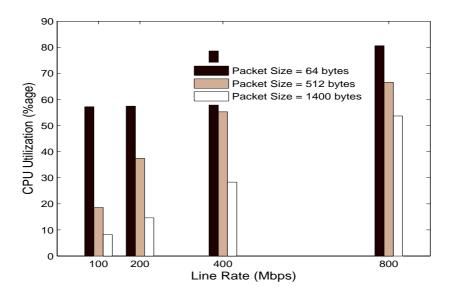

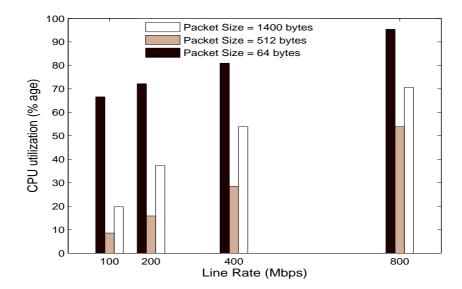

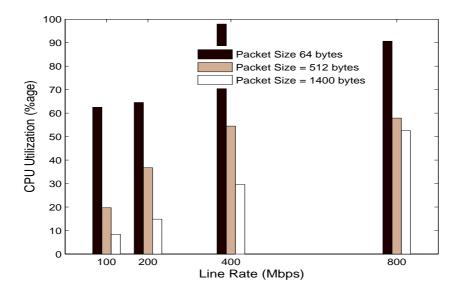

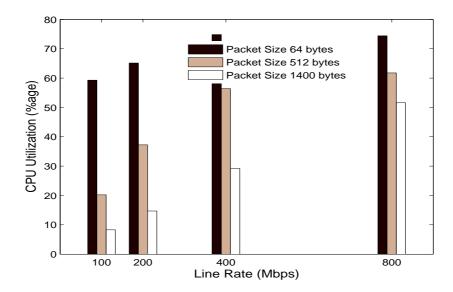

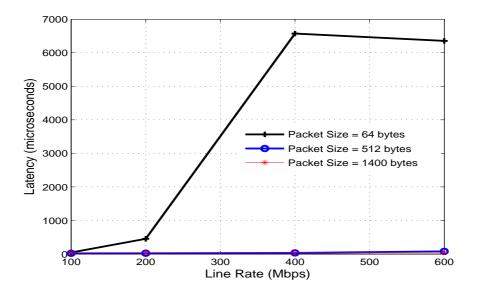

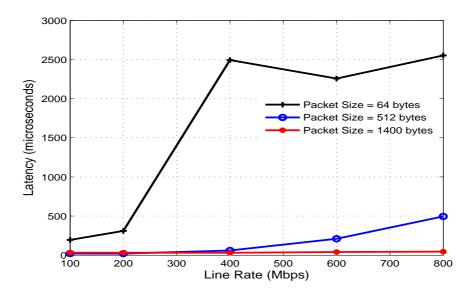

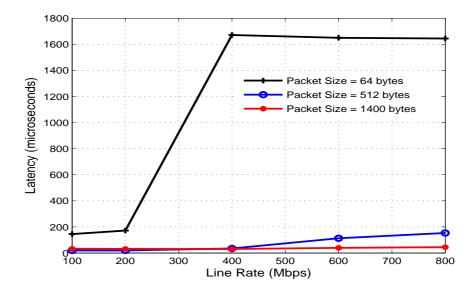

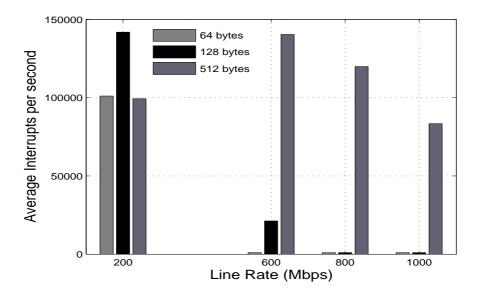

|    |     | 3.8.1  | Average CPU Utilization and Average Number of Interrupts               | 74  |

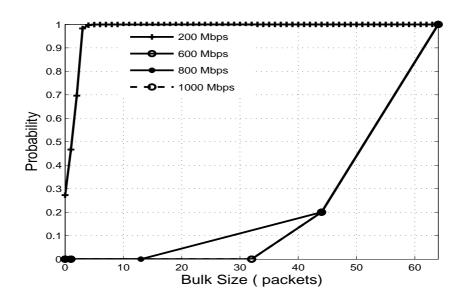

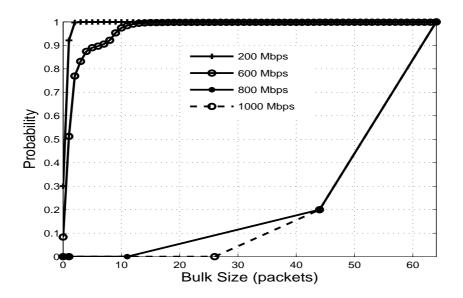

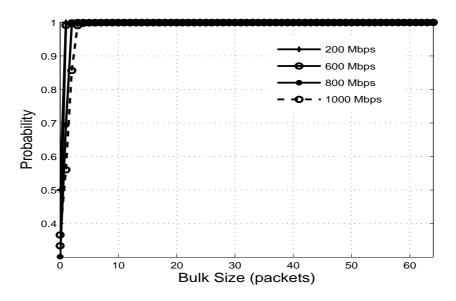

|    |     | 3.8.2  | Average Bulk Size Distribution                                         | 79  |

|    | 3.9 | Summ   | ary                                                                    | 81  |

| 4. |     |        | LING WRITE CONGESTION FOR IMPROVING APPLICATION<br>RFORMANCE           | 82  |

|    | 4.1 | Motiva | ation and Background                                                   | 83  |

|    | 4.2 | Appro  | aches that Impact the Performance of I/O Workloads $\ \ . \ . \ . \ .$ | 88  |

|    | 4.3 | I/O So | cheduling Algorithms                                                   | 90  |

|    | 4.4 | Dynan  | nics of Page Flushing Process                                          | 92  |

|    | 4.5 | Propos | sed WICA Algorithms                                                    | 95  |

|    |     | 4.5.1  | Deterministic WICA: Rate based Approach                                | 96  |

|    |     | 4.5.2  | Estimating $R_i^d$ for $w_i$                                           | 97  |

|    |     | 4.5.3  | Duration of Learning Period                                            | 98  |

|    |     | 4.5.4  | Congestion Control Approach                                            | 101 |

|    |     | 4.5.5  | Limitations of D-WICA                                                  | 102 |

|    |     | 4.5.6  | Probabilistic WICA (P-WICA): Effective Bandwidth(EB)<br>based Approach | 103 |

|    |     | 4.5.7  | Effective Bandwidth (EB) and Smoothing                                 | 103 |

|    |     | 4.5.8  | Congestion Control Approach                                            | 106 |

|    |     | 4.5.9  | Which WICA Algorithm to Choose?                                        | 106 |

|    | 4.6 | Perfor | mance Evaluation                                                       | 107 |

|    |     | 4.6.1  | Workloads using Modified Postmark Macrobenchmark                       | 109 |

|    |      | 4.6.2  | One Reader and One Writer                    | 110 |

|----|------|--------|----------------------------------------------|-----|

|    |      | 4.6.3  | One Reader and Many Writers                  | 113 |

|    |      | 4.6.4  | Situation Outside the Scope of WICA          | 114 |

|    | 4.7  | Summ   | ary                                          | 116 |

| 5. | CON  | ICLUSI | IONS AND FUTURE WORK                         | 118 |

|    | 5.1  | Direct | ions for Future Work                         | 119 |

|    |      | 5.1.1  | Identifying Heavy-hitters in Network Traffic | 119 |

|    |      | 5.1.2  | Extensible Framework for NICs                | 119 |

|    |      | 5.1.3  | Establishing QoS Inside the VM               | 120 |

| RE | EFER | ENCES  | 5                                            | 121 |

| BI | OGR  | APHIC  | AL STATEMENT                                 | 130 |

# LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                      | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

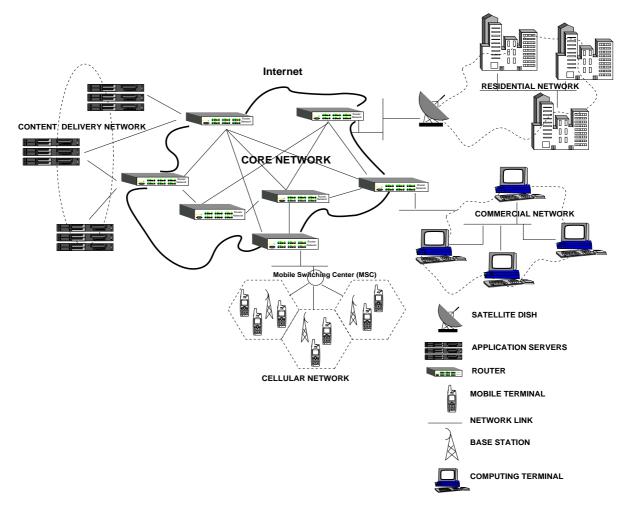

| 1.1    | Conceptual architecture of the Next Generation Networks (NGNs) $\ldots$ .                                                                                                                                                            | 2    |

| 1.2    | A single frame snapshot of streaming multimedia quality under perfect<br>network conditions and negligible load on the streaming server                                                                                              | 4    |

| 1.3    | Snapshot of the same frame of Figure 1.2 with 0.09% packet loss and with negligible load on the streaming server                                                                                                                     | 5    |

| 1.4    | Snapshot of the same frame of Figure 1.2 under perfect network conditions but with non-negligible load on the streaming server                                                                                                       | 5    |

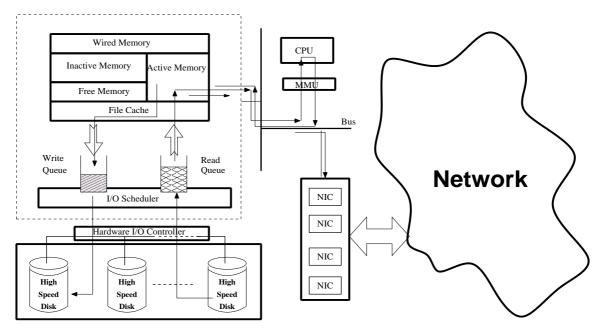

| 1.5    | Primary components that play pivotal role in the packet delivery mechanism<br>of a typical application server. The arrows indicate direction of data travers                                                                         | al 8 |

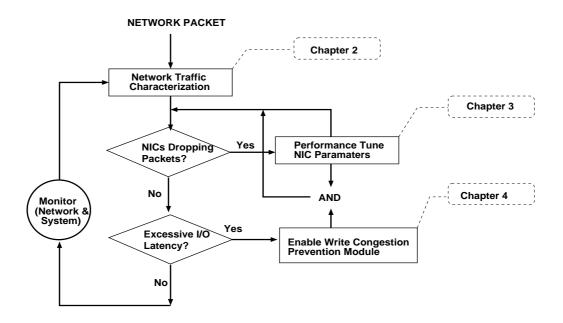

| 1.6    | Suggested steps for monitoring and tuning the performance of application servers in new generation converged networks such as IMSThe 'plus' indicates 'either-or-both' operations                                                    | 12   |

| 2.1    | Structure of Internet Protocol Version 4 (IPv4) packet header. The fields used for computing the five-tuple is shown in bold                                                                                                         | 19   |

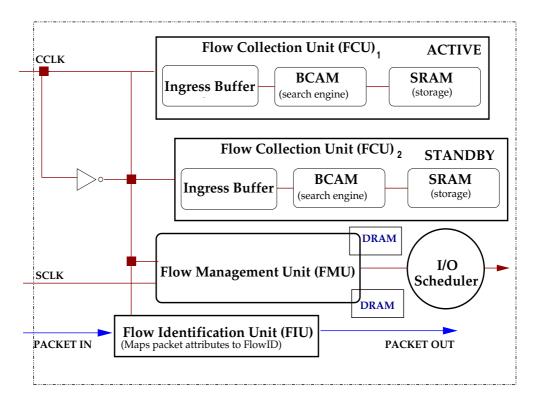

| 2.2    | Architecture of FastFlow. The two FCU units (Active/Standby) have been designed to specifically capture short lived flows                                                                                                            | 23   |

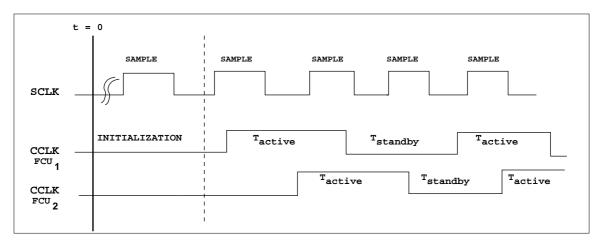

| 2.3    | Illustration of continuous scan clock (CCLK) and sample scan clock (SCLK) used in our measurement architecture                                                                                                                       | 24   |

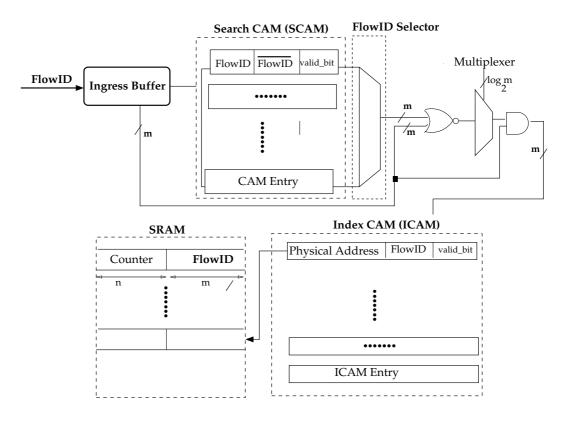

| 2.4    | Architecture of the Flow Collection Unit (FCU) used in our measurement study                                                                                                                                                         | 26   |

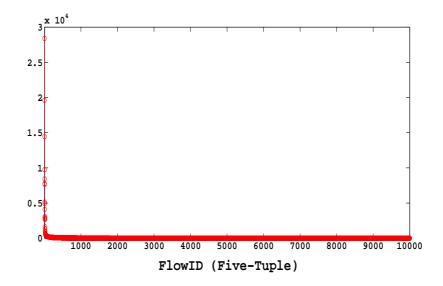

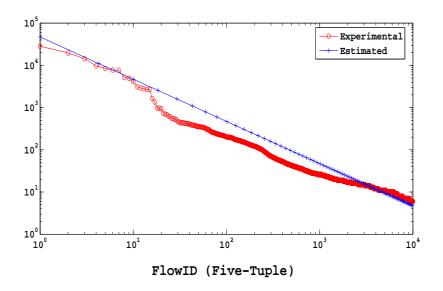

| 2.5    | Linear scale plot of the FlowID density function for traffic collected from our internal LAN. Observe the heavy-tailed nature of FlowIDs                                                                                             | 30   |

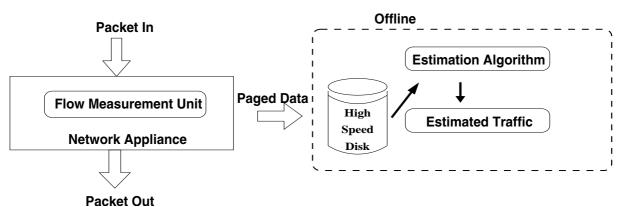

| 2.6    | Offline classification of traffic streams. The pdf of the LLFs in sampled traffic stream is estimated using the non-parametric Parzen window technique                                                                               | 40   |

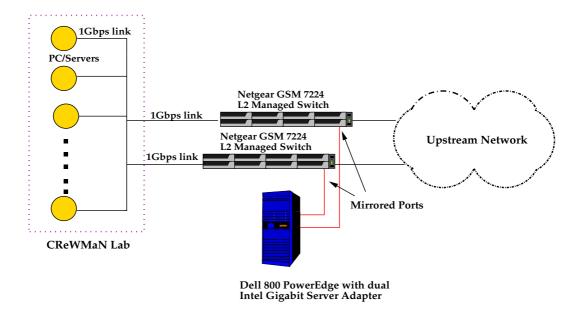

| 2.7    | Framework for capturing flow packets in the internal LAN in our CReWMaN lab. Port mirroring is used to send traffic to a dual port GigabitIntel server adapter from which the packets are capturedusing Ethereal in promiscuous mode | 42   |

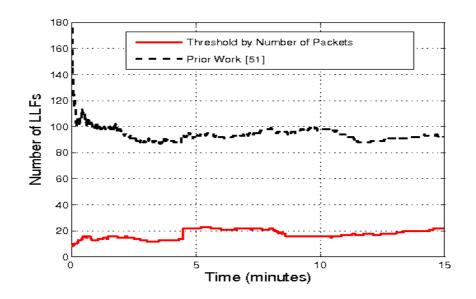

| 2.8  | Time series of the occurrence of LLFs as estimated using our algorithm versus as predicted using existing approach                                                                                                                                    | 43 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

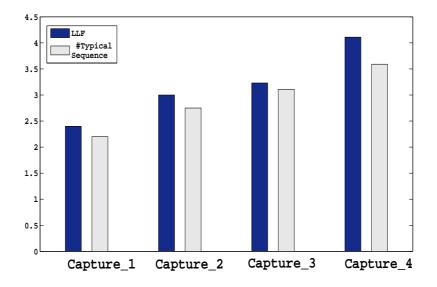

| 2.9  | Histogram of LLFs and the length of typical sequences in traffic traces for traffic collected from our internal lab network                                                                                                                           | 44 |

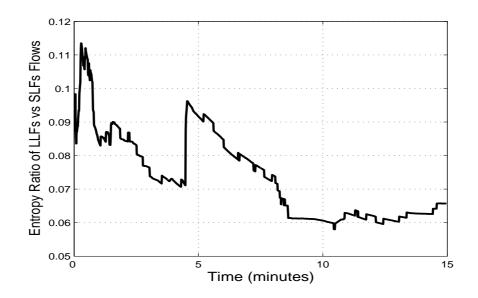

| 2.10 | Ratio of entropy between Long Lived Flows (LLFs) and Short Lived Flows (SLFs)                                                                                                                                                                         | 45 |

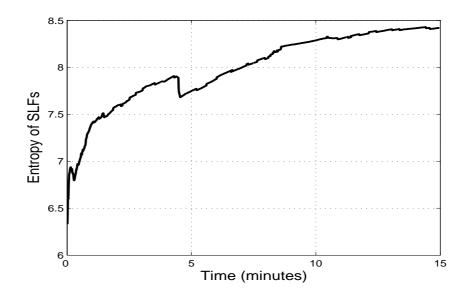

| 2.11 | Temporal distribution of Entropy of Short Lived Flows (SLFs) $\ldots \ldots$                                                                                                                                                                          | 46 |

| 2.12 | Log-log scale plot of the FlowID density function defined using five-tuple in our experiment                                                                                                                                                          | 47 |

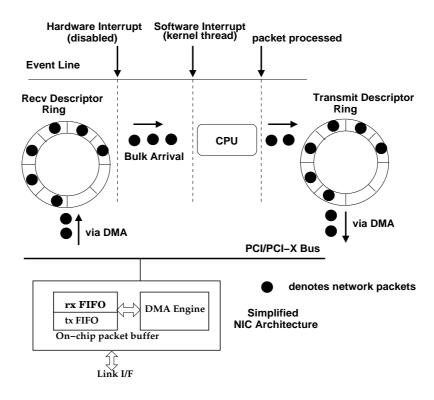

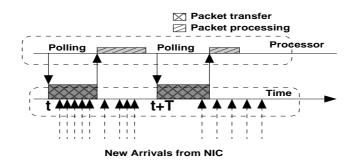

| 3.1  | Description of network packet processing in polling device drivers                                                                                                                                                                                    | 52 |

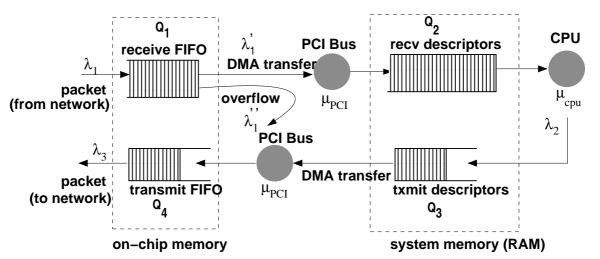

| 3.2  | Basic queuing model of packet processing polling device drivers                                                                                                                                                                                       | 56 |

| 3.3  | Processor sharing model involing the receiver and transmit side PCI/PCI-X bus                                                                                                                                                                         | 57 |

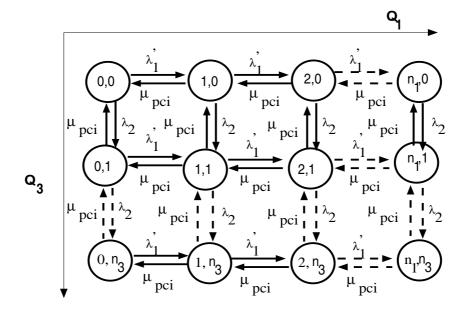

| 3.4  | State Space of the PCI bus where $n_1$ and $n_3$ refer to the size of the buffers $Q_1$ and $Q_3$ respectively $\ldots \ldots \ldots$ | 60 |

| 3.5  | Timeline highlighting bulk removal of packets by the CPU from the receive descriptor ring during each invocation of the polling function                                                                                                              | 62 |

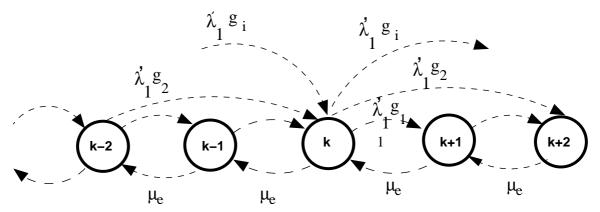

| 3.6  | State Transition Diagram of Bulk Arrival at the CPU work queue during the polling process                                                                                                                                                             | 63 |

| 3.7  | CDF of bulk size Distribution for packet size = $64$ bytes, rxFIFO = $32$ MB, rxDescriptors = $1024$                                                                                                                                                  | 65 |

| 3.8  | CDF of bulk size distribution for packet size = $512$ bytes, rxFIFO = $32$ MB, rxDescriptors = $1024$                                                                                                                                                 | 65 |

| 3.9  | CDF of bulk Size Distribution for packet size = $1400$ bytes, rxFIFO = $32$ MB, rxDescriptors = $1024$                                                                                                                                                | 66 |

| 3.10 | Motherboard architecture used in our experiments. SmartBits 6000C using dual Terametrics card (LAN3327A) inconjunction with SmartFlow was used to generate and analyze traffic from the system-under-test                                             | 69 |

| 3.11 | Average CPU Utilization with rxFIFO = 32MB, rxDescriptors = $1024$ .                                                                                                                                                                                  | 73 |

| 3.12 | Average CPU Utilization with rxFIFO = 32MB, rxDescriptors = 512 $\therefore$                                                                                                                                                                          | 74 |

| 3.13 | verage CPU Utilization with rxFIFO = 32MB, rxDescriptors = $128$                                                                                                                                                                                      | 74 |

| 3.14 | Average CPU Utilization with rxFIFO = 48MB, rxDescriptors = 1024 $\ .$ .                                                                                                                                                                                                                                                                                                   | 75 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.15 | Average CPU Utilization with rxFIFO = 48MB, rxDescriptors = 512 $\therefore$                                                                                                                                                                                                                                                                                               | 75 |

| 3.16 | Average CPU Utilization with rxFIFO = 48MB, rxDescriptors = $128$ .                                                                                                                                                                                                                                                                                                        | 76 |

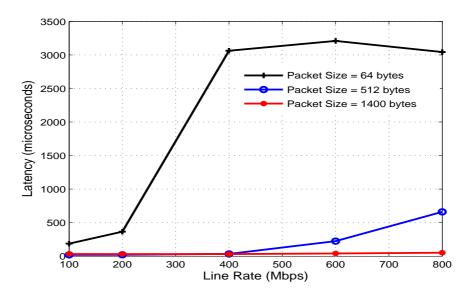

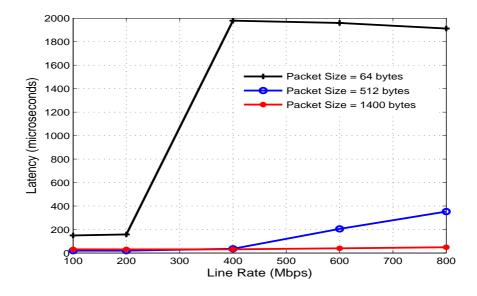

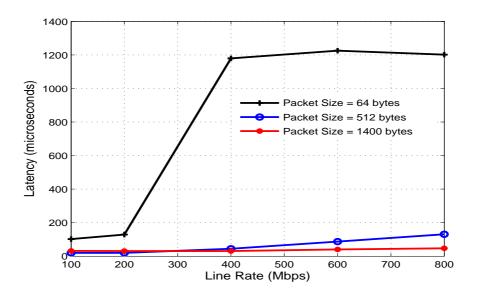

| 3.17 | Average Packet Latency with rxFIFO = 48MB, rxDescriptors = $1024$ .                                                                                                                                                                                                                                                                                                        | 76 |

| 3.18 | Average Packet Latency with rxFIFO = 48MB, rxDescriptors = 512 $\therefore$                                                                                                                                                                                                                                                                                                | 77 |

| 3.19 | Average Packet Latency with rxFIFO = 48MB, rxDescriptors = 128 $\ldots$                                                                                                                                                                                                                                                                                                    | 77 |

| 3.20 | Average Packet Latency with rxFIFO = 32MB, rxDescriptors = $1024$ .                                                                                                                                                                                                                                                                                                        | 78 |

| 3.21 | Average Packet Latency with rxFIFO = 32MB, rxDescriptors = 512 $\therefore$                                                                                                                                                                                                                                                                                                | 78 |

| 3.22 | Average Packet Latency with rxFIFO = 32MB, rxDescriptors = 128 $\therefore$                                                                                                                                                                                                                                                                                                | 79 |

| 3.23 | Average number of Interrupts generated with $rxFIFO = 32MB$ , $rxDescriptors = 128$                                                                                                                                                                                                                                                                                        | 80 |

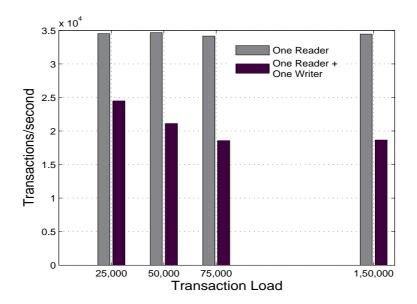

| 4.1  | Example of decreased Transactions per second (TPS), 45% in the worst case, of a single reader process in the presence of a sole background writer process with varying transactional load. The results were obtained using a modified version of Postmark on a NetBSD 3.1 systemwith 512MB of RAM, 4KB page size, and read priority (RPRIO) as the I/O scheduling policy . | 85 |

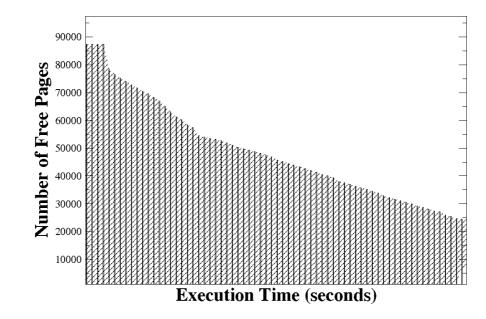

| 4.2  | Temporal variations of the page pool inside the Virtual Memory (VM) during a typical run of the experiment of Figure 4.1.Notice the availability of free pages inside the VM during the lifetime of the experiment                                                                                                                                                         | 86 |

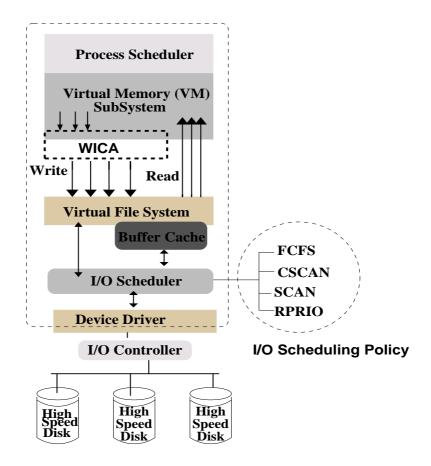

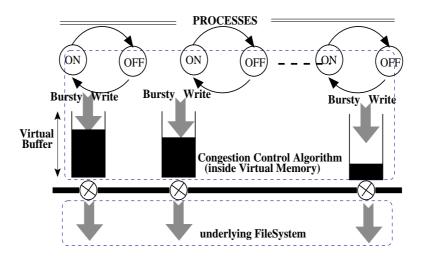

| 4.3  | High Level diagram showing the location of the Write Congestion Indication<br>Algorithm (WICA) inside the Virtual Memory (VM).Notice that WICA<br>traps and monitors the page flushing of the writer processes only                                                                                                                                                        | 87 |

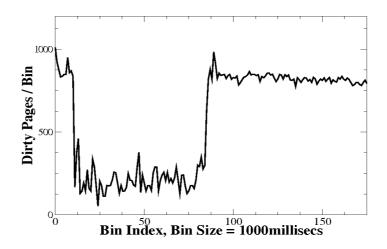

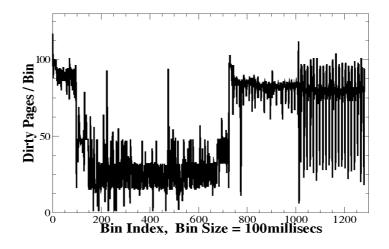

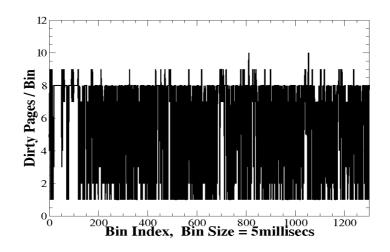

| 4.4  | Stochastic "Burstiness" in the rate of generation of dirty pages for sampling bin size of 1000ms                                                                                                                                                                                                                                                                           | 92 |

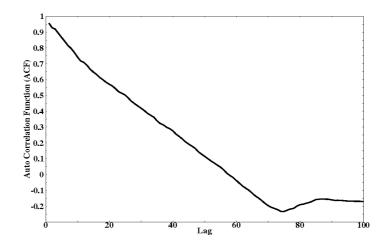

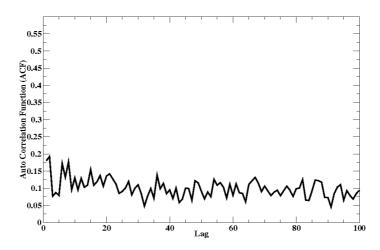

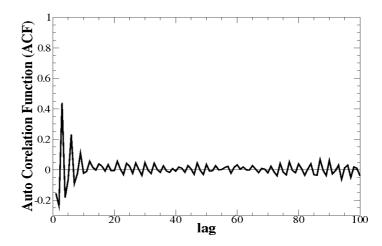

| 4.5  | Rate of decay of Auto Coorelation Function (ACF) for sampling bin size of 1000ms. Notice the high value of ACF                                                                                                                                                                                                                                                             | 93 |

| 4.6  | Presence of "Burstiness" in the rate of generation of dirty pages at reduced sampling bin size of 100ms                                                                                                                                                                                                                                                                    | 94 |

| 4.7  | Rate of decay of Auto Coorelation Function (ACF) for sampling bin size of 100ms                                                                                                                                                                                                                                                                                            | 95 |

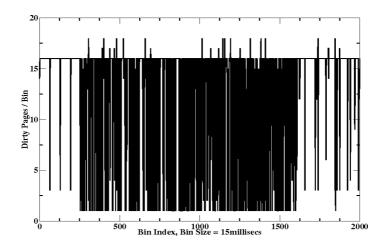

| 4.8  | Disappearance of "Burstiness" in the rate of generation of dirty pages for sampling bin size of 15ms                                                                                                                                                                                                                                                                       | 96 |

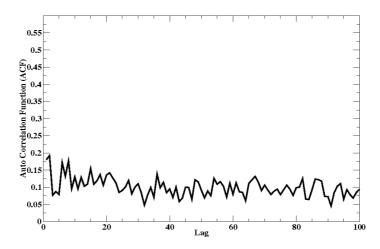

| 4.9  | Rate of decay of Auto Coorelation Function (ACF) for bin sampling bin                                                                                                                                                                                                                                         |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | size of 15ms                                                                                                                                                                                                                                                                                                  | 97   |

| 4.10 | No "Burstiness" in the rate of generation of dirty pages for sampling bin size of 5millisecs                                                                                                                                                                                                                  | 98   |

| 4.11 | Rate of decay of Auto Coorelation Function (ACF) for bin sampling bin size of 5ms                                                                                                                                                                                                                             | 99   |

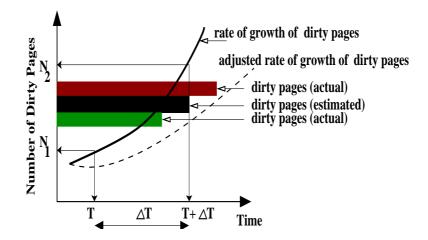

| 4.12 | In deterministic rate based modeling technique (D-WICA), the rate of growth of dirty pages is assumed proportional to the number of dirty pages generated                                                                                                                                                     | 100  |

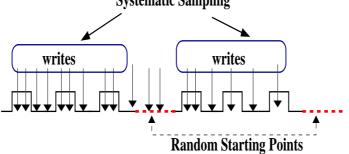

| 4.13 | Systematic sampling, with random start, in order to estimate the rate of generation of dirty pages by the writer processes. Note that such a sampling strategy provides accurate estimation of the rate only when the ACF is close to zero                                                                    | 100  |

| 4.14 | On-Off fluid flow model for determining the effective bandwidth of each of the writer process                                                                                                                                                                                                                 | 103  |

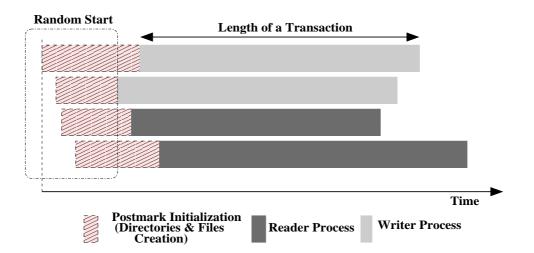

| 4.15 | Evaluation technique with modified version of Postmark for creating reader<br>and writer processes. In each of the experiments, the readers and the writers<br>were independently created at random instants of time and the effective<br>transactions per second (TPS) of the reader processes were recorded | 108  |

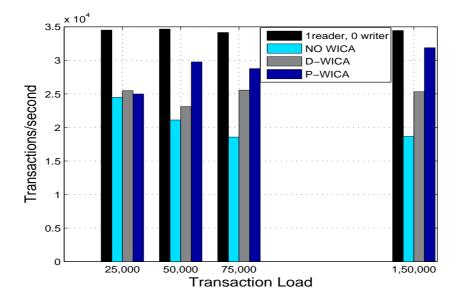

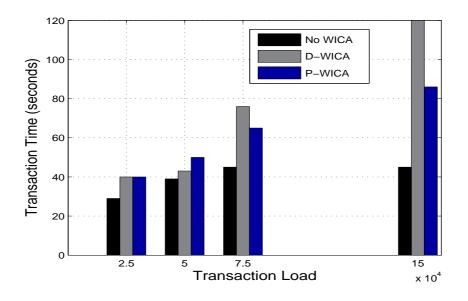

| 4.16 | Postmark results for the Reader process. Observe the increased benefit of P-WICA over D-WICA with increase in the transactional load                                                                                                                                                                          | 110  |

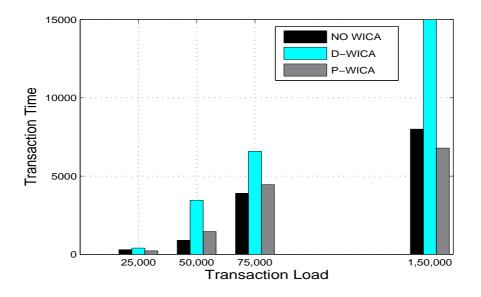

| 4.17 | Transaction time for the Writer process. Observe the sharp increase in the case of D-WICA algorithm                                                                                                                                                                                                           | 111  |

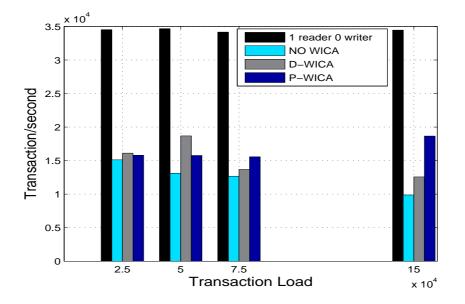

| 4.18 | Postmark results for the Reader process in the presence of three writers .                                                                                                                                                                                                                                    | 112  |

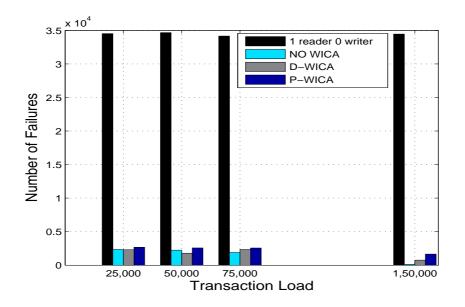

|      | Postmark results for the Reader process in the presence of 20 writers. This identifies failure condition in our experimental settings for the WICA algorithm Transaction time for the Writer process experiencing the highest transaction                                                                     | n114 |

| 4.20 | time among competing writers, in the scenarion where WICA fails                                                                                                                                                                                                                                               | 115  |

# LIST OF TABLES

| Table |                                                                                                                    | Page |

|-------|--------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Notations Used in FastFlow Architecture                                                                            | 22   |

| 2.2   | LLFs actually present in our lab network traffic trace vs. those estimated by length of the typical sequence       | 44   |

| 2.3   | Total number of packets actually present in the traffic trace versus those estimated $(N_{LLF}^{est})$ by FastFlow | 46   |

| 3.1   | Typical configurable parameters available for tuning in off-the-shelf NICs and commodity OS                        | 55   |

| 3.2   | CPU Utilization: rxFIFO = 32KB, rxDescriptors = $1024$                                                             | 70   |

| 3.3   | CPU Utilization: $rxFIFO = 32KB$ , $rxDescriptors = 512$                                                           | 71   |

| 3.4   | CPU Utilization: $rxFIFO = 32KB$ , $rxDescriptors = 128$                                                           | 71   |

| 3.5   | CPU Utilization: $rxFIFO = 48KB$ , $rxDescriptors = 1024$                                                          | 72   |

| 3.6   | CPU Utilization: $rxFIFO = 48KB$ , $rxDescriptors = 512$                                                           | 72   |

| 3.7   | CPU Utilization: $rxFIFO = 32KB$ , $rxDescriptors = 128$                                                           | 73   |

| 4.1   | Notations Used in WICA                                                                                             | 96   |

| 4.2   | Configurable parameters for the Postmark macro benchmark used in our experimental evaluation                       | 107  |

| 4.3   | Characteristics of the system used in our experiments.                                                             | 108  |

# CHAPTER 1

#### INTRODUCTION

The value of present-day Internet is driven by the wide range of application services such as video conferencing, movie-on-demand, IP telephony, online gaming, peer-to-peer communication and numerous other services it is able to provide. Today, the emerging IP Multimedia Subsystem (IMS) architecture [88] is realizing this vision by using a complex array of networks, service applications, and content servers in the infrastructure network. At one end, we have the application servers residing in the application services and in content delivery networks (CDNs) acting as the data sources while at the other end, we have different end points such as cellular, commercial, and residential networks consuming the data. The Internet acts as the intermediary data delivery mechanism for all them and is composed of core and edge routers switching packets along appropriate network links. Figure 1.1 provides a high level architecture of such a layout.

With the evolution and growth of the Internet, it is now possible to control bandwidth allocation, define various packet queuing policies, tune packet dropping thresholds in the core and edge routers for protecting and prioritizing traffic flows belonging to different class of service (CoS) (e.g., via diffserv). All these help to reduce and control end-to-end packet loss, delay, jitter and allow for fine grained traffic aggregation and control across multiple time scales. But before setting the router parameters and tuning application servers in CDNs for optimal performance, it is important to know the composition and characteristics of the network traffic. For example, processing units in application servers and routers exposed to OC-48/192 networking links and carrying large number of control packets with average size of 128 bytes, experience considerable load

Figure 1.1. Conceptual architecture of the Next Generation Networks (NGNs).

on the CPU due to the microsecond granularity of the packet inter-arrival time. Thus, the packet inter-arrival time estimation is important in order to properly understand the allocation of computing resources. A barrage of such control packets has the potential to starve throughput of connections carrying application payload. Consequently, care must be taken to prevent such unwanted interaction of network packets.

At the same time, with the convergence of voice, video, and data packets in all IPbased networks, the volume of traffic is expected to grow considerably. The sheer volume of data that needs to be analyzed makes scalable traffic characterization a big challenge even with the support from the most advanced hardware. Thus, this new converged architecture presents the research community with challenges along two major areas: (i) how to estimate the traffic characteristics of the network in OC-48/192 links and, (ii) how to guarantee the end-to-end latency for the delay sensitive multimedia streams.

#### 1.1 Motivation

Real-time and latency sensitive applications such as streaming multimedia require that the *entire network path* of packet delivery from the originating server to the end host be properly and appropriately configured so as to avoid unnecessary delay and jitter in the data transfer mechanisms. For a pleasing end user experience, the ability to identify and control unwarranted latency in the data delivery mechanism is critical. For example, streaming multimedia require precise sequencing and synchronization of the video frames (I, B, P) for avoiding pixel loss in the video playout mechanism. Since it is well known that packet loss translates to media loss, reliable multimedia delivery dictates that the inter-arrival time gap between the network packets at the receiver network buffer should not be more than 150ms with less than 0.01% network packet loss.

Enforcing such strict end-to-end requirements over the Internet that is shared by different types of traffic is no easy task. And with the advent of new generation networks (NGNs), such as IMS, that are being increasingly built using the Internet Protocol (IP) suite, it is expected that the volume of traffic converging at the network elements (e.g., routers, switches) is going to grow further. Unlike existing specialized networks overlaid on a circuit-switched public switched telephone network (PSTN), such NGNs have no separate paths for voice and data services.

Thus, deploying and delivering rich multimedia applications in NGNs to the end hosts (wired and wireline) is going to be a challenge since packet delivery inherently involves interacting between the storage disks, operating system (OS), network interface cards (NICs), and the various switches and routers; each of which is independently capable of introducting delay in the data transfer mechanism. To compound matters further, as multimedia transitions from standard to high-definition movie format, the demand for a higher data rate (greater than 2 Mbps) is expected to place more strict requirements on packet delivery and processing mechanisms. Consequently, tracing, identifying, and proposing a unified solution that aim to remove performance bottlenecks along the entire path of packet delivery is going to be a daunting if not an impossible task.

# 1.2 The Problem

Traditional design approaches have placed the burden of achieving the required endto-end performance primarily on the network delivery mechanisms. Thus, a lot of effort has been directed in performance evaluation of routers [26], packet classification techniques [22], buffering mechanisms [1], network congestion detection and avoidance [29] schemes for controlling the uncertainties posed by the underlying network. The general expectation is that the application severs plugged on to the network is expected to meet the required performance figures.

Figure 1.2. A single frame snapshot of streaming multimedia quality under perfect network conditions and negligible load on the streaming server. Movie used from [96].

Figure 1.3. Snapshot of the same frame of Figure 1.2 with 0.09% packet loss and with negligible load on the streaming server.

Figure 1.4. Snapshot of the same frame of Figure 1.2 under perfect network conditions but with non-negligible load on the streaming server.

However, to drive a new era of system performance for applications operating in NGNs that demand strict end-to-end performance, it is not enough to consider the performance of the network alone in isolation. Instead the path of data delivery from the storage disks to the physical memory through the NIC cards become as important as the network itself. To emphasize this point, in Figures 1.2, 1.3, 1.4, we provide snapshots of the same image captured from a video sequence encoded at 1 Mbps that is being streamed over a 1000 Mbps Gigabit Ethernet (GbE) network from a high performance streaming server. The streaming server has a database unit that stores the profile of all the registered users. Under immaculate conditions (no network impedance, no database updates), the overall delivered multimedia quality suffers no pixel loss and is considered to be perfect. This is shown in Figure 1.2. However, when the network<sup> $\dagger$ </sup> is experiencing congestion and randomly drops 0.09% of the multimedia packets, it affects the frame reconstruction capability of the media player. As a result, the remote viewer experiences unacceptable video quality. Similar degradation in the media quality is observed in Figure 1.4 when the streaming server experiences varying transactional I/O load from background database jobs due to multiple client access (update operations), thereby increasing the waiting time of the streaming application for the requested data block. Unfortunately, such variations in packet formation delay at the application level affects the audio-video synchronization of the remote media player. Consequently, there occurs pixel distortions and hence the viewing experience is far from perfect.

Although the above experiments were carried out in controlled laboratory settings that simulated the scenario of multiple client accesses, it proves the point that while the underlying network is an important transfer block in the path of packet delivery, it is equally important to consider the performance of the application server in the backdrop of the various OS jobs and the network in which it is expected to perform. All this means that the approach of designing and optimizing application servers that are sensitive to the data arrival process must also evolve to take into account both the network traffic profile along with the data retrieval mechanisms of the OS. At the same time, optimizing

<sup>&</sup>lt;sup>†</sup>In our experiments we simulate varying network conditions using the click modular router [52].

the performance of both the server  $\dagger$  and the network might not be feasible since most of the time the router related tuning parameters (queue type, bandwidth reservation, packet prioritization, etc.) are not available to the end hosts. The natural question that arises is: How do we optimize the performance of latency sensitive application servers present in high traffic network domains with heavy I/O requirements?

# 1.3 Overview of Our Novel Approach

In this dissertation we aim to answer the above question by looking into the interaction between the different components of the host OS and also trying to understand the profile of the underlying network traffic in which the latency sensitive application servers are expected to be placed. With the arrival of NGNs, these application servers are being increasingly built on open source Advanced Telecom Computing Architecture (ATCA) [89] based blade computing units with Linux or xBSD based OS. The infrastructure providers are using ATCA platform for their application server design such as IMS Call Session Control Function (CSCF) controllers and content providers are using it for building content servers in CDNs. Changes are also happening at the core network infrastructure where network planners are using designs based on network processing technology for high capacity core routers supporting OC-192 or OC-768 links. Apart from lowering the cost of ownership and deployment time period, such standardized architectures imply that the optimization and performance solution techniques proposed in this dissertation can be mostly be ported across different network and hardware profiles with little or no modifications. Thus, within the limits of practicability, our proposed technique can be considered to be generic.

To illustrate the concept, we consider the case of content delivery servers in our

<sup>&</sup>lt;sup>†</sup>Note that our focus is exclusively on latency sensitive application servers plugged into high traffic domains as in the content delivery networks (CDNs). From now on, we use the term 'servers' to refer to such category of application servers.

Figure 1.5. Primary components that play pivotal role in the packet delivery mechanism of a typical application server. The arrows indicate direction of data traversal.

work. The architecture and the design concept presented in our research is equally applicable to IMS CSCF servers or other application servers. Since complete path tracing and optimization is impossible, we separate the network delivery mechanism from the packet processing capability of content delivery servers. If we separate out the network delivery mechanism, the performance of such servers that send data over the network from storage disks is dependent on the following main components: (i) the performance of the I/O system that retrieves the data from the hard disks, (ii) virtual memory (VM) that allocates physical memory pages for the data to be mapped in, (iii) scheduling techniques of the CPU, and (iv) finally on the packet transmission mechanisms of the NIC from the OS buffers to the networking links. Such an architecture is shown in Figure 1.5 consisting of the network, the NIC cards, physical memory, and the I/O schedulers. In identifying such component parts, we have purposefully avoided going into the file system performance intricacies, CPU and I/O architectures, and various hardware and software

optimization techniques available in the literature. While such granular level optimization is expected to further improve the performance of the servers, it is outside the scope of this dissertation work. Instead, we aim to look at approaches on how most common OS kernels running over ATCA hardware with known network traffic profile can be designed to support latency sensitive applications such as streaming multimedia.

# 1.4 Contributions of The Dissertation

This dissertation is based on the assumption that application servers built using open source architectures such as ATCA and running commodity OS kernels like Linux, xBSD, or OpenSolaris can be performance tuned for serving latency sensitive applications by understanding the OS packet delivery mechanisms and the network environment in which they are expected to operate.

The major contributions of this dissertation are summarized as follows:

• A New Framework for Network Traffic Characterization: Understanding the nature and composition of network traffic interfacing with the servers is the first step towards planning and deploying large scale CDNs. An accurate diagnosis is achieved by carefully observing the interaction of traffic flows across various degrees of freedom like duration (time), size or protocol composition. There are two parts to the problem of traffic characterization: (i) how to measure the flows, and (ii) *infer* the overall traffic behavior and composition from the collected data. A lot of effort has been directed to the second problem of traffic inference and associated problems of flow dimensioning like short lived flows (SLFs) vs. long lived flows (LLFs), flow sampling (uniform, random, stratified), and on deriving statistical models (Pareto, Weibull, Poisson) that define the nature of traffic flows across the various degrees of freedom. Surprisingly though, the first problem of how to collect the flows has received limited attention. In Chapter 2, we propose an alternate approach to traffic characterization by closely linking the flow measurement architecture with the estimation algorithm. Our measurement framework stores complete information related to SLFs while collecting partial information related to LLFs. For real-time separation of LLFs and SLFs, we propose a novel algorithm based on typical sequences from Information theory [13]. The probability density function (pdf) and the sample space of the underlying traffic is estimated using the non-parametric Parzen window technique [56] and likelihood function defined over the Coupon collector problem [21]. We validate the accuracy and performance of our estimation technique using traffic traces from the internal LAN in our laboratory and from the National Library for Applied Network Research (NLANR).

• An Analytical Framework to Evaluate the Performance of Gigabit Network Interface Cards: Application servers that are the focus of this dissertation, usually have multiple Gigabit Ethernet (GigE) NICs that involve considerable packet processing at high line speeds (greater than 300 Mbps average data rate). Since per packet interrupt processing is impractical at such high data rates, these NICs generally use device polling to transfer the packets to the OS. Network processing bottlenecks may arise due to complex interaction between the NICs, host OS, and the underlying hardware. These may be due to the inherent limitations present in the network adapter (e.g., limited on-chip buffer space), hardware architecture (e.g., I/O bus width), or simply due to improper allocation and configuration of the system resources. Considering the fact that an exhaustive experimentation involving all the parameters is not possible, in Chapter 3, we develop a closed form queuing model to investigate the impact of PCI/PCI-X I/O bus, on-chip packet buffers, receive and transmit descriptor rings of the OS, and processor service time on the dynamics of network packet processing. Our experiments indicate that while device polling is an invaluable approach to prevent interrupt livelock at high line rates, it exhibits high average CPU utilization (greater than 90% for 128 bytes packet at 500Mbps) with increase in packet arrival rate. Furthermore, there occurs non-negligible costs in terms of interrupt generation when the system needlessly switches between polling and interrupt modes either due to: (i) overflow at the on-chip receive buffer, or (ii) due to non-availability of the PCI/PCI-X bus. We also show how results from our analytical framework can provide useful guidelines in evaluating the capability of such high performance networking systems.

• Identifying and Controlling Write Congestion for Improving the Performance of Reader Processes: Write congestion is a phenomenon when the effective transactions per second (TPS) of latency sensitive systems start decreasing in the presence of a large number of writer processes generating bursty workload patterns of disk access. We analyze the underlying behavior of such situations and propose two algorithms - deterministic (or rate based) and stochastic (or effective bandwidth (EB) based) - for improving the effective TPS of reader processes. For the rate based approach, we show by measurements how the presence of memory (Long-Range Dependence) in workload patterns can influence the decision of choosing the sampling type and the length of the sampling window. The stochastic approach is based on the established theory of EB in which we consider a set of fluid On-Off writers that independently generate dirty pages inside the virtual memory (VM). Each of the writers has an EB threshold that depends on the peak rate of generation of dirty pages and on the dynamics of an equivalent Poisson process. The rate based approach is suitable for lightly loaded systems in skewing the disk access towards the readers. However, in the presence of large variance in workload patterns, it unduly penalizes the writers. On the other hand, at the cost of increased complexity of implementation, the effective bandwidth based approach is suitable

Figure 1.6. Suggested steps for monitoring and tuning the performance of application servers in new generation converged networks such as IMS.

for heavy duty servers. It is more resilient towards wide scale fluctuations of work load patterns and provides optimistic benefit in alleviating write congestion.

#### 1.5 Outline of the Dissertation

Figure 1.6 describes a flow of actions that underline our approach for improving the performance of the application servers performance in the next generation converged networks such as CDNs. Before designing the CDNs, it is important to understand the dynamics of the traffic profile that the network is expected to handle. Keeping this in mind, Chapter 2 proposes an architecture for accurate characterization of network traffic. Next comes performance tuning of the NICs and OS parameters for preventing unwarranted packet loss along the receive path of data transmission. Considering the fact that an exhautive experimentation involving all parameters is not possible, Chapter 3 proposes a queuing model and provides guidelines on how to set appropriate value of the parameters under various conditions. Next we focus our attention to reducing the latency in the data retrieval mechanism inside the OS. In Chapters 4, we present two write congestion control algorithms (rate based and stochastic) and study their performances under various tansactional I/O loads. Finally, we conclude the dissertation in Chapter 5 with directions for future work.

# CHAPTER 2

# AN ARCHITECTURAL FRAMEWORK FOR ACCURATE CHARACTERIZATION OF NETWORK TRAFFIC

Understanding the dynamics of traffic crossing boundaries of network appliances (e.g., routers, switches, load balancers, firewalls, etc.) is an important step towards planning and deploying a large scale content delivery network (CDN). An accurate diagnosis is achieved by carefully observing the interaction of traffic flows (defined in Section 2.2) across various degrees of freedom like duration (time), size or protocol composition. The method of accurately estimating the nature of traffic flow along various degrees of freedom is referred to as the *traffic characterization*. Such characterization is essential for precise traffic engineering and is utilized for estimating network resource usage, bandwidth provisioning [18], differentiated services [8], traffic shaping [19]. For application servers inside the CDNs, such traffic characterization provides invaluable insights about the average packet size and data rate that the NICs and the server OS need to handle. For example, if the network is carrying lots of control packets with average packet size of 128 bytes or less, then it is advisable to map interrupt lines to specific processing units in multi-processing capable CPUs and also enable device polling with high bulk service rates. On the other hand, in CDNs with no such traffic profile enabling, such features will needlessly put load on the CPU. Thus, an accurate traffic characterization enables us to tune the performance of the resources of the server according to the needs and demands of the network traffic. The rest of the chapter is organized as follows. In Section 2.1 we define packet flows as they are related to network traffic. The challenges involved in characterizing network traffic at high line speeds (10Gbps or more) are exposed in Section 2.2. In Section 2.4, we propose a flow measurement architecture that tackles the

problem of how to collect traffic flows at high line speeds. Data sampling and recovering of lost sample points for estimating the statistical distribution of the underlying traffic on data collected using our architectural approach is dealt with in Section 2.6. Validation of our approach is done in Section 2.7.

### 2.1 Components of Traffic Characterization

Traffic characterization involves two parts. The first part is paying attention to how to measure the flows and the second part is on *inferring* the overall traffic behavior and composition from the collected data. A lot of effort has been directed to the second problem of traffic inference and associated problems of flow dimensioning like short lived flows (SLFs) vs. long lived flows (LLFs), flow sampling (uniform, random, stratified), and on deriving statistical models (Pareto, Weibull, Poisson) that define the nature of traffic flows across the various degrees of freedom. Surprisingly though, the first problem of how to collect the flows has received limited attention. That being said, the recent work by Kumar et. al [43] [44] focused on using efficient data structures for flow characterization. Their work is a major step towards closely knitting the architecture and measurement technique together. However, the authors did not study the underlying architecture required for such a framework (except for identifying the need for multiple fast memory modules) and also did not take into account the idiosyncratic behaviour of heavy-tailed nature of the Internet flow. As we shall see, solutions to the two problems of collection and inference of network traffic are closely related; a measurement architecture specifically tuned for flow collection provides a strong basis for accurate traffic estimation.

If we consider the longevity of individual traffic flows, it is apparent that SLFs are the most difficult to capture since they die out fast (less than 1 second); but the individual size of such flows (i.e., the number of packets) is small (less than 100 packets). Also, they account for a substantial portion of the network traffic. In our experiments,

we have observed similar behaviour with the average lifetime of SLFs being less than a second (around 250 millisecs) with the combined traffic carried by them being around 40% of the entire traffic volume. On the other hand, LLFs exist in small numbers (around 3%), have longer lifetime (average duration of 30 minutes), and approximately account for 25% of the total traffic. From this observation, it is apparent that solutions that are unable to capture SLFs and take into account the ephemeral nature of such flows will have limited accuracy in estimating the composition of the underlying traffic. In sharp contrast, various statistical sampling techniques can be feasibly applied to LLFs since the traffic carried by them is substantial with each flow lasting for several minutes, hours, and even days.

Our proposed architectural framework for capturing and estimating the traffic distribution is based on the above observation. It is designed to *feasibly* store *complete* information related to SLFs with manageable complexity and hardware cost. At the same time, it uses systematic sampling to collect sufficiently large number of samples of LLFs; together which provides for accurate traffic flow characterization. In the next section, we briefly review existing approaches for traffic characterization.

### 2.1.1 Existing Approaches for Traffic Characterization

Precise knowledge and understanding of the properties and characteristics of the network traffic provide an important yardstick for accurate traffic engineering. An wellestablished mechanism for traffic characterization is to install a network tap at the point of measurement for a certain interval of time, collect packet samples, and infer flow characteristics from the collected data. Based on this philosophy but differing in the methods, two broadly different approaches currently exist for traffic flow characterization. They can be categorized as:

- Traffic analysis based on different sampling methods: Random sampling, simple random sampling, or stratified random sampling based traffic analysis has been studied in [10]. In [18], the authors studied the impact of sampling techniques on LLFs and suggested methods to infer properties of original traffic from sampled flow statistics. Correlated sampling strategy was proposed in [19] to account for the heavy-tailed distribution of flow lengths. Approaches that predict flow properties not available in sampled traffic volume have been studied in [20]. In [25], a theoretical study was undertaken that proved that it is possible to exactly infer the number of packets per flow which is not possible in traditional packet based sampling.

- Characterization of traffic using a combined approach of efficient data structures and related statistical estimation techniques: In [43] [44], the authors used a combination of bloom filters and maximum likelihood estimation techniques to predict the density function of the underlying traffic. Probabilistic data structures such as sketches have been used for identifying the heavy-hitters in large data streams [12]. Such approaches have been shown to yield better traffic characterization with definite bounds on estimation errors. Though novel, the approach of [43] and [44] suffer from architectural limitations related to the mismatch of speed between various memory hierarchies: Static Random Access Memory (SRAM), Dynamic Random Access Memory (DRAM), and mechanical disk storage unit.

#### 2.1.2 Salient Features of Our Approach to Traffic Characterization

The primary limitations of the above approaches are the degree of accuracy of the results and scalability of the algorithms due to the large volume of datasets that need to be analyzed. It seems that a better solution could be achieved if it is first possible to identify and separate flows which carry most of the packets. An added benefit would be to remove the storage limitations posed by the measurement architecture. Once such a goal is achieved, it would then be possible to store information for identifying scarcely occuring flows in the data stream with full accuracy while estimating the information for flows with a large presence. Our study is based on such a philosophy. It aims at linking the measurement architecture with the estimation algorithm such that information related to SLFs could be captured with complete accuracy while information related to LLFs can be predicted using non-parametric statistical techniques.

The salient features of our approach are summarized as follows:

- We propose an architecture framework called *FastFlow* that uses the principle of *typical sequences* [13] for separating the SLFs and LLFs. Experimental results indicate that typical sequences can identify LLFs with around 90% accuracy. Further, the low computational overhead of identifying typical sequences makes our framework suitable for real life implementation.

- We provide a fast SRAM based traffic flow update algorithm that avoids the complexity and overhead of traditional hash based solutions. It is based on binary content-addressable memory (BCAM) using addressing inversion for logic gating.

- We use non-parametric Parzen window technique [56] to estimate the probability density function (pdf) of the underlying traffic.

### 2.2 Definitions

In this section, we define the terminology used in rest of the chapter. We define flows to refer to those packets with similar attributes. For example, a flow might consist of packets having identical values of five-tuple (source address, destination address, source port, destination port, protocol) as shown in Figure 2.1), or comprise of packets matching specific payload information (e.g., group of all TCP packets with payload containing the string "crewman"). Thus, flows can be characterized by packet headers,

| Version | H-Length                          | TOS      |                 | Total Length    |  |  |

|---------|-----------------------------------|----------|-----------------|-----------------|--|--|

|         | Identification                    | วท       | Flags           | Fragment Offset |  |  |

| ТТ      | L                                 | Protocol | Header Checksum |                 |  |  |

|         |                                   | Source / | Addres          | S               |  |  |

|         |                                   | Destinat | ion Ad          | ldress          |  |  |

|         | IP Options (if present)           |          |                 |                 |  |  |

|         | Source Port Destination Port      |          |                 |                 |  |  |

|         | Remaining Transport Header Fields |          |                 |                 |  |  |

|         | Payload                           |          |                 |                 |  |  |

313029282726252423222120191817161514131211109876543210

Figure 2.1. Structure of Internet Protocol Version 4 (IPv4) packet header. The fields used for computing the five-tuple is shown in bold.

payloads or a combination of both.

indent The size of a flow is the number of packets belonging to the flow, and the duration of a flow is its lifetime. For example, the size of a TCP flow is the number of packets exchanged till the last packet containing the FIN bit is sent (during normal termination) while the duration is the time interval between the first and last packets of the flow. In order to associate a packet with a flow, it is necessary to define a *Flow Identification* Tag (abbreviated as FlowID) using appropriate flow definition. For example, if flows are defined using the above five-tuple, then the FlowID is 104 bits long and can be used to separate packets belonging to different flows. Thus, the length of FlowID depends on how traffic flows have been defined. The next section provides a numerical case study that highlights the challenges related to the exhaustive flow collection. The performance figures quoted in the example are obtained by using the packet inter-arrival time of  $\left[\frac{R \times u}{P}\right]$ , where R is the theoretical data rate, u is the link utilization factor, and P is the size of the packet in bytes.

#### 2.2.1 A Motivating Example

To understand how traffic characterization is limited by resource constraints, consider the following example: On an OC-192 link (10 Gbps) with 80% link utilization and average packet size of 500 bytes, the average packet inter-arrival time is 500ns. Within the packet inter-arrival time, the hardware unit responsible for collecting flow statistics has to:

- Extract flow information by parsing fields of the packet.

- Compute the FlowID.

- Locate the FlowID in memory.

- Increment the counter corresponding to the FlowID.

In order to execute the above sequence of operations, the packet processing unit requires more than one memory access. Today's high capacity, high performance off-the-shelf static RAM (SRAM) has access time as low as 10ns with average size of 1-4 MB. Dynamic RAM (DRAM) have much higher densities (1 Gbits) but have equivalent access time of around 50ns or more [1]. If we use a hash table in SRAM, we need approximatly 160 bits [43] per hash table entry in order to store 32 bit wide counters that record the frequency of occurrence of flows in the underlying traffic. Thus, with 5MB SRAM, it is possible to store information corresponding to 0.25 million flows each 32 bits wide. Considering the fact that the number of flows in the Internet backbone links can reach 0.5 million [44] or more during the measurement interval, clearly a single SRAM module will not suffice. Also, in our illustrative example, we have assumed the ideal situation of one counter update per packet. In reality, the update overhead is considerably large since the useful clock cycles have to be expended in order to extract the flow information from the packet, compute the FlowID and take into consideration the overhead of hash table update [44].

Thus, at 10 Gbps with 80% link utilization, the 5MB SRAM module will be filled up (assuming uniform hash table update) once every 5.3ms; requiring that we move 0.25 million flows of 160 bits from SRAM to DRAM as fast as possible in order to prevent the SRAM overflow. At 50ns access time, the DRAM operation will take (assuming bus width of 64 bits) around 63ms. Clearly, the low density, access speed mismatch, and high cost (4:1) [1] of SRAM compared to DRAM, make it practically infeasible for exhaustively capturing the information related to all the packets. Hence, a näive brute force approach of storing flow information is impractical (if not impossible) [20] as it would create memory hotspot problems, consume valuable processor cycles, and also might render the system unresponsive for prolonged periods of time. Added to these are the traditional issues associated with storing, mining, and analysis of large datasets.

## 2.3 Traffic Characterization: Problem Statement

Consider a definite flow measurement interval  $(T_1, T_2)$ . It can be infinite if flow characterization is always on or can be a finite interval during which the algorithm is active. Let  $[\mathcal{F}] = \{F_1, F_2, \ldots, F_i, \ldots, F_N\}$  be a sequence of N FlowIDs from  $\{1, 2, \ldots, i, \ldots, N\}$ , where each FlowID,  $F_i$ , is an index i.e., a number between 1 and N used to identify each flow in the underlying traffic. Denote  $|F_i|$  to represent the number of packets belonging to the flow with FlowID  $F_i$ . It is important to note that the sequence  $[\mathcal{F}]$  is sorted by increasing cardinality of the number of packets present in each FlowID. Our goal is to estimate N and the probability density function (pdf) of the network traffic from the available data sequence  $[\mathcal{F}]$ . As elucidated in Section 2.1, the accuracy of such a technique is primarily governed by the amount of information we are able to collect about the SLFs and LLFs. Under such circumstances, the flow characterization problem

| Notation          | Meaning                                                              |  |

|-------------------|----------------------------------------------------------------------|--|

| $\overline{N}$    | Number of FlowIDs                                                    |  |

| $\mathcal{F}$     | The sequence of FlowIDs                                              |  |

| $\mathcal{F}^{'}$ | The new sequence formed from $\mathcal F$ after clustering operation |  |

| $(F_i)$           | Index used to identify a FlowID                                      |  |

| K                 | size of the ingress buffer                                           |  |

| A                 | Stochastic process denoting interarrival time of ingress buffer      |  |

| В                 | Stochastic process denoting service time of ingress buffer           |  |

| $C_A$             | Coefficient of variation of interarrival time of ingress buffer      |  |

| $C_B$             | Coefficient of variation of service time of ingress buffer           |  |

| $\frac{\rho}{W}$  | Average system occupancy                                             |  |

|                   | Mean waiting time of FlowID in ingress buffer                        |  |

| $\gamma, \delta$  | Shape and Scale parameter of Pareto distribution                     |  |

| m                 | Width (in bits) of each FlowID                                       |  |

| c                 | Number of bits associated with each FlowID counter                   |  |

| S                 | Size (in bits) of SRAM module                                        |  |

| M                 | Total number of FlowIDs collected during a measurement interval      |  |

| $\frac{p}{CL}$    | Probability of occurence of a LLF packet                             |  |

| CL                | Confidence Limit required for FMU initialization                     |  |

| H(X)              | Entropy of random variable X                                         |  |

| $\psi(.)$         | Gaussian kernel function                                             |  |

| h                 | Width of the kernel density function                                 |  |

Table 2.1. Notations Used in FastFlow Architecture

can be broken down into the following three sub-problems that serve as useful starting points for the overall solution: (i) architecture, algorithm, and performance modeling of the measurement architecture, (ii) algorithm for classifying LLFs and SLFs, and (iii) estimating techniques for N and the pdf of the network traffic from the available data set,  $\mathcal{F}$ . In the following sections, we provide solutions to each of these sub-problems. The notations used in our study are present in Table 2.1.

#### 2.4 Measurement Framework: Architecture, Algorithms, and Modeling

We start with a high level description of the proposed architecture, called FastFlow, and analyze its component parts. This architecture shown in Figure 2.2 is envisioned to be a hardware module that plugs as a Smart Interface Card (SIC) into the network appliance. FastFlow is a self-contained hardware module with a Flow Identification Unit

Figure 2.2. Architecture of FastFlow. The two FCU units (Active/Standby) have been designed to specifically capture short lived flows.

(FIU), Flow Management Unit (FMU), and two Flow Collection Units (FCUs). The FIU is responsible for extracting and mapping the attributes of a packet to the corresponding FlowID. When the SIC is active, packets flow through the FIU and are immediately placed in the original line of flow after the information relevant to the calculation of the FlowID has been extracted from the packet. This allows the measurement unit to work transparently from the rest of the appliance. Fundamental to the design is the assumption that a unified measurement approach for collecting information for both SLFs and LLFs is not technically very efficient (see Section 2.1).