# THERMAL FAILURE MECHANISM AND VOLTAMMETRY METROLOGY FOR CU/BARRIER/LOW K INTEGRATION

by

## DONGMEI MENG

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT ARLINGTON

December 2006

Copyright © by Dongmei Meng 2006

All Rights Reserved

#### ACKNOWLEDGEMENTS

My years at University of Texas at Arlington will be always one of the most cherished memories in my life. I would like to thank all the people for their support and encouragement, making this dissertation all possible and beyond worthwhile.

First of all I would like to express my gratitude to my advisor, Professor Choong-Un Kim. Without his guidance, encouragement and support throughout my graduate career including my years at UTA and Intel Corporation this dissertation would not have come to fruition. It is a blessing to have a mentor who is not only a constant source of ideas but also of an open mind to discuss research with his students. I am always be impressed by his technical insight and sharp intuition into not only semiconductor technology but also a broad academic area. It has allowed me to develop some level of insight and intuition myself, that I will always be grateful for.

My gratitude also goes to my friends and colleagues: Dr. Nancy Michael, Dr. Jaeyong Park, Dr. Heedong Yang, Dr. Woong-ho Bang, Dr. Liangshan Chen, Jee Yong Kim, Michael Coviello, Jason Craig, Andrew Howard, Theresa Friske, Jennet Smith, etc, past and present, for their guidance, support, and team spirit. Especially, I thank Dr. Nancy Michael who helped me in too many ways to recall. Without her, the journey to my doctoral degree would have been more difficult. I would also like to thank my dissertation committee members Dr. Roger D. Goolsby, Dr. Pranesh B. Aswath, Dr. Seong Jin Koh and Dr. Alex H. Weiss for their time and expert advice.

Last, but certainly not least, I would like to express my deepest gratitude to my family: my mother-Xiahua Zheng, my father-Qingji Meng, my husband-Zhongdong Yu and my son-Menghan Yu, for always being there in heart to unwavering support me throughout my life and career. No doubt the journey to my doctor degree is not always smooth. It is their unconditional love and understanding that make my pursuing a reality.

This work is supported financially by the Semiconductor Research Corporation (Task ID: 1194.001, and 908.001), Sematech, Texas Instruments and Texas/ATP, and it is gratefully acknowledged.

October 13, 2006

#### ABSTRACT

## THERMAL FAILURE MECHANISM AND VOLTAMMETRY METROLOGY FOR CU/BARRIER/LOW K INTEGRATION

Publication No.

Dongmei Meng, PhD.

The University of Texas at Arlington, 2006

Supervising Professor: Choong-Un Kim

The present study investigates the thermal stability of Cu/barrier/porous low  $\kappa$  (PLK) integration first, and then a new characterization method based on voltammetry is developed to characterize quality of diffusion barrier and pore structure in low  $\kappa$  materials and its thermal stability. The study of thermal stability reveals that Cu/barrier/PLK interconnect fails by Cu out-diffusion through the defects of diffusion barrier into the PLK structure, which is driven by oxidation and stress gradient within the interconnect structure. The failure appears to be triggered by defects in diffusion barrier, however, such defects are not effectively detected by TEM observation due to their small and localized nature. This motivates the development of a new method to characterize defects of diffusion barrier and pore structure of low  $\kappa$  materials in as-

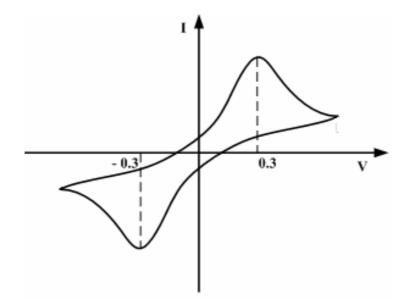

processed Cu/barrier/PLK interconnect. Firstly, a cyclic voltammetry-based method is developed to detect the quality of diffusion barrier by monitoring the current resulting from an applied voltage on the established cell. It utilizes a fact that electrolyte solution is able to infiltrate into the low k layer between two interconnects and creates a situation essentially the same as two-electrode electrolytic cell. When the barrier is intact (defectfree), the I-V shows simple hysteresis without the presence of current peaks. On the other hand, when the barrier is defective, Cu is exposed to electrolyte and current peak is present in the I-V curve due to Cu redox reactions. The application of the developed method on an extensive number of real interconnects provides sufficient evidence that the method is simple, fast, and accurate in detecting the defective barrier. Furthermore, it has a potential to quantify defect density based on the intensity of the current peak and the integration areas within the I-V curves. Secondly, a step voltammetry-based method is developed to characterize pore structure by measuring the effective ions diffusivity. The study produces the identical activation energy and diffusivity results for bulk solution which are in good agreement with references, and reveals that electrolyte ions migrate in dense low  $\kappa$  (DLK) and PLK with different mechanism. The application of the method reveals that pores in low  $\kappa$  materials are not thermally stable but can either collapse or coalesce depending on the stress conditions.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                  | iii  |

|---------------------------------------------------|------|

| ABSTRACT                                          | v    |

| LIST OF ILLUSTRATIONS                             | xiii |

| LIST OF TABLES                                    | XX   |

| NOMENCLATURE                                      | xxi  |

| Chapter                                           |      |

| 1. INTRODUCTION                                   | 1    |

| 1.1 Motivation                                    | 1    |

| 1.2 Background                                    | 1    |

| 1.2.1 Modern Interconnect Technology              | 1    |

| 1.2.2 Cu Metallization: Dual-Damascene Process    | 7    |

| 1.2.3 Challenges in Cu/PLK Interconnect           | 10   |

| 1.2.3.1 Diffusion Barrier                         | 10   |

| 1.2.3.2 Low к Materials                           | 14   |

| 1.3 Objectives and Significance of This Thesis    | 20   |

| 1.4 Overview of Chapters                          | 21   |

| 2. STUDY ON THERMAL STABILITY OF Cu/PLK STRUCTURE | 23   |

| 2.1 Samples and Experimental                      | 23   |

| 2.1.1 Samples                                                                    | 23 |

|----------------------------------------------------------------------------------|----|

| 2.1.2 Experimental                                                               | 25 |

| 2.2 Results                                                                      | 26 |

| 2.2.1 Thermal Instability of Cu interconnect                                     | 26 |

| 2.2.1.1 Tested Under Air Ambient                                                 | 26 |

| 2.2.1.2 Tested Under Inert Ambient                                               | 29 |

| 2.2.2 Microscopy Characterization                                                | 30 |

| 2.3 Discussion: Mechanism of Thermal Instability                                 | 35 |

| 2.3.1 Oxidation Mechanism                                                        | 35 |

| 2.3.1.1 Source of Oxidants                                                       | 35 |

| 2.3.1.2 Oxidation Mechanism                                                      | 37 |

| 2.3.1.3 Kinetic Mechanism for Cu Out-Diffusion                                   | 38 |

| 2.3.2 Stress Mechanism                                                           | 41 |

| 2.3.3 The Role of Diffusion Barrier on Thermal Instability                       | 43 |

| 2.3.4 The Role of Porous Low κ Materials on Thermal<br>Instability               | 44 |

| 2.4 Summary                                                                      | 45 |

| 3. VOLTAMMETRY-BASED METHODOLOGY FOR<br>CHARACTERIZATION OF Cu/LOW-к INTEGRATION | 47 |

| 3.1 Motivation for a New Characterization Methodology                            | 47 |

| 3.2 The Proposed Characterization Methodology                                    | 49 |

| 3.2.1 The Methodology for Barrier Defects Characterization                       | 49 |

| 3.2.1.1 Cyclic Voltammetry Basic                                                 | 49 |

| 3.2.1.2 Electrolytic Cell for Voltammetry                             |

|-----------------------------------------------------------------------|

| 3.2.1.3 The Working Principle for Barrier Defect<br>Characterization  |

| 3.2.2 The Methodology for Low κ Structure Characterization            |

| 3.2.2.1 Step Voltammetry Basic                                        |

| 3.2.2.2 The Working Principle for Low κ Structure<br>Characterization |

| 3.3 Samples and Experimental Apparatus                                |

| 3.3.1 Samples                                                         |

| 3.3.2 Experimental Apparatus                                          |

| 3.4 Summary                                                           |

| 4. STUDY OF BARRIER STABILITY USING VOLTAMMETRY                       |

| 4.1 The Development of Fundamental Theory                             |

| 4.1.1 Sample and Test Condition                                       |

| 4.1.2 Simulation of Various Conditions of Diffusion Barriers          |

| 4.1.2.1 Simulation of Intact Barriers                                 |

| 4.1.2.2 Simulation of Symmetric Defective Barriers                    |

| 4.1.2.3 Simulation of Asymmetric Defective Barriers                   |

| 4.1.2.4 Simulation of Intact/Defective Barrier                        |

| 4.2 Barrier Detection for Real Interconnect                           |

| 4.2.1 Sample Preparation                                              |

| 4.2.2 Results                                                         |

| 4.2.2.1 Initial Conditions of as-Received Samples                     |

| 4.2.2.2 Cu Interconnect with Intact Barrier                                                        | 81  |

|----------------------------------------------------------------------------------------------------|-----|

| 4.2.2.3 Cu Interconnect with Equal Density of Defects in Barrier                                   | 83  |

| 4.2.2.4 Cu Interconnect with Unequal Density of Defects in Barrier                                 | 83  |

| 4.3 Reaction Mechanism of Cu in the Established System                                             | 86  |

| 4.3.1 Cu Reaction in the Established System                                                        | 86  |

| 4.3.2 Cu Reaction in Two Asymmetric Electrodes                                                     | 89  |

| 4.4 Significance and Consideration                                                                 | 91  |

| 4.4.1 Considerations for Industry Application                                                      | 91  |

| 4.4.2 The Potential Applications                                                                   | 92  |

| 4.4.2.1 Evaluation of Capping Layer Integrity                                                      | 92  |

| 4.4.2.2 Evaluation of Pore-seal Integrity                                                          | 96  |

| 4.4.2.3 Evaluation of Ionic Contamination for<br>Package Substrate                                 | 96  |

| 4.5 Summary                                                                                        | 97  |

| 5. CHARACTERIZATION AND INVETIGATION OF THERMAL<br>STABILITY FOR LOW-κ STRUCTURE USING VOLTAMMETRY | 99  |

| 5.1 Development of Characterization Technique                                                      | 100 |

| 5.1.1 Samples and Test Conditions                                                                  | 100 |

| 5.1.2 Current Profile in the Step Voltammetry Method                                               | 101 |

| 5.1.2.1 Charging vs. Discharging Current                                                           | 102 |

| 5.1.2.2 Discharging Current vs. Porosity                                                           | 105 |

| 5.1.3 Analytic Model for Discharging Current                                                       | 106 |

| 5.1.3.1 Concentration Profile of Ions during<br>Discharging Current | 106 |  |

|---------------------------------------------------------------------|-----|--|

| 5.1.3.2 The Solution of Discharging Current                         | 108 |  |

| 5.2 Characterization of Low κ Structure                             | 109 |  |

| 5.2.1 Effective Diffusivity of Electrolyte Ion                      | 109 |  |

| 5.2.2 Ion Diffusion Mechanism                                       | 111 |  |

| 5.3 Investigation of Structure Instability for PLK Materials        | 113 |  |

| 5.3.1 Samples and Test Conditions                                   | 113 |  |

| 5.3.2 Results and Discussion                                        | 114 |  |

| 5.4 Significance and Consideration                                  | 116 |  |

| 5.5 Summary                                                         | 117 |  |

| 6. CONCLUSION AND FUTURE WORK                                       |     |  |

| 6.1 Conclusions                                                     |     |  |

| 6.1.1 Thermal Failure of Cu/PLK Integration                         | 119 |  |

| 6.1.2 Characterization Technique: Voltammetry-based Method          | 120 |  |

| 6.1.2.1 Evaluation of Defects in Diffusion Barrier                  | 120 |  |

| 6.1.2.2 Characterization of Low κ Materials                         | 121 |  |

| 6.2 Future Work                                                     | 122 |  |

| 6.2.1 Characterization of Diffusion Barrier                         | 122 |  |

| 6.2.2 Characterization of Low κ Structure                           | 122 |  |

| 6.2.3 Extend Application of the Voltammetry Technique               | 123 |  |

| Appendix                                                            |     |  |

A. I-V MODEL OF A RC CIRCUIT WITH

| A LINEAR VOLTAGE SWEEP                    | 124 |

|-------------------------------------------|-----|

| B. THE SOLUTION FOR CONCENTRATION PROFILE | 128 |

| C. THE SOLUTION OF DISCHARGING CURRENT    | 132 |

| REFERENCES                                | 136 |

| BIOGRAPHICAL INFORMATION                  |     |

## LIST OF ILLUSTRATIONS

| Figure |                                                                                                                                                                                                                                                                                                      | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

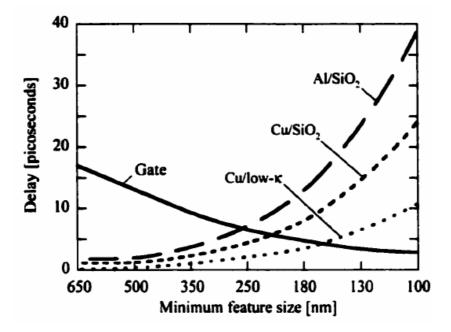

| 1.1    | Gate and interconnect delay as a function of minimum feature size for Al/SiO <sub>2</sub> , Cu/SiO <sub>2</sub> and Cu/low $\kappa$ interconnects                                                                                                                                                    | . 2  |

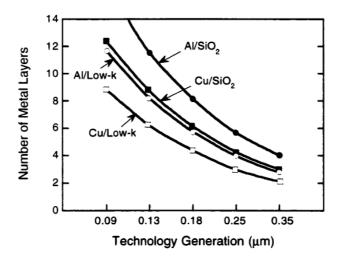

| 1.2    | The requirement metal layers for technology generation with various interconnect/low $\kappa$ construction.                                                                                                                                                                                          | . 4  |

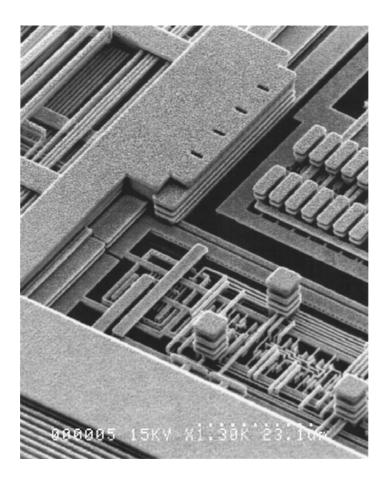

| 1.3    | Cu metallization characteristic of six-level structure (Courtesy of T.Way, IBM Microelectronics Division, Burlington, VT)                                                                                                                                                                            | 5    |

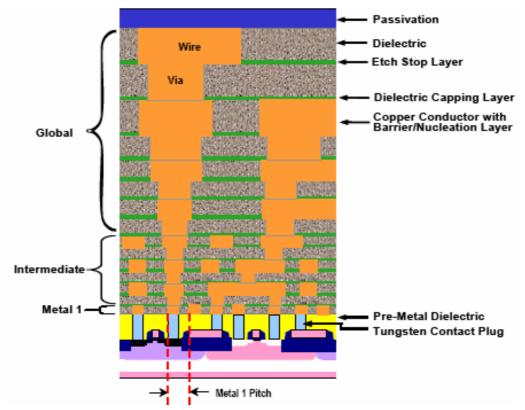

| 1.4    | A cross-section of hierarchical scaling-MPUs (Microprocessor)<br>devices (2005 ITRS roadmap, Interconnect)                                                                                                                                                                                           | . 6  |

| 1.5    | Process flow comparison for Al RIE vs. Cu Dual-Damascene                                                                                                                                                                                                                                             | . 8  |

| 1.6    | Process flow comparison for Al RIE vs. Cu Dual-Damascene<br>(Continuation of figure 1.5)                                                                                                                                                                                                             | . 9  |

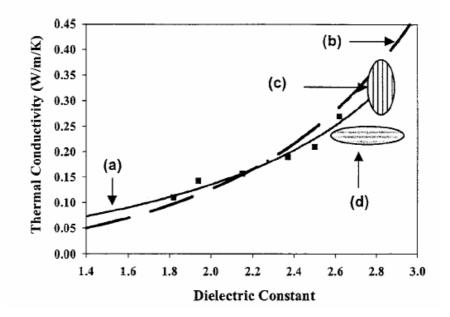

| 1.7    | Correlation of thermal conductivity and dielectric constant (dark square) represents the experimental data for the porous MSQ. Curve (a) is for the porous MSQ and (b) for the porous silica. Oval (c) includes various dense ISG materials, and (d) includes various dense polymeric low $\kappa$ . | . 16 |

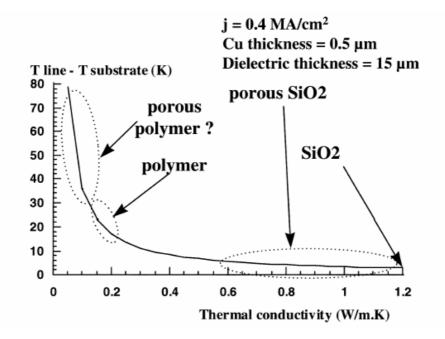

| 1.8    | Interconnect line temperature increase ( $T_{line}$ - $T_{substrate}$ ) as a function of the dielectric thermal conductivity                                                                                                                                                                         | . 17 |

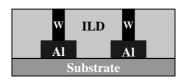

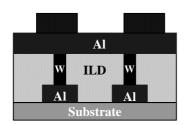

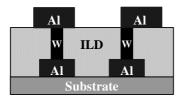

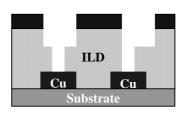

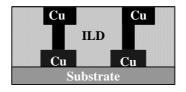

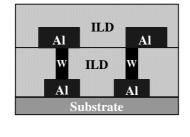

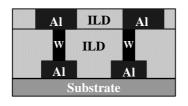

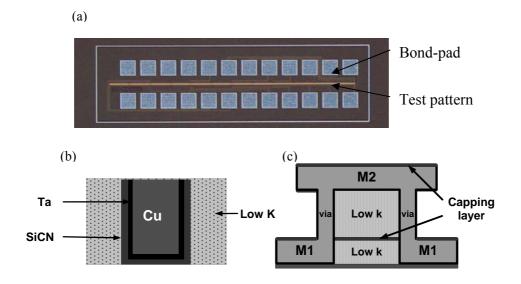

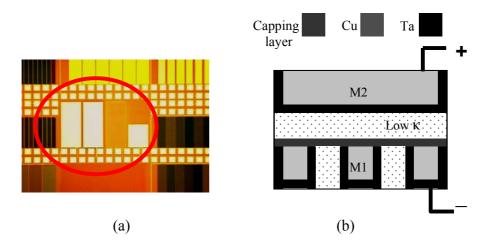

| 2.1    | <ul><li>(a) An optical image of test pattern; a cross section schematic of</li><li>(b) one level (c)two level Cu/barrier/PLK structure</li></ul>                                                                                                                                                     | . 24 |

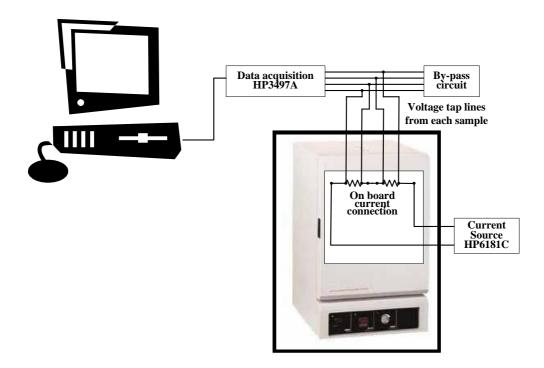

| 2.2    | A schematic representative of the experimental apparatus                                                                                                                                                                                                                                             | . 26 |

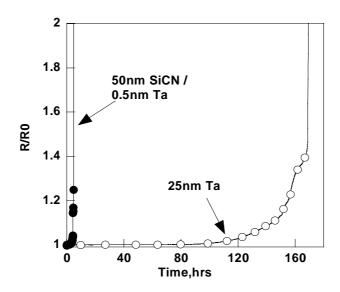

| 2.3    | A plot showing resistance (ratio) of a $0.25\mu$ m single level Cu<br>interconnect with different barrier arrangement baked at 275°C with<br>low level intermittent current, 0.1 mA/cm <sup>2</sup> in air atmosphere                                                                                | . 27 |

| 2.4  | A plot showing resistance (ratio) of a single level with different barrier arrangement and temperature with low level intermittent current, $0.1 \text{mA/cm}^2$ in air atmosphere.                                                                                                                                                                                                                                                                                                                                                               | 28 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.5  | A plot showing resistance (ratio) of a single level, $0.25\mu$ m Cu lines<br>with 25nm Ta barrier as a function of baking time at 325°C. Note<br>that N <sub>2</sub> /Ar ambient substantially delays the failure, but cannot<br>prevent the process.                                                                                                                                                                                                                                                                                             | 29 |

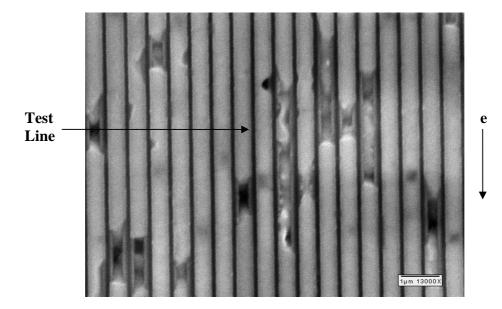

| 2.6  | A typical SEM top-down image taken from 0.25µm wide Cu lines<br>with a 30SiCN/2Ta barrier after 135 hours of baking at 225°C. Note<br>only one of Cu lines is applied current in this test pattern.                                                                                                                                                                                                                                                                                                                                               | 30 |

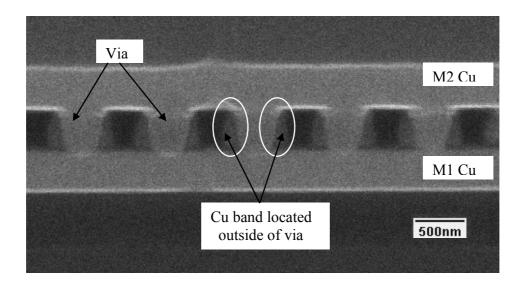

| 2.7  | A typical SEM cross-section image of vias under bond pad in two-<br>level Cu interconnect with 25nm Ta after 45 hours of baking at 225°C.<br>Note that Cu bands from outside of each via (both sides)                                                                                                                                                                                                                                                                                                                                             | 31 |

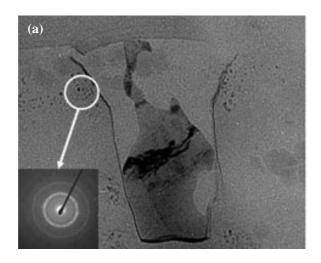

| 2.8  | Cross-section TEM images, taken after baking (a) at 275°C in air<br>showing the formation of dark spots contrast near to a 0.25 $\mu$ m Cu<br>trench with 50 nm SiCN/0.5nm Ta arrangement. (b) at 225°C in air<br>showing band and spots of dark contrast near to 0.25 $\mu$ m Cu trench<br>with 30 nm SiCN/2nm Ta arrangement. The diffraction ring pattern<br>analysis taken from the circle areas indicates that Cu exists outside<br>the trench as the stable oxide phases, either CuO after 225°C baking<br>or Cu <sub>2</sub> O after 275°C | 32 |

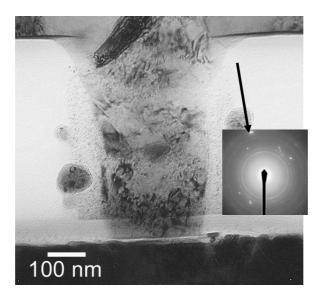

| 2.9  | <ul> <li>A top-down view TEM micrograph after baking at 275°C in Ar/ N<sub>2</sub> ambient showing no noticeable Cu out diffusion observed in PLK next to a 0.25μm Cu trench with 25nm Ta arrangement.</li> <li>(a) An extrusion was observed through Ta barrier of the sample tested in Ar ambient (b) No noticeable extrusion was observed of the samples tested in N<sub>2</sub> ambient.</li> </ul>                                                                                                                                           | 34 |

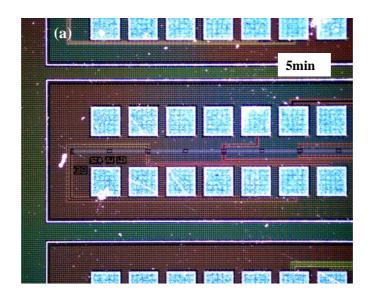

| 2.10 | Optical images show the micrograph of acetone infiltration into<br>Cu/PLK structure from the edge after 5 min even with the presence<br>of the scribe seal. Note the dark contrast indicates the infiltration of<br>acetone (a) dark field (b) bright field                                                                                                                                                                                                                                                                                       | 36 |

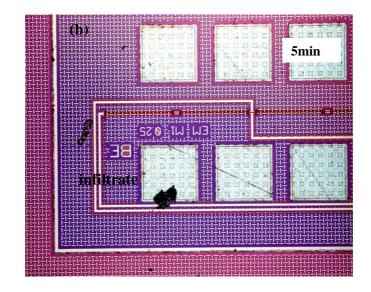

| 2.11 | Failure mechanism driven by oxidation potential (a) Cu interconnect fails by Cu out-diffusion into PLK forming Cu <sub>x</sub> O there and leaving                                                                                                                                                                                                                                                                                                                                                                                                |    |

| voids in the lines (b) Normal oxidation occurs by interdiffusion between Cu and O through Cu <sub>x</sub> O without voiding formation                                                                                                                                                                                           | 37 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

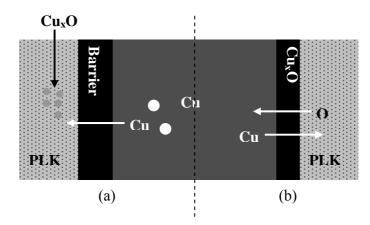

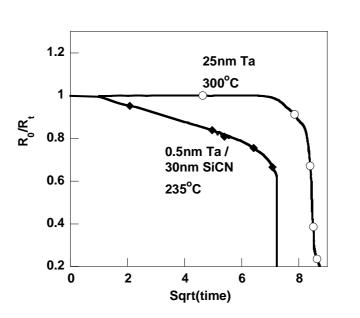

| 2.12 A plot displays the reciprocal resistance ratio of 0.25µm Cu lines with different barrier arrangement and temperature as a function of the root of baking time                                                                                                                                                             | 40 |

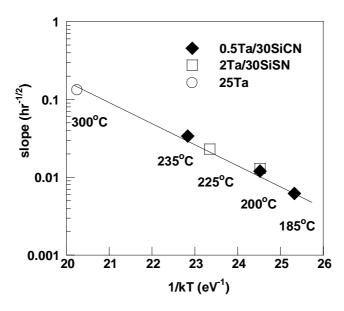

| 2.13 A plot showing the slope of $R_0/R_t$ vs. t <sup>1/2</sup> for various temperature and barrier as a function of 1/KT.                                                                                                                                                                                                      | 41 |

| <ul> <li>2.14 (a) Cu diffuses out of the line through the defects in diffusion barrier in Ar test (b) the reaction of Ta and N<sub>2</sub> repairs the defects in diffusion barrier protecting Cu out diffusion in N<sub>2</sub> ambient.</li> </ul>                                                                            | 42 |

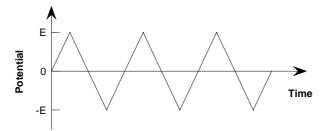

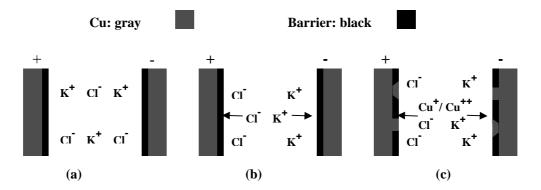

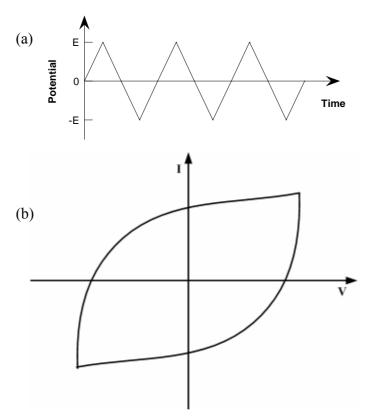

| 3.1 The potential waveform in a cyclic voltammetry                                                                                                                                                                                                                                                                              | 50 |

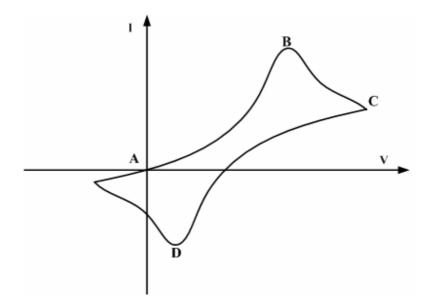

| 3.2 The typical current-voltage (I-V) curve in a cyclic voltammetry                                                                                                                                                                                                                                                             | 51 |

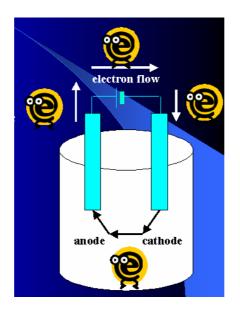

| 3.3 A schematic of a two-electrode electrochemical cell                                                                                                                                                                                                                                                                         | 52 |

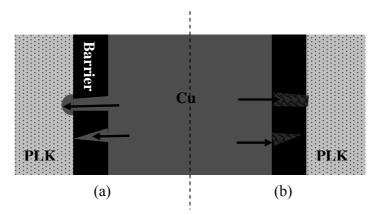

| 3.4 A schematic for working principle (a) Electrolyte solution infiltrates<br>in the two electrodes (b) The current resulted from ionic charging under<br>the applied voltage in the case of an intact barrier (c) The current<br>resulted from both Cu redox reaction and ionic charging in the case<br>of a defective barrier | 54 |

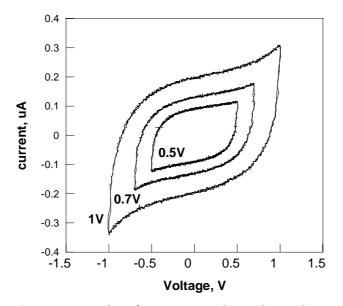

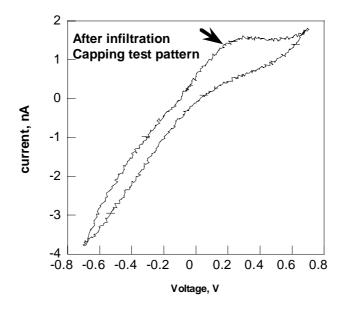

| 3.5 An intact barrier presents the hysteresis I-V curve (b)<br>under a cyclic potential sweep (a)                                                                                                                                                                                                                               | 55 |

| 3.6 The presence of current peaks suggests a defective barrier                                                                                                                                                                                                                                                                  | 56 |

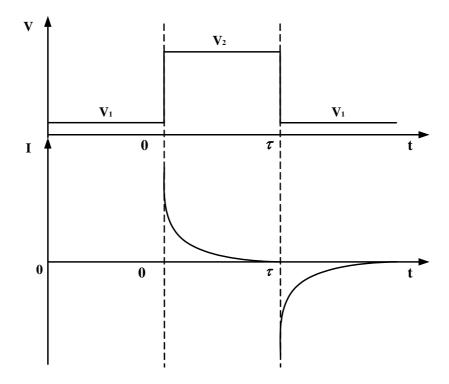

| 3.7 The waveform of potential step voltammetry and the responding current as a function of time                                                                                                                                                                                                                                 | 57 |

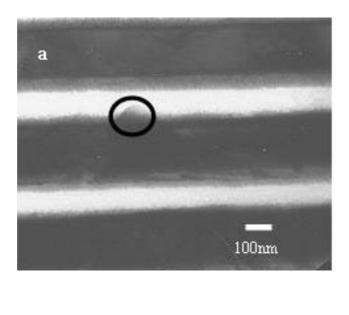

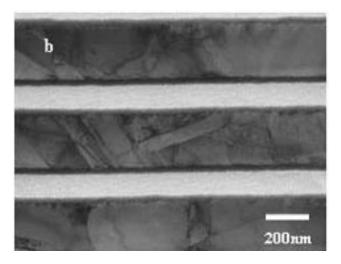

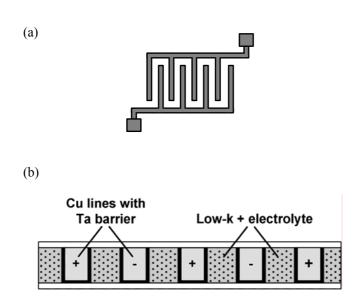

| <ul><li>3.8 A schematic diagram of (a) comb pattern</li><li>(b) a cross-section comb structure test pattern</li></ul>                                                                                                                                                                                                           | 60 |

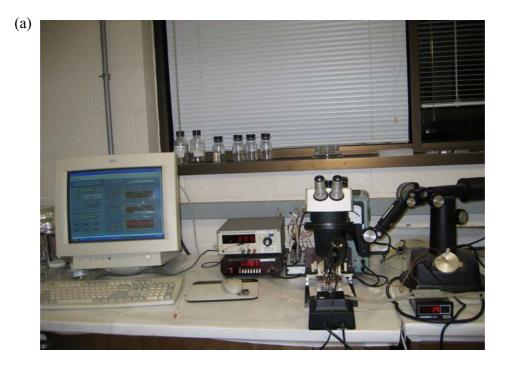

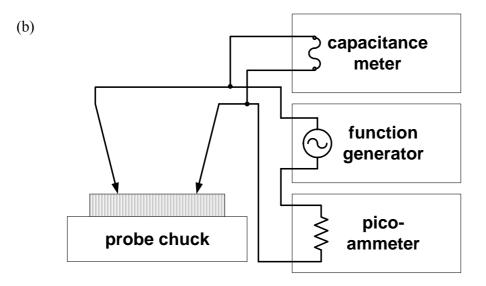

| 3.9 A picture (a) and a circuit schematic (b) of the build up apparatus                                                                                                                                                                                                                                                         | 61 |

| 4.1 Schematic diagrams for idealized samples with controlled Cu fraction (0-100%) used for fundamental study xv                                                                                                                                                                                                                 |    |

|      | (a) top-down view (b) cross-section view                                                                                                                                                                                                                    | 65 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2  | A schematic diagram of I-V test using idealized samples                                                                                                                                                                                                     | 66 |

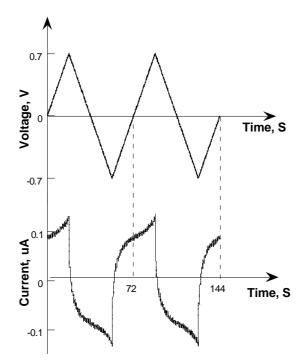

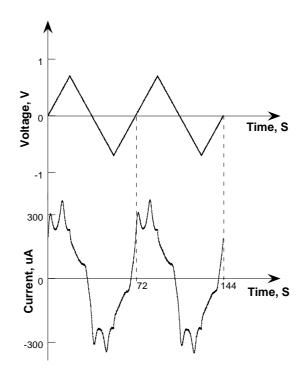

| 4.3  | The typical current data as a function of time under the applied cyclic voltage in the case of two Ta electrodes, simulating the intact diffusion barrier                                                                                                   | 67 |

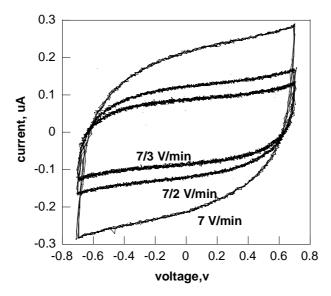

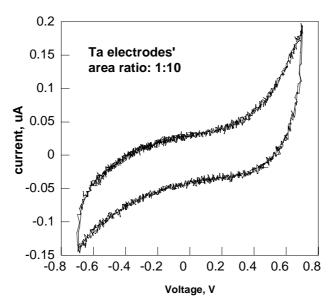

| 4.4  | I-Vs are taken from two Ta electrodes at various sweep rates                                                                                                                                                                                                | 68 |

| 4.5  | I-Vs are taken from two Ta electrodes under various sweep voltages                                                                                                                                                                                          | 68 |

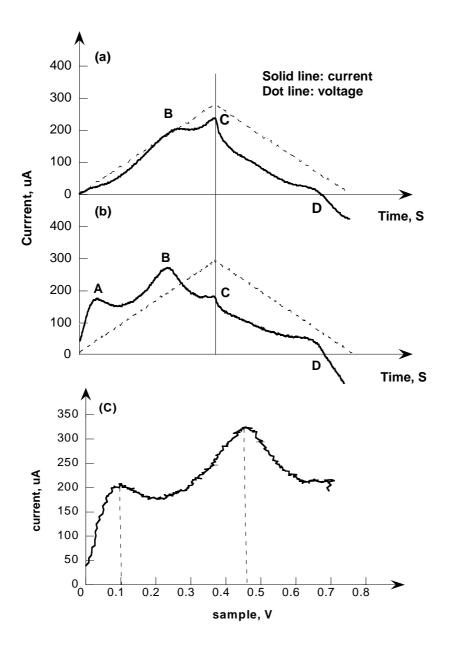

| 4.6  | The typical current data as a function of time under the applied cyclic voltage in the case of electrode with symmetric Cu fraction (100% Cu on two mating electrodes in this figure) simulating the defective diffusion barrier with equal defects density | 69 |

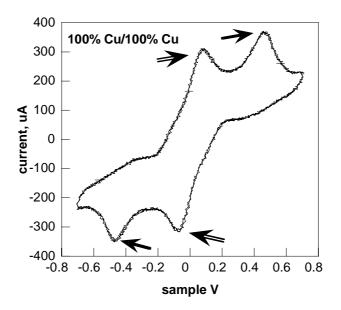

| 4.7  | A typical I-V is taken from two Cu electrodes (100% Cu)                                                                                                                                                                                                     | 70 |

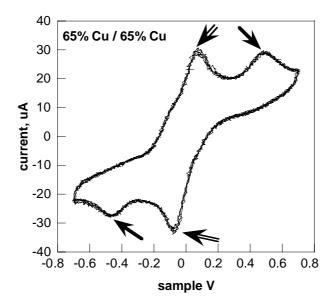

| 4.8  | A typical I-V is taken from two identical electrodes<br>with 65% Cu exposure                                                                                                                                                                                | 71 |

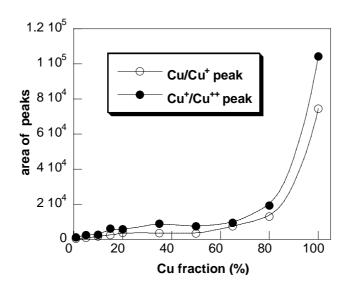

| 4.9  | The peak area as a function of Cu fraction in idealized samples                                                                                                                                                                                             | 72 |

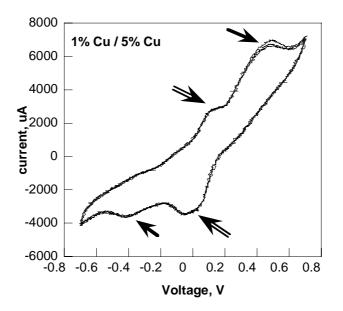

| 4.10 | I-V taken from electrodes with asymmetric Cu fraction,<br>1% Cu vs. 5%Cu                                                                                                                                                                                    | 73 |

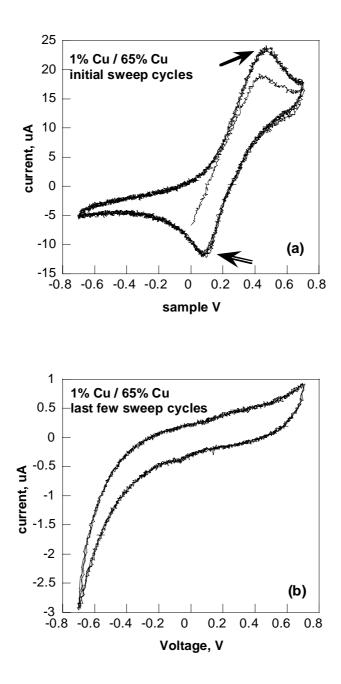

| 4.11 | The I-Vs taken from electrodes with asymmetric Cu fraction, 1%Cu vs. 65%Cu at (a) initial sweep cycle (b) very last sweep cycle                                                                                                                             | 74 |

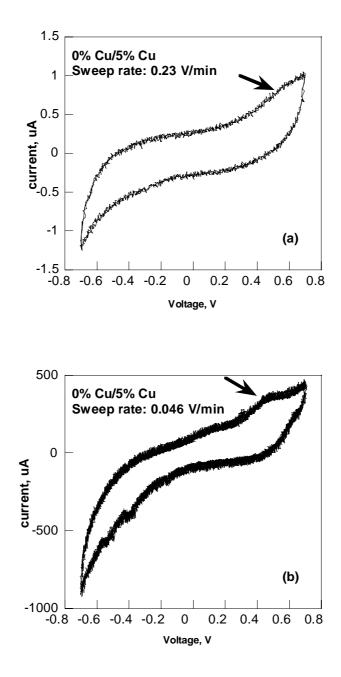

| 4.12 | The I-Vs taken from electrodes with asymmetric Cu fraction, 0%Cu vs. 5% Cu, at (a) sweep rate: 0.23 V/min (b) sweep rate: 0.046V/min                                                                                                                        | 76 |

| 4.13 | An I-V curve taken from two Ta electrodes with asymmetric electrodes' areas: one electrode has an area of $1 \times 1$ cm <sup>2</sup> and the other has an area of $10 \times 1$ cm <sup>2</sup> .                                                         |    |

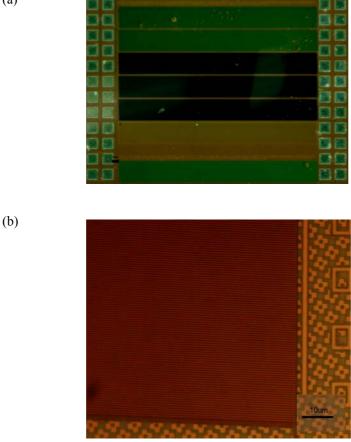

| 4.14 | The optical image of Cu/DLK interconnect with comb/via chain<br>Structure (a) low magnification (b) high magnification                                                                                                                                      | 79 |

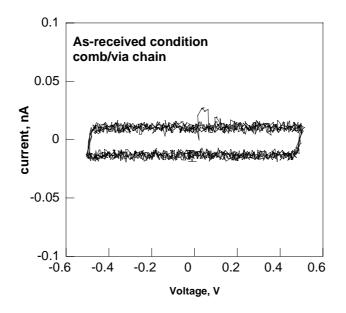

| 4.15 | A typical I-V taken from the initial condition of single level Cu/PLK interconnects with comb structure                                                                                                                                                                  | 80 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

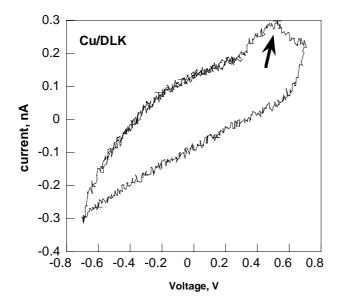

| 4.16 | A typical I-V taken from the initial condition of two-level Cu/DLK interconnects with comb/via chain structure                                                                                                                                                           | 81 |

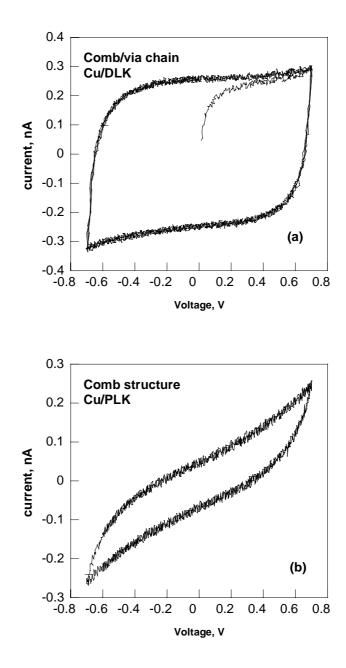

| 4.17 | The representative I-Vs show a simple hysteresis, indicating<br>an intact barrier, taken from (a) two level Cu/10nmTa/DLK<br>with comb/via chain structure (b) single level<br>Cu/25nmTa/PLK interconnect with comb structure                                            | 82 |

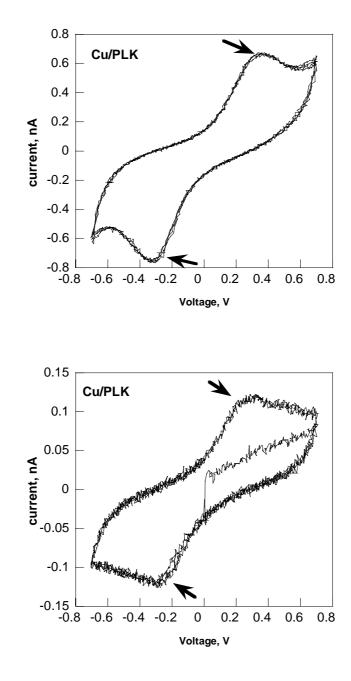

| 4.18 | I-V curves, taken from singel level comb structure Cu/25nmTa/PLK interconnect, show show symmetric current peaks, suggesting defective barrier with equal defects density                                                                                                | 84 |

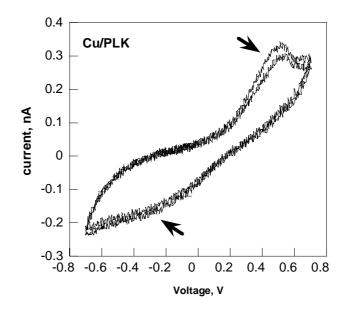

| 4.19 | The I-Vs, taken from taken from single level comb structure<br>Cu/25nm/PLK interconnect, shows asymmetrical current peaks,<br>suggesting that one barrier is more defective than the other                                                                               | 85 |

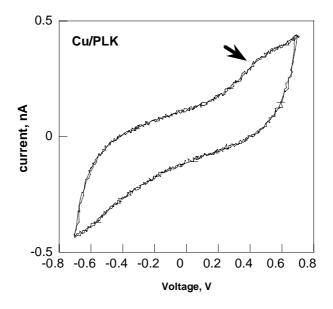

| 4.20 | I-V, taken from single level comb structure Cu/25nmTa/PLK interconnect, shows a single peak for forward sweep, suggesting one intact and one defective barrier                                                                                                           | 85 |

| 4.21 | The I-V, taken from two level comb/via chain structure<br>Cu/10nmTa/DLK interconnect, shows a single peak for forward<br>sweep, suggesting one intact barrier and one defective barrier                                                                                  | 86 |

| 4.22 | Plots of Cu redox reaction as a function of time and applied voltage<br>(a) I/V-t curves for the first half-cycle (0V-0.7V-0V) potential sweep<br>(b) I/V-t curves for a half-cycle potential sweep (after the first cycle)<br>(c) I-V curve for 0V-0.7V potential sweep | 88 |

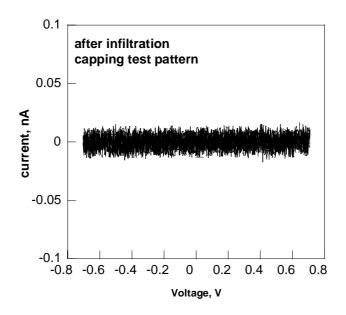

| 4.23 | An optical image of capping layer test pattern and its schematic representative cross section. Note both M1 and M2 are Cu                                                                                                                                                | 93 |

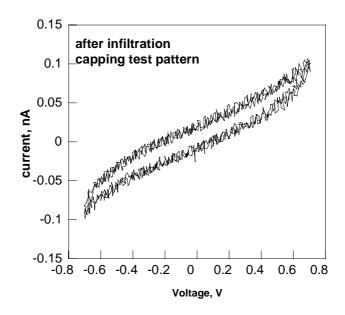

| 4.24 | A representative I-V, taken from the samples after immersed<br>into electrolyte solution, does not show any current signal,<br>suggesting an intact capping layer.                                                                                                       | 94 |

| 4.25 | A representative I-V shows a simple hysteresis, suggesting<br>a defective capping layer                                                                                                                                                                                  | 95 |

| 4.26 | An example of a defective capping layer shows a current peak                                                                                                                                                                                    | . 95  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

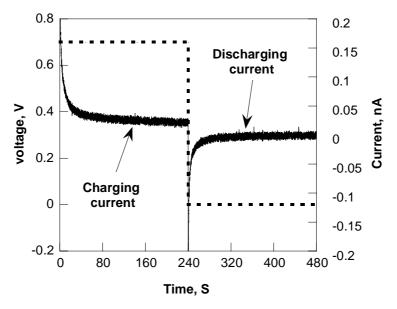

| 5.1  | Current as a function of time under double step voltage sweep taken<br>from single level 0.25µm Cu/PLK interconnects with 0.30µm space                                                                                                          | . 101 |

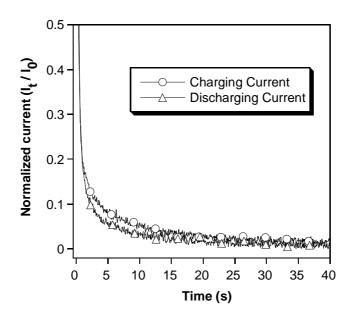

| 5.2  | A comparasion of current decay during charging and discharging process, taken from single level $0.25 \mu m$ Cu/PLK interconnects with $0.30 \mu m$ space                                                                                       | . 102 |

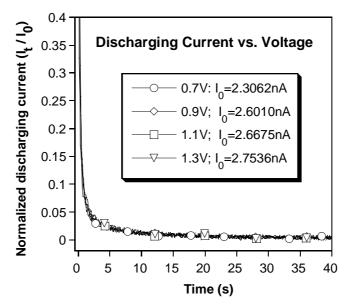

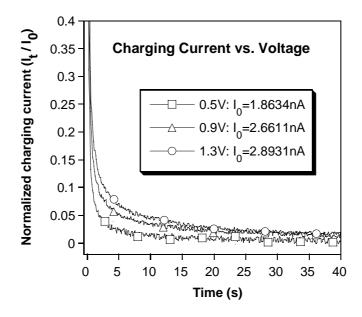

| 5.3  | The impact of applied voltage on discharging current, taken<br>from 0.175µm single level Cu/PLK interconnects with<br>0.175µm space. The initial current values responding to<br>various voltages are given in the plot.                        | . 103 |

| 5.4  | The impact of applied voltage on charging current, taken<br>from 0.25µm single level Cu/PLK interconnects with 0.30µm<br>space. The initial current values responding to various<br>voltages are given in the plot                              | . 104 |

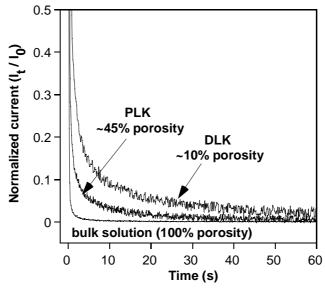

| 5.5  | Normalized discharging current as a function of time measured<br>at 25°C for three different sample groups. For clarity, the high<br>current spike is runcated. Note also that the all cell currents<br>diminish to zero at the long time limit | . 105 |

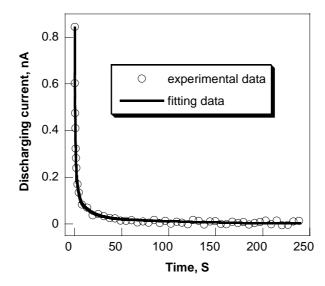

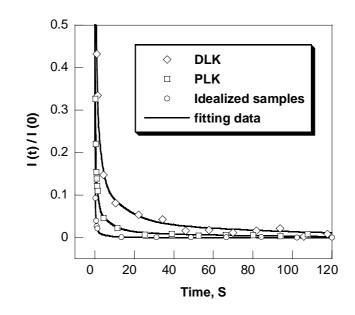

| 5.6  | Discharging current is taken from Cu/DLK and its fitting data                                                                                                                                                                                   | . 109 |

| 5.7  | Discharging current as a function of time with varying porosity of dielectrics between two mating electrodes: Group 1 is Cu/DLK with ~10% porosity; Group 2 is Cu/PLK with ~45% porosity and group 3 is idealized sample with 100% porosity     | . 110 |

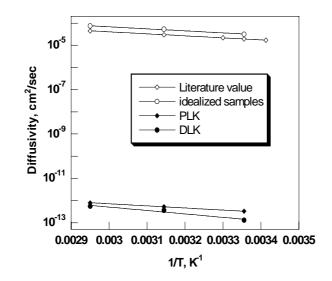

| 5.8  | Diffusivities of ions as a function of reciprocal temperature                                                                                                                                                                                   | . 112 |

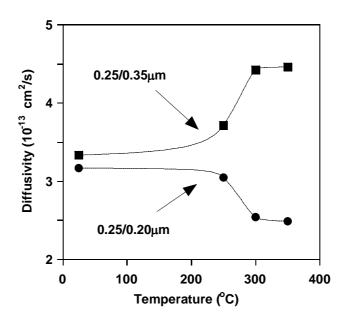

| 5.9  | Diffusivity in DLK as a function of the annealing temperature.<br>Circles represent comb structure patterns of $0.25\mu m$ Cu line and $0.20\mu m$ low $\kappa$ spacing, while squares represent those with $0.35\mu m$ low $\kappa$            | . 114 |

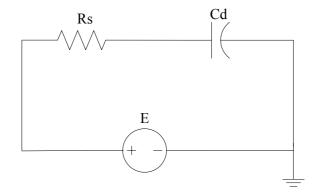

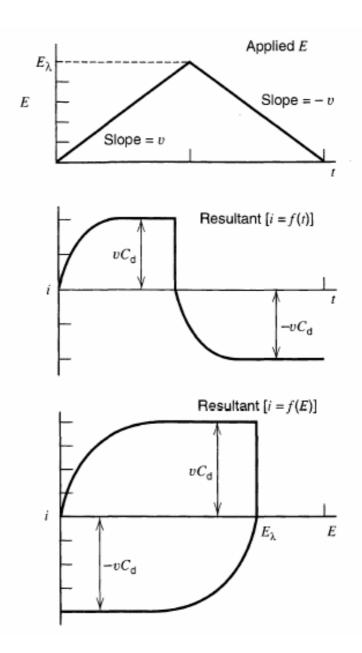

| A.1  | A Schematic of an RC circuit                                                                                                                                                                                                                    | . 125 |

| A.2  | Curent-time (i-t) behavior resulting from a linear                                                                                                                                                                                              |       |

|     | potential sweep applied to an RC circuit                                                                  | . 126 |

|-----|-----------------------------------------------------------------------------------------------------------|-------|

| A.3 | Curent-time and current potential (i-E) resulting from a cyclic linear potential applied to an RC circuit | 127   |

## LIST OF TABLES

| Table |                                                                                    | Page |

|-------|------------------------------------------------------------------------------------|------|

| 1.1   | ITRS Roadmap 2005 Edition.                                                         | 6    |

| 5.1   | The effective ions diffusivity of three groups of samples                          | 110  |

| 5.2   | Effective diffusivity of electrolyte ions measured at three different temperatures | 111  |

## NOMENCLATURE

| BTS  | biased thermal stressing                           |

|------|----------------------------------------------------|

| С    | capacitance                                        |

| СМР  | chemical-mechanical polishing                      |

| CTE  | coefficient thermal expansion                      |

| CVD  | chemical vapor deposition                          |

| DLK  | dense low $\kappa$                                 |

| EM   | electromigration                                   |

| IC   | integrated circuit                                 |

| ILD  | interlayer dielectric                              |

| ITRS | International Technology Roadmap for Semiconductor |

| I-V  | current-voltage                                    |

| к    | dielectric constant                                |

| MPU  | microprocessor                                     |

| MSQ  | methyl silsesquioxane                              |

| PALS | positronium annihilation lifetime spectroscopy     |

| PLK  | porous low κ                                       |

| Ps   | positronium                                        |

| PVD  | physical vapor deposition           |

|------|-------------------------------------|

| R    | resistance                          |

| RIE  | reactive-ion etching                |

| SAXN | small angle x-ray and neutron       |

| SEM  | scanning electron microscopy        |

| SXR  | specular x-ray reflectivity         |

| TEM  | transmission electron microscopy    |

| TDDB | time dependent dielectric breakdown |

| ULSI | ultra-large scale integration       |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Motivation

The transition to Cu/low  $\kappa$  interconnect from Al/SiO<sub>2</sub> creates many challenges for future microelectronic devices. Among those, the development of a reliable diffusion barrier and successful implementation of porous low  $\kappa$  (PLK) are considered as two of the most critical challenges for a reliable Cu interconnect. The continuous shrinking in thickness of the diffusion barrier coupled with the incorporation of pores in low  $\kappa$  materials enables new failure mechanisms which are not found in Cu/SiO<sub>2</sub> and Cu/dense low  $\kappa$  (DLK) interconnect structures. Therefore it is necessary to investigate the potential factors that create new failure mechanisms in this structure to optimize the manufacturing processing and achieve a reliable and functional device. However, the efforts are slowed by the conventional characterization techniques that used to be suitable for Al/SiO<sub>2</sub> and/or Cu/DLK. Therefore it is extremely critical to develop new metrologies for advanced Cu/PLK integration.

#### 1.2 Background

#### 1.2.1 Modern Interconnect Technology

Since Jack Kilby demonstrated integrated circuit (IC) in 1958, the feature size continuously has scaled down and the density of devices will keep increasing in modern

IC as long as fundamental limits allow. The miniaturization coupled with high devices density results in a tremendous cost advantage and faster transistor switching times, and thereby improves the performance [1, 2]. However, the aggressive miniaturization of IC devices as well as the requirement for multiple metallization layers creates lots of challenges, and one of the most fundamental challenges is known as interconnect RC (product of resistance and capacitance) delay.

With the continuous reduction in the dimension of devices, the conducting wires, referred to as interconnects, are becoming narrower and more-closely spaced. Consequently, the resistance (R) of an interconnect increases due to the reduction in its cross-sectional area and the capacitance (C) of interlayer dielectric (ILD) materials increases because of the closer space between the interconnects. This phenomenon is

Figure 1.1 Gate and interconnect delay as a function of minimum feature size for Al/SiO<sub>2</sub>, Cu/SiO<sub>2</sub> and Cu/low  $\kappa$  interconnects [4]

referred as interconnect RC delay, which becomes the bottleneck and limits the speed of logic devices instead of gate delay as the devices scale down into the submicron regions [3,4], as shown in figure 1.1.

The attempt to reduce the interconnect RC delay initiated an extensive study of new materials in the microelectronics industry to replace the Al/SiO<sub>2</sub> interconnect that suffers from major limitations in RC delay due to its relatively high electrical resistivity. The selection of proper materials for advanced ICs is guided by the definition of RC delay, which is given by equation 1.1 [8]

$$RC = \frac{\rho}{t^{M}} \frac{L^{2} \kappa \varepsilon_{0}}{t_{ILD}}$$

(1.1)

where  $\rho$ ,  $t^M$ , L are the resistivity, thickness, length of the interconnection, and  $\varepsilon_0$ ,  $\kappa$  and  $t_{ILD}$  are permittivity of free space, interlevel dielectric (ILD) constant and thickness, respectively. As implied in the equation, the RC delay can be reduced by choosing the materials with low resistivity ( $\rho$ ) as the interconnect and low dielectric permittivity ( $\epsilon$ ) as the insulator.

Of the metals with lower resistivity than Al (Ag, Cu and Au), Cu has been considered to be the best candidate to replace Al as interconnects due to its low resistivity, high electromigration (EM) resistance and its simple and low cost processing [6-9]. Its lower resistivity of 1.67 $\mu$ Ω-cm versus 2.69 $\mu$ Ω-cm for Al, provides significant benefit to RC delay. Although Ag has the lowest room temperature resistivity of any metal (1.60 $\mu$ Ω-cm), the difficulties in processing and rapid diffusion in dielectrics especially in the presence of an electric field make it less desirable than others.

Figure 1.2 The requirement metal layers for technology generation with various interconnect/low  $\kappa$  construction [5]

In the past years, Cu has been used as interconnects in commercial chips primarily due to its low resistivity [10-11]. By using Cu, narrow lines can be used to carry the same amount of current, and a tighter packing density can be achieved per interconnect level. This means that fewer levels of metal are needed for the entire interconnect structure, leading to significant reduction of manufacturing costs. As seen in figure 1.2, it requires 8 to 9 metallization layers for 90nm technology node if using Cu/low  $\kappa$  instead of 11 to 12 layer if using Al/low  $\kappa$  [5]. The early chip technology combined up to six Cu wiring levels at ULSI (ultra-large scale integration) densities, as shown in figure 1.3.[12-13]. Figure 1.4 shows a cross-section of hierarchical scaling-MPUs (Microprocessor) devices presenting in 2005 International Technology Roadmap for Semiconductors (ITRS) in Interconnect section. It shows a high number of metal layers with a hierarchical wiring approach of steadily increasing pitch and thickness at each conductor level to alleviate the impact of interconnect delay on performance[14].

Figure 1.3 Cu metallization characteristic of six-level structure (Courtesy of T.Way, IBM Microelectronics Division, Burlington, VT)

Meanwhile, extensive study has been conducted to investigate low dielectric constant ( $\kappa$ ) materials, both organic and inorganic, to replace conventional SiO<sub>2</sub> [15-17]. Based on 2005 ITRS for interconnect (table 1.1), the target for  $\kappa$  value of the low  $\kappa$  materials is less than 1.6 in 2020 [14]. None of the dense dielectric low  $\kappa$  (DLK) materials is found to achieve such low  $\kappa$ , and therefore pores are being introduced into the low  $\kappa$  materials to further reduce the  $\kappa$  value to meet the needs for future technology

since vacuum has the lowest  $\kappa$  value of 1 [18-21]. They are termed porous low  $\kappa$  (PLK) materials.

Figure 1.4 A cross-section of hierarchical scaling-MPUs (Microprocessor) devices (2005 ITRS roadmap, Interconnect)

Table 1.1 ITRS Roadmap 2005 Edition [14]

| Year                      | 2007 | 2008 | 2009 | 2010 | 2011 | 2013 | 2015 | 2017 | 2020 |

|---------------------------|------|------|------|------|------|------|------|------|------|

| Technology<br>Node (nm)   | 65   | 57   | 50   | 45   | 40   | 32   | 25   | 20   | 14   |

| Metal Levels              |      | 12   | 12   |      | 12   | 13   | 13   | 14   | 14   |

| Barrier<br>thickness (nm) | 4.8  | 4.3  | 3.7  | 3.3  | 2.9  | 2.4  | 1.9  | 1.5  | 1.1  |

| ILD- $\kappa_{bulk}$      | ≤2.4 | ≤2.4 | ≤2.2 | ≤2.2 | ≤2.2 | ≤2.0 | ≤1.8 | ≤1.8 | ≤1.6 |

#### 1.2.2 Cu Metallization: Dual-Damascene Process

The flow of dual-damascene processing has been well established for Cu fabrication during the past years because the conventional reactive-ion etching (RIE) of Cu films has an unacceptably low etching rate due to the low vapor pressure of Cu halides at room temperature [22].

The dual-damascene process flow is illustrated schematically in figure 1.5. For comparison, the conventional Al RIE process is also described. In the dual damascene process, the planar dielectric layer is deposited first and the metallization pattern is etched into this dielectrics. Metals, including a thin diffusion barrier layer and a thin seed layer for the subsequent Cu deposition process, are then deposited by either physical vapor deposition (PVD) or chemical vapor deposition (CVD). A Cu layer is deposited by electroplating to fill the metallization patterns, and the excess metal and barrier layer are then removed by a chemical-mechanical polishing (CMP) process, which provides a planar surface with in-laid interconnect patterns. Finally, a thin layer of silicon nitride is deposited to form a passivation layer [23].

As is seen in figure 1.5, the dual Damascene process involves fewer steps than the RIE process used to fabricate Al interconnects. It eliminates or reduces the need for some of the most difficult and costly steps. For example, dielectrics (ILD) CMP is eliminated. Some steps are simiplified: ILD gap-fill, a challenging issue in Al process, is replaced by simple planar deposition in Cu damascene, Al RIE is replaced by the simpler and higher-integrity ILD RIE in Cu damascene, and W CVD is replaced by Cu electroplating, which costs only about 1/3-1/5 of W CVD. In addition, Cu lines and vias

#### Al RIE **Cu Dual Damascene** (1) Al deposition (1) ILD deposition Al ILD Substrate Substrate (2) Line patterning/ILD etching (2) Line patterning/etching ILD ILD ILD Al Al Substrate (3) Cu deposition and CMP (3) ILD deposition and CMP ILD Cu ILD Cu ILD Substrate ILD Al Al Substrate (4) ILD planar deposition (4) Via patterning/etch ILD Cu Cu Substrate ILD Al Al Substrate (5) Via/line patterning (5) W deposition and CMP

Figure 1.5 Process flow comparison for Al RIE vs. Cu Dual-Damascene

ILD

Substrate

Cu

Cu

#### Al RIE

#### (6) Al deposition and patterning

(7) Al line etch

(8) ILD gap-fill deposition

#### **Cu Dual Damascene**

#### (6) Via/line etching

(7) Cu line/via deposition and CMP

Figure 1.6 Process flow comparison for Al RIE vs. Cu Dual-Damascene. (Continuation of figure 1.5)

can be formed simultaneously in the dual-damascene process, which offers the added benefit of 50% reduction in the number of line-via interfaces.

The dual-damascenc process significantly reduces manufacturing cost. At the same time, the application of Cu/low  $\kappa$  integration improves performance of the devices. Such benefits drive the semiconductor industry inevitably to Cu interconnects.

#### 1.2.3 Challenges in Cu/PLK Interconnect

Although the basic process flow for Cu/low  $\kappa$  interconnects has been well defined over the past few years, several technical challenges of an unforeseen nature have arisen when introducing the new materials into manufacturing.

#### 1.2.3.1 Diffusion Barrier

The shift to the Cu interconnect brings about many benefits for advanced IC due to its low resistivity and its simple and low cost processing, however, the integration of Cu requires the presence of a diffusion barrier because of the high diffusivity of Cu into dielectrics and silicon, which seriously degrades the electronic properties of silicon devices [24-26]. Unfortunately, Cu does not form a stable native oxide layer to act as a diffusion barrier (as  $Al_2O_3$  does in Al based interconnect) to prevent Cu from diffusion into the dielectrics and silicon. Therefore a diffusion barrier for Cu interconnect must be inserted. Also such a layer is needed to enhance the adhesion between Cu and the various low  $\kappa$  materials [27-29].

A barrier is important in improving eletromigration (EM) performance, one of the primary reliability failure mechanisms in IC devices. EM is a result of the momentum exchange between conducting electrons and metal atoms that causes a net diffusion of metal atoms in the direction of electron flow. The resultant metal flux divergence causes the formation of voids at the cathode and/or extrusion at the anode. Voiding at the cathode can result in an electrical resistance increase or open circuit in the interconnect line, and metal extrusion at the anode can cause an electrical short to the neighboring lines [30-32].

EM basically is a diffusion phenomenon, so any efforts to reduce diffusion could improve the EM performance. It was well known that the fastest diffusion paths for Cu in the damascene interconnects structure occur at two interfaces: Cu/diffusion barrier and Cu/cap layer. A barrier providing good adhesion to Cu as well as low  $\kappa$  materials minimizes Cu diffusion along the Cu/barrier interface, and therefore improves the EM performance [32, 34]. Furthermore, the good barrier coverage in the trenches is a prerequisite for uniform Cu seed layer deposition and good Cu fill by electrochemical plating, and therefore reduces the probability for void formation during Cu deposition, which can significantly degrade the EM performance. In addition, the barrier also directly impacts EM by shunting current when void formations interrupt the current path. For this function, the barrier should be a good electrical conductor, such as Ta, and have good coverage and a reasonable thickness [33-35].

A desirable diffusion barrier is the material that provides excellent performance in preventing the diffusion and intermixing of Cu with the adjacent low  $\kappa$  material. Diffusion, regardless of the pathway, basically is "thermally activated", and follows the Arrhenius relationship. It was found experimentally that diffusion rate is proportional to the melting temperature T of the host material, given by equation 1.2,

$$Rate = A \exp(-\frac{E_a}{kT})$$

(1.2)

where E<sub>a</sub> is the activation which is the amount of energy needed for the desired event to occur, T is the absolute temperature, k is Boltzmann's constant and A is a constant that depends on a variety of factors, including lattice structure and type of material. The relationship provides a reasonable guideline in the selection of appropriate materials for diffusion barrier. It indicates that materials with high melting temperature could act as better barriers. Accordingly, refractory metallic systems with characteristically high melting points and chemical inertness serve as viable candidates for diffusion barrier applications in Cu based metallization schemes. Currently, the most popular diffusion barriers are Ta as well as its compounds. From the material properties point of view, Ta is one of the most desirable diffusion barriers. It has a high melting point, 3020 °C, providing a high activation energy for both lattice and grain boundary diffusion. Also it does not form intermetallic compounds with Cu, thus providing a relatively stable interface between Cu and Ta. The reaction between Si and Ta is also known to require rather high temperatures 650 °C, which, in effect, provides a reasonably stable Si/Ta interface. [36].

A diffusion barrier with integrity, conformality and stability is critical to effectively block Cu diffusion into the low  $\kappa$  materials and subsequently into the Si devices. The quality of diffusion barrier is becoming a challenging issue. The aggressive miniaturization of IC devices makes the thickness of the diffusion barrier to be only a few nanometers, yet it has to be of near perfect quality in order to effectively

prevent Cu out-diffusion from Cu lines. Meanwhile, the introduction of pores into low  $\kappa$  materials makes it even difficult to deposit a continuous defect-free diffusion barrier layer. It was reported that the barrier deposited onto porous low  $\kappa$  films with thickness below 20nm are typically found to be permeable due to the presence of pores or pinholes [37-40].

The improvement of diffusion barrier quality is being extensively investigated [41-44], however, the struggle to achieve the needed high-quality barrier is slowed by cumbersome conventional characterization methods in this aggressively miniaturized situation.

The quality of diffusion barrier has been investigated primarily using electrical test methods, such as biased thermal stressing (BTS) and EM testing, and followed by a direct observation of the barrier microstructure using microscopy, especially transition electronic microscopy (TEM). However, these methods are time-consuming (generally taking a couple of months) and ineffective for detecting such small and localized defects. Typically, after a thermal test, a couple of samples are selected from test groups, and prepared (cross-section or top-down plane) for TEM characterization. Unless the defect density is very high, it is very difficult to find the tiny and localized defects on a massive area of diffusion barrier using TEM for the following reasons. First of all, TEM is only able to characterize one local area where it is possible that no any defects exist at all. Secondly, the defects are becoming very tiny as the extreme reduction of barrier thickness, making the characterization difficult. Unfortunately, one tiny defect may degrade the device performance and cause the device failure eventually as the thickness

of diffusion barrier keeps scaling down to a few nano-meters. Lately, time dependent dielectric breakdown (TDDB) test method, a conventional reliability test of the low  $\kappa$  structure, is being investigated to characterize the quality of diffusion barrier by monitoring the current resulted from Cu contamination into the low  $\kappa$  materials [45]. However, the method developed for interconnects integrated with DLK are also time-consuming and ineffetive. It is not designed to exclusively examine the barrier quality, increasing the potential for false diagnosis. For example, it is possible that defects are produced during a TDDB test since it is an accelerated test, conducted at high temperature and voltage. It is, therefore, imperative to develop a method for evaluating the barrier integrity exclusively.

#### 1.2.3.2 Low κ Materials

Generally, there are two approaches to reduce  $\kappa$  of a material: incorporate atoms and bonds that have a lower polarizability and lower the density of atoms and bonds in the materials. The polarization components usually considered are the electronic and nuclear responses of the material. The nuclear dielectric response results from polarization of both permanent and transition dipoles in the material, and the response is often dominated by polar substituents, such as hydroxyl and carbonyl groups. When designing low  $\kappa$  materials, it is desirable to use material with C-C and C-F bonds, which have the lowest electronic polarizability, and avoid using highly polar substituents that attract and bind water, which increase  $\kappa$  significantly due to the large permanent dipole moment of water. The dielectric constant of any material can also be reduced by decreasing the density. As a result, low  $\kappa$  can be obtained by using lighter atoms, such as C and H, and incorporating more free space, such as pores, into the structure. Organic polymers are often used in low  $\kappa$  materials because of their low material density and low individual bond polarizabilities [46].

A particularly difficult challenge for low  $\kappa$  material development is to obtain the combination of low dielectric constant and good thermal and mechanical stability. Generally, the types of chemical structures that impart structural stability are those having strong individual bond that often have strong polarizability and high density of such bonds. It is those two factors (the strong bond and the high density) that offer a high dielectric constant.

To further reduce  $\kappa$  value for advance interconnects, low  $\kappa$  materials with pore structure (PLK) are being integrated with Cu interconnects. However, the high degree of porosity in the PLK materials creates a number of integration reliability challenges. Generally, porous films are considered to further deteriorate reliability compared to their dense counterpart. Although there has been significant progress in the last years regarding the integration of PLK materials, more work is still needed [46-47].

The introduction of pores achieves the goal of lowering  $\kappa$  at the cost of degradation in mechanical strength, thermal conductivity, resistance to chemical attack [47-50].

First of all the mechanical properties degrade significantly with the introduction of pores in solid materials, and the weak mechanical properties often lead to poor adhesion of the PLK materials to other layers, poor CMP compatibility and difficulty in package assembly. In addition, the thermal conductivity drops rapidly as the pores are

Figure 1.7 Correlation of thermal conductivity and dielectric constant (dark square) represents the experimental data for the porous MSQ. Curve (a) is for the porous MSQ and (b) for the porous silica. Oval (c) includes various dense ISG materials, and (d) includes various dense polymeric low  $\kappa$  [54].

incorporated in the matrix material, as seen in figure 1.6 [51]. The thermal conductivity drops to ~0.05W/m/K for porous MSQ/silica from ~0.3 W/m/K for dense polymeric materials. The poor thermal conductivity of porous low  $\kappa$  severely reduces the thermal conduction in interconnect structures, and therefore aggravates joule heating and increases EM reliability concern. As seen in figure 1.7, interconnect temperatures increase from ~5K to 30~80K as PLK replaces SiO<sub>2</sub> due to its poor thermal conductivity [52]. Furthermore, pores in low  $\kappa$  materials can contain contaminants from processing gasses and liquids or ambient, any of which may have a detrimental effect on the dielectric electrical properties or instigate unwanted chemical changes [53-54]. It was reported that the pores can be highly interconnected if porosity is greater than

Figure 1.8 Interconnect line temperature increase ( $T_{line}$ - $T_{substrate}$ ) as a function of the dielectric thermal conductivity [52]

$\sim$ 25% [55-57], which may open new failure mechanism in Cu/PLK materials that not found in Cu/DLK structure [58-59].

The reliability of Cu interconnects becomes even more complicated and demanding with the introduction of pores into low  $\kappa$  structure.

The weak mechanical strength of PLK materials aggravates the EM performance [32, 36].

$$J = \frac{DC}{kT} \left( z^* e \rho j - \Omega \frac{d\sigma}{dx} \right)$$

(1.3)

As seen in equation 1.3, EM performance is the result of two competing factors [60]. The first term,  $z^*e\rho j$ , referred to as electron wind, is the driving force for EM, where  $z^*$  is the apparent effective charge number, e is the absolute value of the electronic charge,

$\rho$  is the metallic resistivity, and j is the current density. The second term,  $\Omega d\sigma/dx$ , referred to as the metal accumulation back-stress gradient, is the force to resisting EM, where  $\Omega$  is the effective atomic volume. The equation highlights the reliability challenges with the scaling of Cu interconnect integrated with low  $\kappa$  materials. On the one hand, the demand for higher current density significantly increases the driving force for EM, and therefore accelerated the EM failure. On the other hand, the PLK materials provide less confinement, or less back-flow stress due to their lower elastic modulus, and further shorten EM failure times. In addition, the pore structure in the PLK materials can aggravate joule heating problem due to poor thermal conductivity and further degrades EM performance [61-63].

The introduction of pores in low  $\kappa$  materials creates a serious TDDB reliability concern. In the past with SiO<sub>2</sub>, TDDB has not been a reliability concern. SiO<sub>2</sub> has a high breakdown strength, ~~10MV/cm, and the operating fields in a typical damascene structure are below 0.5MV/cm. For this reason, TDDB is unlikely to be a reliability concern even if the thickness is very thin. Also the robustness of SiO<sub>2</sub> is partially due to good oxide confinement to the metals and good adhesion between the cap and copper, making it difficult for copper to diffuse out from the line. On the other hand, low  $\kappa$ materials including DLK and PLK (PLK is the worst), generally have less breakdown strength, and less confinement of Cu/barrier, which can result in higher electronic leakage from Cu diffusion and premature TDDB [64, 65].

Extensive studies are being conducted to characterize pore structure, such as positronium annihilation lifetime spectroscopy (PALS), a combination of specular x-ray

reflectivity (SXR), small angle x-ray and neutron (SAXN) scattering and measurement of solvent diffusivity [66-70]. Low energy PALS is able to determine the average pore size and pore structure. In porous films, the formation of positronium (Ps) occurs preferentially in the voids of the film, and the Ps annihilation life time is shortened from the vacuum lifetime ( $\sim$ 142ns) owing to collisions with the pore walls. This effect provides a means of determining the average pore size from the Ps lifetime in the porous film. PALS is also able to detect the onset of an interconnected pore network (pore interconnectivity) because the Ps has a single lifetime if all the pores are connected. Moreover, if the pores are isolated, the Ps has many lifetime components, each corresponding to a different pore size. Therefore, in a closed pore structure, PALS has the potential to provide pore size distribution. SXR is able to measure the porosity by comparing the average film density to an assumed density of the non-porous material. SANS is not a direct technique for pores structure characterization. It measures the density of the connecting material, and therefore mesoporosity can be calculated from the average film density (measured by SXR) relative to the pore wall density (measured by SANS). Measurement of solvent diffusivity is a simple method developed recently for predicting the pore interconnectivity by measuring effective diffusivity of solvent as a function of porosity.

Regardless of the high cost of the equipment and requirement of complex model to extract desired data (except measurement of solvent diffusivity), each technique has its own limitation. Even PALS, the most powerful technique for pore structure characterization, can not characterize the pore size distribution if the low  $\kappa$  material has an open pore structure. However, as modern devices are continuously shrinking down, ultra low  $\kappa$  materials with higher porosity are required to further lower RC delay. When the porosity is greater than 25~30%, the pore interconnection occurs [56,57].

Most important, all those techniques are only effective on blanket films (unpatterned wafer). However, the pore morphology of PLK materials in as-processed interconnect is found not to be thermally stable but alter its characteristics during thermal annealing [65, 71], and the current methods mentioned above are not able to trace its thermal stability. Therefore, it is essential to have a method to characterize the pore morphology with multiple functions for patterned wafer instead of blanket film in order to understand the impact of the pore structure on the product reliability and thereby optimize processing conditions and the resulting properties.

#### 1.3 Objectives and Significance of This Thesis

This study has three major objectives: (1) to investigate the thermal failure mechanism for Cu/PLK interconnect structures, which raises the issue of effectiveness of conventional characterization metrologies, (2) to develop a new metrology for barrier quality detection in fine scale barrier thickness, (3) to develop a new metrology for characterization of pore structure in low  $\kappa$  materials and using the method to investigate the stability of the pore structure in PLK.

The metrology developed in this study is able to characterize both the defects in diffusion barrier and the pore structure in low  $\kappa$  materials of Cu/barrier/PLK integration. This specific technique is simple, fast and effective with low cost. For barrier defects detection, the conventional methods require TEM observation after lengthy electrical

tests. This is time-consuming and of questionable effectiveness due to the localized and tiny defects within massive area of barrier layers, as discussed in 1.2.3.1. On the other hand, the developed method is a room temperature test, and does not require long time baking and intensive microscopy examination to find the tiny defects in massive area of barrier. It is very sensitive due to the intrinsic characterization for chemical reaction. Regarding the characterization of pore structure, unlike the other available methods that are only effective on the blanket film, the developed method is able to characterize and trace the stability of the pore structure in low  $\kappa$  materials on as-processed wafer.

#### <u>1.4 Overview of Chapters</u>

Chapter 2 is devoted to the study on thermal stability of diffusion barrier in Cu/PLK interconnects. The investigation is conducted on Cu interconnects with various barrier arrangements at elevated temperature with various ambient, and then the failure mechanisms and the leading factors are evaluated by a combination of TEM, SEM (Scanning Electron Microscopy), and electrical resistance signal in Cu/PLK structure.

Chapter 3 describes the developed characterization method (voltammetry-based) for both barrier defect detection and pore structure evaluation in low  $\kappa$  materials, including the fundamental concepts of voltammetry and the principle of developed metrology.

Chapter 4 investigates the quality of diffusion barrier in Cu/low  $\kappa$  interconnects using the developed "voltammetry" technique after the fundamental study of the method, in which idealized samples are prepared to simulate various condition of diffusion barriers. Chapter 5 develops the characterization technique and the analytic model for evaluation of the pore structure in low  $\kappa$  materials. Its thermal stability is investigated using the developed method, too.

Finally, conclusions and the future research are presented in Chapter 6.

# CHAPTER 2

# STUDY ON THERMAL STABILITY OF Cu/PLK STRUCTURE

In this chapter, a series of thermal stability investigations are conducted on Cu/PLK interconnects with various types of barrier arrangements at elevated temperature with various ambient to understand thermal failure mechanism as well as the impacts of barrier and ambient on thermal failure process.

Cu interconnect stability is determined by resistance of Cu lines with intermittent application of low current (0.1MA/cm<sup>2</sup>, far lower than a typical current density for EM test). It is only applied on samples when taking data. The purpose for this is to minimize the influence of current on the failure process of interconnects.

The thermal and kinetic failure mechanisms and their factors are assessed by a combination of TEM, SEM, and electrical resistance signal. It is found that Cu/PLK interconnect can fail by Cu out-diffusion into the pore structure simply by thermal baking, and the failure seems to be driven by the mechanism that is not seen in Cu/DLK structure.

## 2.1 Samples and Experimental

## 2.1.1 Samples

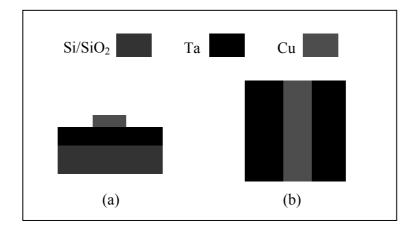

Thermal stability tests are performed on 0.25µm wide, single-level and twolevel Cu interconnect structures processed by SEMATECH. The intra- and inter-leve dielectric is a porous MSQ-based material with  $\kappa$  value of ~2.2 and estimated porosity of ~45%. An optical image of the test pattern and the cross-section schematic of one and two level Cu/barrier/PLK structure are present in figure 2.1

Figure 2.1 (a) An optical image of test pattern; a cross section schematic of (b) one level (c) two level Cu/barrier/PLK structure

The single level samples are 400μm long lines on M2, with no vias and M1 in the resistance measurement circuit. The two-level samples are of multiple M2 segments, 0.25μm wide, 150μm long connected by vias through M1. Between each layer of metal metallization, a 100nm SiN layer (a capping layer) is deposited by plasma enhanced chemical vapor deposited (PECVD). Each layer Cu/PLK interconnect structure consists of 400nm of low-κ material between 250nm Cu with various barrier arrangements, as seen in figure 2.1 (c). Two types of barier arrangement are used in this study. In the first type, a PECVD SiCN layer with a thickness range of 30-50nm SiCN spacer is deposited on lowk material first and then a Ta layer with a thickness range of 0.5-25 nm is sequentially deposited. In the second type, a 25nm Ta layer is deposited on low  $\kappa$  material directly without any SiCN spacer in between. After completion of M2 metallization, a dielectric passivation stack of 100nm SiN/200nm SiO<sub>2</sub> is deposited, followed by TaN and Al protection layers over the bond pad openings. Samples are cleaved to get the test pattern, and then chip with test pattern is mounted in a chip carrier and gold wires are bonded to connect the test pattern circuit to a chip carrier [72]. *2.1.2 Experimental*

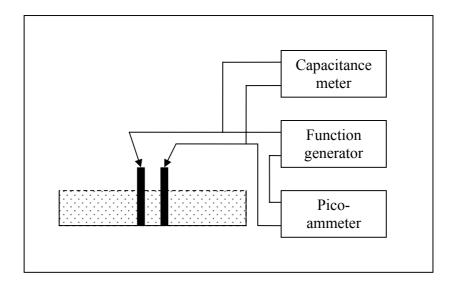

The thermal stability is investigated on the EM lifetime testing set-up built up at UT-Arlington. The detailed description of the equipment, including the particular circuit design and the working principle, can be obtained in the reference [73], but a brief description is given here: The set-up consists of a convection oven, high temperature circuit boards, a special circuit design to allow multiple samples to be tested with one constant current source, and a computer controlled data acquisition system, as shown in figure 2.2. The set-up can conduct simultaneously up to 100 samples at elevated temperature and the resistance is recorded by applying a constant current. The increase in resistance up to 100% is used as a failure criterion instead of 10% increase in industry. For the thermal stability test in a controlled ambient environment, a sealed stainless steel box connected to  $N_2$  or Ar gas is put inside the oven, and serving as an environmental chamber.

In the thermal stability investigation, Cu/PLK interconnects with various barrier arrangements are baked at elevated temperature  $150-325^{\circ}$ C in air/Ar/N<sub>2</sub> ambient, and the thermal stability is monitored by the resistance of Cu lines with occasional

Figure 2.2 A schematic representative of the experimental apparatus

application of low-level current. The microstructure investigation has been performed with a JEOL 845 SEM and a 1200EXX JEOL TEM to reveal the failure mechanism of Cu/PLK interconnects. TEM samples, prepared as the normal procedure, are diced from wafer and attached to 3mm Cu grid; thinned from Si substrate; followed by dimpling and argon ion milling to the interested area thin enough for electron transimision.

## 2.2 Results

# 2.2.1 Thermal Instability of Cu Interconnect

# 2.2.1.1 Tested Under Air Ambient

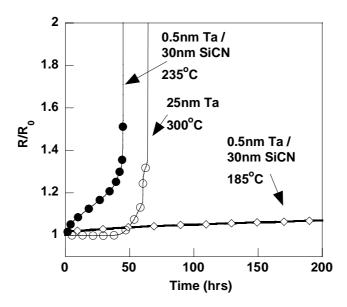

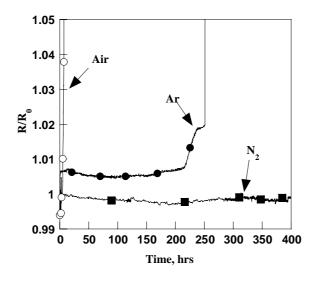

Figure 2.3 and 2.4 present the representative electrical resistance of Cu/PLK with various barrier arrangements baked at different temperatures. The results show that

Cu interconnects fail by two-step process: (1) incubation period where the resistance is pretty stable (2) steady-state increase period of resistance where the resistance gradually increases with time. The failure time of Cu/PLK interconnect is found to be dependent on the barrier arrangement and the test temperature.

Figure 2.3 A plot showing resistance (ratio) of a 0.25um single level Cu interconnect with different barrier arrangement baked at 275°C with low level intermittent current, 0.1 mA/cm<sup>2</sup> in air atmosphere.

As seen in figure 2.3, which presents the typical electrical resistance data resulted from the single level Cu interconnect with two barrier arrangements, 25nm Ta and 50nm SICN/0.5nm Ta, baked at 275°C in air, the failure process is significantly affected by the barrier arrangement. The failure time can be retarded from a couple of hours for Cu integrated with 50nm SiCN/0.5nm Ta to ~140 hours for Cu integrated with 25 nm Ta. Also a clear incubation period (~100 hours) in the sample with thick Ta (25nm) can be seen while almost no incubation period exists in the sample with thin Ta

barrier (50nm SiCN/0.5nm Ta) even through a thick SiCN layer (50nm) is present. The results suggest that the failure time, as well as the incubation period, is affected significantly by the thickness of the Ta layer and a SiCN layer is not as a good barrier for Cu interconnects as a Ta is.

Figure 2.4 A plot showing resistance (ratio) of a single level with different barrier arrangement and temperature with low level intermittent current, 0.1mA/cm<sup>2</sup> in air atmosphere.