# EFFECT OF STRUCTURAL DESIGN PARAMETERS ON WAFER LEVEL CSP BALL SHEAR STRENGTH AND THEIR INFLUENCE ON ACCELERATED THERMAL CYCLING RELIABILITY

Ву

### NIKHIL R LAKHKAR

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

Of the Requirements

For the Degree of

**DOCTOR OF PHILOSOPHY**

THE UNIVERSITY OF TEXAS AT ARLINGTON

May 2010

Copyright © by Nikhil Lakhkar 2010

All Rights Reserved

#### **ACKNOWLEDGEMENTS**

I would like to thank Prof. Dereje Agonafer for the guidance he has provided me through the years. It would not have been possible to accomplish the milestones I have accomplished without his mentoring and support. I have been working with Prof. Agonafer from FALL of 2002. He has encouraged me to publish papers and attend conferences which gave me a great confidence and courage in undertaking many different tasks related to different fields of electronic cooling including Refrigeration, Air cooling, cooling of high heat flux devices etc. Professor Agonafer always had unshakable confidence in me and he will always be my mentor for rest of my life.

I especially thank Dr. Puligandla Viswanadham who has been with me in all the ups and downs during the course of my Ph.D. This dissertation would not have been possible without his help. Dr. Puligandla has always given me honest opinion and has stood with me in the worst of my dissertation days. I thank my senior colleague Dr. Mohammad Hossain who was the first to light the pathway for me to perceive my doctorate studies in the field of Mechanical Reliability despite coming from a Thermal Management background. I extend my thanks to my colleagues from EMNSPC who have helped me directly or indirectly in completion of this degree.

I extend my thanks to thank Prof. A. Haji-Sheikh, Prof. S. Nomura and Prof. Z. Celik-Butler for reviewing my proposal and be on the committee of my dissertation. They really helped me review the proposal and gave me valuable input for creating this dissertation. I extend my thanks to Ms. Sally Thompson who has always been a force to reckon with taking care of all the paper work to the perfection and has always been a great friend and a pleasure to work with.

It is a known fact that the cyclical nature and cyclic emotions of a Doctoral student's life is often more harsh on the supporting partner. Hence, I don't have enough words to express my thanks to my wife Pallavi for her support and giving me many reasons to believe that I can

complete the journey that I have started. I thank my parents Dr. R.B Lakhkar and Mrs. Kunda R. Lakhkar for providing me the encouragement and the courage that I can go ahead and perceive a doctorate degree. Last but not the least I would like to thank my maternal grandparents Mr. Sriram Varudkar and Mrs. Leela Varudkar and my paternal grandmother Mrs. Saraswatibai Lakhkar who provided the real encouragement to complete everything I started.

March 30, 2010

#### **ABSTRACT**

# EFFECT OF STRUCTURAL DESIGN PARAMETERS ON WAFER LEVEL CSP BALL SHEAR STRENGTH AND THEIR INFLUENCE ON ACCELERATED THERMAL CYCLING **RELIABILITY**

#### Nikhil Lakhkar, PhD

The University of Texas at Arlington, 2010

Supervising Professor: Dereje Agonafer

Wafer level chip scale package (WLCSP) is one of the most popular packages due to its size and cost advantages. It is expected that the usage of WLCSP in microelectronics and MEMS industry combined is going to cross 16000 Million Units by 2013. One of the main advantages of implementing WLCSP is its time to market because most of the package is done at the wafer level. Once the wafer processing is completed the package is just diced and mounted on board and the board is ready to go. However, just like any other package WLCSP too is not ideal and do have weaknesses from reliability point of view. The advantage of having a WLCSP is that the reliability program can be divided into two parts namely Wafer level reliability and Board level reliability. Ball shear test, Ball pull test etc. are some of the popular wafer level reliability tests that are very commonly employed in wafer fabs. Popular Board level accelerated tests are Drop tests and accelerated thermal cycling. Typically, the time taken by the board level reliability tests is much more as compared to wafer level reliability tests.

Various researchers have attempted to correlate board level and wafer level reliabilities using experimental and statistical correlations. Such correlations exist for High speed shear and high

v

speed ball pull and board level drop testing. However, such correlations don't exist for accelerated thermal cycling and wafer level reliability tests. In this dissertation, three different solder compositions, three solder sizes are mounted on two structures that are very commonly used in wafer level chip scale packages. The structures are fabricated on wafer and sheared off using a commercially available ball shear tester and two important results were noted (a) ball shear strength and (b) % ductile failure mode incidence. The structures were sheared off at two different heights namely 25µm and 125µm heights. The results in terms of gram force from both heights were combined in a statistical term called as Signal to Noise ratio which is Negative logarithm to the base 10. Results obtained using experimental ball shear were validated computationally using commercially available finite element codes.

Similar WLCSP packages were assembled on standard accelerated thermal cycling boards and were cycled between temperature extremes of -40°C and 125°C at the frequency of 2 cycles/hr. Weibull plots were obtained for all board assemblies for different scenarios considered in the study. Results from accelerated thermal cycling and ball shear testing were matched using two ways (a) the stress and inelastic strain from both the tests were matched on a log-log plot and (b) % ductile failure mode from ball shear testing was matched with Number of cycles and Weibull parameter from accelerated thermal cycling using CORREL function and correlation coefficients were determined. The correlation coefficients were determined from taking into consideration the variation in structure and corresponding changes in the Number of cycles in accelerated thermal cycling. Effect of individual structural parameters on the fatigue life was analyzed and corresponding recommendations were made.

It was concluded that matching stress- strain from accelerated thermal cycling and ball shear strength didn't result into any correlations. % ductile failure mode is a better parameter in establishing correlations between the two tests.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                              | iii   |

|---------------------------------------------------------------|-------|

| ABSTRACT                                                      | v     |

| LIST OF ILLUSTRATIONS                                         | X     |

| LIST OF TABLES                                                | xviii |

| Chapter                                                       | Page  |

| 1. INTRODUCTION                                               | 1     |

| 1.1 Miniatuirization of Electronic Components                 | 1     |

| 1.2 Packaging Efficiency                                      | 2     |

| 1.2.1 Wafer level chip scale package                          | 3     |

| 1.3 Fabrication of structures on wafer level                  | 7     |

| 1.3.1 Wafer level fabrication process                         | 7     |

| 1.4 Reliability considerations in portable electronic devices | 10    |

| 1.4.1 Interconnect Reliability at Wafer level                 | 11    |

| 1.4.2 Interconnect Reliability at board level                 | 14    |

| 1.5 Dissertation Outline                                      | 16    |

| 1.6 Problem Definition                                        | 17    |

| 2. LITERATURE REVIEW OF LEAD FREE SOLDERS                     | 21    |

| 2.1 Transition from Eutectic Tin lead to Lead free solders    | 21    |

| 2.1.1 Selection of a lead free solder                         | 22    |

| 2.2 Constitutive properties of solder                         | 28    |

| 2.2.1 Solder Constitutive behavior                            | 28    |

| 2.3 Partitioned Constitutive model                            | 30    |

| 2.3.1 Elastic Strain                                          | 30    |

| 2.3.2 Plastic Strain                                           | 33 |

|----------------------------------------------------------------|----|

| 2.4 Unified Constitutive model/ANAND's model                   | 35 |

| 2.5 Fatgue Life Prediction models                              | 39 |

| 2.5.1 Stress based models                                      | 39 |

| 2.5.2 Strain based models                                      | 40 |

| 2.5.2.1 Coffin Manson model                                    | 40 |

| 2.5.2.2 Strain rate partitioning model                         | 41 |

| 2.5.2.3 Energy Criterion                                       | 43 |

| 2.5.2.4 Energy partitioning approach                           | 44 |

| 2.5.2.5 Clech's (SRS) model                                    | 45 |

| 2.6 What's the right model to use?                             | 47 |

| 2.6.1 Ball shear testing                                       | 48 |

| 2.6.2 Accelerated Thermal cycling                              | 48 |

| 2.7 Conclusion                                                 | 49 |

| 3. BALL SHEAR TEST – LITERATURE REVIEW                         | 50 |

| 3.1 What is Ball shear test                                    | 50 |

| 3.2 How is Ball shear test performed?                          | 51 |

| 3.2.1 Factors affecting Ball shear test                        | 52 |

| 3.2.1.1 Solder ball composition and effect of Multiple reflows | 53 |

| 3.2.1.2 Solder Volume and shear speed                          | 54 |

| 3.2.1.3 Position of shear tool                                 | 55 |

| 3.3 Conclusion                                                 | 56 |

| 4. BALL SHEAR TEST – COMPUTATIONAL AND EXPERIMENTAL            | 58 |

| 4.1 Experimental Ball shear test                               | 58 |

| 4.2 Design of Experiments                                      | 59 |

| 4.2.1 Results from Ball shear DOE                              | 60 |

| 4.3 Failure Analysis                                                       | 66  |

|----------------------------------------------------------------------------|-----|

| 4.4 Conclusions from Experimental results                                  | 69  |

| 4.5 Computational validation of Ball shear test                            | 69  |

| 4.5.1 Model Creation                                                       | 69  |

| 4.5.2 Preprocessing of Ball shear model                                    | 70  |

| 4.6 Effect of shear speed on shear force and failure mode                  | 72  |

| 4.7 Effect of shear speed on shear height and failure mode                 | 74  |

| 4.8 Effect of Temperature on Ball shear stress                             | 78  |

| 4.9 Conclusion                                                             | 83  |

| 5. ACCELERATED THERMAL CYCLING — COMPUTATIONAL AND EXPERIMENTAL            | 84  |

| 5.1 Introduction to Accelerated thermal cycling                            | 84  |

| 5.2 Experimental setup – Accelerated thermal cycling                       | 86  |

| 5.3 Results and Discussion – Accelerated thermal cycling                   | 87  |

| 5.4 Failure Analysis                                                       | 92  |

| 5.4.1 Classification of failure modes for accelerated thermal cycling      | 96  |

| 5.5 Conclusion                                                             | 96  |

| 5.6 Computational validation of Accelerated thermal cycling                | 97  |

| 5.7 Results and Discussion - Accelerated thermal cycling                   | 102 |

| 5.8 Effect of mean stress on fatigue life of solders                       | 110 |

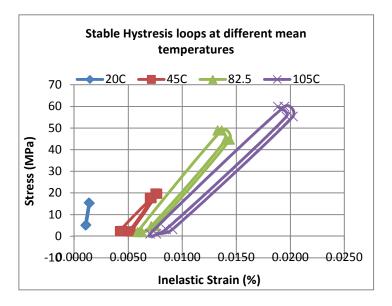

| 5.9 Hysteresis loops obtained at different  Mean temperatures considered   | 114 |

| 5.10 Conclusion from Accelerated Thermal Cycling tests                     | 117 |

| 6. CORRELATION BETWEEN WAFER LEVEL RELIABILITY AND BOARD LEVEL RELIABILITY | 119 |

| 6.1 Literature review                                                      | 119 |

| and different metrics for comparison                                                               | 121 |

|----------------------------------------------------------------------------------------------------|-----|

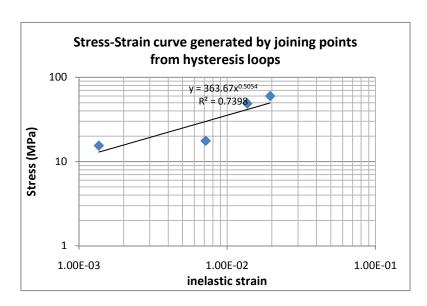

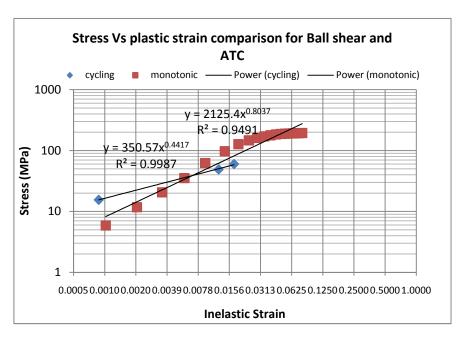

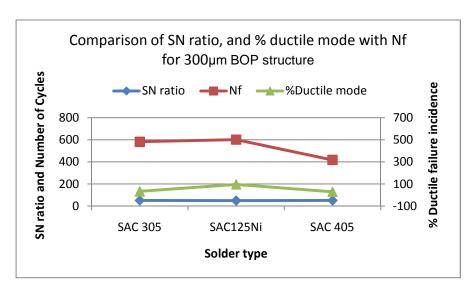

| 6.3 Statistical correlations between Ball shear Test and Accelerated thermal cycling               | 122 |

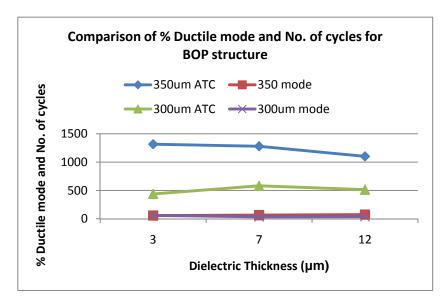

| 6.3.1 Comparative charts between Ball shear test And accelerated thermal cycling                   | 122 |

| 6.3.2 CORREL function                                                                              | 127 |

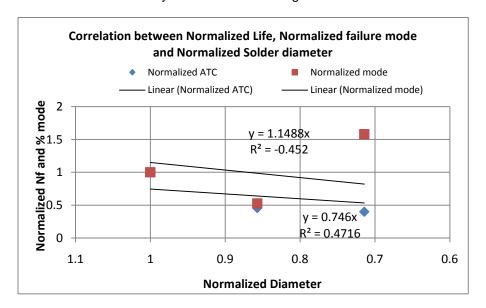

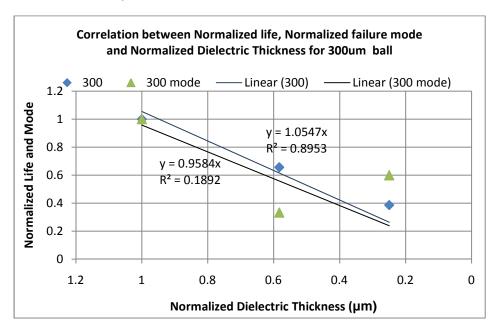

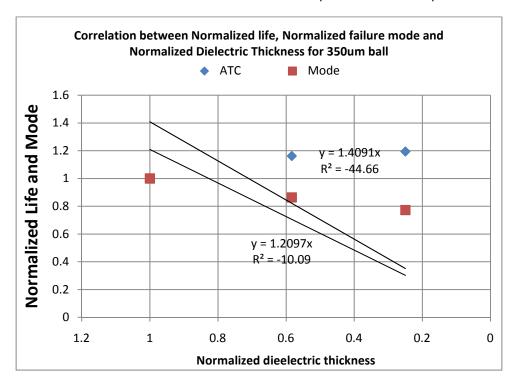

| 6.3.3 Correlations between fatigue life and Geometrical design parameters considered In this study | 129 |

| 6.4 Conclusion                                                                                     | 133 |

| 7. CONCLUSION                                                                                      | 135 |

| APPENDIX                                                                                           |     |

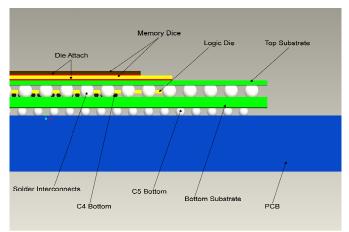

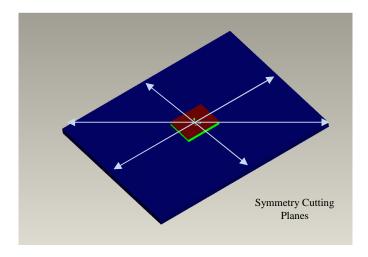

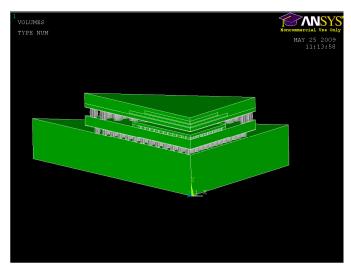

| MECHANICAL DESIGN OPTIMIZATION OF PACKAGE ON PACKAGE                                               | 139 |

| REFERENCES                                                                                         | 160 |

| BIOGRAPHICAL INFORMATION                                                                           | 170 |

# LIST OF ILLUSTRATIONS

| Figur | re                                                                                       | Page |

|-------|------------------------------------------------------------------------------------------|------|

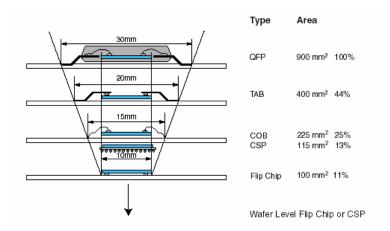

| 1.1   | Reduction of the footprint of Electronic Package                                         | 1    |

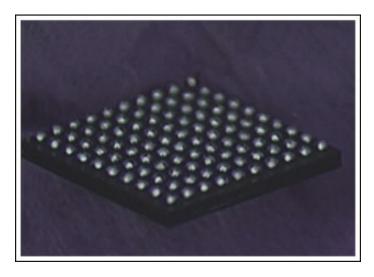

| 1.2   | Typical Wafer Level Chip Scale Package                                                   | 4    |

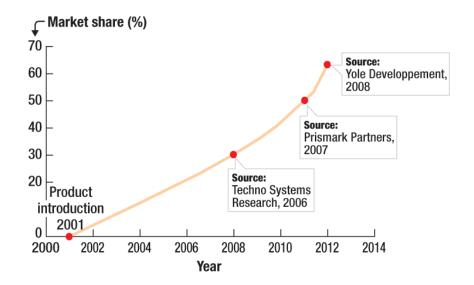

| 1.3   | Market share of WLCSPs in Camera Modules                                                 | 4    |

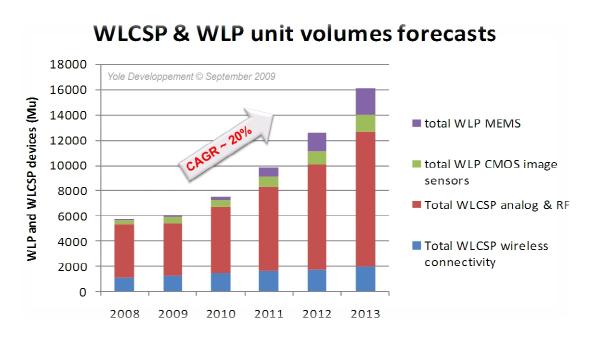

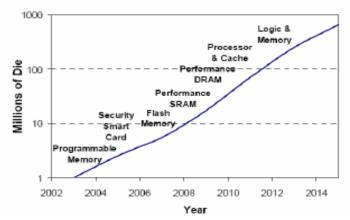

| 1.4   | WLCSP and WLP unit volume forecast                                                       | 5    |

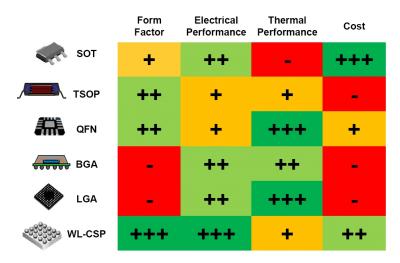

| 1.5   | Comparison of WLCSP with other small packages                                            | 6    |

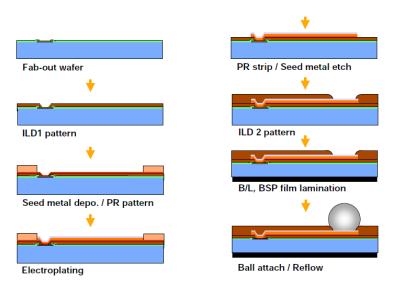

| 1.6   | Process of fabrication of structures on a wafer                                          | 9    |

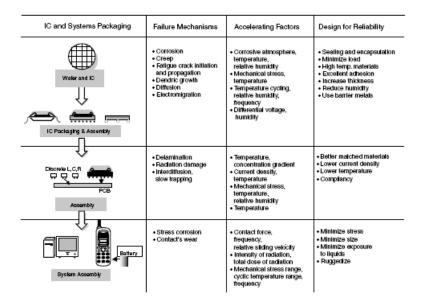

| 1.7   | Failure mechanisms and Acceleration factors at Different levels of Packaging             | 11   |

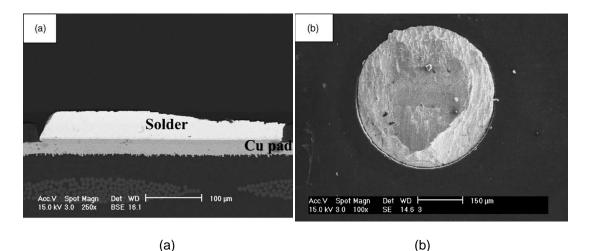

| 1.8   | Typical failures observed in a Ball shear test (a) Side view and (b) Top View            | 13   |

| 1.9   | Typical Thermal Cycling test setup (a) Chamber (b) Arrangements of boards in the chamber | 14   |

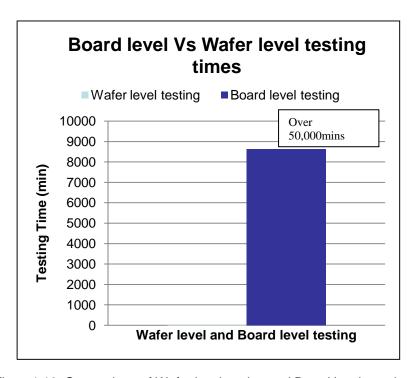

| 1.10  | Comparison of Wafer level testing and Board level testing Times                          | 16   |

| 1.11  | Process Flow followed in developing this dissertation                                    | 18   |

| 2.1   | Four point bending reliability issues of Solders                                         | 25   |

| 2.2   | Comparison of SEM's for (a) SAC solder and (b) SAC solder with gold addition             | 26   |

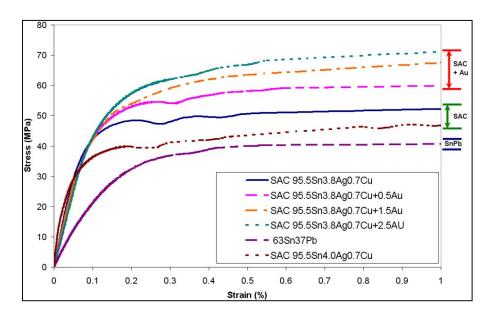

| 2.3   | Tensile Stress-Strain curves of SAC alloy with Gold addition                             | 27   |

| 2.4   | Rheological changes that happen because Of addition of Nickel to lead free alloy         | 27   |

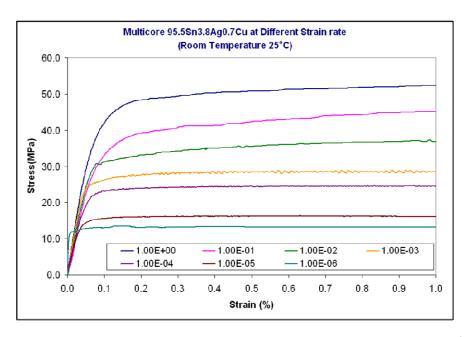

| 2.5   | Stress – strain behavior of SAC 3807 alloy At different strain rates at 25°C             | 31   |

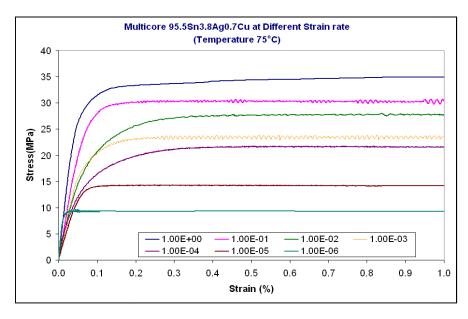

| 2.6  | Stress- Strain behavior of SAC 3807 alloy At different strain rates at 75°C                                                                                                               | 31 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

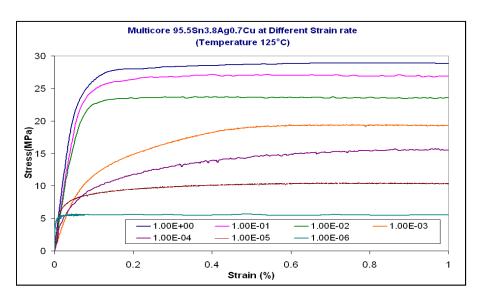

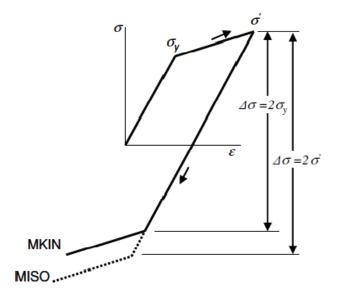

| 2.7  | Stress- Strain behavior of SAC 3807 alloy At different strain rates at 125°C                                                                                                              | 32 |

| 2.8  | Stress- Strain behavior of SAC 3807 alloy At different strain rates at 150°C                                                                                                              | 32 |

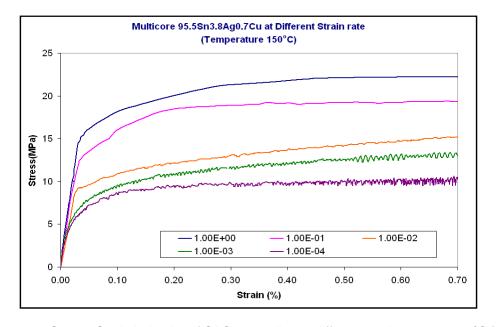

| 2.9  | Types of modeling plasticity (a) Perfectly elastic (b) elastic linear hardening and (c) non- linear hardening                                                                             | 33 |

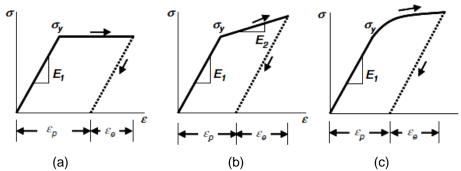

| 2.10 | Bauschinger effect captured by Multi-linear kinematic hardening model                                                                                                                     | 35 |

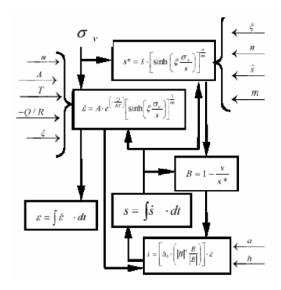

| 2.11 | Interrelationship between the set of Equations in ANAND's model                                                                                                                           | 38 |

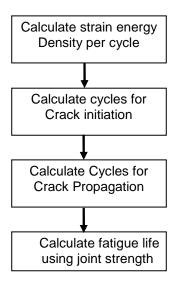

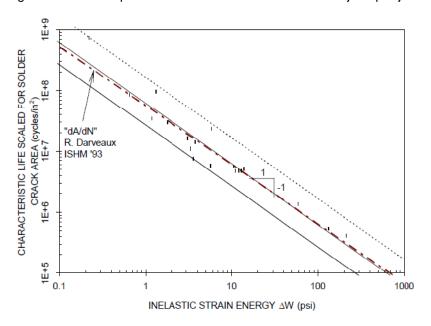

| 2.12 | Flow chart for implementing Darveaux's approach                                                                                                                                           | 44 |

| 2.13 | Solder Reliability Solutions correlation of accelerated data                                                                                                                              | 46 |

| 3.1  | Schematic of a Ball shear test                                                                                                                                                            | 52 |

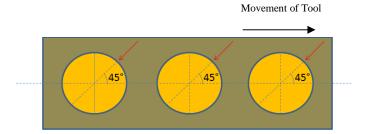

| 4.1  | Schematic of a wafer with solder joints.  Red Arrow shows motion of ball shear tool                                                                                                       | 58 |

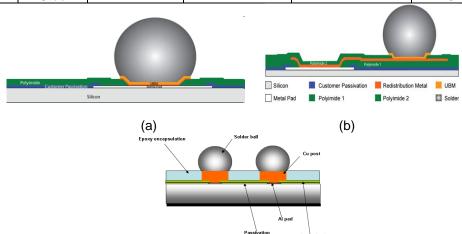

| 4.2  | Structures under Consideration (a) Ball on Pad (b) Ball on RDL (c) Ball on Stub                                                                                                           | 59 |

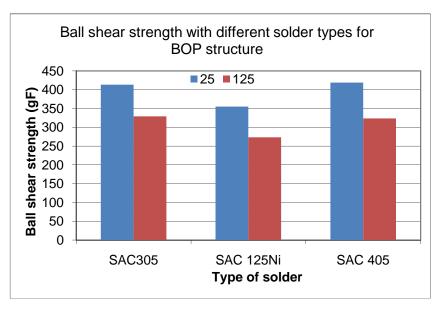

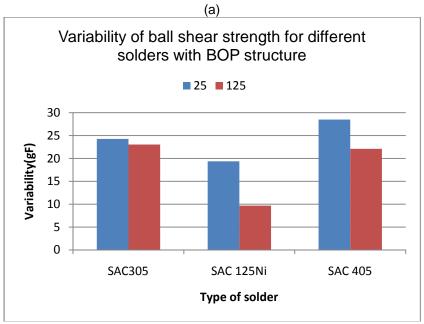

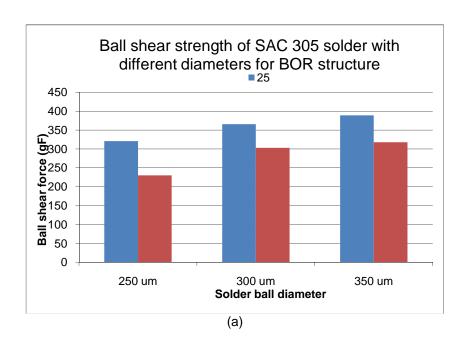

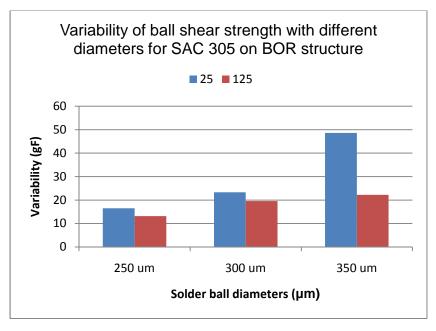

| 4.3  | Variation of Ball shear strength with different solder materials on Ball on Pad Structure (a) Ball Shear Strength (b) Variability                                                         | 62 |

| 4.4  | Variation of Ball shear Strength with different ball types with 300µm BOR structure (a) Ball Shear Strength (b) Variability                                                               | 63 |

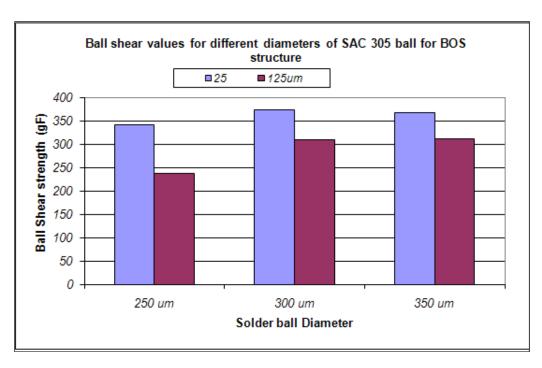

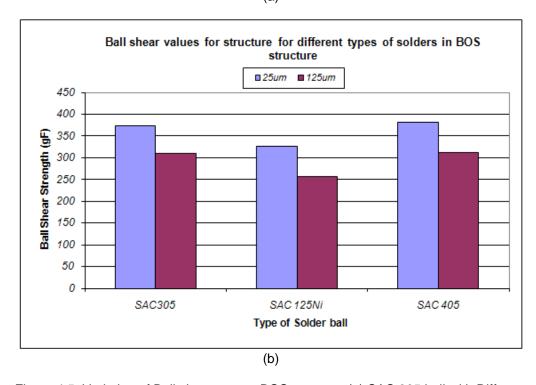

| 4.5  | Variation of Ball shear strength on BOS structure (a) SAC 305 ball With different diameters (b) 300µm solder ball with different diameters                                                | 64 |

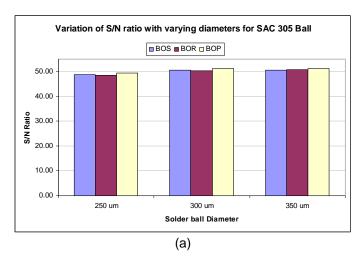

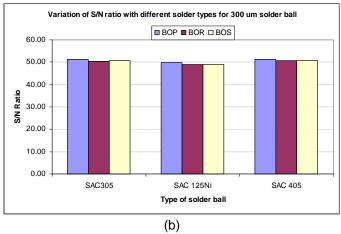

| 4.6  | Variation of S/N ratio for (a) Different solder Diameters mounted on different structure for SAC 305 ball and (b) Different solder                                                        |    |

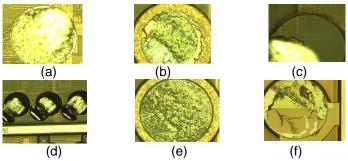

| 4.7  | With 300µm diameter mounted on different structures<br>Failure modes observed in ball shear testing<br>(a) Mode I at 25µm (b) Mode II at 25µm<br>(c) Mode III at 25µm (d) Mode I at 125µm |    |

|      | (e) Mode II at 125µm (f) Mode III at 125µm                                                                                                                                                | 66 |

| 4.8  | Ball shear Testing                                                                                                                                                                     | 67 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

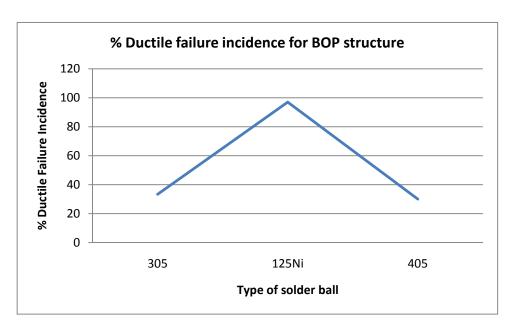

| 4.9  | % Ductile failure incidence for different solder ball compositions For Ball on Pad structure with 300µm Ball diameter                                                                  | 68 |

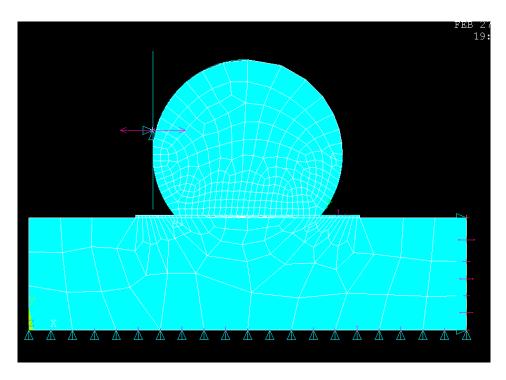

| 4.10 | Meshed 2D model for Ball Shear Test                                                                                                                                                    | 71 |

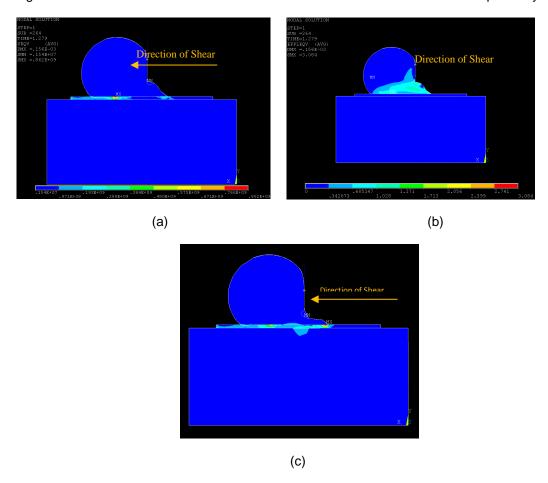

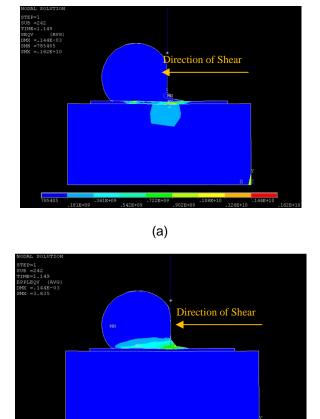

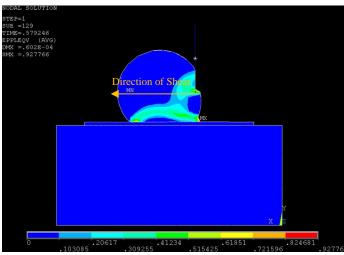

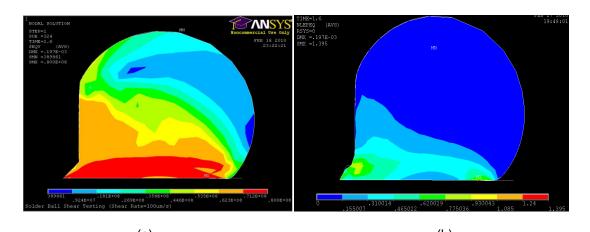

| 4.11 | Simulation of Ball shear test on BOR structure (a) Von-Misses stress on SAC 305 at 100µm/s (b) Von-Misses strain on SAC 305 at 100µm/s and (c) Von-Misses stress on SAC 305 at 700µm/s | 72 |

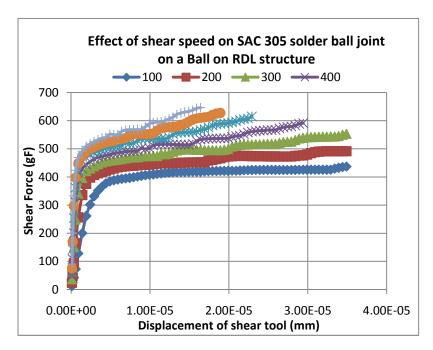

| 4.12 | Shear Force Vs Displacement curve for SAC 305 BOR Structure                                                                                                                            | 73 |

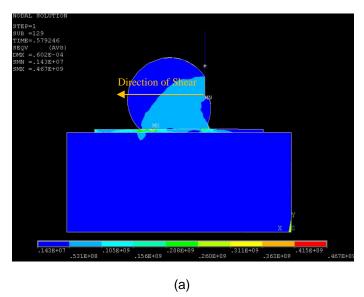

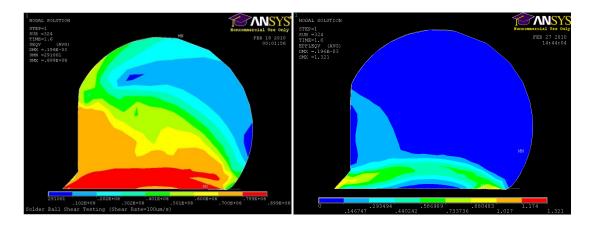

| 4.13 | Simulation of Ball shear test for SAC 305 solder ball mounted<br>On BOR structure sheared at 10µm (a) Von-Misses stress and<br>(b) Von-Misses strain                                   | 74 |

| 4.14 | Simulation of Ball shear test for SAC 305 solder ball mounted<br>On BOR structure sheared at 100µm (a) Von-Misses stress and<br>(b) Von-Misses strain                                  | 75 |

| 4.15 | Simulation of Ball shear test for SAC 305 solder ball mounted On BOR structure sheared at 125µm (a) Von-Misses stress and (b) Von-Misses strain                                        | 76 |

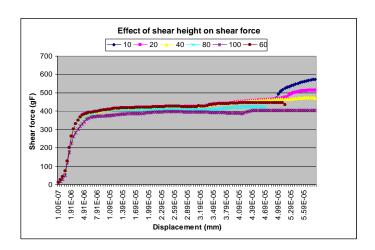

| 4.16 | Effect of Shear Height studied on SAC 305 solder ball On BOR structure                                                                                                                 | 77 |

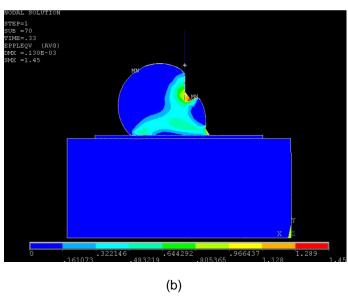

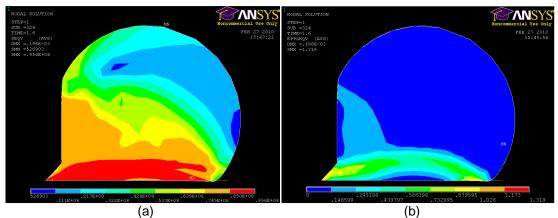

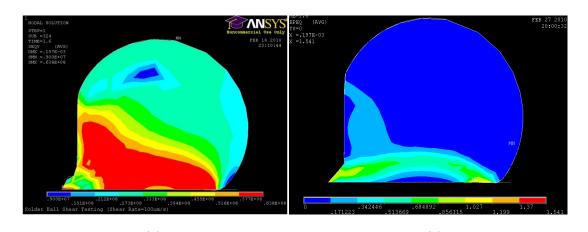

| 4.17 | Simulation of Ball Shear at 20°C for SAC 305 (a) Von-Misses<br>Stress (b) Equivalent Plastic Strain                                                                                    | 78 |

| 4.18 | Simulation of Ball Shear at 45°C for SAC 305 (a) Von-Misses<br>Stress (b) Equivalent Plastic Strain                                                                                    | 79 |

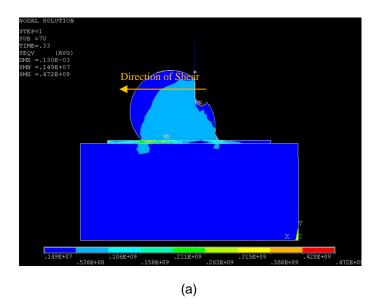

| 4.19 | Simulation of Ball Shear at 82.5°C for SAC 305 (a) Von-Misses<br>Stress (b) Equivalent Plastic Strain                                                                                  | 79 |

| 4.20 | Simulation of Ball Shear at 125°C for SAC 305 (a) Von-Misses<br>Stress (b) Equivalent Plastic Strain                                                                                   | 80 |

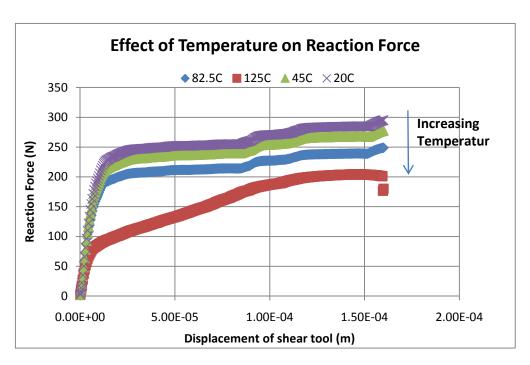

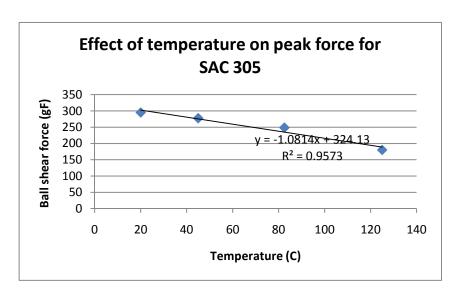

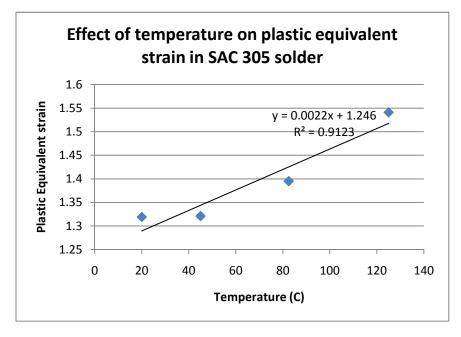

| 4.21 | Effect of Temperature on Ball shear force for SAC 305 solder Bump with 250µm on RDL structure                                                                                          | 81 |

| 4.22 | Reduction of Peak Ball shear force when Ball shear test was done At 25µm height                                                                                                        | 82 |

| 4.23 | Effect of temperature on plastic equivalent strain induced In 250µm solder bump in SAC 305 ball                                                                                        | 82 |

|      |                                                                                                                                                                                        |    |

| 5.1  | Accelerated thermal cycling profiles commonly Used in Microelectronics industry84                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------|

| 5.2  | Thermo-Mechanical deformation that are observed in Electronic packages during thermal cycling85                                  |

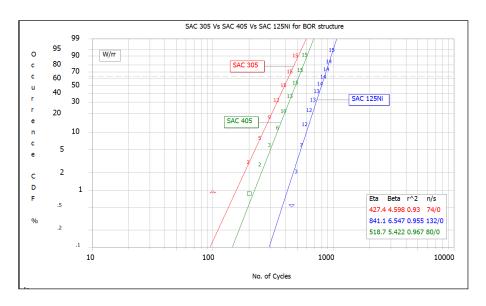

| 5.3  | Weibull plot for 300µm solder ball with different composition  For a ball on pad structure                                       |

| 5.4  | Weibull plot for 300µm solder ball with different composition  For Ball on RDL structure88                                       |

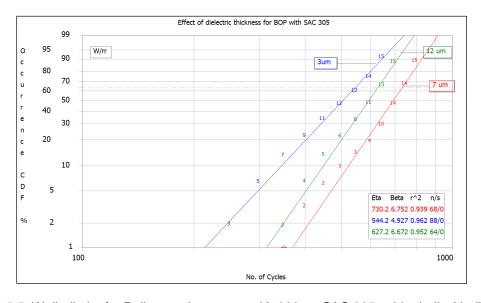

| 5.5  | Weibull plot for Ball on pad structure with 300µm SAC 305 solder ball with different Dielectric thicknesses                      |

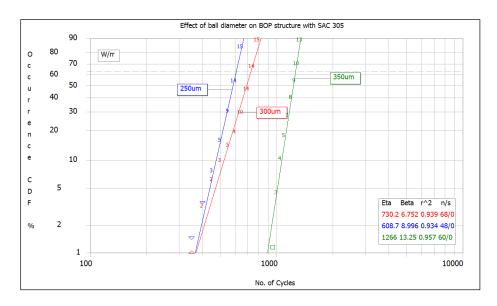

| 5.6  | Weibull plot for ball on pad structure with 250µm, 300µm and 350µm SAC 305 solder ball With 7µm dielectric thickness89           |

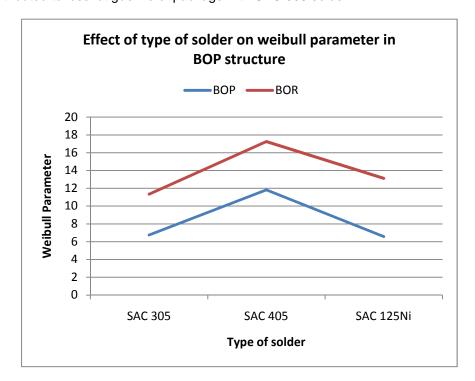

| 5.7  | Effect of type of solder on weibull parameter tested On Ball on Pad and Ball on RDL structure90                                  |

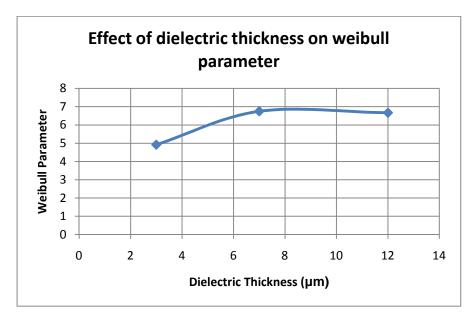

| 5.8  | Effect of dielectric thickness on weibull Parameter for Ball on Pad structure91                                                  |

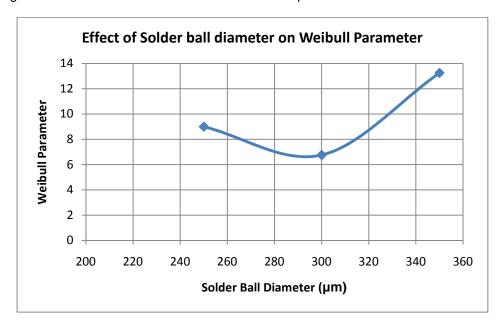

| 5.9  | Effect of solder ball diameter on weibull parameter for Ball on Pad structure91                                                  |

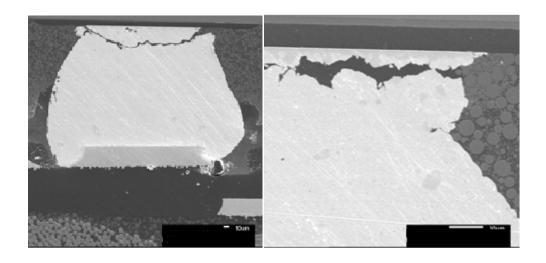

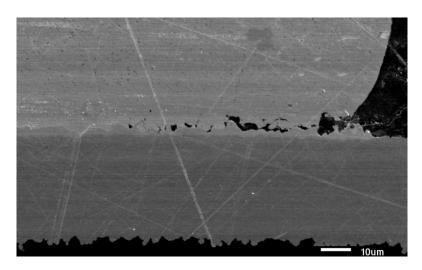

| 5.10 | SEM micrograph of a 250µm on BOR structure (a) Solder Bump (b)Focussed on Corner and (c) Different solder bump from same package |

| 5.11 | Scanning electron micrographs for 300um SAC 305 crack on PWB side94                                                              |

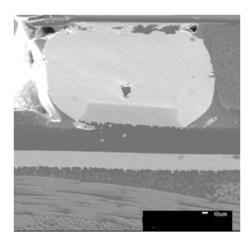

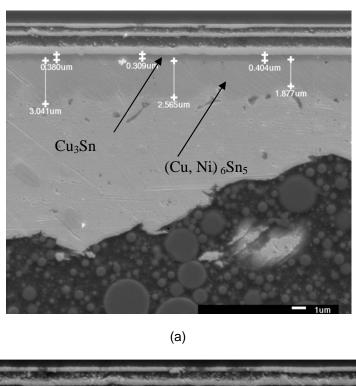

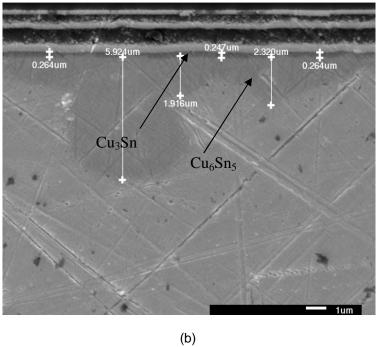

| 5.12 | Intermetallic thickness observed in solder bumps (a) SAC 125Ni (b) SAC 40595                                                     |

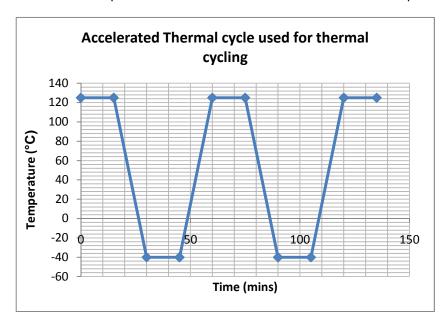

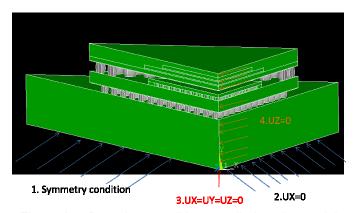

| 5.13 | Standard accelerated thermal cycle used for accelerated thermal cycling of electronic assemblies                                 |

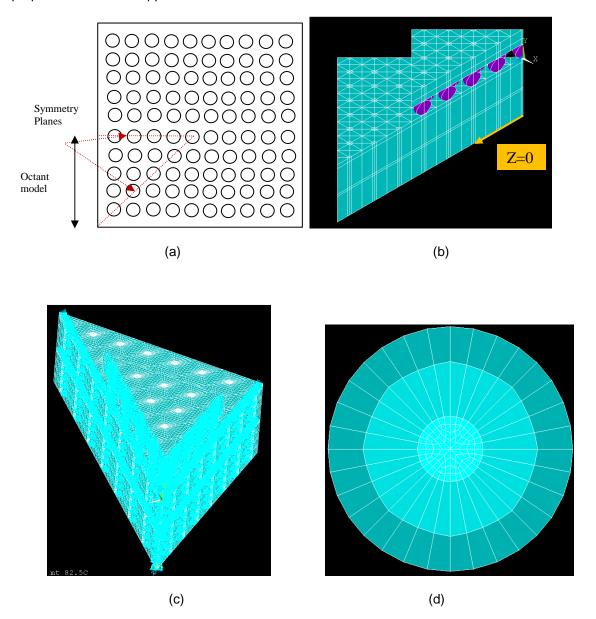

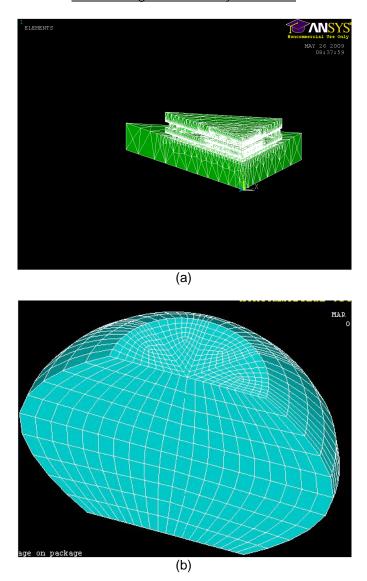

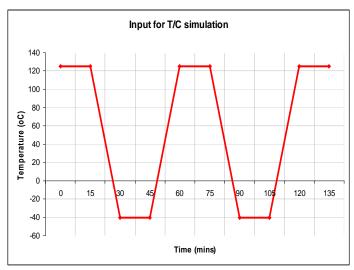

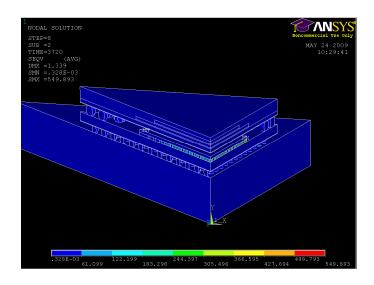

| 5.14 | WLCSP model under consideration (a) Schematic (b) Octant Model (c) Mesh with boundary Conditions and (d) Mesh on Solder Ball     |

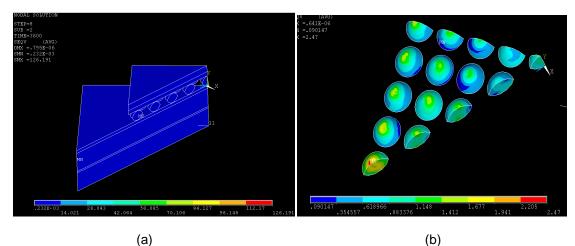

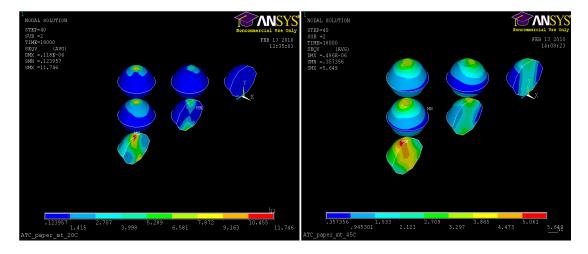

| 5.15 | Simulation of the Octant model (a) Von-Misses stress in  Complete model (b) Von-Misses stress in solder bumps102                 |

| 5.16 | Simulation of the Octant model (a) Von-Misses strain in  Complete model (b) Von-Misses strain in solder bumps                    |

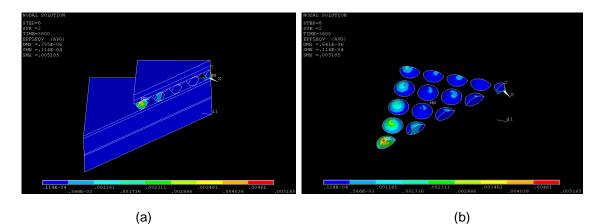

| 5.17 | Simulation of the Octant model (a) Plastic work Variable and (b) Plastic Work/Volume | 103 |

|------|--------------------------------------------------------------------------------------|-----|

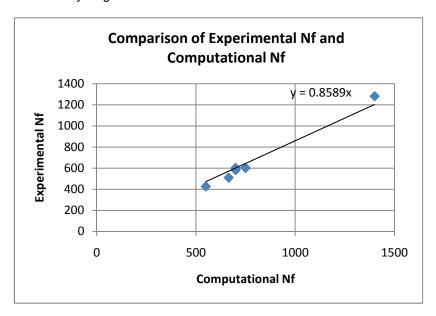

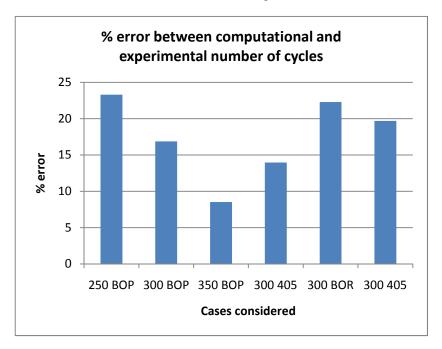

| 5.18 | Experimental Cycles to failure Vs Computational Cycles To failure                    | 104 |

| 5.19 | % Error in between Computational life cycles and Experimental life cycles            | 105 |

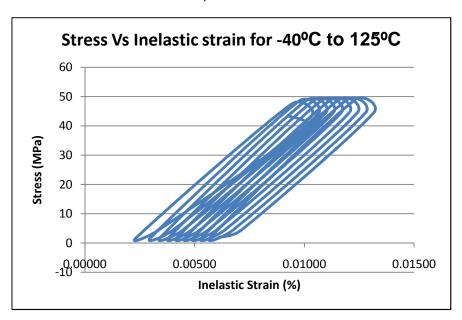

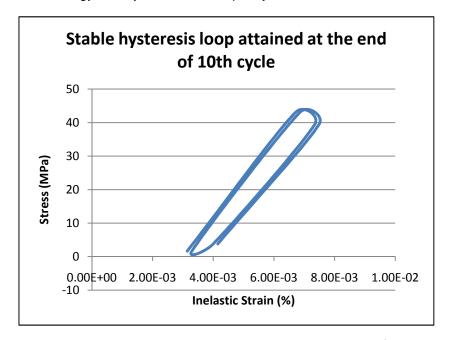

| 5.20 | Hysteresis loops observed in the corner most solder bump                             | 106 |

| 5.21 | Stable Hysteresis loop obtained at the end of 10 <sup>th</sup> cycle                 | 107 |

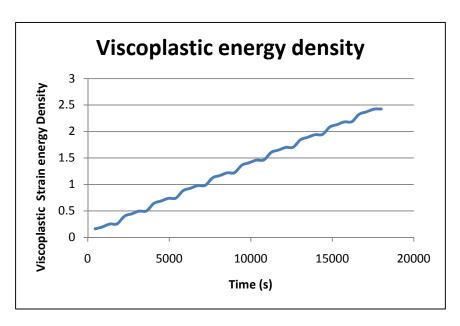

| 5.22 | Viscoplastic Strain energy density build up in corner Bump over time                 | 108 |

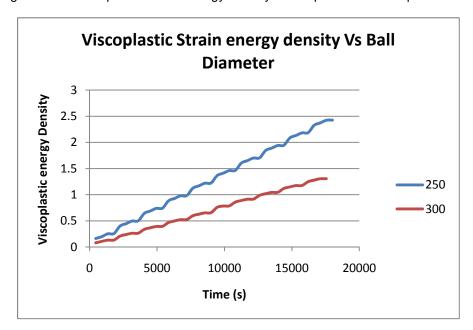

| 5.23 | Effect of Ball diameter on Viscoplastic Strain energy density                        | 108 |

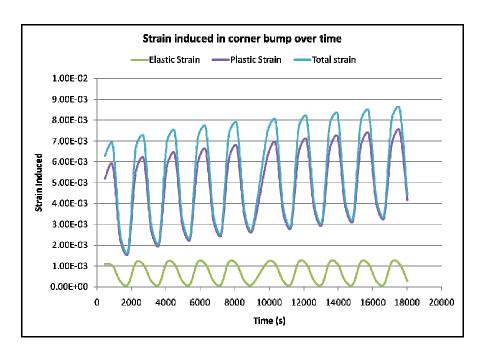

| 5.24 | Comparison of Elastic and Inelastic strain induced in Corner Solder bump with time   | 109 |

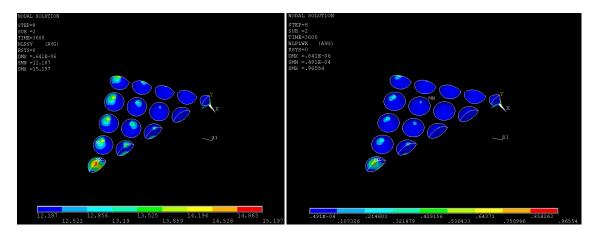

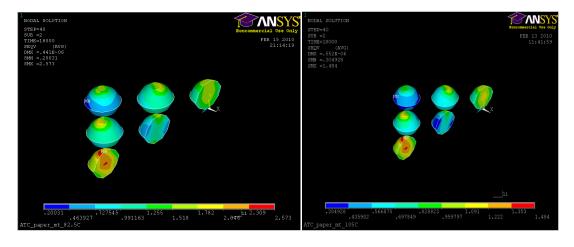

| 5.25 | Von-Misses stress for various mean temperatures (a) 20℃ and (b) 45℃                  | 111 |

| 5.26 | Von-Misses stress for various mean temperatures (a) 82.5℃ and (b) 105℃               | 112 |

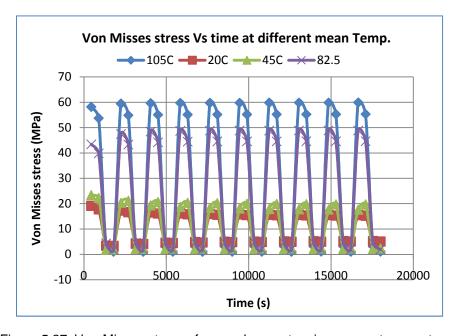

| 5.27 | Von-Misses stress of corner bump at various mean Temperatures                        | 112 |

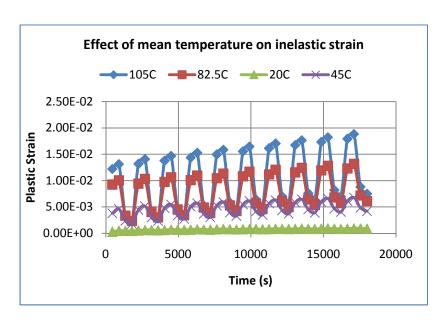

| 5.28 | Von-Misses Inelastic strain of corner bump at various mean<br>Temperatures           | 113 |

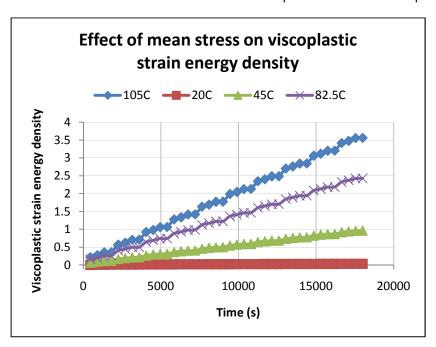

| 5.29 | Effect of mean stress on Viscoplastic strain energy density For corner bump          | 113 |

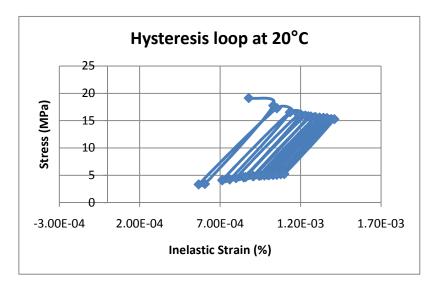

| 5.30 | Hysteresis loop obtained for Corner bump at 20℃ mean<br>Temperature                  | 114 |

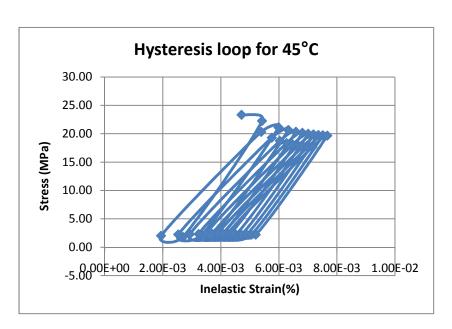

| 5.31 | Hysteresis loop obtained for corner bump at 45°C mean Temperature                    | 115 |

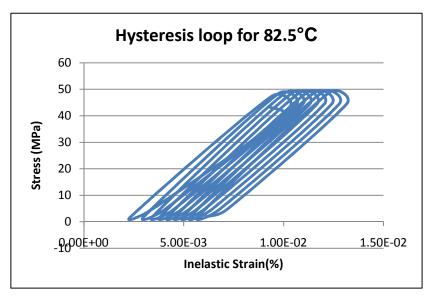

| 5.32 | Hysteresis loop obtained for corner bump at 82.5°C mean Temperature                  | 115 |

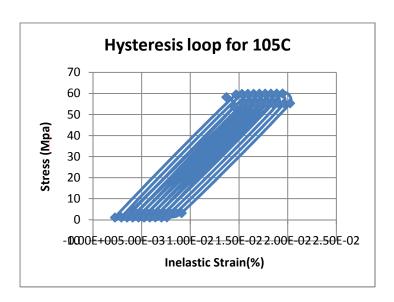

| 5.33 | Hysteresis loop obtained for corner bump at 105°C mean Temperature                   | 116 |

| 5.34 | Stable Hysteresis loop obtained for corner bump at different mean Temperatures       | 116 |

| 5.35 | Of hysteresis loops                                                                                                                                         | 117 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.1  | Superimposing stress Vs Inelastic strain for monotonic and Cyclic loading                                                                                   | 122 |

| 6.2  | Comparing the metrics - SN ratio, % Ductile failure incidence and Number of cycles Vs different solder ball compositions for 300 µm ball with BOP structure | 123 |

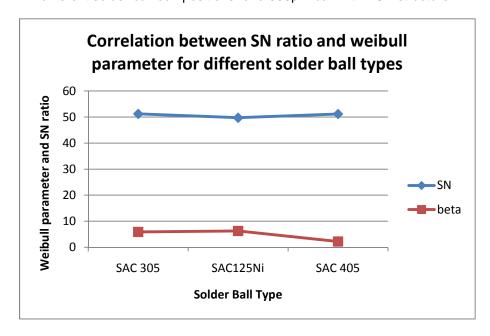

| 6.3  | Correlation between signal to noise ratio and weibull parameter For different solder compositions with 300 µm solder diameter                               | 123 |

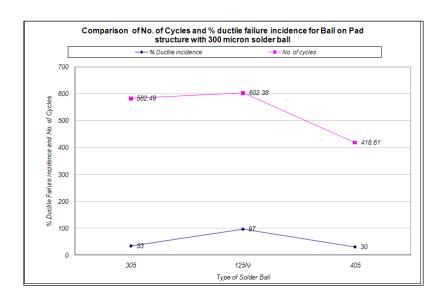

| 6.4  | Relationship between % ductile failure incidence And No. of cycles for 300 µm ball with Different solder compositions mounted on BOP structure              | 124 |

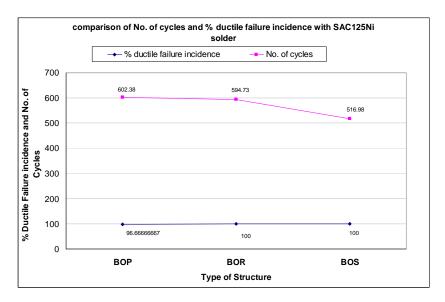

| 6.5  | Relationship between % ductile failure Incidence And No. of cycles for 300 µm SAC 125Ni Ball on different structures                                        | 125 |

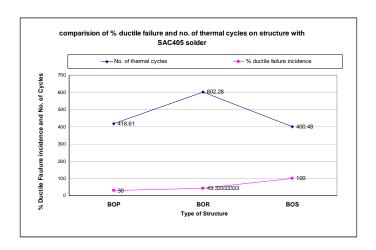

| 6.6  | Relationship between % ductile failure incidence And No. of cycles for 300 µm SAC 405 ball on BOP structure                                                 | 126 |

| 6.7  | Relationship between % ductile failure incidence And No. of cycles for 300 µm and 350 µm SAC 305 Ball on BOP structure                                      | 126 |

| 6.8  | Correlation between Normalized Life, Normalized failure mode and and normalized solder diameter                                                             | 130 |

| 6.9  | Correlation between Normalized life, Normalized failure mode and normalized dielectric thickness for 300µm ball                                             | 131 |

| 6.10 | Correlation between Normalized life, Normalized failure mode and normalized dielectric thickness for 350µm ball                                             | 132 |

## LIST OF TABLES

| Tab | le                                                                                                                                                                    | Page |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1 | Summary of commonly employed failure tests at wafer level                                                                                                             | 12   |

| 2.1 | Properties to look for in a new solder                                                                                                                                | 23   |

| 2.2 | Comparison of various Young's Modulus reported in literature                                                                                                          | 33   |

| 2.3 | Comparison of Anand's parameters obtained by different researchers                                                                                                    | 38   |

| 4.1 | Parameters that are varied in Ball shear test                                                                                                                         | 59   |

| 4.2 | DOE for all varied parameters along with results                                                                                                                      | 61   |

| 4.3 | Summary of ball shear test analysis                                                                                                                                   | 68   |

| 4.4 | Material properties used in the computational study of ball shear                                                                                                     | 71   |

| 4.5 | Effect of temperature on shear strength of solder                                                                                                                     | 83   |

| 5.1 | Summary of Thermal cycling DOE                                                                                                                                        | 89   |

| 5.2 | Material properties used in the model                                                                                                                                 | 100  |

| 5.3 | ANAND's constants for SAC 305 and SAC 405 solder                                                                                                                      | 101  |

| 5.4 | Temperature extremes and corresponding mean Temperatures considered in the study                                                                                      | 111  |

| 6.1 | Statistical correlation between Weibull parameter, Number of cycles and % ductile failure incidence for Different solder compositions with 300µm diameters.           | 128  |

| 6.2 | Statistical correlation between Weibull parameter, Number of cycles and % ductile failure incidence For SAC 305 solder with different ball Diameters on BOP structure | 128  |

| 6.3 | Statistical correlation between Weibull parameter, Number of cycles and % ductile failure incidence For different solders with 300 µm diameter on RDL structure       | 128  |

| 6.4 | Statistical correlation between Weibull parameter, Number of cycles and % ductile failure incidence For different dielectric thicknesses with 300 µm SAC 305 ball     | 128  |

| 6.5 | Statistical correlation between Weibull parameter,             |     |

|-----|----------------------------------------------------------------|-----|

|     | Number of cycles and % ductile failure incidence               |     |

|     | For different dielectric thicknesses with 350 µm SAC 305 ball. | 129 |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Miniaturization of Electronic Components

Electronic devices now permeate virtually in every aspect of our life. Among most ubiquitous of these are the portable consumer electronics such as Laptop, PDA, cell phones, smart phones etc. The applications of electronic systems vary from entertainment to highly complex systems supporting vital health, economic, scientific and military. Developments in the semiconductor industry, along with consumer demand for cheaper, lighter, high density information processing tools have revolutionized the entire electronic packaging infrastructure. The result of this demand has resulted in development of high function, high density interconnect semiconductor devices with ever increasing functionality into smaller and smaller devices. Figure 1.1 shows the trend of packages decreasing size from a Quad Flat Pack to a Flip Chip Package and more.

Figure 1.1 Reduction of the footprint of Electronic Package [1]

Chip scale packages were the workhorses of miniaturization post 1995. But Wafer level package reduces the size of the package and increases the packaging efficiency even more than a chip scale package. Next section talks about chip scale package and Wafer level Chip scale package.

#### 1.2 Packaging Efficiency

Packaging Efficiency is defined as the ratio of area of die to the area of IC package. This is a very important parameter and plays a key role in miniaturizing electronic systems. Portable consumer electronic systems such as cell phones, PDAs, smart phones, digital cameras, camcorders and laptops have packages with high Packaging Efficiency where size is the most important concern. Bare chip packaging, as per the above definition is 100% efficiency, Dual Inline Package has less than 2% efficiency, BGA has about 30%-80% efficiency. Chip Scale Package (CSP) is defined as any IC package which occupies a footprint area of no more than 50% greater than area of the chip it packages and which has a perimeter no more than 20% greater than that of the chip it packages [1]. CSP is one of the most important packages types in recent years due to the unprecedented demand for portable and hand held devices. The advantage of CSP, compared to direct chip attach of flip chip to a board, is that the CSP is designed to take up the mismatch if coefficient of thermal expansion (CTE) between the chip and the board. Hence, in general it is not necessary to underfill the chip scale package after it is soldered to the board, which is very important component in flip chip assembly. This is one of the main reasons why CSP packages were the driving force of miniaturization especially in portable electronics in last decade. Another important reason for popularity of Chip scale package is it can normally be implemented into a standard surface mount process without any major modifications. Wafer level package however offers even better packaging efficiency, when chip scale package technology is implemented on the wafer scale that's when we get the Wafer Level Chip Scale Package (WLCSP).

#### 1.2.1 Wafer level Chip Scale Package

The Wafer level package (WLP) is a type of chip scale package (CSP), which enables the IC to be attached face down to a printed circuit board (PCB) using conventional Surface Mount Assembly methods. WLP technology differs from Ball Grid Array, leaded and laminates based CSPs because no bond wires or interposers are required to connect die to the substrate. WLP can have good reliability without using an underfill because typically for WLP to be used in portable electronic devices the size of interconnect is big hence it has more compliance with the CTE mismatch. The main advantages of WLP are as follows

- Space savings from attainment of the smallest package possible for a device

i.e. a true chip size package.

- Lowest cost per I/O since the traditional package assembly processes that are independent of wafer fab have been replaced by wafer level interconnection processes.

- 3. Lowest cost of electrical testing since this is done more efficiently at wafer level.

- 4. Lowest cost of burn-in since this is done more efficiently at wafer level.

- Enhancement of device performance because of its minimum length interconnections.

- Eliminating the need for underfilling of solder joints with organic materials hence possibility to rework the package and,

- 7. Easier inventory management since fab, assembly, test and burn-in can essentially be housed under one production floor. [2]

Typical wafer level package is shown in figure 1.2.

Figure 1.2: Typical Wafer Level Chip Scale Package [3]

Figure 1.3: Market share of Wafer level packages in camera modules [91]

Yole.com reports that "Wafer level packaging is a confirmed high growth trend in the semiconductor packaging industry. Wafer level chip scale packaging (WLCSP), or the direct bonding on printed circuit boards (PCB's) of bumped integrated circuits (IC's) as one of the most visible expressions of WLP and is the fastest growing package type in the whole industry. Yole's research study forecasts that it will exceed 10 billion units per year by 2012, at a

compound annual growth rate of more than 20% over the next 5 years as seen in figure 1.4. Primarily driven by footprint and thickness reduction of packaged integrated circuits in mobile phones, in a wide range of circuits for handsets, EMI/ESD interface protection, power supply, converters, LED drivers, MOSFET's and other features like FM,GPS, TV and on camera."

Figure 1.4: WLCSP and WLP unit volumes forecasts [92]

Besides offering unequaled benefits of small footprint and thickness geometries, WLCSP has become cost competitive with QFN, its main package platform competitor in handsets. This cost benefit now paves the way for the adoption of WLCSP by more consumer end user applications like netbooks, notebooks, gaming consoles, MP3 players and digital still cameras. Some WLCSP devices can also be found in automotive applications, which may well represent a future growth sector for WLP. Figure 1.5 shows the comparison of value offered by a wafer level chip scale package as opposite to other small packages.

# **Package Value Proposition Summary**

Figure 1.5: Comparison of WLCSP with other small packages [92]

Besides offering unequaled benefits of small footprint and thickness geometries, WLCSP has become cost competitive with QFN, its main package platform competitor in handsets. This cost benefit now paves the way for the adoption of WLCSP by more consumer end user applications like netbooks, notebooks, gaming consoles, MP3 players and digital still cameras. Some WLCSP devices can also be found in automotive applications, which may well represent a future growth sector for WLP.

Although Wafer level Chip scale package is great from all aspects of reducing size, increasing packaging efficiency, saving cost etc. it is not entirely free from failures. Wafer level chip scale packages present unique reliability challenges because as the size of the package reduces, number of packages put together on a wafer increases dramatically. Hence there are issues related to processing that typically can get percolated down the line as the package goes through different levels of packaging. In order to understand the reliability challenges that are offered by wafer level chip scale packages it is important to understand the process in which a package is fabricated from silicon crystal.

#### 1.3 Fabrication of structures on wafer level

Wafer level fabrication of a chip scale package is an extremely complicated process and it typically involves a lot of processes and each of that process is dependent on controlling factors. Typical steps involved in wafer level fabrication of an IC package are discussed in this section. Processing of wafers can essentially be divided into two sections namely, front end processing and back end processing. Semiconductor manufacturing consists of the following steps

- 1. Production of silicon wafers from very pure silicon ingots

- 2. Fabrication of integrated circuits into these wafers

- 3. Assembly of every integrated circuit on the wafer into a finished product and

- 4. Testing and back-end processing of finished products.

#### 1.3.1 Wafer level fabrication process

Wafer fabrication generally refers to the process of building integrated circuits on to silicon wafers. Prior to wafer fabrication, the raw silicon wafers to be used for this purpose are produced as a single crystal using Czochralski (CZ) method. The single crystal is then cut into very thin plate's perpendicular to its axis. The thin plates (also called as ingots) are then shaped into wafers using a process called as wafering. At the end of this process, a wafer has number of transistors that are connected to the second level interconnect which will eventually be connected to a board. A generalized process of forming devices is as follows

- A p-type or n-type epitaxial layer on the silicon substrate is grown through chemical vapor deposition.

- A Nitride layer is then deposited over the epi-layer, the nitride layer is masked and

is then etched out using physical or chemical etch leaving behind exposed areas on

the epi-layer i.e. areas no longer covered by the nitride layer.

- The exposed areas are masked again and then bombarded with ions of the doping material in specific patterns using diffusion or ion implantation. Typical dopants used are phosphorous forming n-wells.

- 4. Silicon dioxide is then grown thermally to form oxides that isolate the n-wells from other parts of the circuit. This may be followed by several other steps of masking/oxidation cycle to grow gate oxide layers over the n-wells intended for pchannel MOS transistors. The gate oxide layer serves as the insulation between the p-type and n-type.

- 5. Deposition of polysilicon layer over the wafer may then be done, to be followed by a masking/etching cycle to remove unwanted polysilicon areas defining the polysilicon gates over the gate oxide of the p-channel transistors. At the same time, openings for source and drain drive-ins are made on the n-wells by etching away oxide at the right locations.

- 6. Another round of mask/implant cycle may then follow, this time driving the p-type dopant (typically boron) into new openings forming the p-type sources and drains. In such a way there are several mask/implant cycles that are repeated depending on the structure of the package.

- 7. The wafer is covered with phosphor-silica glass, which is then subjected to reactive ion etching in specific patterns to expose contact areas for metallization. Aluminum is then sputtered on the wafer, after which it is subjected to reaction ion etching, also in specific patterns, forming connections between various components of the circuit.

- 8. The wafer may then be covered with glassivation as its top protective layer, after which a mask/etch process removes the glass over the bond pads. Such is the process of wafer fabrication, consisting of a long series of mask/etch and mask/deposition steps until the circuit is completed.

- 9. The interconnection typically in case of a wafer level chip scale package is a solder bump. Thus once, the wafer with complete integrated circuit comes at the bumping process, pre-formed bumps are placed over the wafer and are pressed against the bond pads to form a temporary joints.

- 10. After the bumping process the wafer goes through a reflow oven where under the action of a reflow profile a firm bond between the solder and the bond pad due to formation of intermetallics and hence the wafer fabrication of the chip scale or for that matter any package is completed. [4]

Figure 1.6 shows the fabrication process of fabricating the device structure.

Figure 1.6 Process of fabrication of structures on a wafer [5]

The procedure mentioned in the above section is followed for practically every wafer level device fabricated in the industry with variation of the actual process parameters. Most important thing about fabrication of devices on wafer is that they have to be designed for reliability considerations of portable devices, high end devices, military standard devices etc. A wafer level package faces reliability challenges that are unique to each of these environments. In this dissertation however, we are going to focus only on the portable electronics section.

#### 1.4 Reliability Considerations in Portable Electronic Devices

Portable electronic devices are exposed to a wider variety and severity of environmental stresses than their desktop counterparts. The failure of packaging and semiconductor components is often accelerated by higher than normal stresses such as temperature, relative humidity, excess voltage and current, vibration, shock and high acceleration. Ionic Contaminants, air borne particulates (dust and dirt), and environmental pollutants are added to hasten the onset of certain failure modes. [6] Long-term degradation cannot always be demonstrated at normal operating conditions. The sample size and the test are subjected to larger than usual environmental stresses to obtain failure data in a short amount of time. These tests are called accelerated environmental stress tests. The objective of accelerated tests is to estimate the lifetime distributions of the components at normal stress levels using failures data from such tests. These are designed to evaluate the robustness and reliability of the board level packages. Many of the tests with accelerated stress conditions are designed to enable the packaging engineer to extrapolate the test results to the field environments. Some of these tests are conducted with specially designed test vehicles, prior to the product manufacturing. The test vehicles are designed to exercise the design, fabrication and process limits of a given technology. Most products utilizing that technology are expected to have the intended reliability.

With the growing availability of low cost, portable devices, reliability engineers need to develop test programs that can be administered and can quickly to provide accurate information about the performance of the entire system. A well thought out and aggressive test program is one of the most significant techniques to validate the design's integrity and ability to meet established usability requirements. In this discussion general test planning plus considerations spanning the categories of mechanical, and thermo-mechanical reliability have been discussed.

One of the most important advantages of having wafer level chip scale packages was their faster time to market time and cost. Acceleration tests to determine the failure mechanism

and hence failure are different at every packaging level. Figure 1.7 shows different failure mechanisms and acceleration factors involved at all different levels of packaging.

Figure 1.7: Failure mechanisms and acceleration factors at different levels of packaging [1]

It can be inferred from figure 1.7 that different levels of packaging have different failure mechanisms, different acceleration factors and different designs for reliability. Hence different at different levels of packaging there are different reliability tests that have been designed by Joint Electronic Device Engineering council (JEDEC) to capture the failures and eventually create design for them. An important challenge in designing a reliability program and a test vehicle is how to reduce its duration without sacrificing the accuracy of results.

#### 1.4.1 Interconnect Reliability at Wafer level

Due to miniaturization, the number of iterations involved with the mask/etch process typically forming layers of interconnect increase. These different layers are then metalized using various processes and are programmed to perform specific tasks. Each of the processes namely spinning, etching, lithography, UV exposure, bumping and reflow are extremely sensitive to their controlling factors and temperature. Any variations in these knobs directly affect attachment of these layers considerably and hence it is important to have a test that can

check structure mechanically. The interconnect in case of a wafer level chip scale package is a solder bump made of a lead free solder that is attached on the bond pad and then reflowed to form a joint. The desired test should satisfy the following requirements.

- The reliability test should let the designer know what knobs are important and what the possible failures over a wide range of strain rates.

- 2. The reliability test should be easily employed in the wafer fabrication routine.

- 3. The test should be inexpensive and

- 4. The turnaround time of the test should be as little as possible.

Table 1.1 gives a summary of commonly employed failure reliability tests that are used for checking quality of a wafer level structure.

Table 1.1: Summary of Failure Reliability Tests that are used to check quality of wafer level structure

| No. | Mechanical Testing  Method | Cost of Test | Prep and Test time |

|-----|----------------------------|--------------|--------------------|

| 1   | Solder Ball shear          | Low          | Short              |

| 2   | High speed ball shear      | Low          | Long               |

| 3   | Cold Ball Pull             | Low          | Short              |

| 4   | High speed ball pull       | Low          | Long               |

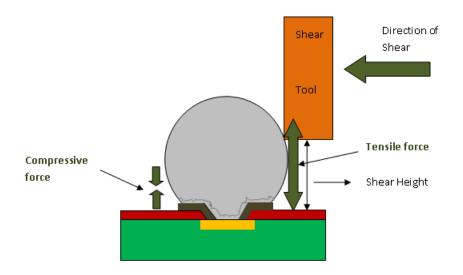

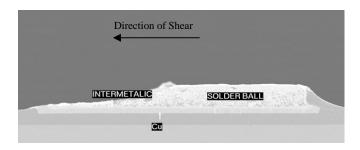

Ball pull test and ball shear test are very commonly employed in a wafer fabrication facility to check the process reliability. In case of high speed shear and high speed pull typically sample preparation is required. The sample consists of a particular part of wafer that is separated out by breaking the wafer and then is glued to a mounting plate using LocTITE and hence the time taken by the test is long. Figure 1.6 shows the typical failure mode that is observed in a ball shear test.

Figure 1.8: Typical failures observed in a Ball shear Test (a) side view and (b) top view [7]

Several researchers have attempted to compare ball shear and ball pull and have tried

to find out which mechanical testing method is better in identifying brittle failure mode. In ball pull test the primary failure mechanism is tensile force whereas in ball shear test the primary failure mechanism is shear force. Figures 1.8a and 1.8b show the typical failure modes that are observed in a ball shear test respectively. Typically the failures observed in these tests are divided into three modes namely ductile failure, semi-ductile failure and brittle failure. Different researchers have used different nomenclatures for describing the above mentioned failures. In this dissertation they are described as mode 1 failure, mode 2 failure and mode 3 failures. More about ball shear test and its failure is explained in chapter 3 of this dissertation. Every failure mechanism has its own signature and that can be found through its failure modes. For a ball shear test it is tension on one side and compression on other side of the bond pad. That particular failure signature matches with accelerated thermal cycling test which is a standard test done for the assessing reliability of interconnects at second level of packaging. In case of accelerated thermal cycling the failure mechanism is compression and on one side and tension on other side of bond pad. In case of accelerated test the direction of shear forces and hence signature alternates as temperature is ramped up and down in the given thermal cycle.

#### 1.4.2 Interconnect Reliability at board level

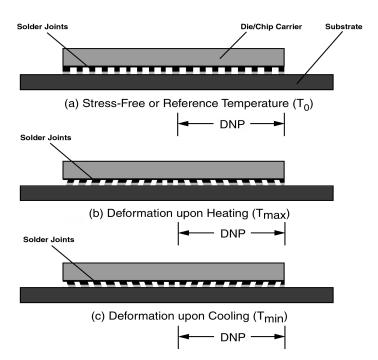

As the package climbs up the ladder from first level packaging test to second level packaging the reliability tests change considerably. Second level reliability tests are followed after the reflow cycle. Thermal cycling tests are used to study the effect of thermo-mechanical stresses generated during operation of electronics. Shear strains and hence stresses are generated because of the mismatch between coefficient of thermal expansion between package and board. Thermal cycling tests are typically carried out in air-to-air or fluid-to-fluid test chambers depending on the required ramp rate of the cycling. Figure 1.9 shows the typical arrangement of boards and the acceleration cycle that is given to the chamber.

(a) (b)

Figure 1.9: Typical thermal cycling test setup (a) Chamber (b) Arrangement of boards in the chamber [8]

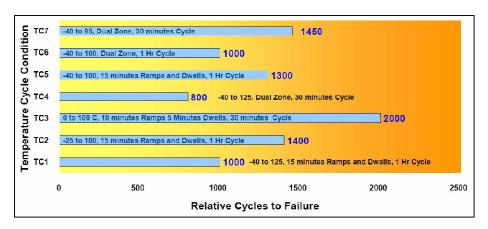

Important factors affecting the fatigue life of solders in accelerated thermal cycling are the temperature extremes and hence the mean temperature, the ramp rates, dwell times and frequency of cycle. Typically the maximum temperature in a thermal cycle is 125°C which corresponds to a homologous temperature of 0.57-0.6 thus it allows the creep strain is also a major contributor to the total strain which cannot be ignored totally as it is done in a plasticity dominated failures. Different organizations have different standardized tests for accelerated

thermal cycling; JEDEC has published its own standardized test standard JESD22-A104C [9] for standard handheld portable electronic product. So for every test an organization spends thousands of dollars on equipment operating cost and maintaining cost. On top of it every product line will be going through a series of board level reliability tests. Researchers have actually started getting a crack at establishing acceleration factors between board level reliability and wafer level reliability. This dissertation is an attempt to establish similar acceleration factors between ball shear test and accelerated thermal cycling reliability.

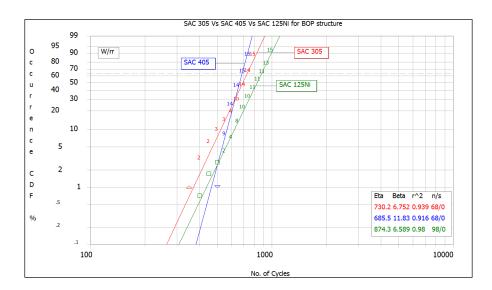

In this dissertation, an attempt has been made to establish acceleration factors between wafer level ball shear testing and board level accelerated thermal cycling. Figure 1.10 compares the turnaround time of ball shear test and accelerated thermal cycling. Establishing acceleration factors between wafer level reliability testing and board level reliability testing is tedious. At wafer level the solder typically is as cast or virgin solder. An as cast lead free solder will have very less number of grains. In case of board level reliability tests the solder goes through another reflow process for joining of solder to board. This process adds another set of intermetallics formed on the board pad side. As the package goes through the accelerated thermal cycling the solder structure is modified into many grains primary due to the grain boundary binding phenomena that is very common in fatigue loadings. Thus, development of an analytical model is not possible between the two. Hence any correlation that is derived between wafer level reliability tests and board level reliability tests are empirical. To understand various aspect of structure, solder material and solder size a huge DOE has to be planned. In this study a DOE comprised of three solder materials SAC 305, SAC 405 and SAC 125Ni, three solder bump sizes 250µm, 300 µm and 350 µm, two different structures namely ball on pad structure and ball on RDL structure, three different dielectric thicknesses 3 µm, 7 µm and 12 µm are discussed. In this study ball shear test and accelerated thermal cycling were done separately and hence are discussed separately. Figure shows the difference in testing times between the ball shear test and the accelerated thermal cycling.

Figure 1.10: Comparison of Wafer level testing and Board level test times

#### 1.5 Dissertation outline

In order to understand and correlate the failure mechanisms at the two levels it is essential to understand the structure and also the constitutive models that a solder follows. In Chapter 2 lead free solders have been reviewed, also in chapter 2 a short review of various constitutive and fatigue life predicting models are made. Chapter 3 talks about the literature review of ball shear test. Detailed literature review that talks on the different aspects of ball shear test. In chapter 4 the details of experimental setup is discussed along with the finite element model generation in commercially available software. Chapter 4 also includes the results and discussion of experimental and computational testing of ball shear test. In chapter 5 accelerated thermal cycling performed on wafer level chip scale package is reviewed. Chapter 5 also reviews the publications where some publications were wafer level testing and ball shear testing is compared. In chapter 6 the experimental and computational setup for accelerated thermal cycling are discussed along with the results and discussion. In chapter 7 correlation

coefficients between accelerated thermal cycling and ball shear test are discussed along with empirical correlations that are derived based on the structural parameters at wafer level. Chapter 8 finally concludes the dissertation and suggests ideas for future work.

#### 1.6 Problem Definition

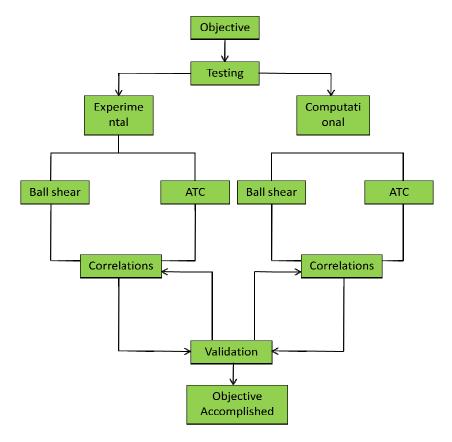

From the above discussion, it is clear that one of the challenges today for electronic packaging industry is to reduce the testing time of board level packages. A methodology that can predict the fatigue reliability of board level packages based on the wafer level ball shear tests, can impact the entire electronic manufacturing industry, from component supplier to equipment manufacturer. The industry is moving forward to wafer level chip scale package which has only one interconnect between the substrate and board and hence this study is possible only on a wafer level package. Figure 1.11 shows the process that was followed in developing this dissertation. In this dissertation three different solder bumps of three different sizes on two different structures is tested and compared with the similar packages mounted on board level. Correlation factors are derived by comparing the shear forces and strains generated during the test. Work done in completing the dissertation is described as follows.

- Wafers are processed using the dedicated processing parameters so that the ball on pad and ball on RDL structures are generated.

- The structures are tested mechanically on a dedicated ball shear testing machine. The ball shears are carried out in zone. The zones are located in center and one of the corners of the wafer to make sure a mechanical integrity of structure is maintained throughout the wafer.

Figure 1.11: Process flow followed in developing this dissertation

- A DOE comprised of two different structures, three different solders and three different sizes is designed and implemented. Ball shear tests are carried out at two heights 25µm and 125µm to make sure that the design is tested in shear as well as a combination of shear and torsion loading. Best leg of the DOE was determined by using Signal/Noise ratio from larger the better option in Taguchi Analysis.

- All the ball shear cases were validated computationally and using the force Vs distance diagram the strain rates for different cases were obtained. shear stress was obtained using the time-history viewer in ANSYS® and compared with experimentally measured forces. Ball shear tests were also carried out at different temperatures using the

- temperature dependent material properties that were fed into the multi-linear kinematic hardening model.

- Packages similar to the packages tested in ball shear test are mounted on a standard four layer accelerated thermal cycling boards. The boards are subjected to accelerated thermal cycling based on JEDEC standard JESD22-A104C [9] and weibull plot, along with other failure analysis data was obtained.

- All the accelerated thermal cycling cases are duplicated computationally using a mapped structured mesh. Anand's model was used to model the Viscoplasticity of solder joint considered; anand's model parameters of different solders were obtained through literature. All material properties given as inputs are modeled as temperature dependent properties. The post-processing of all the models was carried out using Darveaux's approach to calculate the crack initiation and crack propagation.

- The shear stress obtained from monotonic loading (ball shear test) and cyclic loading (accelerated thermal cycling) are fed into the Basquin's equation and basquin's coefficients were calculated for different temperatures and for different solder bumps with different solder sizes.

- Number of cycles required to failure occurred in accelerated thermal cycling is calculated based on Basquin's coefficients.

- Best configuration is determined based the studies performed computationally and experimentally.

- Correlation coefficients were drawn using statistical function "CORREL" between different arrays. These correlations are derived based completely on experimental data. The mode of failure obtained in Ball shear test was considered as a metric from monotonic loading. Failure mode is compared with weibull parameter, Number of cycles; solder ball diameter, dielectric thickness and correlation coefficients were derived.

Trends were established in dimensions, types of solder of wafer level chip scale

package structure on wafer level between Number of cycles and Weibull parameter

from accelerated thermal cycling which is essentially a board level test.

#### **CHAPTER 2**

#### LITERATURE REVIEW OF LEAD FREE SOLDERS

## 2.1 Transition from Eutectic Tin Lead to Lead free Solders

The use of solders for establishing interconnection between package and board goes back at least five decades. Consistent reduction in size of electronic packages has resulted in reduction in size of interconnects. Number of interconnect went on increasing with different types of package evolution starting from DIP, QFP and finally to area array packaging following the rent's rule. Demand for decreasing dimensions of packages also prompted development of new technologies such as CSP, FlipChip, WLP etc. The change in interconnect technologies demanded changes in processes and in the dispensing technologies required for their application. For these packages, solder is both the electrical and mechanical interconnect and thus its reliability is one of the most researched studies in electronic packaging industry. In the past, the Sn-Pb system was used almost exclusively in interconnect industry. Sn-Pb system was well understood, well characterized and very forgiving from process engineering point of view. However, in recent years the Sn-Pb system has been under scrutiny due to concerns over lead contamination, pollution in ground water. It is now recognized that use of lead based alloys is an environmental and health problem. As a result of environmental concerns and anxiety over the use of lead based alloys, lead free soldering got introduced as a main stream interconnect technology in the present decade. In Europe, the Waste Electronic and Electrical Equipment (WEEE) and the restriction of hazardous substances (RoHS) directives set resitrictions that consumer electronic equipment must be free by July 1, 2006 [10]. In Asia, the Japanese Ministry of Industry and Trade Institute (MITI) passed a new environmental legislation calling for a complete elimination of the use of lead by December 31, 2005. These laws kick started the implementation and characterization of different lead free alloy systems in consumer electronic industry. Another equally important issue in lead free development is the trend toward continuous increase in density of interconnects in electronic packages. This, in turn requires finer line circuitry solders with mechanical properties capable of withstanding the increasingly severe demands of miniaturization compared to the eutectic Pb-Sn solder.[11]

#### 2.1.1 Selection of a Lead free Solder

Hossain [8] has a great chapter in his dissertation that reviews the selection process of Lead free solder. The development and selection of any viable lead-free solder is based on different properties such as metallurgical bonding capability, wetting ability during reflow process and metallurgical interactions with bond pad material. Practical factors cover the availability of natural resources, manufacturability, toxicity and cost. Table 2.1 summarizes important properties that are necessary in solder alloy. Over the past decade there has been an increasing number of consensus for using one family of alloys, based on tin, silver and copper, at least for many surface mount and wafer level package applications. The large telecommunication industry is the one that has targeted this alloy. But the choice will still be largely product or applications dependant, when factors such as temperature, compatibility and/or cost may sway the choice towards other alloys. The following alloys are considered representative of viable candidates for replacing eutectic Sn/Pb system. Many of the systems are based on adding a small quantity of third or fourth element to binary alloy systems in order to lower the melting point and increase the wetting and reliability. It is reported that with increasing amount of additive elements, (a) melting point of system decreases, (b) bond strength is affected positively or negatively depending on the amount of element added, and (c) the wettability increases rapidly, reaches the maximum at a particular composition and then a decrease in bond strength may decrease. [13]

Table 2.1: Properties to look for in a new solder [12]

| Preferable Properties of solders from DFM           | Preferable properties of solder from solder |  |  |  |

|-----------------------------------------------------|---------------------------------------------|--|--|--|

| Transfersion reporting of column and an arrangement | fatigue                                     |  |  |  |

| Low Melting/ liquidus temperature                   | Electrical Conductivity                     |  |  |  |

| Good wettability to Copper/Aluminum                 | Good thermal Conductivity                   |  |  |  |

| Cost                                                | Coefficient of thermal expansion            |  |  |  |

| Environmental Friendliness                          | Shear Properties                            |  |  |  |

| Avaliability and no. of suppliers                   | Tensile properties                          |  |  |  |

| Manufacturability using current processes           | Creep Resistance                            |  |  |  |

| Ability to be made into balls                       | Fatigue properties                          |  |  |  |

| Copper pick up rate                                 | Corrosion and oxidation resistance          |  |  |  |

| Recyclability                                       | Intermetallic compound formation            |  |  |  |

| Ability to be made into paste                       |                                             |  |  |  |

## • Sn 96.5/Ag3.5:

Sn96.5/Ag3.5 (221oC) is considered as one of the most promising alloys and is well researched in the automobile and telecom industry. Indium Corp. reports this alloy to have poorest wetting for reflow solder among high Sn alloys [14].

# • Sn/Ag/Cu

Sn/Ag/Cu (SAC) is a ternary eutectic solder alloy system with melting point of around 217°C. Cu is added to the existing Sn-Ag system to get this system of alloys. There are a lot of alloys that are being used in the industry from this alloy system. Some of the early reports about this lab came from International Tin Research institute, Lucent, Ford and Sandia National Labs to have greater fatigue life than the eutectic Sn/Pb alloy. Brite-Euram reported 0.5% Sb addition may strengthen the alloy further. Hossain et.al [15] reported that adding gold increases the

strength considerably in tensile test. SAC alloy system is one of the most popular alloy systems in amongst the lead free alloy systems. Typically SAC 105, SAC 305 and SAC 405 alloys are very popular in consumer electronics, surface mount technology and also wafer level packaging industry. The intermetallics formed in soldering of SAC alloys are Cu<sub>6</sub>Sn<sub>5</sub> and Cu<sub>3</sub>Sn. These intermetallics are known to be brittle in structure.

## Sn/Ag/Cu/X

Sn96.2/Ag2.5/Cu0.8/Sb0.5 (213-218°C) is reported by International Tin research institute, Lucent, Ford and Sandia National Labs, to have a greater fatigue life as compared to eutectic Pb/Sn alloy. Brite-Euram project reported that 0.5%Sb addition the alloy further. Sn 97/Sb0.8/Ag0.2 (226oC-228oC, Kester, SAF-A-LLOY) is considered for wave and hand soldering application.

#### Sn/Cu/X

Sn99.3/Cu0.7 (227°C) is reported by Nortel to have soldering quality equal to eutectic Sn/Pb in telephone manufacturing. In air reflow the wettability reduced, fillet exhibits rough and textured apperance. Probably the "poorest" in mechanical properties available from all lead-free solders. Preferably this material is used for wave soldering because low material cost and also inserting of waves not costly. 99.3Sn/0.7Cu is one of the cheapest solders as no silver is present in the solder. This solder is not very complicated as only a binary system of intermetallics is present. It has a low environmental impact and hence does not complicate recycling. One of the major problems associated with this solder is it is difficult to use because for reflowing this solder temperatures as high as 300oC are required. The solder joints formed are dull and they have high incidence of bridging hence not suitable for manufacturing. [16,17]

## Sn/Ag/Cu + XAu

Park et.al [18] reported an increase in strength with the Golde (Au) addition of Sn-Ag-Cu near eutectic alloys. From the thermal and microstructural characterization of Sn-3.8Ag-0.7Cu

alloys containing various amounts of Au, it was found that the Au promotes the formation of a quaternary-eutectic reaction at  $204.5\% \pm 0.3\%$ .

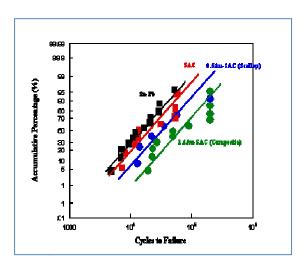

Kabade and Kim [19] performed four points cyclic bending of the Pb-Sn, SAC and SAC +1.5 Au alloys at 2Hz speed and 0.125" maximum deflection. Figure 8 shows that the SAC + Au solder is more reliable when compared to SAC and Pb-Sn solder. Addition of small weight percentage of Au into SAC, thus improved the four point bending reliability further. Lifetime comparison showed the trend:

## SnPb<SAC<1.5 Au-SAC

Figure 2.1: Four point bending reliability results of solders [18, 19]

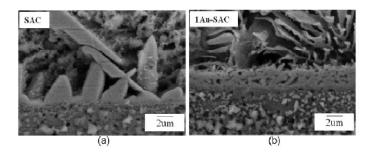

Addition of gold significantly affects the microstructure of solder as was described by Kim et al [8]. Fig 9 shows comparison of SAC solder Vs SAC solder with gold addition. These SEM were taken after the reflow process at 260°C for 3 min.

Figure 2.2: Comparison of SEM's for (a) SAC Solder and (b) SAC solder with gold addition [19,20]

Figure 2.2 (a) shows the solder joint with SAC alloy showing well-documented morphology of the  $Cu_6Sn_5$  interface microstructure, a consistent observation that the first phase formed at the Cu interface is  $Cu_6Sn_5$  when the Cu substrate is reacts with Sn bearing alloys. With further reaction a few  $Cu_6Sn_5$  grains preferentially grow to produce scallops. Figure 2 (b) depicts a completely different story. The interface microstructure of 1.0 Au-SAC and 2.0 Au-SAC alloys show completely different interface microstructures; interface phase,  $(Au_xCu_{1-x})_6Sn_5$  does not show the same scallop formation. Rather, the  $(AuCu)_6Sn_5$  shows grains with finely dispersed pores. Hossain et.al performed tensile testing of SnAgCu alloy with gold addition on a dog bone type of sample and reported that with addition of gold the tensile strength of gold increases by as much as 1.5 times.

Figure 2.3: Tensile stress-strain curves of SAC alloy with Gold addition [21]

# Sn/Ag/Cu/X

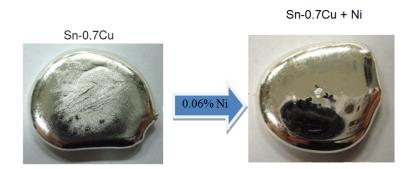

Addition of upto 0.05% Nickel (Ni) in the SAC solder completely changes the metallurgical structure of the alloy. Nickel is a well known diffusion barrier between Copper and Tin. Nickel atoms reduce the rate of reaction for the formation of  $Cu_6Sn_5$  and instead  $Ni_6Sn_5$  is formed which is much stronger intermetallic. Hence typically devices with SAC+Ni solders perform better in accelerated tests as compared to the regular SAC alloys.

Figure 2.4: Rheological changes that happen because of addition of Nickel to lead free alloy [76]

Thus additions of foreign materials in lead free solders can definitely help improving the properties of solders. However, a judicious of foreign material and the quantity to be is

necessary is necessary because excess addition can prove to be detrimental for reliability of the solder interconnects.

### 2.2 Constitutive properties of solder

Accurate prediction of fatigue life of solder bumps is important for safe and reliable operation of all electronic equipment. It takes a lot of time and can cost thousands of dollars to design and test a prototype using traditional methods, which in turn slows down the entire product development. The advantage of using software tools is that their post processing capabilities make it possible to visualize the stresses and strains that are imposed in the system due to testing conditions. Current commercial software provides a very powerful method for carrying out thermo-mechanical simulations. However it is important to understand the physics behind the software. In this section, constitutive properties of materials will be discussed. As this dissertation involves plasticity dominated failures and fatigue dominated failures we will be talking about both types of loading and material behavior in both the loadings.

### 2.2.1 Solder Constitutive behavior

Solder stress/strain behavior is traditionally divided into three parts: elastic strain, plastic time independent plastic strain and time depended creep strain. Solder is a ductile material and hence it plastically deforms and even creeps under the action of force. The force is temperature for accelerated thermal cycling. Creep is the slow deformation of a material under elastic stress (less than the yield stress) that results in a permanent change in shape, and even failure. Although creep can occur at any temperature, it is significant at temperatures exceeding about one half of the melting temperature of the solder alloy. A constitutive equation describes the stress strain relation in the materials involved in testing. Constitutive equation can be derived by testing solders under different loadings and different temperatures. The finite element method analysis requires a valid constitutive (stress, strain and strain rate) equations

and damage criteria. Based on the stress strain relation of a solder joint determined from the constitutive equation by finite element simulation, a FEM model is constructed to find out the maximum stresses induced in case of a plasticity dominated failure or to predict the fatigue life in case of a fatigue dominated failure. The stress strain behavior for engineering materials is complicated and depends generally on temperature, strain and strain rate [8]. The total strain induced in solder is typically is the sum of three portions

$$\mathcal{E}_{tot} = \mathcal{E}_{el} + \mathcal{E}_{nl} + \mathcal{E}_{cr}$$

2.1

In the next section details of elastic, plastic and creep strains are discussed in one dimensional term. As described in equation (total strain) the strain induced in the solder can be divided into elastic strain, plastic strain and creep strain. Stress induced in a material is material's response of the applied strain. The same equation in terms of different stresses can be expressed as

2.2

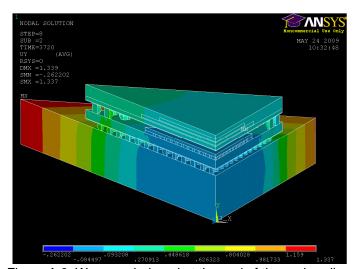

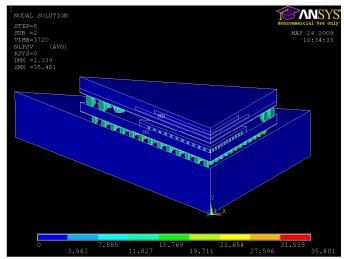

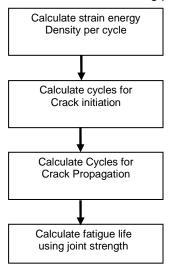

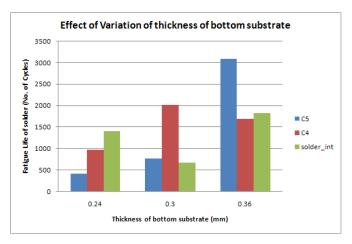

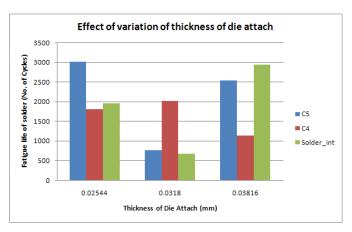

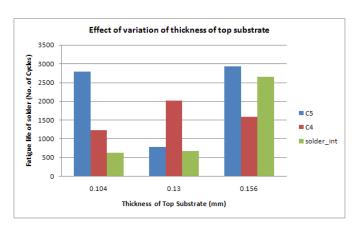

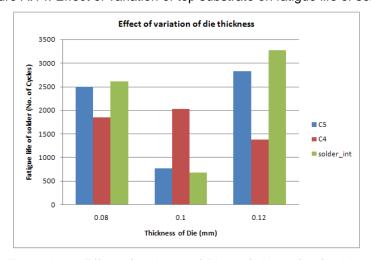

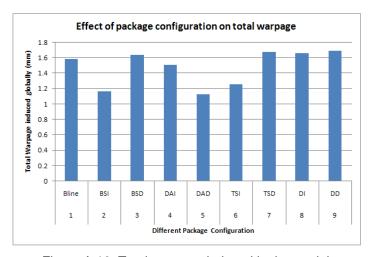

$$\varepsilon_{total}(t) = \frac{\sigma}{E(T)} + \left[\frac{\sigma}{K(T)}\right]^{\frac{1}{n_p(T)}} + tA(\sigma)^{\frac{1}{n_c}} e^{\frac{-Q}{RT}}$$