## ISSUES IN FRONT-END ENGINEERING OF CMOS NANOELECTRONICS

by

## XIAOLONG YANG

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT ARLINGTON

MAY 2007

Copyright © by Xiaolong Yang 2007

All Rights Reserved

#### **ACKNOWLEDGEMENTS**

I would like to offer my sincere gratitude and thanks to Dr. Meng Tao for his guidance, instruction, and thorough advising on my research work. I also present my acknowledgement for offering me the opportunity to work under him. I would also like to thank Dr. Alan Davis, Dr. Weidong Zhou, Dr. Nikolai Stelmakh, and Dr. Qiming Zhang for agreeing to be committee members. I would also like to acknowledge Eduardo Maldonado for his efforts to help us carry out selenium passivation on our wafers and Dr. Nasir Basit for his help in the cleanroom. I would also like to acknowledge and thank all other previous and current group members including Jinggang Zhu, Longcheng Wang, Guanghua Song, Yusuf Ali, and Kunhee Han.

I would like to acknowledge and thank Petroleum Research Fund, Semiconductor Research Corporation, and National Science Foundation for partial support, and NanoFAB Center and Department of Electrical Engineering at the University of Texas at Arlington for the financial and technical support that made this research possible.

I would also like to thank my co-researchers for their support and instrumental guidance. Last but not the least I would like to acknowledge my parents and Yamin Wu who have always supported me through thick and thin.

February 9, 2007

#### **ABSTRACT**

#### ISSUES IN FRONT-END ENGINEERING OF CMOS NANOELECTRONICS

Publication No. \_\_\_\_\_

### Xiaolong Yang, PHD

The University of Texas at Arlington, 2007

Supervising Professor: Meng Tao

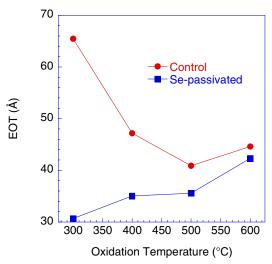

Several issues exist in current CMOS front-end engineering such as interfacial layer formation at high-k/Si interface, high metal/Si contact resistance in source and drain regions, and absence of a quantitative model for silicon-germanium alloy growth. In this dissertation, monolayer Se passivation is employed to create a Si (100) surface free of dangling bonds. Since dangling bonds are the origins of surface reaction sites and surface states, interfacial layer formation at high-k/Si interface can be suppressed and metal/Si contact resistance can be lowered by Se passivation. Firstly, results on interface engineering between HfO<sub>2</sub> and n-type Si (100) with Se passivation are reported. HfO<sub>2</sub> on Se-passivated sample by dry oxidation at 300°C shows much improved properties: a smaller *EOT* (equivalent oxide thickness) 31 Å compared with

EOT 65 Å for control sample, and a smaller leakage current with about 2 order of magnitude lowering. These results indicate Se passivation can effectively suppress the interfacial layer formation at the HfO<sub>2</sub>/Si interface and reduce the gate leakage current. Secondly, experimental results for Ti/n-type Se-passivated Si (100) contacts are presented. The sheet resistance of Se-passivated 10<sup>19</sup> cm<sup>-3</sup> doped n-type Si (100) shows a 30% reduction as compared with control (non-passivated) samples. The extracted contact resistance decreases by about one order of magnitude. Up to 29 times reduction in contact resistivity is achieved by Se passivation on heavily-doped n-type SOI substrates. Finally, a kinetic model is proposed for Si<sub>1-x</sub>Ge<sub>x</sub> growth from SiH<sub>4</sub> and GeH<sub>4</sub> by chemical vapor deposition (CVD). Growth behaviors like growth rate and Ge content are discussed by considering both the heterogeneous and homogenous reactions. The model agrees well with the experimental data.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                   | iii |

|--------------------------------------------------------------------|-----|

| ABSTRACT                                                           | iv  |

| LIST OF ILLUSTRATIONS                                              | X   |

| LIST OF TABLES                                                     | xiv |

| Chapter                                                            |     |

| 1. INTRODUCTION                                                    | 1   |

| 2. CHALLENGES IN TRANSISTOR FEATURE SIZE DOWN SCALING              | 6   |

| 2.1 High Gate Leakage Current                                      | 7   |

| 2.1.1 Limitations of SiO <sub>2</sub> as the Gate Dielectric Layer | 7   |

| 2.1.2 High- <i>k</i> Materials as the Gate Dielectric Layer        | 9   |

| 2.1.3 High- <i>k</i> Gate Material Property Considerations         | 11  |

| 2.1.4 Current Status with High-k Materials                         | 16  |

| 2.2 High Source/Drain Metal/Si Parasitic Resistance                | 18  |

| 2.2.1 Silicide, Junction Extension and Overlap Resistance          | 19  |

| 2.2.2 Contact Resistance                                           | 20  |

| 2.2.3 Schottky Barrier Height                                      | 23  |

| 2.3 Channel Mobility Degradation                                   | 26  |

| 2.3.1 Strained Silicon                                             | 26  |

| 2.3.2 SiGe Alloy Growth Behavior                                                 | 27 |

|----------------------------------------------------------------------------------|----|

| 2.3.3 Previous Models for SiGe Growth                                            | 29 |

| 3. SURFACE PASSIVATION OF SILICON (100) BY MONOLAYER SELENIUM                    | 30 |

| 3.1 Si (100) Surface Structure in Vacuum                                         | 30 |

| 3.2 Si (100) Surface Structure with Se Passivation                               | 31 |

| 3.3 Se passivation on Si (100) surface by molecular beam epitaxy                 | 33 |

| 4. HAFNIUM DIOXIDE ON N-TYPE SILICON (100) WITH SELENIUM PASSIVATION             | 35 |

| 4.1 Experiments                                                                  | 35 |

| 4.1.1 Wafer Preparation                                                          | 35 |

| 4.1.2 Se Passivation                                                             | 35 |

| 4.1.3 HfO <sub>2</sub> Growth                                                    | 36 |

| 4.1.4 Post-Deposition Annealing                                                  | 37 |

| 4.1.5 Photolithography                                                           | 37 |

| 4.1.6 Metal Deposition                                                           | 37 |

| 4.2 Characterization                                                             | 38 |

| 4.3 Results and Discussion                                                       | 40 |

| 4.3.1 HfO <sub>2</sub> by Reactive Sputtering                                    | 40 |

| 4.3.2 HfO <sub>2</sub> by O <sub>3</sub> Oxidation                               | 42 |

| 4.3.3 HfO <sub>2</sub> by Dry Oxidation                                          | 46 |

| 4.4 Summary                                                                      | 50 |

| 5. LOW RESISTANCE TITANIUM/N-TYPE SILICON (100) CONTACTS BY SELENIUM PASSIVATION | 52 |

| 5.1 Experiments                                                             | 52 |

|-----------------------------------------------------------------------------|----|

| 5.1.1 Wafer Preparation                                                     | 52 |

| 5.1.2 Se Passivation                                                        | 52 |

| 5.1.3 Photolithography                                                      | 53 |

| 5.1.4 Metal Deposition                                                      | 53 |

| 5.1.5 Post-Deposition Annealing                                             | 53 |

| 5.2 Characterization                                                        | 54 |

| 5.2.1 Current-Voltage Characterization                                      | 54 |

| 5.2.2 Four-Point Probe Method                                               | 55 |

| 5.2.3 Circular Transmission Line Method                                     | 56 |

| 5.3 Results and Discussion                                                  | 57 |

| 5.3.1 I-V Characterization                                                  | 57 |

| 5.3.2 Sheet Resistance and Contact Resistance                               | 60 |

| 5.3.3 Contact Resistivity                                                   | 64 |

| 5.4 Summary                                                                 | 66 |

| 6. KINETIC MODEL FOR SILICON-GERMANIUM GROWTH FROM SILANE ANDGERMANE BY CVD | 67 |

| 6.1 Process Principles and Deposition Mechanism                             | 67 |

| 6.2 Kinetics                                                                | 68 |

| 6.2.1 Heterogeneous Decomposition                                           | 68 |

| 6.2.2 Surface H Coverage                                                    | 71 |

| 6.2.3 Homogeneous Decomposition                                             | 72 |

| 6.3 Growth Rate                                                             | 73 |

| 6.3.1 Growth Rate in Heterogeneous Regime                                                                                | 75 |

|--------------------------------------------------------------------------------------------------------------------------|----|

| 6.3.2 Growth Rate in Homogeneous Regime                                                                                  | 77 |

| 6.3.3 Conditions for Homogeneous Decomposition                                                                           | 80 |

| 6.4 Germanium Content                                                                                                    | 81 |

| 6.5 Summary                                                                                                              | 85 |

| 7. CONCLUSIONS AND FUTURE SCOPES                                                                                         | 87 |

| 7.1 Conclusions                                                                                                          | 87 |

| 7.2 Future Scopes                                                                                                        | 90 |

| 7.2.1 HfO <sub>2</sub> on Se-passivated Si (100)                                                                         | 90 |

| 7.2.2 Low resistance Ti/n-Si (100) by Se passivation                                                                     | 90 |

| 7.2.3 Kinetic model for Si <sub>1-x</sub> Ge <sub>x</sub> alloy growth from SiH <sub>4</sub> and GeH <sub>4</sub> by CVD | 90 |

| REFERENCES                                                                                                               | 92 |

| BIOGRAPHICAL INFORMATION                                                                                                 | 99 |

# LIST OF ILLUSTRATIONS

| Figure |                                                                                                                                   | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------|------|

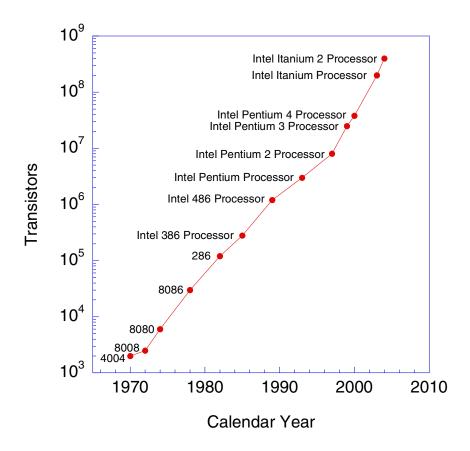

| 1.1    | Projections of transistors per chip by Moore's Law                                                                                | 2    |

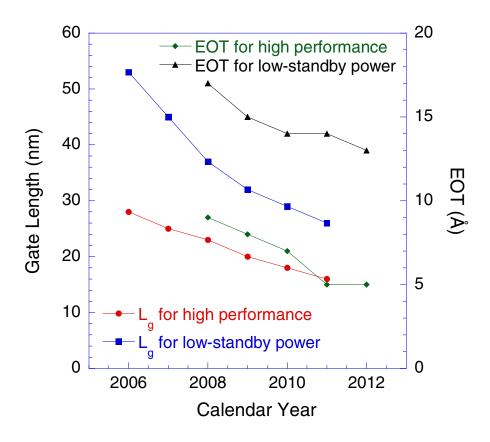

| 1.2    | 2005 ITRS projections of physical gate length and <i>EOT</i> for both high performance logic and low-standby power devices        | 5    |

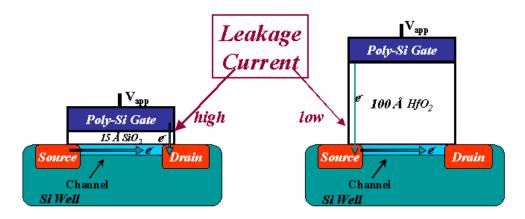

| 2.1    | Leakage current reduced by replacing SiO <sub>2</sub> with a high- <i>k</i> dielectric as the gate material                       | 9    |

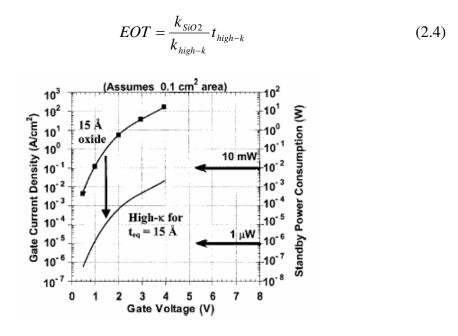

| 2.2    | Comparisons of device power consumption and leakage current between 15 Å SiO <sub>2</sub> gate and 15 Å EOT HfO <sub>2</sub> gate | 10   |

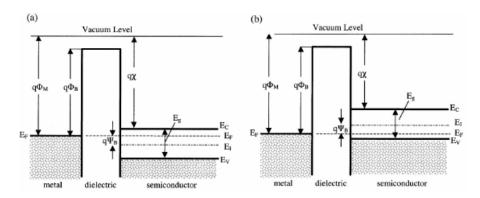

| 2.3    | Energy band diagrams for ideal MOS capacitors for (a) n-type and (b) p-type semiconductor structure                               | 11   |

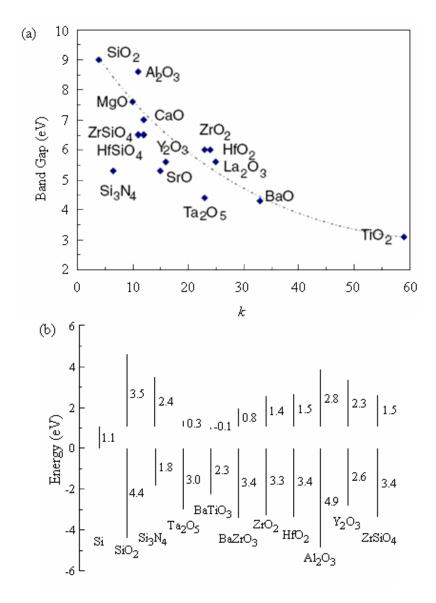

| 2.4    | (a) Dielectric material band gaps as a function of the dielectric constant values; (b) Dielectric material band offset with Si    | 13   |

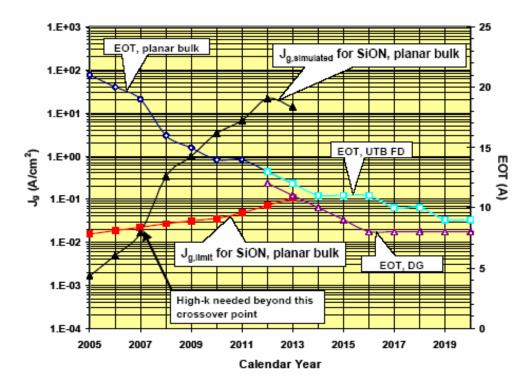

| 2.5    | Leakage current limitation of SiON as gate dielectric for low standby power by ITRS 2005                                          | 15   |

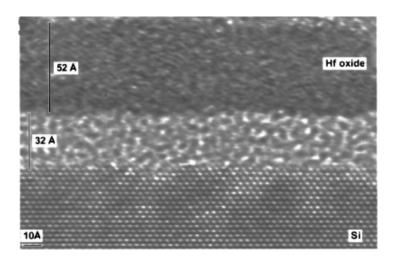

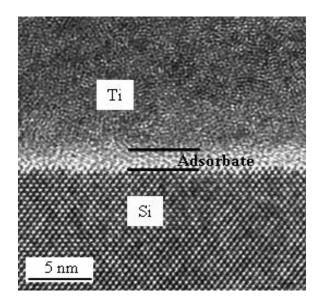

| 2.6    | HRTEM image of interfacial layer between HfO <sub>2</sub> and Si substrate                                                        | 17   |

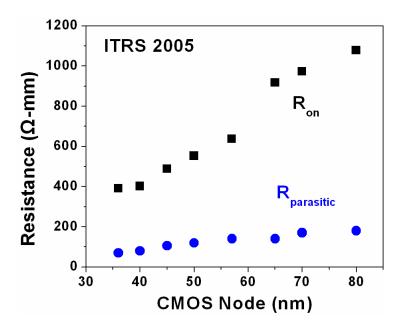

| 2.7    | Projections by ITRS 2005 for the channel 'on' resistance and parasitic resistance of high performance devices                     | 18   |

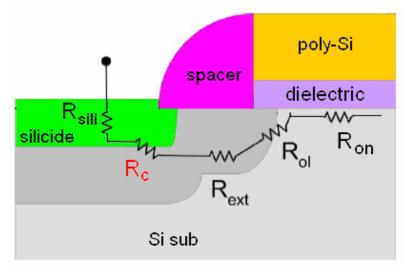

| 2.8    | MOSFET parasitic resistances which cause device performance loss                                                                  | 19   |

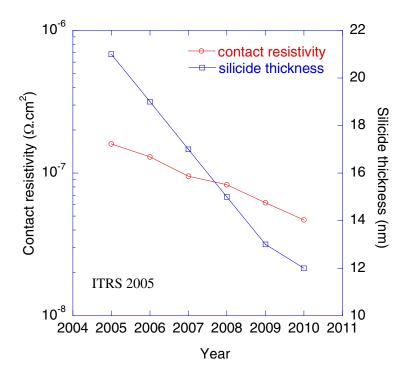

| 2.9    | ITRS 2005 projections for contact resistivity and silicide thickness                                                              | 20   |

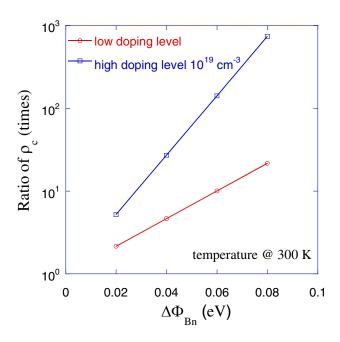

| 2.10   | Improvement of contact resistivity by lowering the Schottky barrier height for electrons                                          | 22   |

| 2.11   | Ideal metal/Si contact energy band diagram for (a) n-type and (b) p-type                                                          | 23   |

| 2.12   | Metal/Si contact energy band diagram with surface states for  (a) n-type (b) p-type                                               | 24   |

| 2.13 | Mobility versus scaling trend for Intel process technology                                                                                                                                                           | 25 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.14 | Illustration of structure for strained Si                                                                                                                                                                            | 27 |

| 3.1  | Atomic structure of the clean Si (100) surface in ultrahigh vacuum                                                                                                                                                   | 31 |

| 3.2  | Atomic structure of the Se-passivated Si (100) surface                                                                                                                                                               | 32 |

| 3.3  | (a) RHEED image of bare Si (100) with 2×1 surface structure and (b) RHEED image of Se-passivated Si (100) with 1×1 surface structure                                                                                 | 34 |

| 4.1  | Fabrication processes of the experiments: (a) wafer preparation; (b) Se monolayer passivation; (c) HfO <sub>2</sub> growth; (d) Photolithography, Al deposition for front contact and Ti deposition for back contact | 38 |

| 4.2  | C-V characterizations of control and Se-passivated samples by reactive sputtering at different annealing temperatures                                                                                                | 40 |

| 4.3  | I-V characterizations of control and Se-passivated samples by reactive sputtering at different annealing temperatures                                                                                                | 41 |

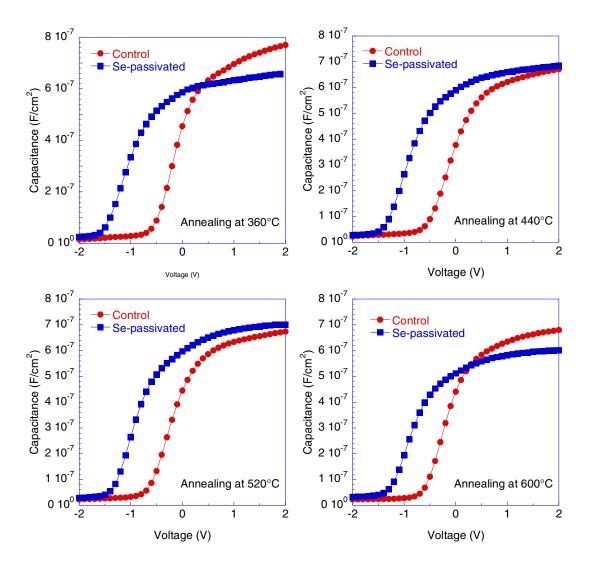

| 4.4  | C-V characterizations of control and Se-passivated samples by O <sub>3</sub> oxidation at different annealing temperatures                                                                                           | 42 |

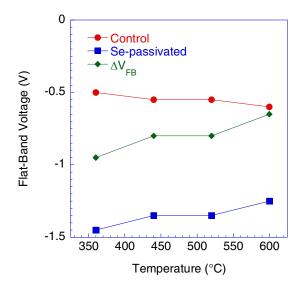

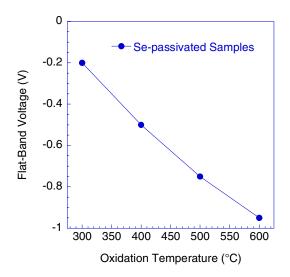

| 4.5  | Flat-band voltages as a function of oxidation temperature for control and Se-passivated samples oxidized in $O_3$                                                                                                    | 43 |

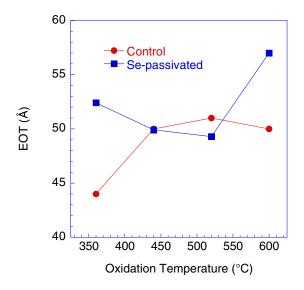

| 4.6  | $EOT$ as a function of oxidation temperature for control and Se-passivated samples oxidized in $O_3$                                                                                                                 | 44 |

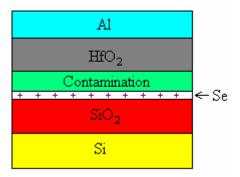

| 4.7  | Illustration of the Se monolayer sandwiched in the dielectric stack after O <sub>3</sub> oxidation                                                                                                                   | 45 |

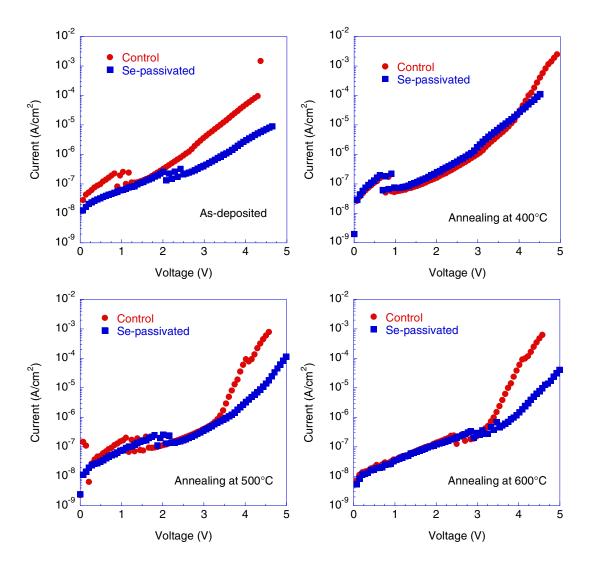

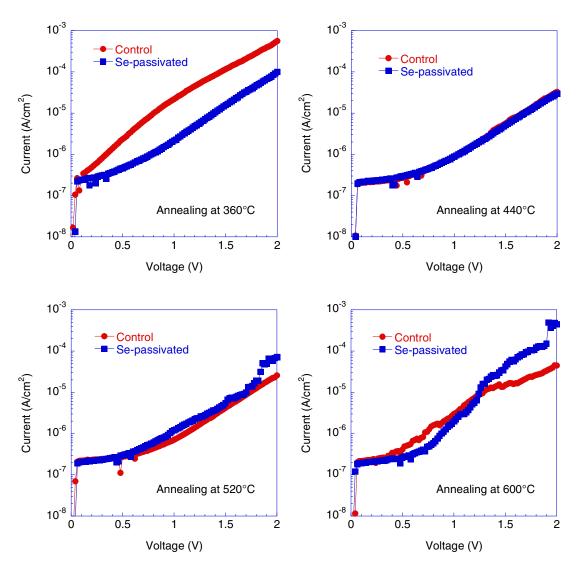

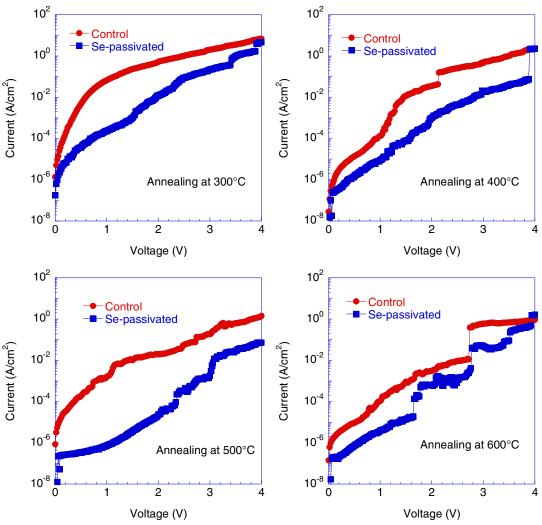

| 4.8  | I-V characterizations of control and Se-passivated samples by O <sub>3</sub> oxidation at different annealing temperatures                                                                                           | 46 |

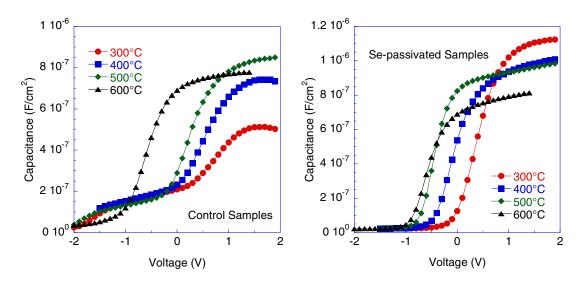

| 4.9  | C-V characterizations of control and Se-passivated samples by dry oxidation at different temperatures                                                                                                                | 47 |

| 4.10 | EOT as a function of oxidation temperature for control and Se-passivated samples by dry oxidation                                                                                                                    | 48 |

| 4.11 | Flat-band voltage as a function of oxidation temperature for                                                                                                                                                         |    |

|      | Se-passivated samples by dry oxidation                                                                                                                                                                       | 49 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.12 | I-V characterizations of control and Se-passivated samples by dry oxidation at different temperatures                                                                                                        | 50 |

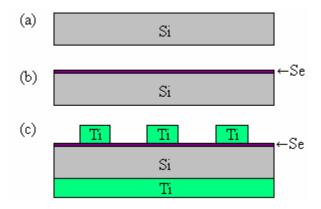

| 5.1  | Fabrication processes of the experiments: (a) wafer preparation; (b) Se monolayer passivation; (c) Photolithography, Ti deposition for front contact and back contact followed by thermal annealing          | 53 |

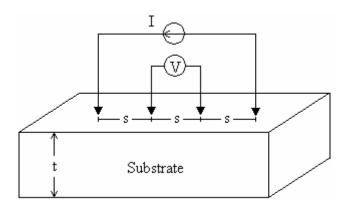

| 5.2  | Sheet resistance measurements by four-point probe method                                                                                                                                                     | 54 |

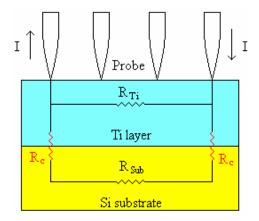

| 5.3  | Current paths for Ti/Si two layer structures in $R_s$ measurements                                                                                                                                           | 55 |

| 5.4  | Structure of circular transmission line method for contact resistivity measurements                                                                                                                          | 56 |

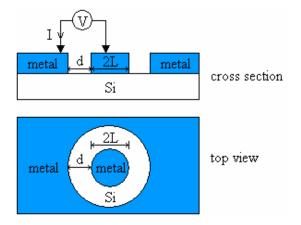

| 5.5  | I-V characteristics for the Se-passivated and control samples with low 10 <sup>15</sup> cm <sup>-3</sup> n-type doping Si (100) at (a) room temperature and (b) low temperature                              | 59 |

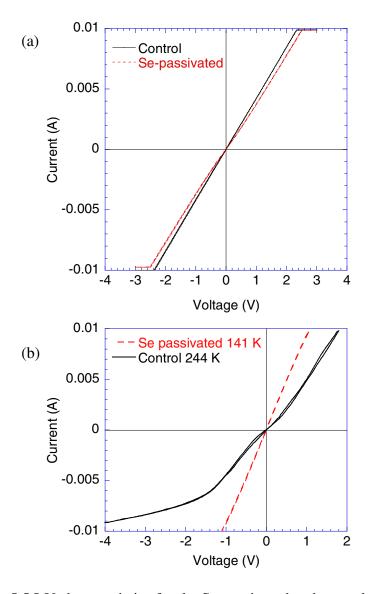

| 5.6  | Sheet resistance as a function of annealing temperature for 100 Å Ti on Se-passivated and control n-type Si (100) samples                                                                                    | 60 |

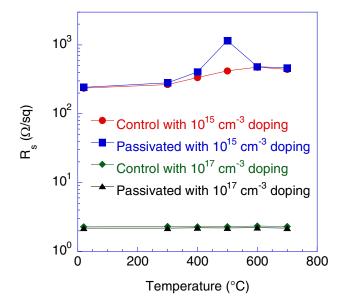

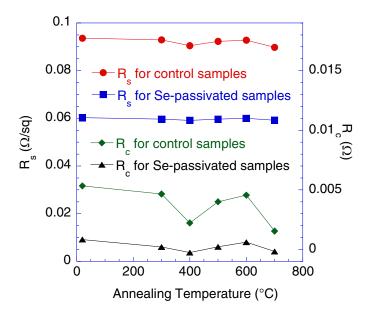

| 5.7  | Comparison of sheet resistance and contact resistance as a function of annealing temperature for 100 Å Ti on Se-passivated and control n-type Si (100) samples with 10 <sup>19</sup> cm <sup>-3</sup> doping | 62 |

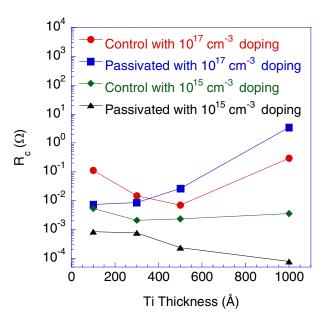

| 5.8  | Comparison of contact resistance as a function of n-type Si (100), substrate doping level and Ti layer thickness for Se-passivated and control samples                                                       | 63 |

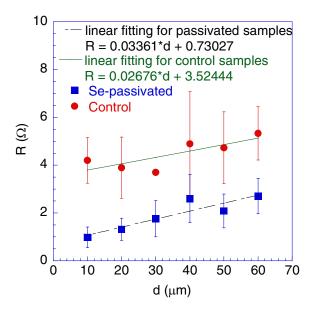

| 5.9  | Linear fittings of the experimental data from the circular transmission line measurements of Se-passivated and control samples with 500 Å Si buffer layer and 500 Å Ti layer                                 | 64 |

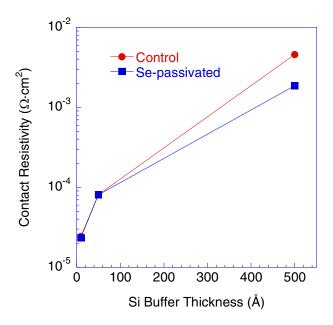

| 5.10 | Comparison of specific contact resistance as a function of Si buffer layer thickness for Se-passivated and control samples with 500 Å Ti at bottom and 1500 Å Al on top                                      | 65 |

| 5.11 | HRTEM image of surface adsorption layer between Ti and Si substrate                                                                                                                                          | 66 |

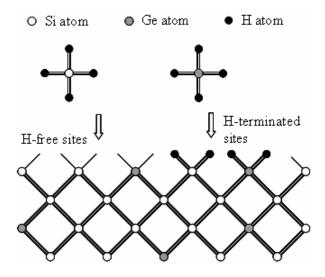

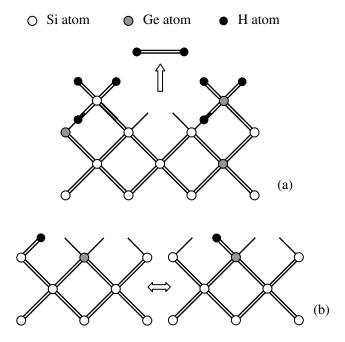

| 6.1. | Heterogeneous reactions in Si <sub>1</sub> "Ge" CVD from SiH <sub>4</sub> and GeH <sub>4</sub>                                                                                                               | 69 |

| 6.2.  | (a) H desorption from surface sites and (b) H diffusion between  Ge and Si sites                                                                                                                                                                                                                                     | 71 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

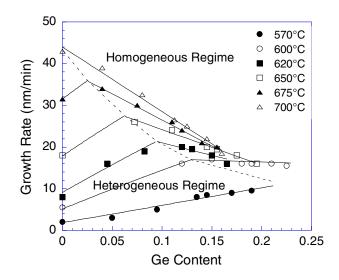

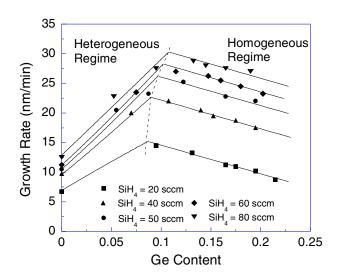

| 6.3.  | Growth rate as a function of Ge content at different temperatures. Solid lines are model predictions and experimental data from Ref. 65. SiH <sub>4</sub> flow rate is 40 sccm. The dash line is the boundary between homogeneous and heterogeneous regimes                                                          | 74 |

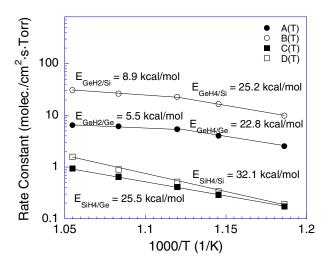

| 6.4.  | Arrhenius plot for rate constants used in Eq. (6.6). Activation energies for different heterogeneous unimolecular reactions on the surface sites are extracted                                                                                                                                                       | 77 |

| 6.5.  | Growth rate as a function of Ge content at different SiH <sub>4</sub> flow rate. Deposition temperature is 620°C. Solid lines are model predictions and experimental data from Ref. 65. The dash line is the boundary between homogeneous and heterogeneous regimes                                                  | 79 |

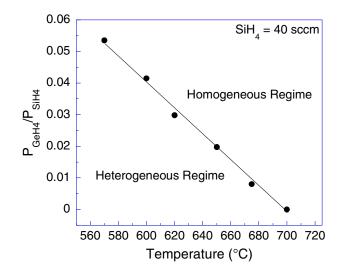

| 6.6.  | Boundary between heterogeneous and homogeneous regimes as experimentally defined in Figure 6.3 by $P_{\text{GeH4}}/P_{\text{SiH4}}$ ratio and temperature                                                                                                                                                            | 80 |

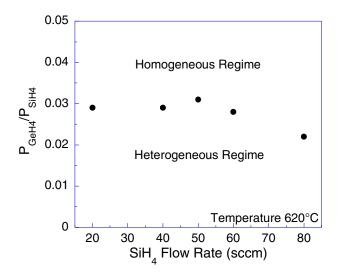

| 6.7.  | Boundary between heterogeneous and homogeneous regimes as experimentally defined in Figure 6.5 by $P_{\text{GeH4}}/P_{\text{SiH4}}$ ratio and SiH <sub>4</sub> flow rate                                                                                                                                             | 81 |

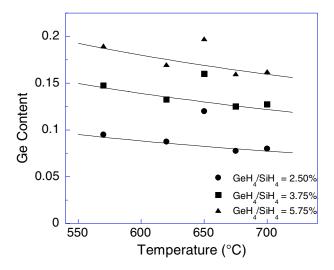

| 6.8.  | Ge content as a function of temperature at different GeH <sub>4</sub> /SiH <sub>4</sub> ratio. SiH <sub>4</sub> flow rate is 40 sccm. Solid lines are model predictions and experimental data from Ref. 65                                                                                                           | 82 |

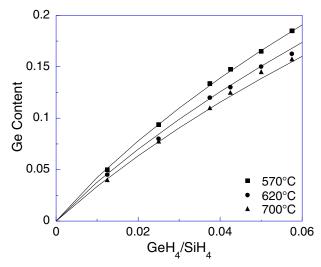

| 6.9.  | Ge content as a function of GeH <sub>4</sub> /SiH <sub>4</sub> ratio at different temperatures. SiH <sub>4</sub> flow rate is 40 sccm. Solid lines are model predictions and experimental data from Ref. 65. The m values extracted from Eq. (6.8) are 3.38 at 570°C, 3.12 at 620°C and 2.91 at 700°C for comparison | 84 |

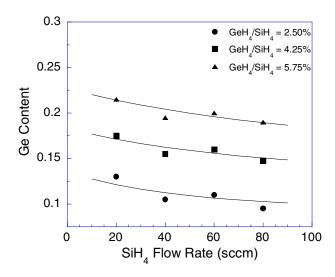

| 6.10. | Ge content as a function of SiH <sub>4</sub> flow rate at different GeH <sub>4</sub> /SiH <sub>4</sub> ratios. Deposition temperature is 620°C. Solid lines are model predictions and experimental data from Ref. 65                                                                                                 | 85 |

## LIST OF TABLES

| Table |                                                                                                                         | Page |

|-------|-------------------------------------------------------------------------------------------------------------------------|------|

| 3.1   | Covalent and atomic radius of Si and group VI elements                                                                  | 33   |

| 3.2   | Structural parameters of bulk phases of S and Se and of the ideal and restored Si (100) surfaces                        | 33   |

| 6.1   | Most likely heterogeneous reactions in Si <sub>1-x</sub> Ge <sub>x</sub> CVD from GeH <sub>4</sub> and SiH <sub>4</sub> | 69   |

| 6.2   | Primary Ge and Si fluxes in Si <sub>1-x</sub> Ge <sub>x</sub> CVD from GeH <sub>4</sub> and SiH <sub>4</sub>            | 70   |

| 6.3   | Fitting parameters used in Eq. (6.4) and thus Eq. (6.6) for Figure 6.3                                                  | 76   |

| 6.4   | Activation energy for GeH <sub>4</sub> and GeH <sub>2</sub> adsorption                                                  | 79   |

| 6.5   | Fitting parameters used in Eq. (6.4) and thus Eq. (6.6) for Figure 6.5                                                  | 80   |

#### CHAPTER 1

#### INTRODUCTION

Since the first transistor devised by John Bardeen<sup>1</sup> in 1947 and the first integrated circuit invented by Jack Kilby<sup>2</sup> in 1958, the rapid development of computer and communications technology has catapulted electronics to its current status as the dominant global industry. Exploitation of electron and hole conduction in silicon has resulted in electronic memory and logic circuits such as dynamic random access memory (DRAM) and the microprocessor. Especially during the last 20 years, there has been rapid progress in the complementary metal-oxide-semiconductor (CMOS) integrated circuit technology. This has pushed the IC industry to its highly-developed age. The demand for greater integrated circuit functionality and performance (such as high speed and low static power consumption) at lower cost requires an increased circuit density, which has translated into a higher density of transistors on a wafer. This integration trend had been successfully projected by Gordon Moore<sup>3,4</sup> in 1965 that the growth of the number of transistors per chip quadruples every two years, subsequently modifying to about three-to-four years in 1995 which is well recognized as Moore's Law and is shown in Figure 1.1. In early 2006, Intel groups published their test static random access memory (SRAM) chips using a 45 nm process with an integrated density of over 1×10<sup>9</sup> transistors/chip. Compared with previous 65 nm process technology, this process technology offers more than 20% enhancement in transistor switching speed or more than a five-fold reduction in transistor current leakage, and more than 30% reduction in transistor switching power, which show the latest but not final improvement of the transistor performances.

Figure 1.1 Projections of transistors per chip by Moore's Law.

The high transistor integrated density towards high circuit functionality and performance is accomplished by reducing the feature size of the active device in the circuit (called down-scaling),<sup>5-7</sup> which can be clearly seen by the performance metrics shown below. For a CMOS circuit, the dynamic response, or the switching response time, is given by<sup>8</sup>

$$\tau = \frac{C_L V_{DD}}{I_D} \tag{1.1}$$

where  $C_L$  is the load capacitance,  $V_{DD}$  is the supply voltage,  $I_D$  is the drive current. The switching response time gives the delay for the signal transportation from the upper logic level to the lower logic level. Eq. (1.1) indicates that to reduce the switching response time, the drive current should be increased. By considering a simple model for the drive current associated with a MOSFET, in the ohmic region, the drive current  $I_D$  can be written as<sup>8</sup>

$$I_{D} = \frac{W}{L} \mu C_{gate} (V_{GS} - V_{T} - \frac{V_{DS}}{2}) V_{DS}$$

(1.2)

where W and L are the width and length of the transistor channel, respectively,  $\mu$  is the channel carrier mobility,  $C_{gate}$  is the gate capacitance,  $V_{GS}$  and  $V_{DS}$  are the voltage applied on gate and drain, and  $V_T$  is the threshold voltage. Eq. (1.2) shows the drain current is proportional to the average charge across the channel and the average electric field  $(V_{DS}/L)$  along the channel direction. Initially,  $I_D$  increases linearly with  $V_{DS}$  and then eventually saturates to a maximum when  $V_{Dsat} = V_{GS} - V_T$  to yield

$$I_{Dsat} = \frac{W}{2L} \mu C_{gate} (V_G - V_T)^2$$

(1.3)

By considering the gate dielectric as a parallel plate capacitor, the gate capacitance is given as

$$C_{gate} = A \frac{\varepsilon_0 k}{t} \tag{1.4}$$

where A is the capacitor area, k is the gate oxide relative dielectric constant,  $\varepsilon_0$  is the

free space permittivity and t is the gate dielectric thickness. Eq. (1.3) and Eq. (1.4) indicate that drive current can be increased by either reducing the channel length or increasing the gate capacitance by reducing the thickness of the gate dielectric, which is recognized as down-scaling. The conventional SiO<sub>2</sub> gate dielectric thickness has proceeded from the range of 75~100 nm for the 4K DRAM in 1974 to 1.1 nm for today's leadership MPU in 2005. Likewise, the physical gate length has decreased from 7.5 $\mu$ m for the 4K DRAM to a physical gate length of about 35 nm for the MPU at the 90 nm technology generation. Figure 1.2 shows the projections by ITRS 2005<sup>9</sup> (International Technology Roadmap for Semiconductor) of physical gate length and gate equivalent oxide thickness (*EOT*) for both high-performance and low standby-power devices, which gives the tendency for the future CMOS transistor generations. It indicates that CMOS technology has already stepped into the nanometer era.

However, in the past several years it has become clear that despite advances in these crucial process technologies and the resultant ability to produce ever-smaller feature sizes, front-end process technologies have not kept pace, and scaled device performance has been compromised. The rapid shrinkage of the feature size has forced the CMOS industry to face several problems in the traditional transistors such as high gate leakage current, high source/drain parasitic resistances and channel mobility degradation, etc. The crux of these problems comes from the fundamental materials used in traditional transistors. Silicon, silicon dioxide and silicide, have been pushed to their fundamental material limits and continued scaling requires the introduction of new

materials.

Figure 1.2 2005 ITRS projections of physical gate length and *EOT* for both high performance logic and low-standby power devices. 9

In summary, an introduction is given in Chapter 1. Three issues in current CMOS front-end engineering are addressed in Chapter 2. Chapter 3 presents the surface passivation on Si (100) surface by monolayer Se atoms. Chapter 4 gives the experiments and results of HfO<sub>2</sub> on Se-passivated n-type Si (100). Chapter 5 shows the experiments and results of low resistance Ti/n-type Si (100) contacts by Se passivation. In Chapter 6, a kinetic model for Si<sub>1-x</sub>Ge<sub>x</sub> growth from SiH<sub>4</sub> and GeH<sub>4</sub> by CVD is proposed. Conclusion and future scopes are given in Chapter 7.

#### CHAPTER 2

#### CHALLENGES IN TRANSISTOR FEATURE SIZE DOWN SCALING

Several issues associated with the transistor feature size down scaling exist within current CMOS front-end technology, such as high gate leakage current due to the thin gate SiO<sub>2</sub> film, high source/drain parasitic resistance with smaller transistor dimension, and electron/hole mobility degradation at the surface of the channel, which have already restricted the extension and development of IC industry to even greater functionality and higher performance. High dielectric constant (high-k) materials have been investigated to replace SiO<sub>2</sub> as the gate material. However, continued research is needed before using them as the gate materials. A significant part of the source/drain parasitic resistances is the metal/Si contact resistance. This emerges as the dominant component with the transistor feature size down scaling. Research works and techniques towards lowering the metal/Si contact resistance must be studied and developed to meet the future requirement on source/drain parasitic resistance. Strained-Si technology has been successfully applied to current CMOS technology to enhance the transistor surface channel mobility. Since the Ge content in the strained-Si plays a key role to determine the mobility enhancement, a quantitative and comprehensive kinetic model for SiGe alloy (Strained-Si) growth is needed.

## 2.1 High Gate Leakage Current

The key element enabling the scaling of Si-based metal-oxide-semiconductor field effect transistor (MOSFET) is the gate dielectric material used to isolate the transistor gate from the Si channel in CMOS devices for decades: silicon dioxide (SiO<sub>2</sub>). The amorphous silicon dioxide is the most commonly used material as the gate dielectric since it offers several key advantages such as large band gap ( $E_g \sim 8.9 \text{ eV}$ ), large band offsets with Si ( $\Delta E_c = 3.1 \text{ eV}$ ,  $\Delta E_v = 4.6 \text{ eV}$ ), high hard breakdown fields of 15 MV/cm, low surface states density at the Si/SiO<sub>2</sub> interface ( $D_{it} \sim 1-3\times10^{10}/\text{eV}\cdot\text{cm}^2$ ), good thermal stability and well-established fabrication processes. However, with the increase in transistor integration density and resultant decrease in transistor feature size, SiO<sub>2</sub> has already been pushed to its fundamental limitations as the gate dielectric.

## 2.1.1 Limitations of SiO<sub>2</sub> as the Gate Dielectric Layer

With the down scaling of the feature size, the thickness of the gate SiO<sub>2</sub> turns much thinner than before. As shown in Figure 1.2, the required gate dielectric thickness has already reached below 12 Å with SiO<sub>2</sub> as the gate material. Previous works<sup>10-12</sup> indicate that the CMOS devices with SiO<sub>2</sub> gate oxide thinner than 10~12 Å result in no gains in transistor drive current. Therefore, 10~12 Å could serve as a practical limit for reducing the SiO<sub>2</sub> thickness.<sup>13, 14</sup> Besides, there are two main issues that remain with such a thin SiO<sub>2</sub> film. Firstly, the gate leakage current will increase dramatically due to direct tunneling through the thin SiO<sub>2</sub> film. This is shown below <sup>15</sup>

$$J_{DT} = \frac{A}{t_{gate}^2} \exp\left(-2t_{gate} \sqrt{\frac{2m*q}{\hbar^2} (\Phi_B - \frac{V}{2})}\right)$$

(2.1)

where A is a constant,  $t_{\text{gate}}$  is the gate physical thickness,  $m^*$  is the electron effective mass in SiO<sub>2</sub>,  $\hbar$  is the Planck constant,  $\Phi_B$  is the barrier height, and V is the voltage drop across SiO<sub>2</sub>. Eq. (2.1) indicates that thin SiO<sub>2</sub> will promote the increase of the gate leakage current, and sequentially increase the static power consumption. This undesired gate leakage current degrades the device reliability since the IC design rules generally assume no appreciable gate current. Secondly, the traditional CMOS transistor usually uses poly-Si with boron highly-doped as the gate electrode. Thin SiO<sub>2</sub> will enhance boron diffusion from the poly-Si gate electrode into the surface of Si substrate (called boron penetration) during thermal annealing in the fabrication process. This will result in a higher concentration of boron in the channel region, which changes the channel doping level and causes instability in the threshold voltage since the threshold voltage,  $V_{th}$ , is a function of channel doping concentration, which is shown below  $V_{th}$

$$V_{th} = V_{FB} + 2\psi_B + \frac{1}{C_{eate}} \sqrt{4\varepsilon_s q N_A \psi_B} \quad \text{for p-type substrate}$$

(2.2a)

$$V_{th} = V_{FB} - 2\psi_B - \frac{1}{C_{gate}} \sqrt{4\varepsilon_s q N_D \psi_B} \quad \text{for n-type substrate}$$

(2.2b)

where  $V_{FB}$  is the flat-band voltage,  $q\psi_B$  is the potential difference between the Fermi level  $E_F$  and the intrinsic Fermi level  $E_i$ ,  $C_{gate}$  is the gate capacitance,  $\varepsilon_s$  is the permittivity of Si,  $N_A$  and  $N_D$  are the channel doping concentrations for p-type substrate and n-type substrate, respectively. Boron penetration will alter the intended device properties in an unacceptable way.<sup>16</sup> All these problems, especially high gate leakage

current, force the CMOS industry to replace the SiO<sub>2</sub> with a high dielectric constant (high-k) material for the gate dielectric.

Figure 2.1 Leakage current reduced by replacing  $SiO_2$  with a high-k dielectric as the gate material.

### 2.1.2 High-k Materials as the Gate Dielectric Layer

Eq. (2.1) indicates the direct tunneling current depends on gate physical thickness. In order to keep or reduce the direct tunneling current to the acceptable level, the  $SiO_2$  gate physical thickness can not be too thin. However, the high performance improvement requires large drain current, which needs thin gate film as a result of feature size down scaling. So using high-k materials will increase the physical gate thickness thus lowering the direct tunneling gate leakage current and resulting in no loss of the performance as a result,<sup>17</sup> which is illustrated in Figure 2.1. The high dielectric constant k is used to compensate the loss of gate capacitance due to the increase of physical thickness, which maintains and even enhances the necessary device drive current. It can be easily seen by a simple equation below <sup>17</sup>

$$C_{gate} = \frac{\varepsilon_0 k_{SiO2}}{t_{SiO2}} = \frac{\varepsilon_0 k_{high-k}}{t_{high-k}}$$

(2.3)

For the electrical design of a device the precise material does not matter, so it is convenient to define an "electrical thickness" of the new gate material in terms of its equivalent silicon dioxide thickness or "equivalent oxide thickness" (EOT). EOT, is used to represent the theoretical thickness of  $SiO_2$  that would be required to achieve the same capacitance as the high-k dielectric, which can be derived from Eq. (2.3) and shown below

Figure 2.2 Comparisons of device power consumption and leakage current between 15 Å SiO<sub>2</sub> gate and 15 Å *EOT* HfO<sub>2</sub> gate. <sup>17</sup>

By introducing high-k dielectric materials, the direct tunneling gate leakage current and thus static power consumption can be decreased with the increase of gate physical thickness, which is illustrated in Figure 2.2. Increasing the k value can increase drive current without increasing direct tunneling current, which causes transistor performance improvement. In this way, the traditional down-scaling of SiO<sub>2</sub> thickness turns into down-scaling of the EOT of the high-k gate dielectrics. The objective is to develop

high-k materials which allow scaling to continue to ever lower values of EOT.

### 2.1.3 High-k Gate Material Property Considerations

Many high-k dielectric materials<sup>18</sup> have been investigated as the candidate gate material for future CMOS transistors. All these materials must meet a set of criteria to perform as a successful gate dielectric. Several aspects need to be considered for the appropriate material properties used for gate dielectric applications.

The requirements of a new dielectric material are five-fold.

- 1. Its *k* value must be high enough to be used for a long term of scaling and it must have band offsets with Si of over 1 eV to minimize carrier injection into its bands.

- 2. The high-k material is in direct contact with the Si channel, so it must be thermodynamically stable and form a good electrical interface with Si.

- 3. It must be amorphous in order to act as an insulator and prevent the leakage current.

- 4. It must be compatible with the metal gate electrode.

- 5. The deposition of the high-*k* materials must be compatible with the standard CMOS fabrication process.

Figure 2.3 Energy band diagrams for ideal MOS capacitors for (a) n-type and (b) p-type semiconductor structure. <sup>17</sup>

### 2.1.3.1 Dielectric constant and barrier height

Obviously a gate material with a higher dielectric constant than that of SiO<sub>2</sub> is needed. However, the required dielectric constant must be balanced against the barrier height for the tunneling process of electrons or holes. For electrons tunneling from the Si substrate to the gate, the conduction band offset,  $\Delta E_c = q[\chi - (\Phi_m - \Phi_B)]$ ; for electrons tunneling from the gate to the Si substrate, this offset is  $q\Phi_B$  (see Figure 2.3). The leakage current increases exponentially with decreasing barrier height and gate thickness for electron direct tunneling transport, as shown in Eq. (2.1). However, almost all the high-k materials show a tradeoff tendency between the k value and band offset, which requires reasonably large band gaps. 19 Figure 2.4(a) shows the bad gaps and Figure 2.4 (b) shows the band offset for a number of potential high-k gate dielectric materials. Previous research work<sup>17</sup> pointed out that if the band offsets,  $\Delta E_c$ , of some dielectric materials are less than 1.0 eV, it will likely preclude using these materials as gate dielectric, since tunneling leakage current will lead to an unacceptable value. For the dielectric materials with small band gap (like  $SrTiO_3 \sim 3.3 \text{ eV}$ ), their bands must be aligned symmetrically with respect to those of Si for both barrier height to be over 1 eV. In practice, the conductance band offset is smaller than the valence band offset. This limits the choice of dielectric materials to those with band gaps over 5 eV. So to keep the balance of dielectric constant and band offset, it is suggested from Figure 2.4(a) that materials with k values of 20-25 and band gap of  $\sim 6$  eV are the potential candidates as the gate dielectric materials.

Figure 2.4 (a) Dielectric material band gaps as a function of the dielectric constant values; (b) Dielectric material band offset with Si. <sup>17</sup>

## 2.1.3.2. Stability and interface quality.

For all gate dielectrics, the interface with Si plays a key role in determining the overall electrical properties. Most of the high-k metal oxide materials under investigation have an unstable interface with Si: they will react with Si to form an undesirable interfacial layer (either SiO<sub>2</sub> or silicate) because this interfacial layer will

increase the *EOT* and negate the effect of using the high-k dielectrics. Besides, the dielectric is in direct contact with the Si channel. The carriers in the channel flow within angstroms of the Si/high-k interface. Hence, this interface must be of the highest electrical quality, in terms of roughness and the absence of interface states. Most of the high-k materials show a high interface state density  $D_{it} \sim 10^{11} - 10^{12}/\text{eV} \cdot \text{cm}^2$  while SiO<sub>2</sub> has an interface state density as low as  $D_{it} \sim 1-3\times10^{10}/\text{eV} \cdot \text{cm}^2$ .

### 2.1.3.3. Film morphology

It is desirable to select an amorphous dielectric material because the grain boundaries of poly-crystal will introduce extra defects which enhance the leakage current. But most of the advanced gate dielectrics studied to date are easily crystallized during the thermal treatment in fabrication process. Since an amorphous dielectric must be chosen, a material with high crystallization temperature is preferred. According to the standard CMOS fabrication process, the high-*k* dielectrics must withstand a rapid thermal anneal for 5 seconds at 1000°C. But if an amorphous material is desired, this is a strenuous condition in that most high-*k* materials are not good glass formers, unlike SiO<sub>2</sub>.

#### 2.1.3.4. Gate compatibility

Boron penetration still exists between poly-Si gate electrode and high-k gate material. In addition, the interfacial layer will also form at poly-Si and high-k interface. So metal gates are desired when high-k dielectric material is used as the gate dielectric. In general, a metal with a low work function is preferred for nMOS and a metal with a high work function is preferred for pMOS. A key issue for gate metal electrode

materials will be the control of the gate metal work function after CMOS process, which is the main factor to determine the transistor threshold voltage.

## 2.1.3.5. Process compatibility

A crucial factor in determining the final film quality and properties is the method used for the dielectrics deposition in a fabrication process. The deposition process for the dielectric must be compatible with current or expected CMOS processing, cost, and throughput. Several methods have already been used for high-k dielectric deposition including physical vapor deposition (PVD) (e.g. sputtering and evaporation), chemical vapor deposition (CVD) (involving MOCVD, ALCVD *et al*) and molecular beam epitaxy (MBE).

Figure 2.5 Leakage current limitation of SiON as gate dielectric for low standby power by ITRS 2005. 9

## 2.1.4 Current Status with High-k Materials

The concerns regarding high leakage current, boron penetration of thin  $SiO_2$  have led to the material stack such as silicon-oxynitride (SiON). This material provides a slightly higher k value ( $k \sim 5$ ) than  $SiO_2$  and reduces the leakage current and boron penetration (since the film is physically thicker). The addition of N to  $SiO_2$  greatly reduces the boron diffusion through the dielectric. Furthermore, small amounts of N incorporation at or near the Si channel has been shown to improve device performance. However, due to the relatively low k value (although higher than  $SiO_2$ ), the scaling of SiON appears to be limited to an  $EOT \sim 8$  Å. Below this, the effects of gate leakage current will prevent further improvement in device performance, which is shown in Figure 2.5. So SiON dielectric only represents a near-term solution for scaling the CMOS transistor. Materials with even higher dielectric constant are still needed.

Among those high-k dielectric materials, Hf-based materials such as HfO<sub>2</sub>, HfSiO<sub>4</sub>, HfSiO<sub>x</sub>N<sub>y</sub> *et al* have recently attracted much more attention as potential gate dielectric materials. HfO<sub>2</sub> shows high dielectric constant ( $k \sim 25$ ) and large band offset ( $\Delta E_c = 1.5 \text{ eV}$ ). Although HfO<sub>2</sub> shows a low crystallization temperature below 600°C, it forms a nano-crystalline phase without introducing extra leakage current. Lee *et al*<sup>23</sup> and Kim *et al*<sup>23</sup> find that the leakage currents of amorphous and nanocrystalline HfO<sub>2</sub> are similar. However, two main issues hinder the utilization of HfO<sub>2</sub> as the gate dielectric.

One of the issues is the formation of the interfacial layer between  $HfO_2$  and Si substrate. Figure 2.6 shows a high-resolution transmission electron microscope (HRTEM) image of an interfacial layer formation between the  $HfO_2$  gate dielectric and

Si substrate.<sup>31</sup> This interfacial layer contributes to the EOT, and thus defeats the purpose of using high-k dielectric material to replace the  $SiO_2$  as the gate dielectric, which is given below

$$EOT_{total} = EOT_{high-k} + EOT_{IL}$$

(2.5)

Another issue is the high trap density at the HfO<sub>2</sub>/Si interface. Unlike the SiO<sub>2</sub>/Si interface, HfO<sub>2</sub>/Si interface possesses a high surface states density, which can easily trap electrons and pin the interface Fermi energy level, and thus the threshold voltage of the transistor. Moreover, channel mobility degradation is partially due to the scattering by interface traps, in additional to scattering by phonons and fixed charges in high-*k* dielectrics.

Figure 2.6 HRTEM image of interfacial layer between HfO<sub>2</sub> and Si substrate. <sup>31</sup>

Since the formation of the interfacial layer and the high density of interface traps severely degrade the transistor performance, suppressing the interfacial reaction and lowering the interface trap density between HfO<sub>2</sub> and Si substrate are needed to get a good HfO<sub>2</sub>/Si interface for improving transistor performance.

### 2.2 High Source/Drain Metal/Si Parasitic Resistance

Metal/Si contacts have always been an integral part of Si device technology. With the continued shrinkage of feather size in Si CMOS technology, source/drain parasitic resistances represent a significant fraction of the total device resistance and contribute to a loss of device performance. Figure 2.7 shows the projections by ITRS 2005 for the channel "on" resistance  $R_{on}$  and parasitic resistance  $R_{parasitic}$  for different CMOS nodes. A key source/drain requirement is to limit the  $R_{parasitic}$  to a small fraction of the  $R_{on}$ . The parasitic resistance,  $R_{parasitic}$ , mainly includes the silicide resistance  $R_{sili}$ , junction extension resistance  $R_{ext}$ , junction overlap resistance  $R_{ol}$  and metal/Si contact resistance  $R_c$ , which are shown in Figure 2.8.

Figure 2.7 Projections by ITRS 2005 for the channel "on" resistance and parasitic resistance of high performance devices. <sup>9</sup>

Figure 2.8 MOSFET parasitic resistances which cause device performance loss.

### 2.2.1 Silicide, Junction Extension and Overlap Resistance

Silicide resistance,  $R_{sili}$ , is an important part in the parasitic resistance. TiSi<sub>2</sub> always acted as the low resistance silicide material for source/drain contact till 1990s, in which the resistance increased sharply with lines narrower than 350 nm. Then CoSi<sub>2</sub> was used to replace TiSi<sub>2</sub> as the silicide material with low resistance. However, when the line width is below 50 nm associated with the down scaling of transistor feature size, CoSi<sub>2</sub> also showed a rapid rise in resistance. CMOS industry now focuses on NiSi as the silicide material since<sup>32-36</sup> NiSi shows several advantages such as low resistivity in narrow dimension below 50 nm, low thermal budget for formation, low Si consumption and low transistor leakage current.<sup>37</sup>

As the gate length decreases, the depth of source and drain extensions has to be reduced to suppress short channel effects. At the same time, low sheet resistance of the source/drain extensions has to be realized to take full advantage of the reduced channel resistance in shorter gate length MOSFETs. So it requires junction high doping

concentration for the junction extension resistance  $R_{ext}$  and abrupt lateral junction for overlap resistance  $R_{ol}$ , it requires junction high doping concentration and abrupt lateral junction to keep it to a relatively low value.

Figure 2.9 ITRS 2005 projections for contact resistivity and silicide thickness. 9

### 2.2.2 Contact Resistance

The metal/Si contact resistance,  $R_c$ , is a significant part of the total parasitic resistance. With continued scaling of device feature size, the contact resistance is emerging as the dominant component of the parasitic resistance. Figure 2.9 shows the required contact resistivity and silicide thickness from ITRS 2005. Future MOSFETs will require contact resistivity values as low as  $10^{-8} \ \Omega \cdot \text{cm}^2$ , which is an order of magnitude less than the current contact resistivity  $10^{-7} \ \Omega \cdot \text{cm}^2$ . A report by Ozturk *et al*<sup>38</sup> indicates that if the contact resistivity is kept at current value, the contact resistance

alone will produce series resistance values that are unacceptable for physical gate lengths smaller than ~30 nm. Since the physical gate length for high performance devices has already reached below 30 nm as shown in Figure 1.2, it's important and urgent to lower the contact resistance  $R_c$  or practically, contact resistivity  $\rho_c$  to meet the requirement of source/drain engineering.

Theoretically the contact resistivity is defined as  $\rho_c \equiv \left(\frac{\partial J}{\partial V}\right)_{V=0}^{-1}$ , J and V are the current density and voltage bias, respectively. For metal-semiconductor contacts with lower doping concentrations ( $<10^{17}~\rm cm^{-3}$ ), the thermionic-emission current dominates the current transport while for contacts with higher doping concentration ( $>10^{17}~\rm cm^{-3}$ ), the tunneling current dominates the current transport. The equations are expressed below  $^{15}$

$$J = A * T^{2} \exp(-\frac{q\Phi_{B}}{kT})(e^{\frac{qV}{kT}} - 1) \text{ for low doping}$$

(2.6a)

$$J \sim \exp(-\frac{q\Phi_B}{E_{00}})$$

and  $E_{00} = \frac{q\hbar}{2} \sqrt{\frac{N}{\varepsilon_s m^*}}$  for high doping (2.6b)

Since  $\rho_c = \left(\frac{\partial J}{\partial V}\right)_{V=0}^{-1}$ , the contact resistivity is a function of Schottky barrier height  $\Phi_B$

and Si substrate doping level N, which is shown below 15

$$\rho_c = \frac{k}{qA * T} \exp(\frac{q\Phi_B}{kT}) \text{ for low doping}$$

(2.7a)

$$\rho_c \propto \exp(\frac{2\Phi_B}{\hbar} \sqrt{\frac{\varepsilon_s m^*}{N}})$$

for high doping (2.7b)

where  $A^*$  is the effective Richardson constant, k is the Boltzmann constant, k is the absolute temperature, k is Planck constant, k is the unit charge, k is the bulk doping concentration and k is the effective mass of electron or hole. A small contact resistance has been achieved by applying heavily-doped Si on both source and drain regions. This kind of metal/Si contact with linear current-voltage characteristic, which is called ohmic contact, has been the most widely used technique. However, from Eq. (2.7a) and Eq. (2.7b), lower contact resistivity can also be realized by lowering the Schottky barrier height especially when the doping level in Si is reaching its solubility or high doping levels are undesirable. From Eq. (2.7a) and Eq. (2.7b), the improvement of contact resistivity by lowering the Schottky barrier height is given below and shown in Figure 2.10

Figure 2.10 Improvement of contact resistivity by lowering the Schottky barrier height for electrons.

$$\frac{\rho_c(\Phi_B)}{\rho_c(\Phi_B - \Delta\Phi_B)} = \exp(\frac{q\Delta\Phi_B}{kT}) \text{ for low doping}$$

(2.8a)

$$\frac{\rho_c(\Phi_B)}{\rho_c(\Phi_B - \Delta\Phi_B)} = \exp(\frac{2\Delta\Phi_B}{\hbar} \sqrt{\frac{\varepsilon_s m^*}{N}}) \text{ for high doping}$$

(2.8b)

Figure 2.10 indicates that theoretically by lowering the Schottky barrier height by 0.06 eV, the contact resistivity for electron can be lowered by one order of magnitude for low doping level and two orders for high doping level. So the Schottky barrier height should be lowered to lower the contact resistivity at metal/Si interface.

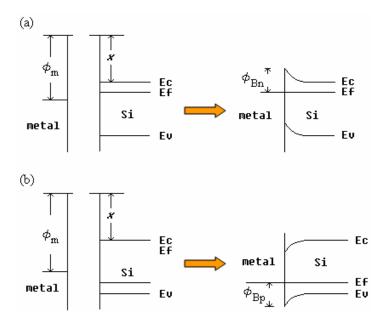

Figure 2.11 Ideal metal/Si contact energy band diagram for (a) n-type and (b) p-type.

# 2.2.3 Schottky Barrier Height

Before a metal and Si contact with each other, the system is not in thermal equilibrium. After the metal contacts with Si, the Fermi energy level of the metal lines up with the Fermi energy level of the Si, thermal equilibrium is established and a

Schottky barrier is formed. Ideally, the Schottky barrier height  $\Phi_{Bn}$  for electron is determined by the difference between the metal work function and the Si electron affinity. The Schottky barrier height for hole,  $\Phi_{Bp}$ , is determined by the difference between metal work function, Si electron affinity and Si band gap, which is shown in Figure 2.11. The equations are given below, respectively<sup>15</sup>

$$\Phi_{Bn} = \Phi_m - \chi \tag{2.9a}$$

$$\Phi_{Bp} = E_g - (\Phi_m - \chi) \tag{2.9b}$$

where  $\Phi_m$  is the metal work function,  $\chi$  is the Si electron affinity, and  $E_g$  is the Si band gap. Eq. (2.9a) and Eq. (2.9b) shows that a low Schottky barrier height can be obtained by choosing a small work function metal like Al and Ti for electrons and by choosing a large work function metal like Ni and Pt for holes.

Figure 2.12 Metal/Si contact energy band diagram with surface states for (a) n-type and (b) p-type.

However, the Si surface is inherently dominated with a large density of

surface states. Surface states will introduce surface Fermi level in the band gap of Si, so the bulk Fermi level will line up with the surface Fermi level or in another word, Fermi level is pinned at the Si surface. The actual barrier height is mainly determined by the pinned Fermi level and largely independent of metal work function, which is shown in Figure 2.12. The equations are shown below, respectively:

$$\Phi_{Bn} \approx E_{cs} - E_{fs} \tag{2.10a}$$

$$\Phi_{Bp} \approx E_{fs} - E_{vs} \tag{2.10b}$$

where  $E_{cs}$  and  $E_{vs}$  are the surface conductance and valence band energy levels, respectively,  $E_{fs}$  is surface pinned Fermi energy level. According to Eq. (2.9) and Eq. (2.10), to lower the Schottky barrier height, the surface state density needs to be minimized to tune the barrier height by choosing a metal with a proper work function according to the ideal metal/Si contacts.

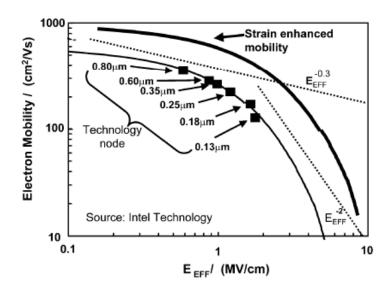

Figure 2.13 Mobility versus scaling trend for Intel process technology. 42

## 2.3 Channel Mobility Degradation

A key scaling problem in nanoscale transistors is mobility degradation caused by the large vertical electric fields. Figure 2.13 shows the mobility versus technology scaling trend for various Intel process technologies. The mobility has decreased from 400 to 120 cm<sup>2</sup>/V·s during the last decade. To counteract this undesirable mobility trend, it is very important to incorporate mobility enhancing mechanisms in nanometer logic technology.

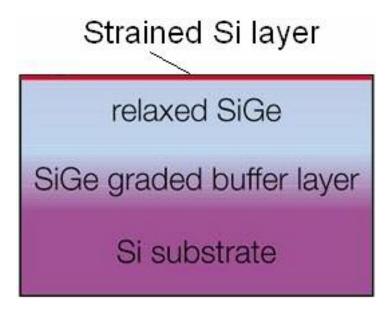

#### 2.3.1 Strained Silicon

Strained Si<sup>43-45</sup> technology enables improvement in CMOS performance and functionality since strained Si has electronic properties that are superior to those of bulk Si. Specifically, the strained Si film has greater electron and hole mobilities, which translate into greater drive current for CMOS transistors. A recent report by Thompson *et al*<sup>42</sup> indicated an increase in hole mobility of more than 50% for p-type strained Si transistor and an increase in electron mobility of ~ 20% for n-type strained Si transistor. The key to get high quality strained Si for high performance devices is the growth of a low-defect-density SiGe film. Figure 2.14 shows a simple illustration for the strained Si structure. Growing a Si layer on SiGe, which has a larger lattice constant than Si, generates a strained Si heterostructure, which can be tailored to enable various properties. One of the main factors for performance enhancement with strained Si technology is the amount of strain introduced to the strained Si film, which is determined by the Ge content in the underlying SiGe film. Since the deposition of SiGe has a great effect on performance improvement, it is very important to understand the

SiGe growth behavior.

Figure 2.14 Illustration of structure for strained Si.

## 2.3.2 SiGe Alloy Growth Behavior

In the early 1990's, heteroepitaxtial silicon-germanium alloys (Si<sub>1-x</sub>Ge<sub>x</sub>) were successfully applied to Si-based heterojunction bipolar transistors to achieve better performance in current gain and cutoff frequency. Horror More recently, Si<sub>1-x</sub>Ge<sub>x</sub> attracted more attention for its important application in the strained-Si complementary MOSFET for mobility enhancement. A number of growth techniques have been used to deposit Si<sub>1-x</sub>Ge<sub>x</sub> including various chemical vapor deposition (CVD) techniques: ultrahigh vacuum CVD (~10<sup>-5</sup> Torr), Horror low pressure CVD (~10<sup>-3</sup> Torr), Si<sub>2-54</sub> rapid thermal CVD (~1 Torr), Si<sub>2-56</sub> atmospheric pressure CVD (~740 Torr), plasma-enhanced CVD, si well as gas source molecular beam epitaxy. Several precursors have been investigated for Si<sub>1-x</sub>Ge<sub>x</sub> deposition as the Ge source, such as germane (GeH<sub>4</sub>), Horror and digermane (Ge<sub>2</sub>H<sub>6</sub>), Horror and as the Si source,

silane  $(SiH_4)$ ,  $^{48,49,50,51,53,63}$  disilane  $(Si_2H_6)$ ,  $^{49,62}$  and dichlorosilane (SiH<sub>2</sub>Cl<sub>2</sub>). <sup>54,56,58,64</sup> Si<sub>1-x</sub>Ge<sub>x</sub> growth by CVD is a much more complicated process than the growth of pure Si by CVD. For example, the Ge content in the film is controlled by several parameters, including deposition temperature, deposition pressure, SiH<sub>4</sub> flow rate, and most importantly, GeH<sub>4</sub> flow rate. Different behaviors in growth rate have been observed with respect to the effect of Ge content incorporated in the film. With GeH<sub>4</sub> and SiH<sub>2</sub>Cl<sub>2</sub> as the precursors, a monotonic increase in growth rate has been reported with increasing Ge content by Hartmann et al<sup>54</sup> in low pressure CVD at deposition temperature of 650°C, 700°C and 750°C, by Kamins et al<sup>58</sup> in atmospheric pressure CVD at 625°C, by Garone et al<sup>56</sup> in rapid thermal CVD between 625°C and 700°C, and by Hoyt et al<sup>64</sup> in rapid thermal CVD at 640°C. With SiH<sub>4</sub> and GeH<sub>4</sub> as the precursors. Jang et al<sup>65</sup> demonstrated that the effect of Ge content on growth rate is more complicated in very low pressure CVD. A monotonic growth rate increase was observed with Ge content at 570°C, but a monotonic growth rate decrease with Ge content at 700°C. Between 600°C and 675°C, the growth rate exhibited first an increase and then a decrease, resulting in a maximum with Ge content. Using ultrahigh vacuum CVD, Meyerson et al<sup>48</sup> reported a growth rate increase with Ge at 550°C, Robbins et al<sup>53</sup> reported a growth rate decrease with Ge at 700°C, and Racanelli et al<sup>66</sup> reported that the growth rate first increased and then decreased with Ge between 577°C and 665°C.

#### 2.3.3 Previous Models for SiGe Growth

Several kinetic models have been proposed to explain the complicated growth behavior in Si<sub>1-x</sub>Ge<sub>x</sub> CVD from SiH<sub>4</sub> and GeH<sub>4</sub>. Robbins *et al*<sup>53</sup> attributed the growth rate maximum with Ge content to a competition between desorption of H from the surface and adsorption of H from the gas phase. A scaling factor was introduced in order for their model to fit the experimental data. Russell *et al*<sup>67</sup> proposed a model by treating SiH<sub>4</sub> and GeH<sub>4</sub> deposition as two parallel processes. Each is a competition between adsorption of precursor and desorption of H, and there is a fast equilibration between Si and Ge hydrides on the surface. Malik *et al*<sup>68</sup> attempted to explain the growth behavior on the basis of Langmuir-Hinshelwood's adsorption theory. Lee<sup>69</sup> presented a model based on competitive adsorption of GeH<sub>4</sub> and SiH<sub>4</sub> on vacant surface sites, coupled with GeH<sub>4</sub>-assisted H desorption. Jang<sup>65</sup> explained the growth behavior with two mechanisms: (1) enhanced H desorption by the presence of Ge at low Ge content and/or temperature and (2) reduced reaction probability of GeH<sub>4</sub> and SiH<sub>4</sub> with the incorporation of Ge at high Ge content and/or temperature.

These models attempted to quantitatively explain the growth behavior of  $Si_{1-x}Ge_x$  by various CVD processes. Although many of them provide reasonable explanations for several aspects, they are best described as semiquantitative or qualitative models. A comprehensive and quantitative model is still needed for SiGe growth from  $SiH_4$  and  $GeH_4$  by CVD.

#### CHAPTER 3

# SURFACE PASSIVATION OF SILICON (100) BY MONOLAYER SELENIUM

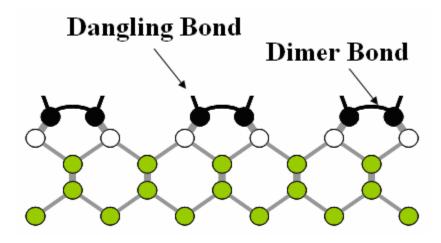

#### 3.1 Si (100) Surface Structure in Vacuum

Surface atoms on Si (100), due to the discontinuity of lattice atoms above them, have to undergo reconstruction in ultrahigh vacuum to minimize surface energy.<sup>70</sup> Figure 3.1 shows the atomic structure of clean Si (100) in vacuum. Each surface atom has a dangling bond and shares a dimer bond with its neighboring surface atom. Both the dimer bonds and back bonds are strained on this surface. Because dangling bonds are not saturated at the Si (100) surface, they are the sites for surface chemical reactions. When a metal oxide dielectric material is deposited on the surface of Si (100), oxygen atoms can easily react with the surface Si atoms to form an interfacial layer between high-k dielectric and Si substrate. These dangling bonds also give rise to interface states within the energy band gap of Si, which cause interface traps at the high-k/Si interface. When a metal is deposited on Si, the interface Fermi energy is often pinned by these interface states, making the Schottky barrier height independent of metal work function. Since the dangling bonds are the origin of surface reaction sites and surface states, it is important to remove the dangling bonds in order to suppress the interfacial layer formation between the high-k dielectric and the Si substrate, minimize the interface trap density at high-k/Si interface, and lower the metal/Si (100) contact resistivity.

Figure 3.1 Atomic structure of the clean Si (100) surface in ultrahigh vacuum. <sup>70</sup>

3.2 Si (100) Surface Structure with Se Passivation

The idea of surface passivation by adsorbates has been studied more than three decades ago. The most important aspect of surface passivation is a valence difference between the substrate and the adsorbate such that, when adsorbate atoms replace the bulk-terminated plane, all broken covalent bonds are eliminated. Forming gas  $(95\% \text{ N}_2 + 5\% \text{ H}_2)$  annealing has been a standard CMOS process used to passivate the Si (100) surface for a long time. During the annealing, each dangling bond at Si (100) surface will be terminated by one H atom. However, the dimer bonds are still intact and can break again to act as dangling bonds especially when oxygen-contained high-k dielectric is applied. So it's desirable that the passivation on Si (100) can both terminate dangling bonds and relax the dimer bonds.

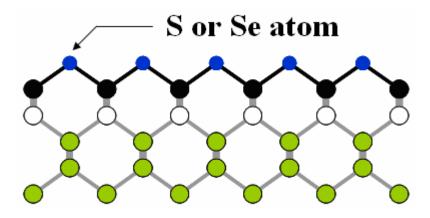

Figure 3.2 Atomic structure of the Se-passivated Si (100) surface. 71

In 1991, Kaxiras<sup>71</sup> introduced the concept "valence-mending" to passivate the Si (100) surface. He concluded that natural "valence-mending" choices for Si (100) would be elements with valence 2 or 6. The best choices would be group-VI elements (O, S, Se, and Te) because they tend to form structures with twofold coordination and  $sp^3$  bonding hybrids, precisely as required for restoration of Si (100). O and Te can be dismissed since O can easily diffuse into Si and form SiO2 and Te has bulk bond length which is different from that of Si by 22%. As shown in Figure 3.2, atoms of sulphur (S) and selenium (Se) can bridge between two surface atoms on Si (100), thereby terminating dangling bonds and relaxing the strained dimer bonds. Se was predicted to be a better choice than S for passivating Si (100) because the Se atom has several proper factors with Si: covalent and atomic radius; bond length and angle, which are shown in Table 3.1 and 3.2. It will introduce less strain in the passivated surface. The Se-passivated Si (100) surface is stable so that it is expected that Se passivation will suppress interfacial layer formation between high-k dielectric and Si substrate. The interface trap density will also decrease due to the removal of dangling bonds. As a result, Schottky barrier heights between metals and Se-passivated Si (100) are more closely correlated to metal work functions 'than the surface properties of Si (100) without passivation.

Table 3.1 Covalent and atomic radius of Si and group VI elements

|                     | Si   | Se   | S    | Te   |

|---------------------|------|------|------|------|

| Covalent Radius (Å) | 1.17 | 1.17 | 1.04 | 1.37 |

| Atomic Radius (Å)   | 1.18 | 1.16 | 1.06 | 1.42 |

Table 3.2 Structural parameters of bulk phases of S and Se and of the ideal and restored Si (100) surfaces.

|                      | SI (100) sulfaces. |                     |  |

|----------------------|--------------------|---------------------|--|

|                      | Bond length(Å)     | Bond angle(degrees) |  |

| Monoclinic Se        | 2.34               | 105.5               |  |

| Rhombohedral S       | 2.06               | 102.2               |  |

| Ideal Si (100)       | 2.35               | 109.4               |  |

| Restored Si (100):S  | 2.24               | 118.4               |  |

| Restored Si (100):Se | 2.34               | 110.2               |  |

#### 3.3 Se passivation on Si (100) surface by molecular beam epitaxy

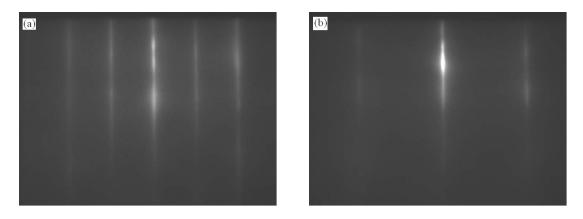

In this research work, monolayer Se atoms are deposited on Si (100) surface to passivate the dangling bonds by molecular beam epitaxy (MBE) system. The Si (100) wafer is first rinsed in de-ionized water for 2 minutes and then immediately dipped into 2% HF for 35 seconds to remove the native oxide. It is then terminated by H atoms. After the HF dip, wafer is blown dry with N<sub>2</sub> and loaded into the MBE system. In the MBE chamber, ultrahigh vacuum (~10<sup>-10</sup> Torr) is maintained as the base pressure. The Si (100) wafer is first annealed at 600°C for 25 minutes. This is to desorb the surface H atoms. Then the wafer is transferred to the Si source chamber. A Si buffer layer of 100~1000 Å is deposited at 600°C and then annealed at 800°C for 1 hour. This is to have a perfect Si (100) surface for the Se passivation. In Figure 3.3(a) is shown a sharp

2×1 surface reconstruction atom structure. That is obtained with reflection high-energy electron diffraction (RHEED) after annealing, which indicates that the Si surface is in the structure shown in Figure 3.1. The wafer is then transferred to the Se source chamber for passivation. The Se source temperature is 224°C, while the Si wafer is kept at a temperature of 300°C during the passivation. Once the shutter of the Se source is open, Se atoms will deposit on the Si surface. The in situ RHEED shows the Si (100) surface gradually changes in 60 seconds from 2×1 structure to 1×1 structure, which is shown in 3.3(b). This indicates that one monolayer of Se atoms is deposited on the Si (100) surface, which forms the surface atomic structure in Figure 3.2. Then the shutter of the Se source is closed and Si wafer is kept inside the MBE chamber till it cools down to room temperature.

Figure 3.3 (a) RHEED image of bare Si (100) with 2×1 surface structure and (b) RHEED image of Se-passivated Si (100) with 1×1 surface structure.

#### **CHAPTER 4**

# HAFNIUM DIOXIDE ON N-TYPE SILICON (100) WITH SELENIUM PASSIVATION

In this chapter, experiments are designed to verify the interfacial layer suppression effect at HfO<sub>2</sub>/Si interface by Se passivation. Results for HfO<sub>2</sub> on Se-passivated n-Si (100) are reported. <sup>72</sup> Capacitance-voltage (C-V) and current-voltage (I-V) measurements are utilized for characterization analysis.

# 4.1 Experiments

## 4.1.1 Wafer Preparation

N-type Si (100) wafer with resistivity 1-10  $\Omega$ -cm is chosen. The wafer is first rinsed in de-ionized water for 2 minutes. This is to oxidize the surface. Then the wafer is dipped into 2% HF for 35 seconds to remove the surface native oxide and be terminated by H atoms. After HF dip, the wafer is blown dry with  $N_2$  and loaded into the MBE system.

#### 4.1.2 Se Passivation

This is described in section 3.3. A 500 Å Si buffer layer is deposited during Se passivation. A control wafer with 500 Å Si buffer layer is also fabricated without Se passivation for comparison.

#### 4.1.3 HfO<sub>2</sub> Growth

Three methods are employed to grow  $HfO_2$  on the control and Se-passivated samples.

# — HfO<sub>2</sub> growth by reactive sputtering

Both control and Se-passivated samples are loaded into a 4-inch target reactive sputtering system. After pumping to  $\sim 4\times10^{-6}$  Torr, Ar and O<sub>2</sub> with a ratio of 10 sccm/40 sccm are introduced into the chamber. The pressure during sputtering is kept at 10 mTorr. Hafnium oxide is deposited on both the control and Se-passivated samples at room temperature for 3 minutes. The plasma power is chosen at 40 watts. A 99.95% Hf target is used for the sputtering.

# — HfO<sub>2</sub> growth by O<sub>3</sub> oxidation

Both control and Se-passivated samples are loaded into the E-beam evaporator system. After pumping to  $\sim 8\times10^{-7}$  Torr, 40 Å of Hf is deposited on both control and Se-passivated samples. Then samples are cut into small pieces and loaded into a home-made furnace. After pumping, ultra-pure  $O_2$  is introduced to the furnace at 1 atm.  $O_3$  is generated by a UV-lamp. Then both samples are oxidized and annealed simultaneously at 360, 440, 520, and 600°C for 10 minutes. Step (d) is skipped since samples have been already annealed during oxidation. 99.95% Hf metal pellets are used for the evaporation.

#### — HfO<sub>2</sub> growth by dry oxidation

The  $HfO_2$  growth by dry oxidation is similar with the  $HfO_2$  growth by  $O_3$  oxidation. The differences are for  $HfO_2$  growth by dry oxidation, dry  $O_2$  is introduced

instead of O<sub>3</sub> and oxidation temperatures are chosen at 300, 400, 500, and 600°C.

#### 4.1.4 Post-Deposition Annealing

After HfO<sub>2</sub> deposition, both control and Se-passivated samples are cut into small pieces and loaded into a home-made furnace. After pumping to a base pressure 10<sup>-6</sup> Torr, ultra-pure N<sub>2</sub> is introduced into the furnace chamber at 1 atm. The samples are annealed at 400, 500 and 600°C for 1 minute. (This step is only applied for HfO<sub>2</sub> growth by reactive sputtering. For HfO<sub>2</sub> growth by O<sub>3</sub> and dry oxidation, it can be skipped because annealing has been performed simultaneously during oxidation.)

## *4.1.5 Photolithography*

All the samples are spin-coated with HMDS (Hexamethyldisilazane) at 4000 rpm for 30 seconds and S1808 (photoresist) at 2000 rpm for 30 seconds, consecutively. Then a post baking is applied to all the samples at 90°C for 35 seconds. After that, samples will be exposed under mask by UV lamp for 50 seconds. Then samples will be dipped in develop solution for 35 seconds for pattern transformation.

# 4.1.6 Metal Deposition

The metal electrodes are fabricated by using a lift-off process. After photolithography, both control and Se-passivated samples are loaded into an E-beam system. After pumping to  $\sim 2\times10^{-6}$  Torr, 1000 Å Al is deposited for top electrodes and 500 Å Ti is deposited on the back side for contact.

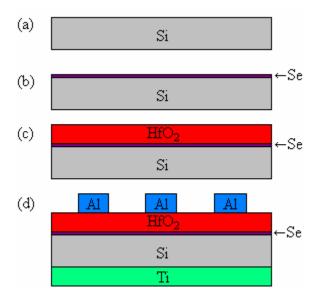

Figure 4.1 shows the main fabrication process flow for the experiments.

Figure 4.1 Fabrication processes of the experiments: (a) wafer preparation; (b) Se monolayer passivation; (c) HfO<sub>2</sub> growth; (d) Photolithography, Al deposition for front contact and Ti deposition for back contact

#### 4.2 Characterization

High frequency C-V characterization is performed to determine the *EOT* of the gate dielectric and flat-band voltage. On the C-V curve, the maximum capacitance in accumulation region is the gate oxide capacitance. The *EOT* can be extracted by

$$EOT = A \frac{\varepsilon_0 k_{SiO_2}}{C_{occu}} \tag{4.1}$$

The flat-band voltage  $V_{FB}$  can be extracted from the C-V curve, which reveals the shift in threshold voltage due to interface and fixed charges. Theoretically the ideal flat-band voltage  $V_{FB}$  is determined by the difference between the metal work function  $\Phi_m$  and the semiconductor work function  $\Phi_S$ , which is given below <sup>15</sup>

$$V_{FB} = \frac{1}{q} (\Phi_m - \Phi_S) = \Phi_{ms}$$

(4.2)

But the actual flat-band voltage will shift from the ideal flat-band voltage by an amount  $\Delta V_{FB}$  due to the interface charge  $Q_{it}$  and fixed charges  $Q_f$  in the dielectric, which is given by

$$\Delta V_{FB} = -\frac{Q_{it} + Q_f}{C_i} \tag{4.3}$$

So the actual flat-band voltage is

$$V_{FB} = \Phi_{ms} + \Delta V_{FB} = \Phi_{ms} - \frac{Q_{it} + Q_f}{C_i}$$

(4.4)

Since the actual flat-band voltage  $V_{FB}$  corresponds to flat-band capacitance  $C_{FB}$ , it can be determined by finding the corresponding voltage to  $C_{FB}$  on the C-V curves. The  $C_{FB}$  is given by <sup>15</sup>

$$\frac{1}{C_{FR}} = \frac{1}{C_i} + \frac{1}{C_D} \tag{4.5}$$

where  $C_i$  is gate dielectric capacitance and equals to maximum capacitance  $C_{accu}$  in accumulation region,  $C_D$  is extrinsic Debye capacitance, which is given by <sup>15</sup>

$$C_D = A \frac{\varepsilon_0 \varepsilon_{Si}}{L_D}$$

and  $L_D = \sqrt{\frac{kT \varepsilon_0 \varepsilon_{Si}}{N_{bulk} q^2}}$  (4.6)

The dielectric constant of the high-k material can be calculated below:

$$k = \frac{3.9t_{high-k}}{EOT_{total} - EOT_{tt}} \tag{4.7}$$

where  $t_{high-k}$  is the physical thickness of high-k dielectric,  $EOT_{IL}$  is the equivalent oxide thickness contributed by interfacial layer (equals to interfacial layer physical thickness if the interfacial layer is assumed to be SiO<sub>2</sub>),  $EOT_{total}$  is the equivalent oxide thickness

from the gate dielectric and it can be calculated by Eq. (4.1). I-V characterization is used to directly measure the gate leakage current.

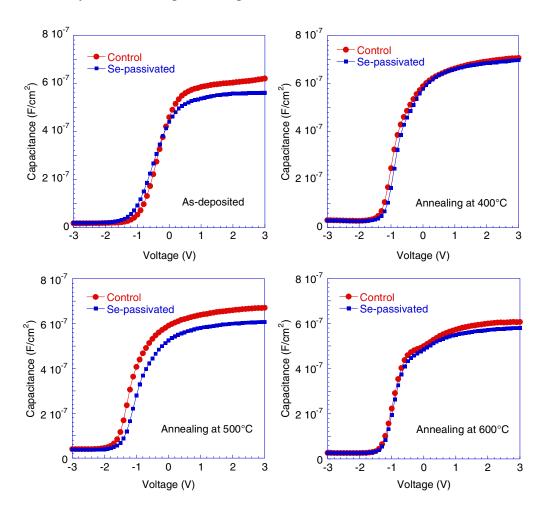

Figure 4.2 C-V characterizations of control and Se-passivated samples by reactive sputtering at different annealing temperatures. <sup>72</sup>

## 4.3 Results and Discussion

## 4.3.1 HfO<sub>2</sub> by Reactive Sputtering