# ANALYSIS AND CHARACTERIZATION OF THERMAL EFFECTS IN ANALOG CIRCUITS

by

## ABHIJIT CHAUGULE

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

## MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

THE UNIVERSITY OF TEXAS AT ARLINGTON

December 2005

Copyright © by Abhijit Chaugule 2005

All Rights Reserved

# DEDICATED TO MY FAMILY

#### ACKNOWLEDGEMENTS

I would like to express my gratitude and thank Dr. Ronald Carter for giving me the opportunity to work on this project under his guidance. He has been the backbone of my work and I thank him for his continuous guidance, motivation and patience throughout the completion of this thesis. I would also like to thank Dr. W.A.Davis & Dr. Howard Russell, for their constant support and guidance to solve my problems. I would like to thank Dr. Enjun Xiao for being a part of my thesis committee and sharing his views on my work.

Funding for this research was provided in part from the National Semiconductor Corporation (NSC Virtual Laboratory Program Manager: Dr. Bijoy Chatterjee) and the Department of Electrical Engineering of The University of Texas at Arlington. I thank them for making this thesis possible.

In addition, I would like to thank my family and friends for supporting me in every means.

November 21, 2005

### ABSTRACT

# ANALYSIS AND CHARACTERIZATION OF THERMAL EFFECTS IN ANALOG CIRCUITS

Publication No.

Abhijit Chaugule, M. S.

The University of Texas at Arlington, 2005

Supervising Professor: Dr. R. L. Carter

Dielectrically Isolated Bipolar Junction Transistors (DIBJTs) are used in industry for high speed and high power applications. These devices suffer from thermal heating and are subjected to change in their characteristics. This thesis explores the thermal effects involving the self heating and inter-device heating (thermal coupling) at the device as well as at the circuit level.

Systematic analysis of individual device heating characteristics in a particular Current feedback operational amplifier (CFOA) design is carried out, using the VBIC (Vertical Bipolar Inter-company) model in the the Cadence SpectreS simulator. A diagnostic and design procedure is established for circuit designers to determine the possible causes of the thermal tail and to eliminate the problem. To consider the interdevice heating effects, a BJT symbol including adjacent device heating in the VBIC model is developed at the schematic capture level.

Different test structures are developed, and fabricated using National Semiconductor process to study dependence of inter-device heating of DIBJTs on various layout factors. An innovative method for the inter-device heating measurement is developed using IC-CAP / HPIB interfaced evaluation system.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                                                         | iv  |

|----------------------------------------------------------------------------------------------------------|-----|

| ABSTRACT                                                                                                 | v   |

| LIST OF ILLUSTRATIONS                                                                                    | xi  |

| LIST OF TABLES                                                                                           | xiv |

| Chapter                                                                                                  |     |

| 1. INTRODUCTION                                                                                          | 1   |

| 2. DIELECTRICALLY ISOLATED BIPOLAR JUNCTION TRANSISTORS<br>(DIBJT)                                       | 6   |

| 2.1 Structure of DIBJT                                                                                   | 6   |

| 2.2 Thermal Definitions                                                                                  | 10  |

| 2.2.1 Self Heating                                                                                       | 10  |

| 2.2.2 Thermal Coupling or Inter-device Heating                                                           | 10  |

| 2.2.3 Thermal Resistance                                                                                 | 10  |

| 2.2.4 Thermal resistivity                                                                                | 11  |

| 2.2.5 Thermal Capacitance                                                                                | 12  |

| 2.3 Thermal and Electrical analogy                                                                       | 12  |

| 2.4 Five Element Thermal Resistance (Rth) Model for DIBJT                                                | 14  |

| 2.5 Thermal model for inter-device heating or thermal coupling for DIBJT                                 | 16  |

| 2.6 Voltage controlled voltage source (VCVS) representation for inter-device heating or thermal coupling | 18  |

| 3. | CAD TOOLS & SIMULATION TECHNIQUES FOR MODELING<br>TEMPERATURE EFFECTS        | 21 |

|----|------------------------------------------------------------------------------|----|

|    | 3.1 Vertical Bipolar Inter Company (VBIC) Model                              | 21 |

|    | 3.2 Different CAD tools supporting VBIC model                                | 23 |

|    | 3.3 Use of VBIC model in Cadence SepctreS simulator                          | 23 |

|    | 3.4 Different temperature related terms                                      | 26 |

| 4. | THERMAL CHARACTERIZATION OF CURRENT FEEDBACK<br>OPERATIONAL AMPLIFIER (CFOA) | 30 |

|    | 4.1 General Current Feedback Operational Amplifier (CFOA)<br>topology        | 31 |

|    | 4.2 Need for the thermal study of CFOA                                       | 32 |

|    | 4.3 Thermal response of the devices constituting the CFOA                    | 36 |

|    | 4.3.1 Nomenclature used for CFOA                                             | 36 |

|    | 4.3.2 Thermal Simulations                                                    | 37 |

|    | 4.4 Layout study of the CFOA                                                 | 43 |

| 5. | THERMAL CHARACTERIZATION OF OFFSET AND GAIN<br>ERROR FOR CFOA                | 46 |

|    | 5.1 Input offset voltage (Vio) variation with temperature                    | 47 |

|    | 5.1.1 Input offset voltage (Vio)                                             | 47 |

|    | 5.1.2 Thermal Voltage Drift                                                  | 47 |

|    | 5.2 Different Circuit Configurations for input offset voltage simulations.   | 48 |

|    | 5.3 Thermal characterization of Time Dependent Gain Error<br>of CFOA         | 59 |

|    | 5.3.1           | Gain change of the CFOA with circuit temperature (dA/dtemp)        |

|----|-----------------|--------------------------------------------------------------------|

|    | 5.3.2           | 2 Device temperature change with Circuit temperature<br>(dT/dtemp) |

|    | 5.3.            | 3 Gain change with device temperature variation (dA/dTi)           |

| 6. | INTER-DEVI      | CE HEATING MEASUREMENTS                                            |

|    | 6.1 Test Struct | ures for Thermal Coupling Measurements                             |

|    | 6.1.1 UTA       | A 184 & UTA 189 test structures                                    |

|    | 6.1.2 UTA       | A 185 & UTA 190 test structures                                    |

|    | 6.1.3 UTA       | A 204 and UTA 205 Test Structures                                  |

|    | 6.2 Configurat  | ion for Apparent temperature measurement of BJT                    |

|    | 6.3 IC-CAP / I  | IP IB interfaced Evaluation system                                 |

|    | 6.3.1 HP        | 4142B Modular DC Source/Monitor                                    |

|    | 6.3.2 IC-0      | CAP tool                                                           |

|    | 6.4 Measurem    | ent set-up and procedure for thermal coupling measurement          |

|    | 6.4.1 Measu     | arement set up for thermal coupling measurements                   |

|    | 6.4.2 Measu     | arement Procedure                                                  |

|    | 6.5 Measurem    | ent Results & Discussion                                           |

|    | 6.5.1 Mea       | surement results with forward Gummel configuration                 |

|    | 6.5.2 Mea       | surement results for inter-device heating                          |

| 7. | Conclusion and  | Future Work                                                        |

| Ap | opendix         |                                                                    |

|    | A. LAYOUTS      | FOR EAGLE 19                                                       |

| REFERENCES               |     |

|--------------------------|-----|

|                          |     |

| BIOGRAPHICAL INFORMATION | 102 |

## LIST OF ILLUSTRATIONS

| Figure |                                                                                         | Page |

|--------|-----------------------------------------------------------------------------------------|------|

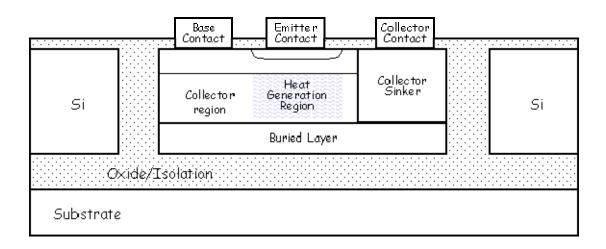

| 1.1    | Schematic cross-section of a DIBJT                                                      | . 4  |

| 2.1    | Schematic cross-section of a DIBJT                                                      | . 7  |

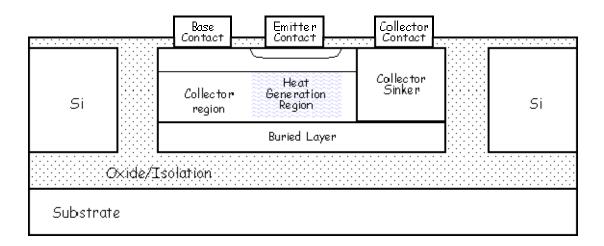

| 2.2    | VIP10 Transistor Cross-section                                                          | . 7  |

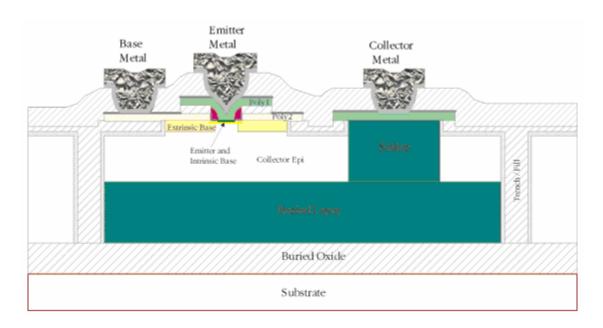

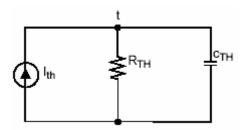

| 2.3    | Additional Thermal Network in VBIC Model                                                | . 13 |

| 2.4    | Five Element Thermal Resistance (Rth) Model for DIBJT                                   | . 15 |

| 2.5    | Overall Thermal Resistance (R <sub>th</sub> ) model for DIBJT                           | . 16 |

| 2.6    | Modeling of Thermal Coupling between Two Adjacent Devices                               | . 17 |

| 2.7    | Intrinsic VBIC Model for Transistor Qi                                                  | . 18 |

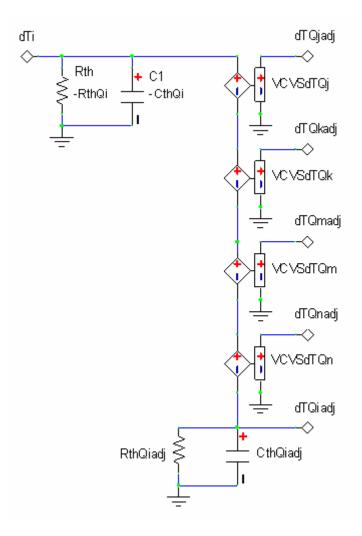

| 2.8    | Extrinsic VBIC Thermal Model for Inter-Device Heating                                   | . 19 |

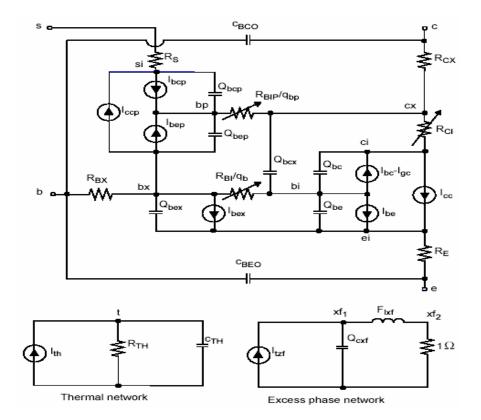

| 3.1    | Equivalent Circuit VBIC Model                                                           | . 22 |

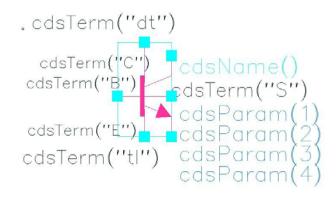

| 3.2    | The VBIC 6 Terminal Transistor Symbol for the SpectreS Simulator                        | . 24 |

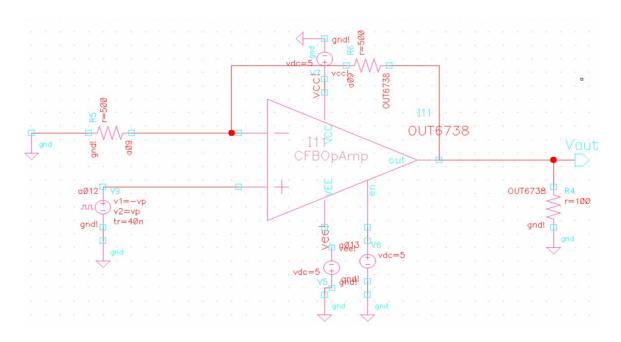

| 3.3    | Schematic of CFOA used to verify different temperature related parameters in SpectreS   | . 27 |

| 4.1    | General Schematic of typical high speed complementary bipolar CFOA                      | . 31 |

| 4.2    | Simulation plot of log of TO vs. time for CFOA                                          | . 34 |

| 4.3    | Measured TO data for the CFOA on a 2V P-P (-1 to +1) transition                         | . 34 |

| 4.4    | General Schematic of CFOA Showing the nomenclature used for devices on different sticks | . 38 |

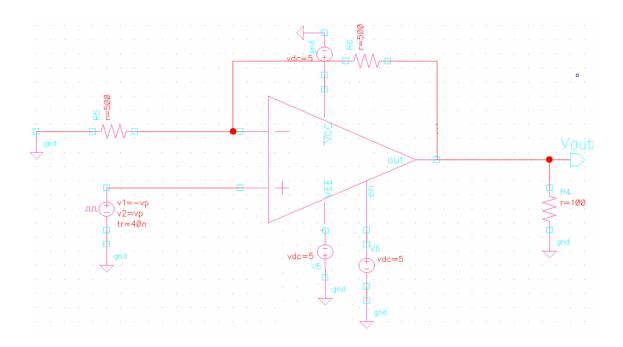

| 4.5    | Simulation set up for thermal analysis of CFOA                                          | . 39 |

| 4.6  | Transient response of the voltages at 'dt' nodes of all NPN devices<br>in CFOA with 'selft' on for all devices                               | . 40 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.7  | Final temperature at 'dt' nodes of all NPN devices in CFOA with 'selft' on for all devices                                                   | . 40 |

| 4.8  | Transient response of the voltages at 'dt' nodes of all PNP devices in CFOA with 'selft' on for all devices                                  | . 41 |

| 4.9  | Final temperature at 'dt' nodes of all PNP devices in CFOA with 'selft'<br>on for all devices                                                | . 41 |

| 4.10 | Part of Layout representation for the devices on stick1, 2 & 3                                                                               | . 44 |

| 5.1  | Closed loop CFOA configuration for Vio simulations                                                                                           | . 48 |

| 5.2  | Input offset voltage (Vio) with variation in the circuit temperature for selft = 0 and selft = 1                                             | . 49 |

| 5.3  | Simulation set up for input offset voltage measurements with DC source in non-inverting input.                                               | . 51 |

| 5.4  | Simulation set up for input offset voltage measurements with DC source in inverting input.                                                   | . 54 |

| 5.5  | Input Offset Voltage Error contribution by individual NPN device for the circuit configuration in fig.5.                                     | . 56 |

| 5.6  | Input Offset Voltage Error contribution by individual PNP device for the circuit configuration in fig.5.                                     | . 57 |

| 5.7  | Simulation set up for thermal analysis of CFOA                                                                                               | . 60 |

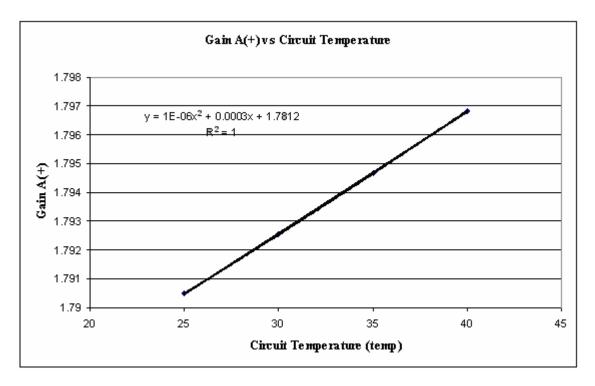

| 5.8  | Variation of CFOA gain during positive half cycle A(+) with overall circuit temperature when all the devices are with self heating turned on | . 61 |

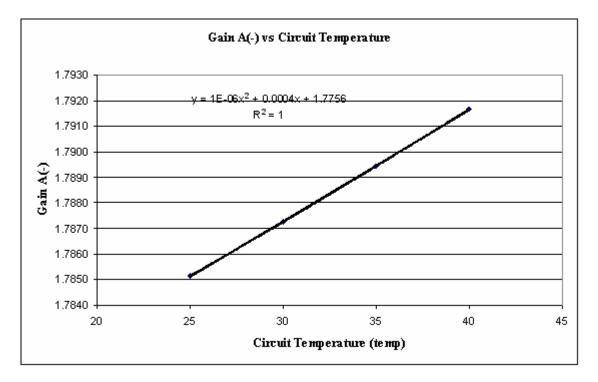

| 5.9  | Variation of CFOA gain during negative half cycle A(-) with overall circuit temperature when all the devices are with self heating turned on | . 62 |

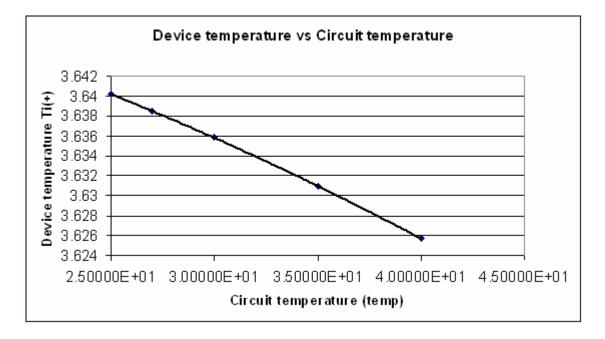

| 5.10 | Temperature variation of NPN2 device with circuit temperature when only NPN2 is turned on with self heating                                  | . 64 |

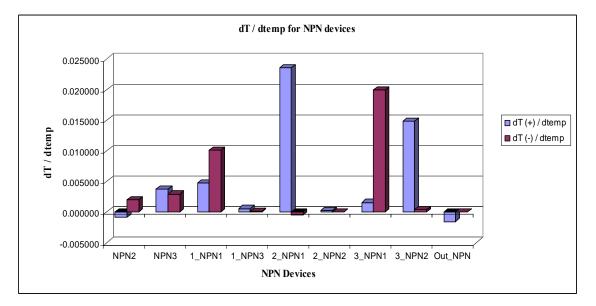

| 5.11 | dT / dtemp values for NPN devices during the positive and negative half cycle of input voltage                                   | 66 |

|------|----------------------------------------------------------------------------------------------------------------------------------|----|

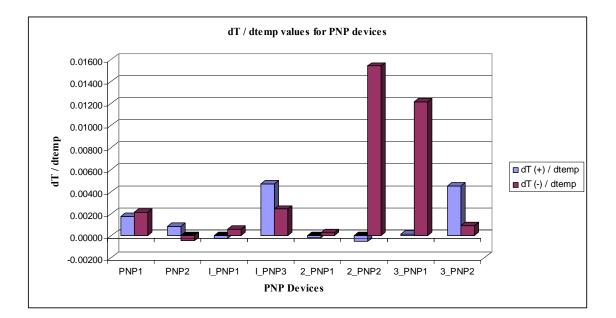

| 5.12 | dT / dtemp values for PNP devices during the positive and negative half cycle of input voltage                                   | 66 |

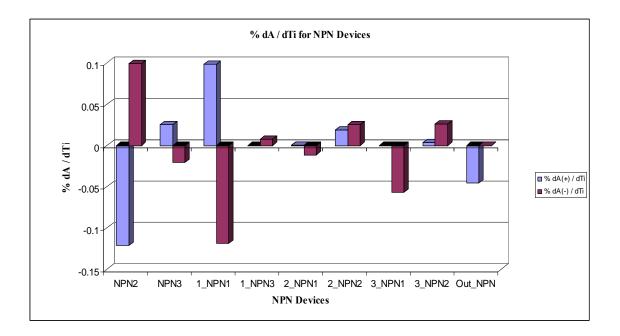

| 5.13 | Percentage Gain error due to variation of device temperature (NPNs), during positive and negative half cycle of input voltage    | 69 |

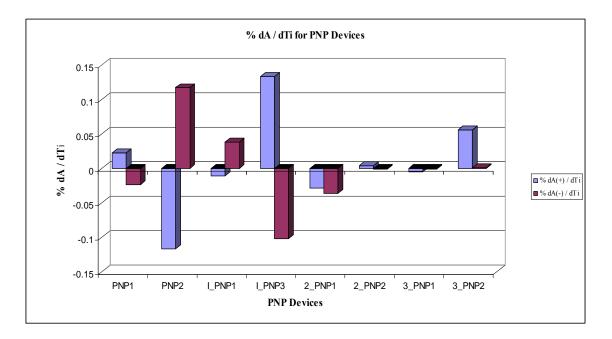

| 5.14 | Percentage Gain error due to variation of device temperature<br>(PNPs), during positive and negative half cycle of input voltage | 70 |

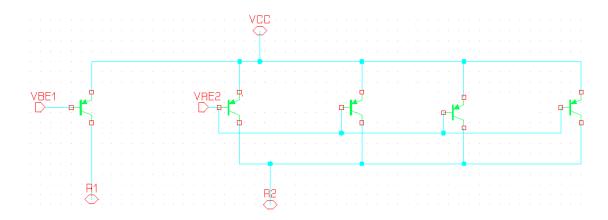

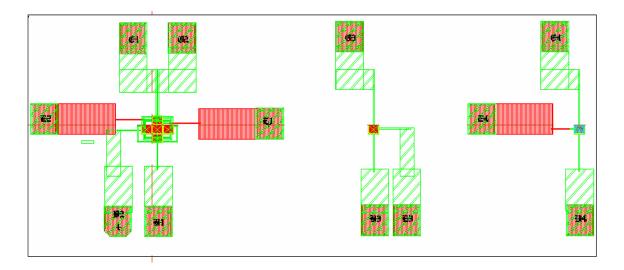

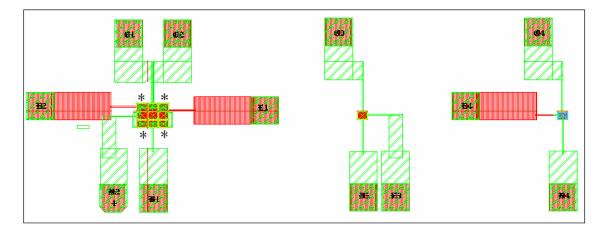

| 6.1  | Part of UTA 184 Schematic                                                                                                        | 72 |

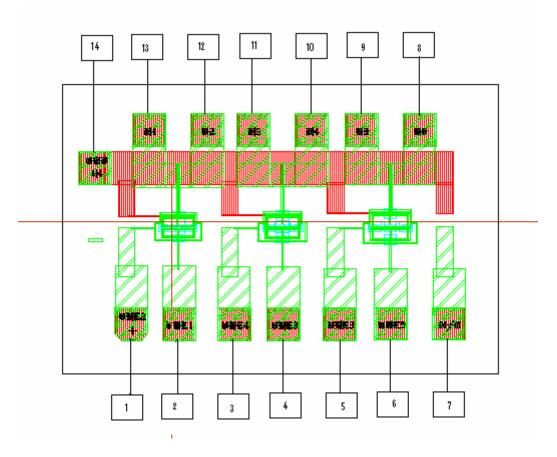

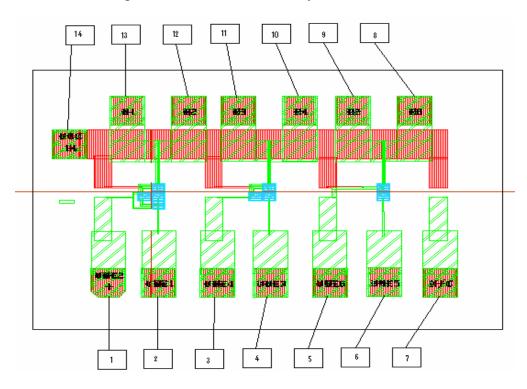

| 6.2  | Pin out with final layout for UTA 184                                                                                            | 73 |

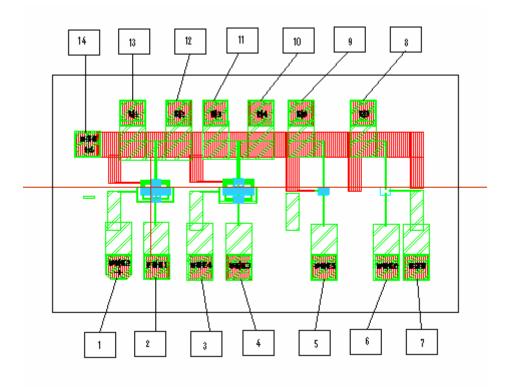

| 6.3  | Pin out with final layout for UTA 189                                                                                            | 74 |

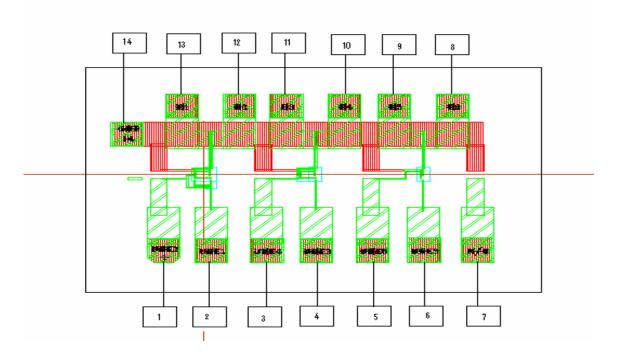

| 6.4  | Pin out with final layout for UTA 185                                                                                            | 75 |

| 6.5  | Pin out with final layout for UTA 190                                                                                            | 75 |

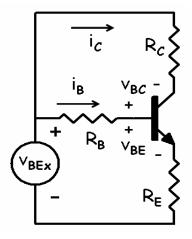

| 6.6  | Forward Gummel configuration for an intrinsic transistor with its Internal resistances                                           | 76 |

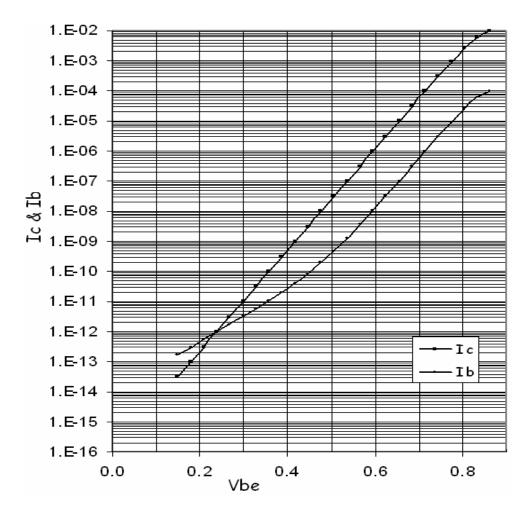

| 6.7  | Ideal forward Gummel plot                                                                                                        | 78 |

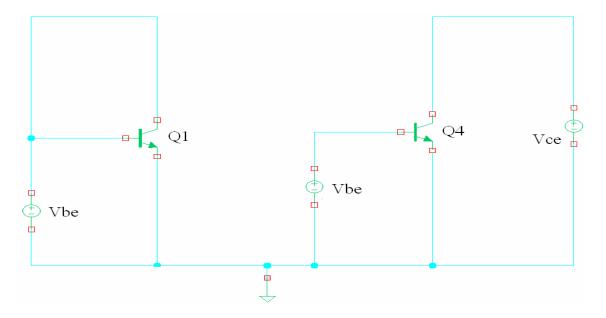

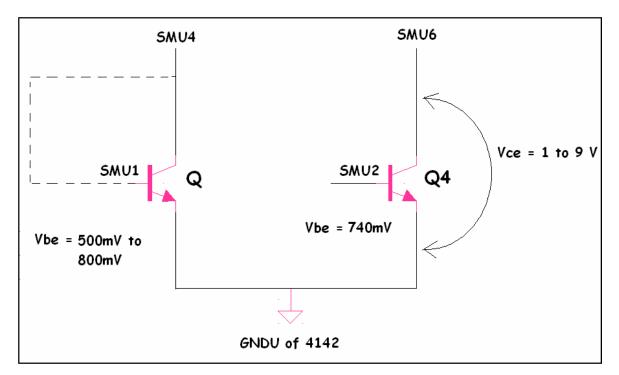

| 6.8  | Configuration for thermal coupling measurement                                                                                   | 79 |

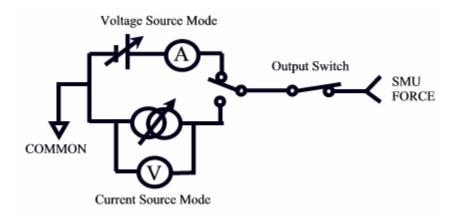

| 6.9  | Simplified SMU (Source/Monitoring Unit) Circuit Diagram                                                                          | 82 |

| 6.10 | Measurement set up showing the connections of SMUs and GNDU                                                                      | 84 |

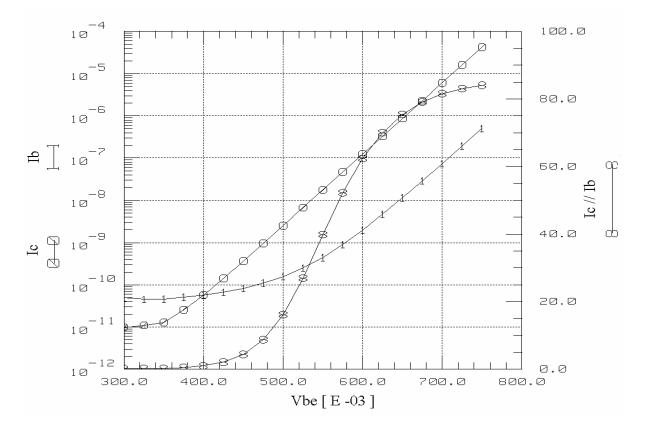

| 6.11 | Measured forward Gummel plot for the central device                                                                              | 88 |

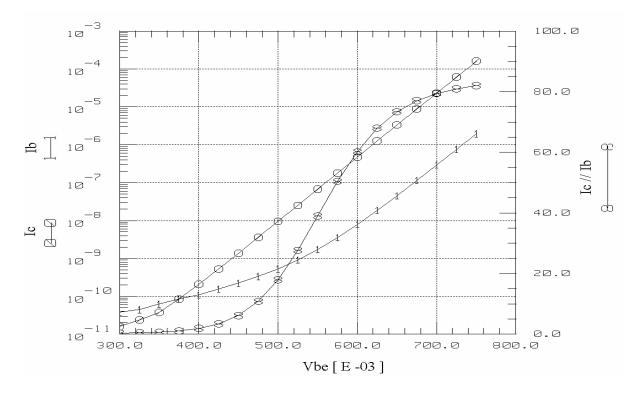

| 6.12 | Measured forward Gummel plot for the outer devices                                                                               | 89 |

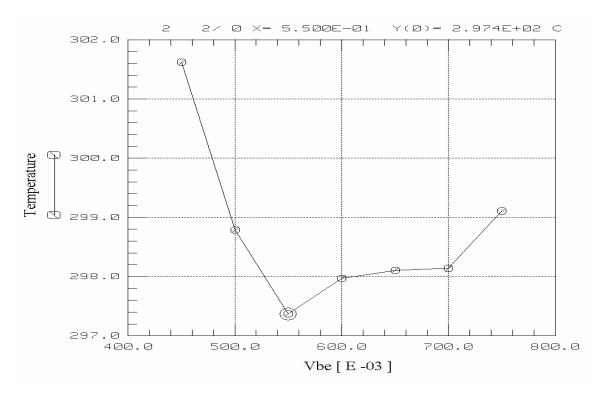

| 6.13 | Temperature of the central device with constant power on the outer devices                                                       | 90 |

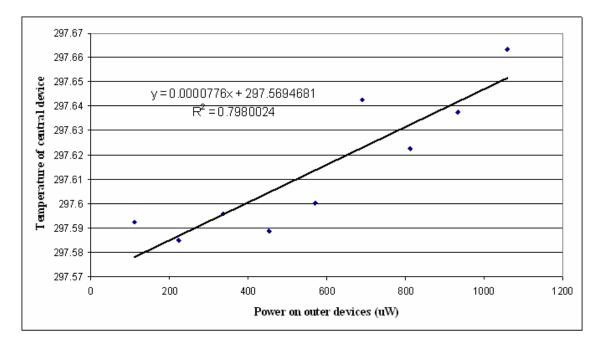

| 6.14 | Apparent temperature variation of the central device with increasing power on outer devices                                      | 92 |

# LIST OF TABLES

| Table |                                                                                                                   | Page |

|-------|-------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | VIP10 transistor parameters                                                                                       | . 8  |

| 2.2   | Thermal-Electrical Analogy                                                                                        | . 14 |

| 3.1   | Simulation results for CFOA with selftx = 0 and TREF = 25                                                         | . 27 |

| 3.2   | Simulation results for CFOA with selftx = 1 and TREF = 25                                                         | . 28 |

| 5.1   | Input offset voltage values with selft = 0 and selft = 1 for the schematic shown in fig.5.1                       | . 49 |

| 5.2   | Input offset voltage with a particular NPN device selft turned OFF for the circuit configuration shown in fig.5.3 | . 52 |

| 5.3   | Input offset voltage with a particular PNP device selft turned OFF for the circuit configuration shown in fig.5.3 | . 52 |

| 5.4   | Input offset voltage values with all devices turned ON and OFF                                                    | . 54 |

| 5.4   | Input offset voltage with a particular NPN device selft turned OFF for the circuit configuration shown in fig.5.4 | . 55 |

| 5.5   | Input offset voltage with a particular PNP device selft turned OFF for the circuit configuration shown in fig.5.4 | . 55 |

| 5.7   | dT/dtemp at 27 <sup>°</sup> C for NPN devices                                                                     | . 65 |

| 5.8   | dT/dtemp at 27 <sup>°</sup> C for PNP devices                                                                     | . 65 |

| 5.9   | Percentage Gain errors due to variation of device temperature,<br>for NPN devices                                 | . 68 |

| 5.10  | 0 Percentage Gain error due to variation of device temperature,<br>for PNP devices                                | . 69 |

| 6.1 | Features of HP 4142B                                         | 81  |

|-----|--------------------------------------------------------------|-----|

|     | Variation of apparent temperature of the central device with | 0.1 |

|     | power                                                        | 91  |

### CHAPTER 1

#### INTRODUCTION

Extensive research has been done to study the self heating of BJTs (Bipolar Junction Transistors). Positive feedback between collector current, Ic and the base emitter voltage (Vbe), in BJT results in the dissipation of power. This is the self heating of the BJT. If this thermal feedback is ignored, it can cause increase in the self heating effect of the transistor and the device can burn out. The dependence of the self-heating effect of the BJT on the base-emitter voltage and collector current has been developed [1]. Self heating of the BJT increases the temperature of the device above the ambient temperature. In the case of integrated circuits this localized power dissipation within different devices can cause chip temperature gradients and variations which strongly affect the performance of the overall circuit. The deviation in performance from the ideal case is important; particularly in cases where very high accuracy is required or where large power dissipation occurs on the chip. The effect of thermal feedback on various integrated circuits like operational amplifiers, voltage regulators and voltage references has been proved by Fukahori and Gray [2]

With the invention of advanced process technologies the device size is being scaled down and density of transistors on a given chip area is increasing rapidly. The thermal runway issue becomes more important and complex as the density of the devices on a chip and the operational speed of the ICs increase. In analog circuits the heat dissipation is continuous and operating characteristics of the devices are sensitive to temperature changes. Hence more accurate thermal analysis is required to study the thermal feedback phenomenon at the device level as well as at the circuit level.

With scaling of transistor geometries the current densities and thermal spreading resistance increase. As the density of the devices on a chip increases another thermal issue called 'inter-device thermal coupling' comes into the picture. For devices with high power densities and small separation distances, there can be a direct coupling between temperature rise in these devices and the temperature of neighboring devices. Thus the device with high power density heats up neighboring device in addition to its own self heating. This thermal coupling or inter-device heating depends on layout as well as operating conditions of the power device and the adjacent device. These factors do vary on a larger scale in circuits containing a large number of devices and can affect the performance of the overall circuit. Fukahori and Gray [2] showed that thermal coupling can profoundly affect the gain characteristics of an operational amplifier.

The temperature rise in a chip is basically because of the three different heat transfer mechanisms; a) Chip to package and package to an ambient thermal impedance b) Self heating in a device due to power dissipation and c) Thermal coupling between the neighboring devices. As mentioned previously the last two effects have greater impact on analog circuits and are the concentration of this thesis work. Thus, to model the thermal effects in analog circuits, it is necessary to study thermal modeling of discrete devices as well as IC chips. In addition to this it is necessary to model the

thermal coupling or inter-device heating phenomenon and implement the improved thermal model at the device level to include the self heating as well as the inter-device heating effects.

One way to consider the thermal effect of BJTs in analog circuits is to use simulators which provide access to model equations and modify the model equations [3, 4]. But in this approach it is necessary to change the model equations each time the layout and operating conditions of the devices change. It becomes tedious for circuits containing a large number of devices. Another approach to consider thermal effects is to use a coupled electro-thermal simulation [5]. This approach needs a large amount of change in source code of simulator or entirely new simulator design to solve the three dimensional heat equations.

Advanced process technologies have made it easier to fabricate a transistor using a trench isolation technique. Trench isolation is used to form isolation regions suitable for very fine features. In this isolation technique a very narrow and relatively deep trench is etched around the device to be isolated. The trench is filled with an insulating material like SiO<sub>2</sub>. Thus the device is surrounded on five sides by SiO<sub>2</sub>, which is a poor conductor of heat. Since the maximum heat flow occurs only through the interconnecting conductors, and the five sides offer high resistance to heat flow, these devices are affected the most from thermal heating. Hence these devices are used for studying the thermal effects.

National Semiconductor Corporation has developed a dielectrically isolated complementary bipolar process, VIP10. It is one of the members of National's VIP

(Vertically Integrated PNP) family of complementary bipolar processes. This VIP10 process is used for design of high speed, high performance analog circuits. Transistors in this process are used to design High-frequency Operational Amplifiers [6]. The schematic cross-section of a dielectrically isolated BJT (DIBJT) is shown in Figure 1.1. As seen from the cross-section, the insulating oxide, SiO<sub>2</sub> in this case, surrounds the transistor and restricts the heat flow in all directions except the top surface. Because of the thermal isolation it is necessary to study the thermal behavior of these particular transistors. It is also necessary to study the impact of thermal characteristics on the performance of circuits containing these devices.

Figure 1.1 Schematic cross-section of a DIBJT [Dielectrically Isolated Bipolar Junction Transistor]. The Emitter, Base and Collector (including sinker and buried layer) regions are isolated within the dielectric (Si0<sub>2</sub>) box. For forward-active operation, the heat generation region is primarily confined to the portion of the collector-base depletion region under the emitter [6]

The thermal analysis of DIBJT devices (using VIP10 process) and their impact on the performance variation of circuits like the Current Feedback Operational Amplifier (CFOA) containing these devices is the main focus of this thesis work. Various methods have been developed to characterize and measure the thermal resistance of the DIBJTs using VIP10 process [7]. This thesis is the continuation of the research work in the same area. Here the thermal effects have been considered at circuit level to find the main factors affecting the inter-device heating. Test structures are developed to study the effect of these factors at the device level. An innovative measurement technique is developed to measure the device temperature using IC-CAP / HP1B evaluation system. The inter-device heating effect has been studied for various layout and operating conditions of the device. Thermal analysis has been carried out to study the effect of change in circuit temperature as well as device temperature on gain-error and input offset voltage for the current feedback operational amplifier (CFOA). Profound study of these specifications of CFOA has been done to propose a possible relation between device level and circuit level thermal effects.

The VBIC model for the BJT is an improvement over the Gummel-Poon model since the VBIC model considers the thermal effects more accurately. Self heating effects are well simulated using the existing VBIC model, and it is used for simulation purposes in this work. Also attempts have been made to modify the VBIC model externally to consider the inter-device heating phenomenon.

#### CHAPTER 2

#### DIELECTRICALLY ISOLATED BIPOLAR JUNCTION TRANSISTOR (DIBJT)

Dielectrically Isolated Bipolar Junction Transistors (DIBJTs) developed by National Semiconductor Corporation using the VIP10 process are used for the thermal study. Thermal properties of a device depend on its geometry and boundary conditions. It is necessary to develop accurate techniques to characterize the thermal resistance depending on the geometry of the device. Hence it is essential to study the structure of the DIBJT. This chapter describes the structure of a DIBJT, various thermal definitions and the five element resistance model developed from the geometry consideration of these particular DIBJTs.

#### 2.1 Structure of DIBJT

Simplified schematic cross section of a Dielectrically Isolated Bipolar Junction Transistor is shown in figure 2.1. The National Semiconductor VIP10 process is a complementary bipolar process implementing NPN and PNP BJTs. VIP10 transistor cross section is shown in fig.2.2.

Figure 2.1 Schematic cross-section of a DIBJT [Dielectrically Isolated Bipolar Junction Transistor]. The Emitter, Base and Collector (including sinker and buried layer) regions are isolated within the dielectric (Si0<sub>2</sub>) box. For forward-active operation, the heat generation region is primarily confined to the portion of the collector-base depletion region under the emitter [6]

Figure 2.2 VIP10 Transistor Cross-section [8]

The active area is Silicon-On-Insulator (SOI) which is fabricated using the bonded wafer technique. This produces a buried oxide layer which isolates the bottom

of the epitaxial tubs, which are usually the collectors of bipolar transistors. P and N type buried layers are followed by epitaxial growth. Trenches are anisotropically etched into the silicon and filled to form the isolation sidewalls. Consequently the VIP10 transistor collectors are fully dielectrically isolated (DI) and have no P-N junction between the collectors and substrate or well. This reduces the parasitic collector-substrate capacitance [8]. The main transistor parameters for these DIBJTs using the VIP10 process are listed in table 2.1.

| Table 2.1 | VIP10 | transistor | parameters | [8] |

|-----------|-------|------------|------------|-----|

|           |       |            |            |     |

| NPN ft                    | 9 GHz    |

|---------------------------|----------|

| PNP ft                    | 8GHz     |

| ΝΡΝ β                     | 100      |

| ΡΝΡ β                     | 50       |

| NPN Va                    | 120      |

| PNP Va                    | 40       |

| Cjs                       | 0.005 pF |

| Emitter Width             | 1 um     |

| Maximum Supply<br>Voltage | 12 V     |

Complementary DIBJTs using the VIP10 process has the following advantages over other existing BJT processes [8]:

1. The collector-substrate capacitance in a DIBJT is less than that in a junction isolated BJT and hence has an increased amplifier frequency response.

- 2. The presence of oxide isolation obviates leakage currents otherwise found in junction isolated (JI) transistors.

- 3. The trench isolation eliminates large sidewall base collector junction capacitance.

- 4. The DIBJTs drastically reduces the area required for isolation.

- 5. The complementary process enables class AB output stages with very low quiescent current and high output drive in analog circuits.

- 6. The DIBJTs offers low collector resistance and reduced quasi-saturation effects.

- 7. Unlike MOSFET devices, DIBJTs combine low distortion, low power dissipation and frequency stability.

Because of the above listed advantages, designs using complementary bipolar transistors, offer the best combination of features required in high speed amplifiers: wide bandwidth, low power consumption, low supply voltages, large output swing, high output current and low distortion.

But the main drawback of the DIBJTs in this process is that they suffer from thermal issues since the trenches surrounding the device are filled with  $SiO_2$  which is a poor conductor of heat. Hence it is necessary to consider the different thermal effects affecting the performance of these particular transistors. Also it is essential to model and characterize the effect of thermal properties on the overall performance of designs using these devices. The basic thermal definitions and the analogy between thermal and electrical networks are discussed in the next section.

#### 2.2 Thermal Definitions

Self heating is the main cause for the heating of the BJT. Thermal coupling or inter-device heating also plays an important role in high density ICs.

#### 2.2.1 Self Heating:

Self heating is defined as the rise in the junction temperature of an emitter, which is caused by the transistor's own power dissipation. The heat generated elevates the temperature within the structure apart from the heating caused by the ambient temperature.

#### 2.2.2 Thermal Coupling or Inter-device Heating:

Inter-device heating is defined as the increase in the temperature of the device caused by power dissipation in neighboring devices. Among all other factors, the interdevice heating depends most on the number of neighboring devices, spacing between the devices and the power dissipation of the adjacent devices.

Heat generation and dissipation in a transistor depends upon two main parameters: a) The resistance of the material to heat flow and b) the amount of heat stored in the material. These are the two main parameters which should be characterized accurately.

#### 2.2.3 Thermal Resistance:

Thermal resistance is defined as the difference in temperature between two closed isothermal surfaces divided by the total heat flow between them.

Mathematically thermal resistance for a device can be expressed as

$$R_{th} = \frac{T_j - T_a}{P} \tag{2.1}$$

Where,

$T_i$  is the junction temperature

T<sub>a</sub> is the ambient temperature and

P is total heat flow rate.

$R_{th}$  is expressed in units of °K / Watt.

A complete heat flux network is necessary to study the three dimensional conduction of heat from a device's hot core to its outer surface. The heat flux network depends on the geometry of the body. Thermal resistance is specific to the heat flux network. Hence any change in the geometry of the device changes its thermal resistance. Electro-thermal simulations for the DIBJTs using the VIP10 process have been carried out to characterize the thermal resistance of these devices [9].

#### 2.2.4 *Thermal resistivity:*

Thermal resistivity is defined as the ratio of the thermal gradient to the heat flux density for one dimensional heat conduction. It is the property of the material indicating the resistance of the material to thermal conduction. It has units of KW<sup>-1</sup>cm<sup>-1</sup> and mathematically it can be expressed as

$$r = \frac{\frac{T_1 - T_2}{2}}{q} \quad . \tag{2.2}$$

where,

$T_1$  and  $T_2$  are the temperatures of the two isothermal surfaces,

x is thickness of the material separating the two isotherms, and

q is the heat flux per unit area.

#### 2.2.5 Thermal Capacitance:

Thermal capacitance,  $C_{th}$ , is a measure of how much heat energy can be stored and dissipated in a device. It is expressed in the units of J/K and in rectangular structure given as

$$C_{th} = \rho_s \times C_s \times w \times l \times d \tag{2.3}$$

Where,

$\rho_s$  is specific weight of the substance (kg/m<sup>3</sup>),

$C_s$  is specific heat capacity of the substance (Jkg<sup>-1</sup>K<sup>-1</sup>), and

w, l and d are width, length and thickness of the substance respectively in m.

#### 2.3 Thermal and Electrical analogy

From the above discussed thermal definitions, it is clear that the temperature rise  $\Delta T$  [°K], is given by the product of the power dissipated, P [W] and the thermal impedance,  $Z_{th}$  [°K / W] as

$$\Delta T = Z_{\rm th} * P \tag{2.4}$$

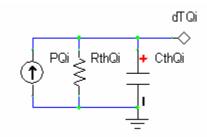

In the VBIC model thermal effects are modeled by implementing an additional thermal network as shown in fig 2.3. This thermal network models the interaction between electrical characteristics and thermal effects.

Figure 2.3 Additional Thermal Network in VBIC Model [10]

The above thermal sub-circuit with  $I_{th} = P * 1$  A/W and  $Z_{th} = Z_{th} * 1$  Ohm W/°K couples the instantaneous power dissipation in the device to the thermal network. Thus from equation (2.4) the voltage level of the temperature node t (called the dt node in the VBIC syntax) is numerically equal to the local temperature rise °K, which is used to calculate the instantaneous electrical characteristics of the BJT. The voltage at the temperature node can be written as

$$V_t = R_{th} * I \tag{2.5}$$

$R_{th} = R_{th} * 10 hm W/^{\circ}K$

Comparing equations (2.4) and (2.5), it is clear that the temperature rise in the thermal network is equivalent to the voltage rise in electrical networks. Similarly the heat flow, thermal resistance and thermal capacitance have their equivalent terms in an electrical network. Table 2.2 summarizes this analogy between thermal and electrical networks.

| Thermal             |                                     | Electrical  |               |

|---------------------|-------------------------------------|-------------|---------------|

| Temperature         | T in <sup>o</sup> K                 | Voltage     | U in V        |

| Heat flow           | P in W                              | Current     | I in A        |

| Thermal resistance  | R <sub>th</sub> in <sup>o</sup> k/W | Resistance  | R in V/A      |

| Thermal capacitance | C <sub>th</sub> in J/K              | Capacitance | C in Coul / V |

Table 2.2 Thermal-Electrical Analogy

#### 2.4 Five Element Thermal Resistance (Rth) Model for DIBJT

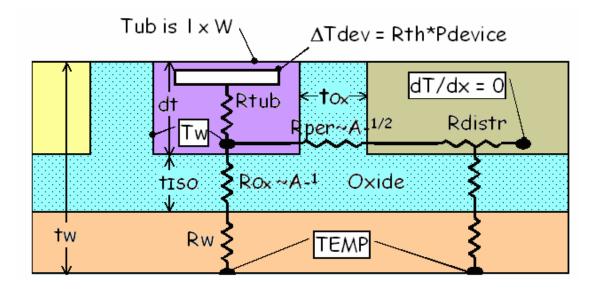

The total thermal resistance of the DIBJT shown in fig. 2.1 can be represented by a thermal network of five resistances as shown in fig.2.4. Each of these five resistances represent the thermal resistance of the particular part of the device and depends upon the geometry and the material in that region. Extensive analysis of different parts of this particular DIBJT has been carried out resulting in exact modeling of the thermal resistances and development of the five element resistance model as shown in fig2.4. This five element thermal resistance ( $R_{th}$ ) model has been used as a basis for the research work in this thesis.

Figure 2.4 Five Element Thermal Resistance (Rth) Model for DIBJT [6]

As can be seen from fig 2.4  $R_w$ ,  $R_{ox}$ ,  $R_{tub}$ ,  $R_{per}$  and  $R_{dist}$  constitute the main five thermal resistances for the DIBJT in VIP10 process. These represent the wafer, buried oxide, tub, peripheral and distributed resistance respectively. The total thermal resistance of the device can be approximately computed from these elements as

$$R_{th,device} \approx R_{tub} + \frac{1}{\left(\frac{1}{R_{ox} + R_{w}}\right) + \left(\frac{1}{R_{per} + R_{dist}}\right)}$$

(2.6)

The measured thermal resistance is given as

$$R_{th,meas} = \frac{1}{\left(\frac{1}{R_{th,device}}\right) + G_S}$$

(2.7)

where,

$G_s$  = effective shunt thermal conductance of interconnects on the top.

The overall thermal model with the inclusion of thermal resistance due to interconnects is shown in fig.2.5. This thermal model undergoes some changes while considering the inter-device heating. The following sections describe the changes in this model to accommodate the thermal coupling or inter-device heating.

Figure.2.5 Overall Thermal Resistance (Rth) model for DIBJT [6]

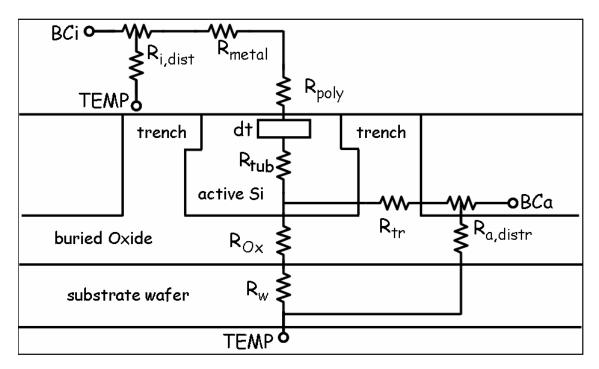

#### 2.5 Thermal model for inter-device heating or thermal coupling for DIBJT

The thermal network shown in fig2.5 can be used to model the self heating effect in a DIBJT. To accommodate change in thermal resistance due to thermal coupling or inter-device heating, this thermal network needs to be modified. As can be seen from figure 2.4, in case of thermal coupling, the wafer resistance  $R_w$ , oxide resistance  $R_{ox}$  and tub resistance  $R_{tub}$ , will still remain the same. The perimeter resistance  $R_{per}$  and distributed resistance  $R_{dist}$  are the resistances which need to be

modeled again. The values of these resistances depend upon various factors like the number of adjacent devices, amount of epitaxial coverage with trenches etc. Also it is essential to add the thermal resistance networks due to the shared interconnect and spacing between the adjacent devices. Device spacing, number of devices, shared interconnect etc. are not constant, but do vary with different designs and layout schemes. Hence it is necessary to model these resistances accurately. Fig.2.6 demonstrates the thermal network for two adjacent devices.

Figure 2.6 Modeling of Thermal Coupling between Two Adjacent Devices [6]

## 2.6 <u>Voltage controlled voltage source (VCVS) representation for inter-device</u> <u>heating or thermal coupling</u>

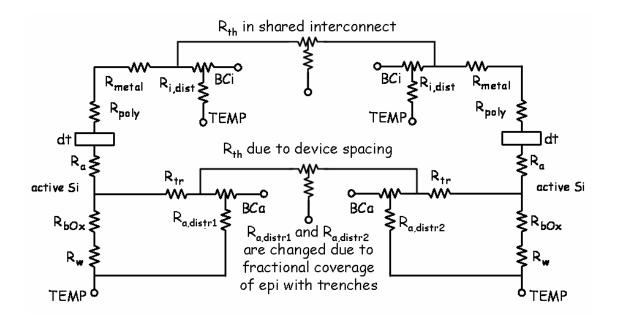

As mentioned in section 2.2 the VBIC model uses the thermal network shown in fig.2.3 to model the thermal effects due to self heating. The voltage at the't' node in fig.2.3 represents the temperature increase above ambient temperature. It is commonly referred as 'dt' node in Spectre simulator. This is explained in detail in chapter 3. To account for the additional rise in temperature due to thermal coupling, it is necessary to modify thermal network at the circuit level. This effect can be modeled by using a modified thermal network at the 'dt' node and voltage controlled voltage sources as explained with the following example.

Consider a single transistor Qi. The intrinsic VBIC model, used for modeling the self heating of this transistor in the absence of any other adjacent devices is shown in fig.2.7. RthQi and CthQi are the default Rth and Cth values for Qi in the VBIC model.

Figure 2.7 Intrinsic VBIC Model for Transistor Qi

Now consider a case when this transistor is surrounded by four other adjacent transistors Qj, Qk, Qm and Qn. The rise in temperature due to inter-device heating

among all these five transistors can be modeled by the "Extrinsic VBIC Thermal Model" [PC] shown in fig.2.8.

Figure 2.8 Extrinsic VBIC Thermal Model for Inter-Device Heating

In the above model the RthQiadj and CthQiadj are the respective Rth, Cth of device Qi in the presence of the devices Qj, Qk, Qm, and Qn. RthQi and CthQi are the values of Rth and Cth that are in the Qi default VBIC model. The inter-device heating effect is represented by the voltage controlled voltage sources (VCVS). The VCVSdtQj

has a gain of aij, where aij is the coupling coefficient for heating in device i due to dissipation in device j. The same is the case for the other transistors with the substitution of k, m, and n for j. There will also be a delay or phase shift associated with the gain of the VCVS. In practice, the node dtQi in fig.2.8 will connect to dTi in fig.2.7. Similarly the nodes dTQiadj, etc. will connect to their counterparts on adjacent devices. The resistance, -RthQiadj and capacitance, -CthQiadj are added at the dTi node to compensate for the default Rth and Cth values in VBIC model for the transistor Qi.

From the above discussion it is clear that to implement the "External VBIC Thermal Model" it is necessary to characterize the thermal coupling coefficients. To determine the values of thermal coupling, it is necessary to develop test structures with different layouts and measure the device temperature rise caused by thermal coupling. Chapter 6 describes the different test structures developed for temperature measurement and different measurement techniques for the same.

With the above background of self heating and thermal coupling, the next chapter will concentrate on different computer aided design (CAD) tools and techniques for modeling the VBIC temperature effects.

20

#### CHAPTER 3

#### CAD TOOLS & SIMULATION TECHNIQUES FOR MODELING TEMPERATURE EFFECTS

The previous chapters described the structure of a DIBJT and the various thermal effects which need to be considered. This chapter focuses more on simulating self heating and different techniques for the same.

The first section talks about the widely used VBIC model and its advantages over the Gummel-Poon model. The second section gives an idea about different simulators available for simulating self heating effect. Use of the VBIC model in SpectreS simulator within the cadence is presented in the third section. The last section illustrates the meaning of the different temperature related terms in the SpectreS simulator.

#### 3.1 Vertical Bipolar Inter Company (VBIC) Model

As mentioned in the previous chapter, the VBIC model has the advantage of incorporating the self heating effect which the Gummel-Poon model lacks. Hence it is widely used in simulators for simulating self heating. Fig.3.1 shows the equivalent circuit for the VBIC model. As can be seen it has an external thermal network and an excess phase network. The voltage at the't' node denotes the rise in temperature above the ambient temperature. The self heating effect is mainly modeled by the thermal

resistance,  $R_{th}$ , and thermal capacitance,  $C_{th}$ . The self heating effect can be turned off by substituting  $R_{th} = 0$  and  $C_{th} = 0$ .

Figure 3.1 Equivalent Circuit VBIC Model [10]

In addition to modeling the self heating effect, the VBIC model has following advantages over the Gummel-Poon model:

- 1. Improved early effect modeling, g<sub>0</sub>

- 2. Quasi-saturation modeling

- 3. Parasitic substrate transistor modeling

- 4. Parasitic fixed oxide capacitance modeling

- 5. Avalanche multiplication modeling

- 6. Improved temperature dependence modeling

- 7. Decoupling of base and collector currents.

Because of the above mentioned advantages and improved temperature modeling, the VBIC model has been used here for analysis and simulation purposes.

#### 3.2 Different CAD tools supporting VBIC model

The most widely used simulator tools are Hspice, Spectre, SpectreS and ADS. Among these Hspice and ADS have limitations on using the VBIC model for simulating thermal effects [12]. Following are the limitations of using Hspice and ADS with VBIC model:

- Hspice does not support PNP devices with 'dt' node. Thermal effects are not scaled with "Area" and "M" (multiplier factor) terms.

- 2. ADS does not have any temperature nodes and hence is unable to simulate thermal coupling effects.

Unlike Hspice and ADS, Spectre and SpectreS support both NPN and PNP devices with the VBIC model. Also in Spectre and SpectreS the thermal effects are scaled with "Area" and "M" terms [6]. Because of this, SpectreS is used in Cadence to simulate the thermal effects with the VBIC model.

#### 3.3 Use of VBIC model in Cadence SepctreS simulator

In a simulator, it is essential to implement an explicit external thermal node for BJT to 1) Observe the temperature of each device and 2) Implement the thermal coupling effect by the addition of voltage controlled voltage sources (VCVS) connecting the external nodes of the adjacent devices.

Considering the above facts a 6-terminal transistor symbol has been created for SpectreS simulations [11]. Fig.3.2 shows the same symbol.

Figure 3.2 The VBIC 6 Terminal Transistor Symbol for the SpectreS Simulator [11]

In the above symbol for the BJT the B, C, E and S nodes represent the base, collector, emitter and substrate terminals as in the case of a normal BJT symbol. The added 'tl' node is the local temperature node and the 'dt' node is the temperature rise above the local temperature caused by the thermal power dissipated by the device. The voltage at the 'dt' node indicates the rise in temperature of the device above the ambient (local) temperature. 1 Volt at the 'dt' node represents a 1 degree rise in temperature of the device above the ambient temperature.

The 'tl' node in the symbol is not necessary and can be removed from the symbol while doing the simulations for self heating. So the BJT symbol will have only five nodes, B, C, E, S and dt. This modified symbol has been used here throughout for the thermal simulations in SpectreS using Cadence.

In the VBIC mode the self heating is modeled by the model parameters RTH, CTH and SELFT. The self heating effect can be simulated by setting RTH and CTH equal to the thermal resistance and thermal capacitance of the device and SELFT is set equal to one. Similarly the design can be simulated without self heating by either setting RTH and CTH equal to zero or SELFT equal to zero.

This means that every time the self heating condition is changed it is necessary to make changes to these model parameters. To avoid the task of accessing the model files while changing the simulation condition from self heating to no self heating or vice versa, the following procedure was used for the thermal simulations:

- In the model file assign the model parameters RTH, CTH and SELFT as RTH = rthx \* (Value of thermal resistance for the device)

CTH = cthx \* (Value of thermal capacitance for the device)

SELFT = selftx \* 1

- 2. In the analog design environment edit the values of rthx and cthx equal to 1.

- To simulate the self heating, the value of selftx is edited as equal to 1 in analog design environment.

- Simulations with no self heating can be done by either editing the values of rthx and cthx equal to zero or by assigning selftx equal to zero in the analog design environment.

- 5. Any variable name can be used instead of rthx, cthx and selftx and can be edited respectively in the analog design environment. For simplicity these

variable names are used here throughout unless and until mentioned otherwise.

With the above basic knowledge of simulating the self heating effect in SpectreS, next section explains the different temperature related terms in Cadence SpectreS simulator.

### 3.4 Different temperature related terms

Various temperature related terms are used in the Cadence SpectreS simulator. These are mainly TREF, thom, temp and T. TREF is a SPICE term and is mentioned in the VBIC model file. T, thom and temp are the terms observed in the analog design environment. To know the exact significance of these terms, simulations were carried out with a current feedback operational amplifier (CFOA) with a circuit configuration as shown in fig.3.3. The simulations were carried out with and without self heating on and varying the above mentioned terms in sequence. Table 3.1 summarizes the simulation results with selftx = 0 and TREF = 25.

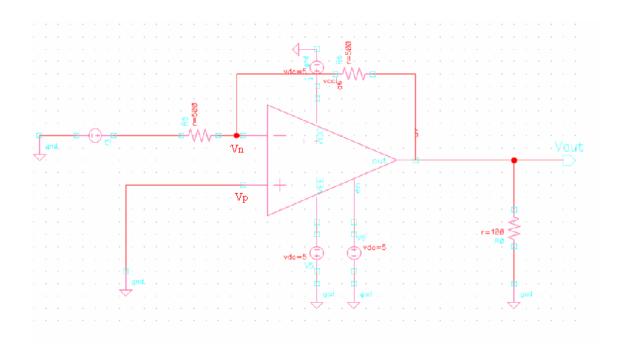

Figure 3.3 Schematic of CFOA used to verify different temperature related parameters in SpectreS

| Тетр | Tnom | Vout    |

|------|------|---------|

| 27   | 27   | 3.56946 |

| 27   | 25   | 3.56946 |

| 27   | 50   | 3.56946 |

| 25   | 27   | 3.56798 |

| 50   | 27   | 3.58935 |

Table 3.1 Simulation results for CFOA with selftx = 0 and TREF = 25

From the above simulation results it is clear that changing 'tnom' with const 'temp' does not have any affect on the output voltage (Vout), proving that 'tnom' gets overwritten by 'TREF'. The output voltage changes with a change in 'temp' with constant 'tnom' and 'TREF' which means that 'temp' represents the overall circuit temperature. By changing the value of 'temp' it was observed during the simulation that in analog design environment, 'T' takes the value of the 'temp' proving, 'T' also represents the overall circuit temperature.

Similar simulations were carried out with selftx = 1 and TREF = 25 and these are tabulated in table 3.2. These results also support the conclusions drawn from the selftx =0 simulations.

| Temp | Tnom | Vout    |

|------|------|---------|

| 27   | 27   | 3.59324 |

| 27   | 25   | 3.59324 |

| 27   | 50   | 3.59324 |

| 25   | 27   | 3.59167 |

| 50   | 27   | 3.61277 |

Table 3.2 Simulation results for CFOA with selftx = 1 and TREF = 25

The above conclusions can be summarized as follows:

- 1. 'TREF' is the temperature at which all the model parameters are calculated.

- 'temp' is the circuit temperature, meaning the temperature at which the overall simulation is carried out, and is available in the analog design environment for editing.

- 3. 'T' is same as 'temp' and can be seen at the top of analog design environment while the simulation is running.

- 4. 'tnom' is available for editing in the analog design environment and gets overwritten by the value of 'TREF'.

5. If 'TREF' is mentioned in the model file, editing 'tnom' in the analog design environment has no effect.

With this background of the CAD tools and simulation techniques used for modeling temperature effects, the next chapter presents the use of these simulation techniques. Thermal characterization of complex circuits such as the current feedback operational amplifier (CFOA) is demonstrated.

#### **CHAPTER 4**

# THERMAL CHARACTERIZATION OF CURRENT FEEDBACK OPERATIONAL AMPLIFIER (CFOA)

Current feedback operational amplifiers (CFOA) have higher slew rate, lower input referred noise, better differential gain and phase performance than the Voltage Feedback Operational Amplifiers (VFOA). Because of these advantages, the CFOA is being used mainly for automatic gain control and video signal processing applications. National Semiconductor has developed a current feedback architecture using an advanced complimentary bipolar process to meet a variety of industrial requirements. One of National's CFOA architectures has been used for the thermal study in this research work and is the main focus of this chapter. The first section describes the general topology of the CFOA. The motivation for the thermal study of the CFOA is presented in section two. The third section presents the thermal behavior of the devices constituting the particular CFOA. The last section gives an idea about the dependence of the thermal effects on different layout factors and the possible representation of these factors at the design or circuit level.

# 4.1 General Current Feedback Operational Amplifier (CFOA) topology

The general schematic of a typical modern complementary bipolar high speed current feedback operational amplifier (CFOA) is shown in fig.4.1. The basic architecture consists of a unity gain input buffer, a current mirror gain stage, and a unity gain output buffer.

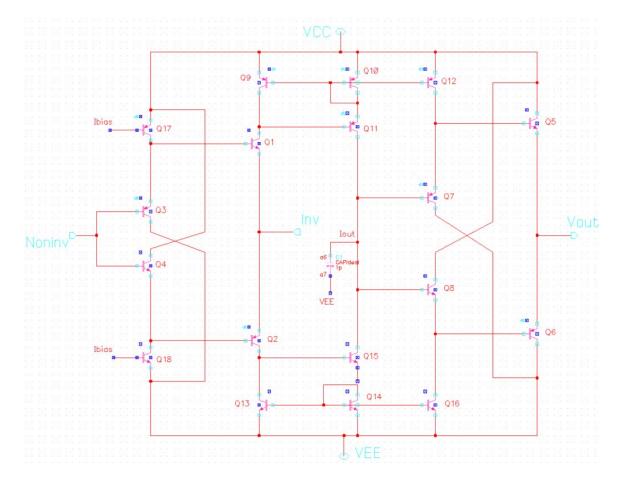

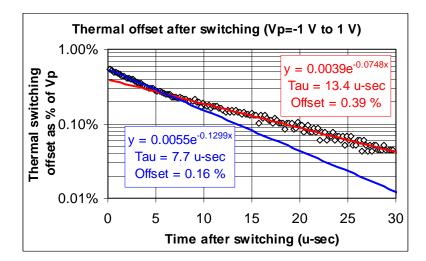

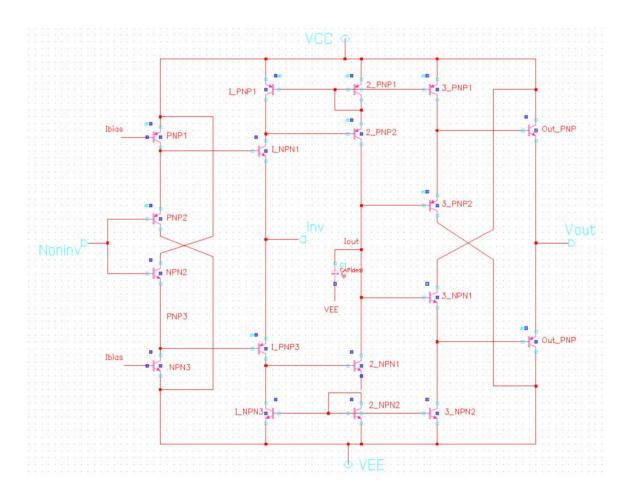

Figure 4.1 General Schematic of typical high speed complementary bipolar CFOA [13]

Complementary emitter followers Q1-Q4 form the input buffer. Collector currents of transistors Q1 and Q2 are turned around and summed through Wilson current mirrors formed by Q9-Q11 and Q13-Q15 respectively. This signal current injected into the high impedance node sets the open loop gain of the amplifier. The output buffer is formed by Q5-Q8. This output buffer provides nearly unity voltage gain and isolates the high impedance current summing node from the amplifier node. The single gain stage architecture provides high bandwidth at the expense of open loop transimpedance. The loss of dc accuracy is usually acceptable in high-speed applications in which these amplifiers are used [13].

Almost all complementary bipolar high-speed CFOAs are a variation of the basic architecture described above and employ some variations to meet different design specifications as well as characteristics of the fabrication process. The particular CFOA used here for the thermal study has architecture similar to the one shown in fig.4.1 with some specific variations to meet fabrication process characteristics. Since this CFOA is actually used by National Semiconductor, its exact architecture is not shown here. However the schematic in fig.4.1 is a functional equivalent for the same and will be used henceforth. Thermal analysis is carried out for all devices in the original CFOA design, but will be discussed here for Q1 to Q18 as mentioned in fig.4.1.

#### 4.2 Need for the thermal study of CFOA

The devices used in this CFOA are dielectrically isolated BJTs (DIBJT). As discussed in previous chapters, these are the devices which are most affected by thermal

effects. So this is a good design to study how the device level thermal effects affect the overall circuit performance when they are used as the building block for the circuit. The primary study of this particular CFOA showed that the percentage output error varies with time for an initial period of a few microseconds. When simulated this CFOA with self heating ON for all the devices, it showed a time varying thermal offset shown in figure 4.2. The thermal offset is same as the time dependent gain error and is defined as  $TO = Thermal Offset (\%) = (dV(t) - dV(settled value)) \times 100$  (4.1)

where,

$dV = \frac{Vout - A \times Vin}{A \times Vin}$  t is the time since the switching transition and A is the closed

loop gain of the amplifier.

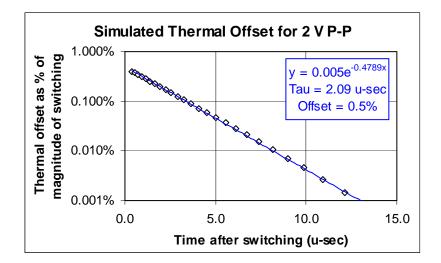

From figure 4.2 it can be observed that the thermal offset immediately after switching is 0.5% with a time-constant of 2.09 microseconds. The time constant is consistent with the, Rth\*Cth product, thermal characteristic time of the devices.

The measurement data taken for the same CFOA is shown in figure 4.3. It shows the measured data for the thermal offset vs time for a Vin transition from -1V to +1V [14].

Figure 4.2 Simulation plot of log of TO vs. time for CFOA [14]

Figure 4.3 Measured TO data for the CFOA on a 2V P-P (-1 to +1) transition [14]

Comparing fig.4.3 with fig. 4.2 it is clear that the simulation and the measured data have approximately the same initial offset error of 0.5%. But the measured data shows two significant time constants, a short time constant of 7.7 microseconds with initial offset of 0.16% and a longer time constant of 13.4 microseconds with a 0.39%

initial offset. This complex time constant response is the main motivation for the detailed thermal characterization of the CFOA. Following are the some of the initial hypothesis made to accommodate the complex time constant:

- 1. The difference in the time constant is because of the different thermal response of the devices forming various stages of the CFOA.

- 2. Considering the layout it can be predicted that the short time constant may be because of the devices on the non-inverting terminal and the longer time constant may be because of the devices forming the inverting input, high impedance node and the output buffer.

- 3. The thermal response of the device, surrounded by the adjacent devices, may be different from that of an isolated device.

- 4. A different time response of the heat flow from the tub than that through the trench oxide.

- 5. Also the absence of the complex time constant response in the simulation results gives some idea about the ineffectiveness of the existing VBIC model to consider additional complex thermal heating effects like thermal coupling, other than self heating and hence needs to be improved or modified.

To prove the above hypothesis, it is necessary to study the thermal behavior of the CFOA in depth. The thermal study needs to be done for all the devices constituting the CFOA to figure out how the device level thermal effects exactly affect the circuit performance. This study needs to be done in a systematic manner so as to analyze the

contribution of each stage in the design, towards the overall thermal time constant. It is also essential to study the layout of the particular CFOA to know the position of each device in the layout, to observe the dependence of device position in a layout, on its thermal response. The next section presents the thermal response of all the devices in the CFOA using the cadence SpectreS simulator.

#### 4.3 Thermal response of the devices constituting the CFOA

To study the effect of each device on the thermal response of a CFOA it is necessary to know the power dissipation and temperature rise above the ambient temperature for all devices. This section describes the simulations carried out to obtain this data with self heating on. The initial analytical observations drawn from this data are mentioned at the end of this section. As mentioned in section 4.1, figure 4.1 is used to represent the particular CFOA and to analyze results stagewise the transistors were named as shown in fig.4.4 where the following nomenclature mentioned in 4.3.1 is used to differentiate various stages of the CFOA.

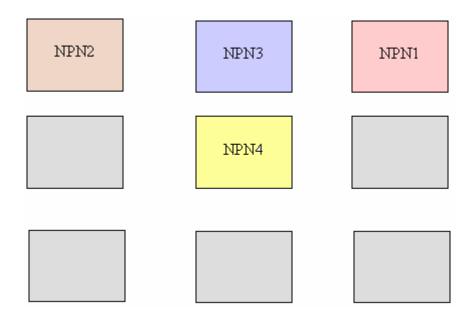

#### 4.3.1 Nomenclature used for CFOA

Basically the CFOA is divided into five main branches each called a stick. The leftmost non-inverting branch is called stick0 and the rightmost branch is denoted as stick4 or the output stick. To differentiate among all the devices on these particular sticks, the transistors on these are named as follows:

NPN and PNP on stick0 (Non-inverting input) is denoted as normal NPN and PNP NPN and PNP on stick1 (Inverting input) is denoted as I\_NPN and I\_PNP NPN and PNP on stick2 is denoted as 2 NPN and 2 PNP

NPN and PNP on stick3 is denoted as 3\_NPN and 3\_PNP

NPN and PNP on stick4 or output stick is denoted as Out\_NPN and Out\_PNP

This convention is used throughout the CFOA analysis and is demonstrated in figure 4.4.

4.3.2 Thermal Simulations

The VBIC model was used to simulate the self heating effects in the Cadence SpectreS simulator. A 2V peak to peak square wave input with rise and fall times of 40 nsec.and a pulse width of 50 µsec with a 50% duty cycle was used for the simulation as shown in figure 4.5. The CFOA was simulated with 'selft' turned on for all the devices.

Figure 4.4 General Schematic of CFOA Showing the nomenclature used for devices on different sticks

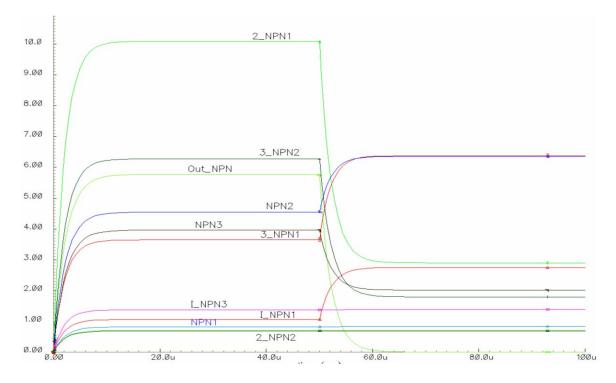

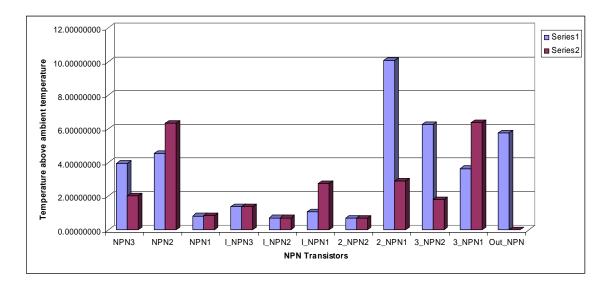

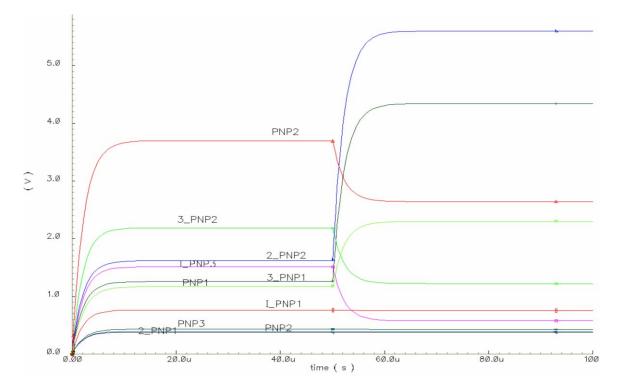

As mentioned in previous chapters the voltage at 'dt' of the device represents the increase in temperature above ambient temperature for the particular device. In this design 'dt' nodes of all the transistors were available, since the 6 terminal transistor symbol described in chapter 3 was used. The 'dt' nodes were labeled the same as the transistor names. The transient response of the voltage (which is equivalent to a rise in temperature) at these 'dt' nodes for NPN and PNP devices is shown in fig.4.6 and 4.8 respectively. The bar graph showing the temperature rise of each device during the positive half cycle and the negative half cycle for the NPN and PNP devices is shown in fig.4.7 and 4.8 respectively.

Figure 4.5 Simulation set up for thermal analysis of CFOA

As can be seen from fig. 4.6 and 4.7 each device in the CFOA heats up in a distinct way because of its self heating and exhibits a different thermal response than any of the other devices. Also the thermal response for a particular device differs for the positive half cycle and negative half cycle.

Figure 4.6 Transient response of the voltages at 'dt' nodes of all NPN devices in CFOA with 'selft' on for all devices

Figure 4.7 Final temperatures at 'dt' nodes of all NPN devices in CFOA with 'selft' on for all devices

Figure 4.8 Transient response of the voltages at 'dt' nodes of all PNP devices in CFOA with 'selft' on for all devices

Figure 4.9 Final temperature at 'dt' nodes of all PNP devices in CFOA with 'selft' on for all devices

•

From the analysis of different graphs shown in figures 4.6 to 4.9 along with the CFOA design study, the following primary results were obtained:

- The maximum temperature rise was observed on transistors 2\_PNP2 and 2\_NPN1. These are the transistors on the high impedance stick and carry almost twice the current than that in the inverting terminal.

- 2. Transistors NPN2 and PNP2 have significant rise in temperature and the difference between the rise in temperature during the positive and negative half cycles of the input is less than the other transistors in the CFOA. This confirms that these transistors do not cool down as fast the other transistors.

- 3. The CFOA output is a class AB stage. The output NPN transistor carries all the current during the positive half cycle and the PNP during the negative half cycle. Since the power dissipation and hence the self heating is directly proportional to the current, the same trend can be observed in the temperature rise of these devices during the positive and negative half cycle of the input.

- 4. Even though the output stage carries the maximum current, the temperature rise in the output devices were not observed to be the highest among all devices. The main reason for it is that each output transistor has 10 transistors in parallel. In other words, the area of each output device is 10 times the area of single device. Since the thermal resistance scales inversely to the area of device, the temperature rise for these devices is less than other devices in the CFOA.

From the above discussion, it can be concluded that the transistors on the noninverting terminal, NPN2 and PNP2 and transistors on the high impedance stick, 2\_PNP2 & 2\_NPN1 are the ones, which heat up significantly and can be the primary cause of the complex time constant and offset error.

#### 4.4 Layout study of the CFOA

As mentioned in section 4.2, the complex time constant response of the CFOA might result from the thermal delay caused by different stages of the CFOA. To study the exact cause for this thermal delay, it is necessary to know the way all the devices are laid out in the CFOA. This section talks about the overall layout study of the CFOA. As mentioned before due to proprietary concerns the layout is not shown here.

A detailed layout study of the CFOA shows that the devices on the noninverting terminal are laid close to each other. The NPN devices on stick1 to stick3 are contiguous as compared to any other NPN devices in the CFOA. The output devices are far away from the input stick and separated from each other. This particular layout style might be the reason for the complex time constant. The shorter time constant may be caused by the devices on non-inverting input terminal. Since the devices on stick1 to stick3 are separated from each other by a minimum spacing (2 um) available for this technology, these devices which could experience thermal coupling in addition to self heating, and contribute towards the longer time constant. Also as observed from the thermal simulations in section 4.3.2, the 2\_NPN1, NPN device on stick2, heats up the most. This device was surrounded by three neighboring devices with a minimum spacing of 2 um between shared walls. The geometry of these particular devices on layout is represented in fig. 4.10. This structure was the motivation for the design of the test structure for studying the thermal coupling and will be explained in more detail in chapter 6.

Figure 4.10 Part of Layout representation for the devices on stick1, 2 & 3

Also it can be observed from fig.4.10 that the device is not square in shape, having the same dimensions for all the sidewalls. Rather it is rectangular with two small sidewalls and two larger sidewalls. Since heat flow is directly proportional to the area of the surface, the heat flow through all the sidewalls is not the same. As the heat flow varies with the device sidewalls, thermal coupling must also vary with the sidewalls as well as the spacing between two adjacent devices. The maximum thermal coupling will be for the devices with minimum spacing. Thus the layout study gives an insight into the geometry of the devices and the different possible ways to lay out the design. It also gives an idea about the possible causes for the complex time constant. In addition to all these points this layout served as the main motivation to develop test structures for the study of the thermal coupling between adjacent devices.

As mentioned above, layout dependant factors like thermal coupling contributes towards the overall circuit performance and varies with variation in the layout. The existing VBIC model for the BJT does not have any model parameter to model these effects. Hence it is essential to make changes in the model file or develop circuit level modifications to accommodate these effects. The second approach is easier than the first, since with the first one different model files will have to be used as the layout changes. The circuit level change involving modification of the existing VBIC model, as mentioned in chapter 2, will be easier and needs to be verified with this particular CFOA design.

With this understanding of thermal simulations along with the layout study of the CFOA, the next chapter explains in-depth characterization of off-set error and gain error for this particular CFOA.

#### **CHAPTER 5**

# THERMAL CHARACTERIZATION OF OFFSET AND GAIN ERROR FOR CFOA

As observed in chapter 4, measurement results for the particular CFOA under study showed a variation in the thermal offset with switching time. This thermal offset basically involves time dependent gain error change. At first sight the main reason for gain error comes from unbalanced components resulting in input offset voltage. It is essential to study the change in time dependent gain error as well as the change in input offset voltage with self heating. Also, in-depth analysis needs to be done to know the contribution of each device. This enables design and layout engineers to implement modifications in order to overcome these errors. Comprehensive analysis of these errors for the CFOA was carried out in this research work and is presented in this chapter. The first and second section of the chapter presents the thermal characterization of the input offset voltage of CFOA. Time dependent gain error analysis is described in the last section of the CFOA.

# 5.1 Input offset voltage (Vio) variation with temperature

#### 5.1.1 Input offset voltage (Vio)

The differential input voltage that exists between two input terminals of an operational amplifier without any external inputs applied is called the 'input offset voltage' and is denoted by Vio. In other words, the input offset voltage is the amount of the input voltage that should be applied between two input terminals in order to force the output voltage to zero.

#### 5.1.2 Thermal Voltage Drift

The most serious variation in the value of Vio is due to the change in temperature. The average rate of change of input offset voltage per unit change in temperature is called 'thermal voltage drift' and is denoted by dVio / dT. As mentioned in chapter 3, circuit temperature is denoted by 'temp' in the SpectreS simulator. Hence thermal voltage drift will be denoted as dVio / dtemp.

Thermal voltage drift is not a constant value. It is not uniform over a specified operating temperature range. Furthermore, the value of the input offset voltage may increase or decrease with increasing temperature. Since the input offset voltage is one of the possible contributors to gain error, it is important to study the behavior of the thermal voltage drift.

# 5.2 Different Circuit Configurations for input offset voltage simulations

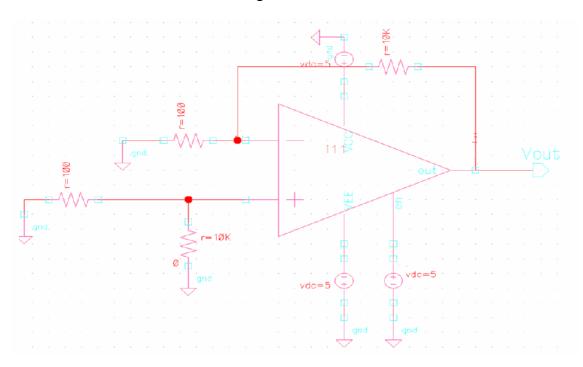

To study the thermal voltage drift of the CFOA under study, it is connected in closed loop with a gain of 101 as shown in fig.5.1. In this particular configuration, it is made sure that the resistors used in the non-inverting and inverting terminals have same ratio in order to eliminate errors arising due to resistance difference.

Figure 5.1 Closed loop CFOA configuration for Vio simulations

The above schematic was simulated with selft ON as well as OFF for all the devices over a circuit temperature range of  $25^{\circ}$  C to  $40^{\circ}$  C. Input offset voltage was calculated for each temperature as (Vout / 101). Table 5.1 lists the values of input offset voltages at different circuit temperatures.

| Circuit<br>Temperature | selft = 0 | selft =1 |

|------------------------|-----------|----------|

| Temp                   | Vio       | Vio      |

| 25                     | 0.00089   | 0.00242  |

| 27                     | 0.00086   | 0.00241  |

| 29                     | 0.00084   | 0.00239  |

| 31                     | 0.00081   | 0.00238  |

| 33                     | 0.00079   | 0.00236  |

| 35                     | 0.00077   | 0.00234  |

| 37                     | 0.00074   | 0.00232  |

| 39                     | 0.00072   | 0.00231  |

| 40                     | 0.00071   | 0.00230  |

Table 5.1 Input offset voltage values with selft = 0 and selft = 1 for the schematic shown in fig.5.1

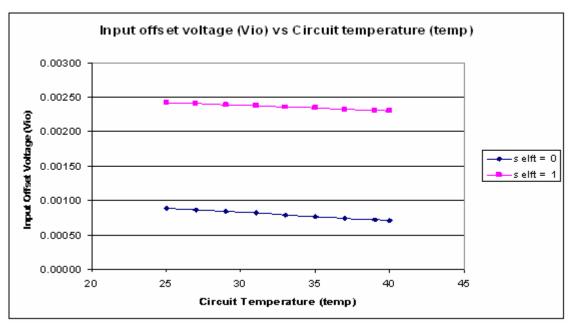

A graph showing the variation of the input offset voltage with overall circuit temperature is plotted in figure 5.2.

Figure 5.2 Input offset voltage (Vio) with variation in the circuit temperature for selft = 0 and selft = 1

It was observed from the plot of fig.5.2 that the input offset voltage varies with circuit temperature. It can also be seen that self heating changes the value of the input offset voltage from its value when all the devices are turned OFF with self heating. This analysis clearly showed that thermal voltage drift not only depends upon the circuit temperature but is also a function of device temperature.

It was observed that offset voltage changes with change in the resistor values in the inverting and non-inverting terminals, even when the ratio is maintained same. Thus this method of finding the offset voltage does not prove to be the accurate one. Also, since the thermal offset analysis and measurements done before were with resistances of 500  $\Omega$  in the feedback as well as in inverting input terminal, the offset voltage analysis should be done with these values of resistors. Hence to improvise the offset voltage results the schematic shown in fig.5.3 was used for simulation purposes. In this method of finding the input offset voltage, the input voltage is inserted in the non-inverting terminal and varied to make the output voltage at both input nodes denoted by Vp and Vn were noted down. The voltage difference (Vp – Vn) between these input nodes is the input offset voltage.

As observed in the previous analysis, the thermal drift voltage depends on the device temperature. To study the contribution of each device temperature variation to the input offset voltage change, self heating was turned ON for all devices except a particular device. This can be obtained by globally turning selft ON for all devices and

turning it OFF for a particular device while carrying out the input offset voltage simulations.

Figure 5.3 Simulation set up for input offset voltage measurements with DC source in non-inverting input

In the first case, for which all transistors are turned ON with self heating, voltage values at the Vp, Vn nodes are -0.00129 V, 0.00068 V respectively. The input offset voltage, which is a difference between the two node voltages is -0.00197 V. The input offset voltage in this case shows the offset voltage contributed by all the devices.

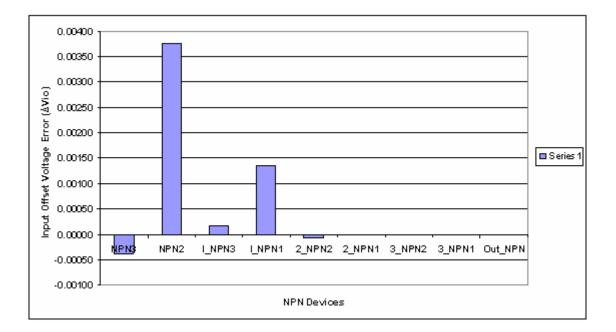

In the second case only one particular device selft was turned OFF. In this case the voltages at the Vp and Vn nodes were observed and the input offset voltage was calculated as the difference between these voltages for all the devices. Table 5.2 and 5.3 list the input offset voltage values with a particular device selft turned OFF at one time. Assuming the superposition for overall input offset voltage, the difference between the input offset values in the first case and the second case ( $\Delta$ Vio) gives the contribution of the particular device towards the offset voltage due to self heating. The value of  $\Delta$ Vio (Input offset voltage error) is also included in table 5.2 and 5.3 for each device.

| Transistor | Vp       | Vn      | Vio      | ΔVio     |

|------------|----------|---------|----------|----------|

| NPN3       | -0.00167 | 0.00068 | -0.00235 | 0.00038  |

| NPN2       | 0.00250  | 0.00070 | 0.00180  | -0.00378 |

| I_NPN3     | 0.00029  | 0.00208 | -0.00180 | -0.00018 |

| I_NPN1     | 0.00007  | 0.00068 | -0.00061 | -0.00136 |

| 2_NPN2     | -0.00206 | 0.00000 | -0.00206 | 0.00009  |

| 2_NPN1     | -0.00132 | 0.00066 | -0.00198 | 0.00001  |

| 3_NPN2     | -0.00140 | 0.00059 | -0.00199 | 0.00001  |

| 3_NPN1     | -0.00129 | 0.00069 | -0.00197 | 0.00000  |

| Out_NPN    | -0.00129 | 0.00068 | -0.00197 | 0.00000  |

Table 5.2 Input offset voltage with a particular NPN device selft turned OFF for the circuit configuration shown in fig.5.3

It can be seen that the input offset voltage Vio and input offset voltage error  $\Delta$ Vio changes are very small. Hence simulations for the same need to be carried out with high accuracy.

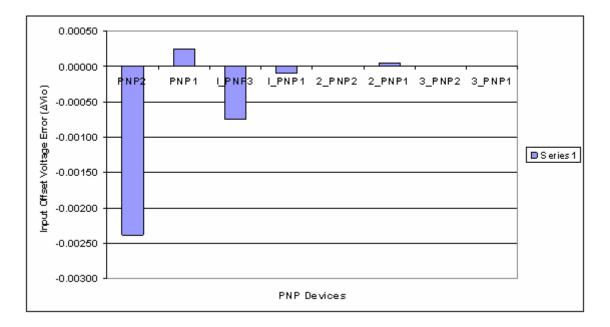

Table 5.3 Input offset voltage with a particular PNP device selft turned OFF for the circuit configuration shown in fig.5.3

| Transistor | Vp       | Vn       | Vio      | ΔVio     |

|------------|----------|----------|----------|----------|

| PNP2       | -0.00367 | 0.00069  | -0.00436 | 0.00239  |

| PNP1       | -0.00105 | 0.00068  | -0.00173 | -0.00024 |

| I_PNP3     | -0.00206 | 0.00067  | -0.00273 | 0.00076  |

| I_PNP1     | -0.00219 | -0.00012 | -0.00208 | 0.00010  |

| 2_PNP2     | -0.00181 | 0.00078  | -0.00259 | 0.00061  |

| 2_PNP1     | -0.00086 | 0.00106  | -0.00193 | -0.00005 |

| 3_PNP2     | -0.00131 | 0.00067  | -0.00198 | 0.00000  |

| 3_PNP1     | -0.00123 | 0.00074  | -0.00197 | -0.00001 |

| Out_PNP    | -0.00129 | 0.00068  | -0.00197 | 0.00000  |

Careful analysis of the figure 5.3 indicates that at the amplifier input terminals, node Vp and Vn, there will be an input differential signal, since the non-inverting terminal is not grounded. In addition to the input offset voltage this small input differential signal will be amplified by the amplifier's closed loop gain. Hence the output is equal to the closed loop gain times the summation of input offset voltage and small differential input signal. Hence the results obtained for the input offset voltage with this circuit configuration are not accurate.

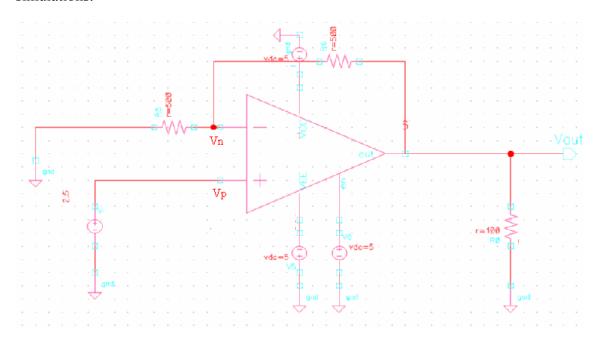

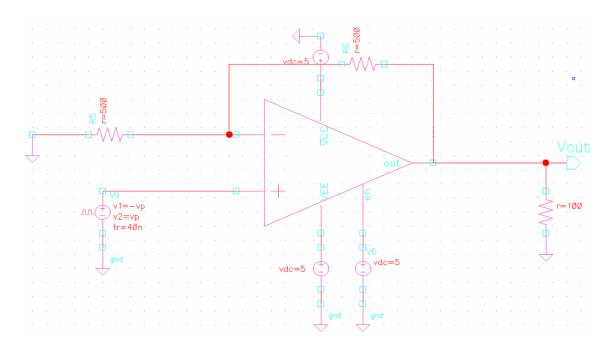

To overcome the problem of small input differential voltage observed with the circuit configuration of figure 5.3 an improved circuit as shown in fig.5.4 is used. In this arrangement the input voltage source forcing the output to zero is placed in the inverting terminal with the non-inverting terminal grounded. With this arrangement, the non-inverting terminal is grounded and since the inverting input terminal is at virtual ground the problem of additional input differential input signal gets resolved.

Figure 5.4 Simulation set up for input offset voltage measurements with DC source in inverting input

With this configuration, the input offset voltages are found for two cases; first with all devices selft turned ON and the second with all devices selft turned OFF. The input offset results for these two cases are tabulated in table 5.4. In this circuit configuration, since the non-inverting terminal is grounded, the input offset voltage is equal to the voltage at the Vn node with the opposite polarity. From table 5.4 it is confirmed that the offset voltage varies with variation in device temperature or self heating.

Table 5.4 Input offset voltage values with all devices turned ON and OFF.

| Selft for all devices | Vio      |