# INVESTIGATION ON THE MECHANISM OF INTERFACE ELECTROMIGRATION(EM) IN COPPER(Cu) THIN FILMS

by

### JEE YONG KIM

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

## DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT ARLINGTON

December 2006

Copyright © by Jee Yong Kim 2006

All Rights Reserved

#### ACKNOWLEDGEMENTS

I deeply appreciate my supervisor, Dr. Choong-Un Kim for his guidance during the course of this research, tireless enthusiasm for research and numerical technical discussions.

In addition, special thanks are extended to the other committee members Dr. Pranesh Aswath, Dr. Seong Jin Kho, Dr. Yaowu Hao and Dr. Alex Weiss for their thoughtful questions and valuable feedback.

I would like to thank Prof. Jaegab Lee and Prof Ji Young Kim, have been a mentor since my school life at Koomin University and will remain forever.

Another group of people that have assisted me throughout includes my colleagues: Dr. Nancy Michael, Dr. Jaeyong Park, Dr. Dr. Heedong Yang, Dr. Woongho Bang, Dongmei Meng, Jason Craig, Liangshan Chen and Dr. Manjong Lee. I also thank Dr. Nasir Basit for his assistance for handling in FIB.

I wish to thank my friends and colleagues who supported and assisted me during my academic life at UTA. Particularly, I am grateful to Ms. Prudence Brett for her smiling face and helpfulness in all things administrateive; to Dr. Dong-Ho Shin and Dr. Micahael Jin for fruitful discussions throughout my entire graduate studies.

I express my special thanks to my Mokjang family in our church and Jaehoon Kho for their support and love. Especially, I am deeply grateful to my lovely wife Sol (Ji Yeon), who makes it all possible. No matter what my goal is, she is my counselor, friend and love. It is through her patience, prayers and vision that I can write this.

Finally, my deepest thanks and appreciation belong to my parent in-laws, parents, and my family. Their concern, understanding and encouragement have been the cornerstone to my success.

October 20, 2006

#### ABSTRACT

# INVESTIGATION ON THE MECHANISM OF INTERFACE ELECTROMIGRATION(EM) IN COPPER(Cu) THIN FILMS

Publication No.

Jee Yong Kim, PhD.

The University of Texas at Arlington, 2006

Supervising Professor: Choong-Un Kim

This study concerns the mechanism of the interface electromigration (EM) in copper (Cu) thin films. While EM in Cu is one of the most concerned reliability failure phenomena in Cu interconnects used microelectronic devices, its mechanism is not well understood yet. In order for better understanding of the EM mechanism, this study attempt to investigate the interface EM mechanism by examining the passivation effects on Cu EM using a cross-strip structure where Cu lines are cross-stripped with different passivation layers. From the observation of the marker polarity (hillocks and voids), the interface EM mechanism is determined whether the passivation layer increases or decreases the interface EM of Cu.

A series of investigation finds that the surface/interface EM mechanism of Cu is different depending on both the passivation material and the thickness of passivation. Differing passivation materials and their thickness do induce change in the kinetics of the marker formation. In all cases, the results show that the mass transport along the metal passivation/Cu interfaces has slower EM rate than dielectric passivation/Cu interfaces. CoWP passivation provides interface with the slowest interface EM, and TaN passivation provides more stable interface with slower EM rate than Ta. In addition, Si<sub>b</sub>N<sub>4</sub> passivation seems to provide interface with slower interface EM than SiO<sub>2</sub>. On the other hand, when interface EM is compared to surface EM, it is found that the interface EM tends to be faster than the surface EM. This is somewhat unexpected result, but all systems inspected produced a consistent indication. It is found that the reason for higher rate of interface EM than the surface EM may be related to higher Z\* at interface.

The results of this investigation may bear importance both for scientific and engineering aspects. This is the first study that shows direct evidence for active interface EM in Cu. While the interface EM and also surface EM needs further investigation in order to understand how they occur, especially the mechanism, the results suggest that engineering the interface may be critical for reliability improvement of Cu interconnects.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                              | iii |

|-----------------------------------------------|-----|

| ABSTRACT                                      | v   |

| LIST OF ILLUSTRATIONS                         | xii |

| LIST OF TABLES                                | XV  |

| Chapter                                       |     |

| 1. INTRODUCTION                               | 1   |

| 1.1 Research Objective                        | 1   |

| 1.2 Background                                | 4   |

| 1.2.1 Cu interconnects                        | 4   |

| 1.2.2 Reliability issues in Cu interconnects  | 9   |

| 1.3 Review of electromigration (EM) mechanism | 10  |

| 1.3.1 Mechanism of electromigration (EM)      | 10  |

| 1.3.2 EM in interconnects                     | 14  |

| 1.4 EM failure in interconnects               | 17  |

| 1.4.1 EM lifetime testing                     | 17  |

| 1.4.2 Various factors affecting Cu EM         | 18  |

| 1.4.2.1 Grain Size and line width             | 19  |

| 1.4.2.2 Texture                                                                                  | 20 |

|--------------------------------------------------------------------------------------------------|----|

| 1.4.2.3 Passivation layer                                                                        | 22 |

| 1.5 Cross-strip test                                                                             | 23 |

| 2. STUDY OF INTERFACE AND SURFACE ELECTROMIGRATION<br>(EM) USING SIGLE CROSS-STRIP CONFIGURATION | 26 |

| 2.1 Introduction                                                                                 | 26 |

| 2.2 Experiments                                                                                  | 27 |

| 2.2.1 Single cross-strip sample configuration                                                    | 27 |

| 2.2.2 Sample preparation                                                                         | 29 |

| 2.2.2.1 Cuprous oxide (Cu <sub>2</sub> O) cross-strip deposition                                 | 31 |

| 2.2.2.2 Cobalt tungsten phosphide cross-strip deposition                                         | 32 |

| 2.2.3 Test procedure                                                                             | 34 |

| 2.2.4 Joule heating                                                                              | 35 |

| 2.3 Results                                                                                      | 38 |

| 2.3.1 Influence of interface materials                                                           | 39 |

| 2.3.1.1 Tantalum (Ta) cross-strip                                                                | 39 |

| 2.3.1.2 Silicon nitride (Si $_3N_4$ ) cross-strip                                                | 45 |

| 2.3.1.3 Tantalum nitride (TaN) cross-strip                                                       | 46 |

| 2.3.1.4 Titanium nitride (TiN) cross-strip                                                       | 47 |

| 2.3.1.5 Chromium (Cr) cross-strip                                                                | 48 |

| 2.3.1.6 Cobalt tungsten phosphide (CoWP) cross-strip                                             | 50 |

| 2.3.2 Blech effect and Interface EM                                                              | 52 |

| 2.3.2.1 Effect of the passivation layer thickness                                                | 53 |

| 2.3.2.2 Cross-strip length effect on Cu EM                                         | •••  |

|------------------------------------------------------------------------------------|------|

| 2.4 Discussion                                                                     | •••  |

| 2.4.1 Surface and microstructure of the test pattern                               | •••• |

| 2.4.1.1 Ta cross-strip under Ar ambient                                            | •••  |

| 2.4.1.2 Cu <sub>2</sub> O cross-strip test                                         | •••  |

| 2.4.1.3 Consideration on film stress                                               | •••• |

| 2.4.1.4 Comparison of grain structure                                              |      |

| 2.4.2 Mechanism of marker formation                                                |      |

| 2.4.3 Mechanism of thickness and length dependence                                 |      |

| 2.4.4 Consideration on surface EM and interface EM                                 | •••• |

| 2.5 Summary                                                                        |      |

| 3. TEMPERATURE AND CURRENT DENSITY EFFECTS ON<br>COPPER (Cu) ELECTROMIGRATION (EM) |      |

| 3.1 Introduction                                                                   |      |

| 3.2 Experiments                                                                    |      |

| 3.3 Results                                                                        | •••  |

| 3.3.1 Influence of Test Temperature on Marker Location                             |      |

| 3.3.2 Influence of Current density on Marker Location                              |      |

| 3.4 Discussion                                                                     | •••• |

| 3.5 Summary                                                                        |      |

| USING DOUBLE PASSIVATION LAYER CROSS-STRIP |    |

|--------------------------------------------|----|

| AND UNDER LAYER CROSS –STRIP TEST          | 89 |

|    | 4.1 Introduction                                                                                                                  | 89  |

|----|-----------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 4.2 Experiments                                                                                                                   | 92  |

|    | 4.3 Results                                                                                                                       | 94  |

|    | 4.3.1 Double passivation layer cross-strip                                                                                        | 94  |

|    | 4.3.1.1 Ta cross-strip with $Si_BN_4$ over passivation vs.<br>Si <sub>3</sub> N <sub>4</sub> cross-strip with Ta over passivation | 94  |

|    | 4.3.1.2 Ta cross-strip with CoWP over passivation vs.<br>CoWP cross-strip with Ta over passivation                                | 97  |

|    | 4.3.1.3 TaN cross-strip with CoWP over passivation                                                                                | 99  |

|    | 4.3.1.4 Ta cross-strip with TaN over passivation                                                                                  | 99  |

|    | 4.3.1.5 Cr cross-strip with Si <sub>3</sub> N <sub>4</sub> over passivation                                                       | 100 |

|    | 4.3.2 Under layer cross-strip                                                                                                     | 101 |

|    | 4.3.2.1 Ta under layer cross-strip on $Si_3N_4$ vs. $Si_3N_4$<br>under layer cross-strip on Ta                                    | 102 |

|    | 4.3.2.2 Ta under layer cross-strip on SiO <sub>2</sub>                                                                            | 105 |

|    | 4.3.2.3 Si <sub>3</sub> N <sub>4</sub> under layer cross-strip on SiO <sub>2</sub>                                                | 106 |

|    | 4.4 Discussion                                                                                                                    | 107 |

|    | 4.5 Summary                                                                                                                       | 108 |

| 5. | CONCLUSIONS AND RECOMMENDATIONS                                                                                                   | 110 |

|    | 5.1 Introduction                                                                                                                  | 110 |

|    | 5.2 Significant Findings and Implications                                                                                         | 111 |

|    | 5.2.1 Single passivation cross-strip test                                                                                         | 111 |

|    | 5.2.2 Double passivation and under layer cross-strip test                                                                         | 111 |

| 5.2.3 Implications       | 112 |

|--------------------------|-----|

| 5.3 Further Research     | 112 |

| REFERENCES               | 114 |

| BIOGRAPHICAL INFORMATION | 127 |

# LIST OF ILLUSTRATIONS

| Figure |                                                                                                                                    | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------|------|

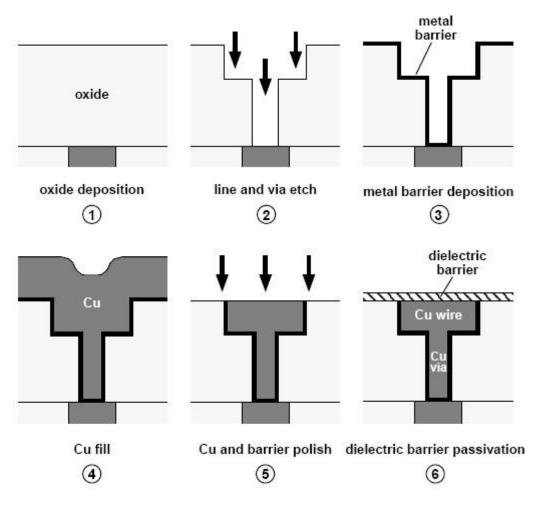

| 1.1    | Simplified copper dual damascene process flow                                                                                      | . 7  |

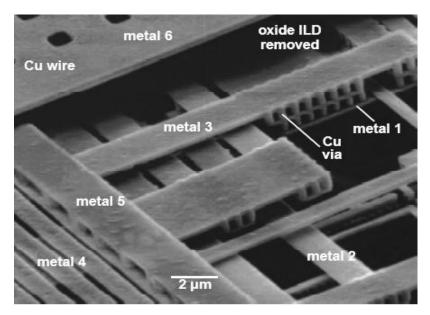

| 1.2    | Multilevel interconnections; Demonstration by (a) Motorola, and (b) IBM                                                            | . 8  |

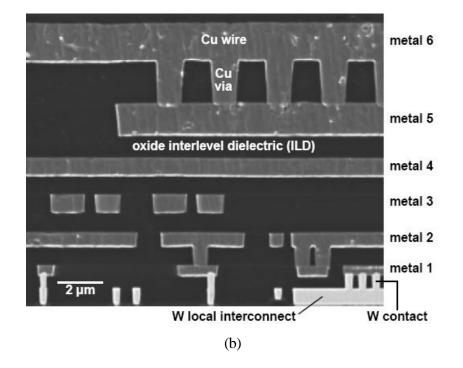

| 1.3    | The schematic diagram illustrating net atomic flux and stress gradient                                                             | . 16 |

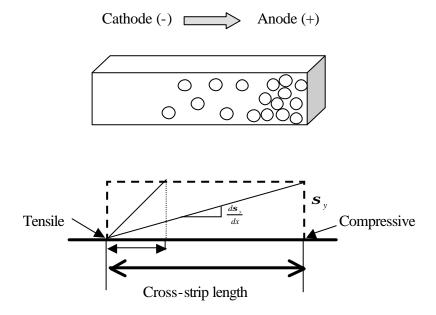

| 1.4    | The schematic diagram of cross-strip sample configurations;<br>(a) Surface EM > Interface EM, (b) Surface EM < Interface EM        | . 25 |

| 2.1    | A schematic diagram of sample configuration                                                                                        | . 28 |

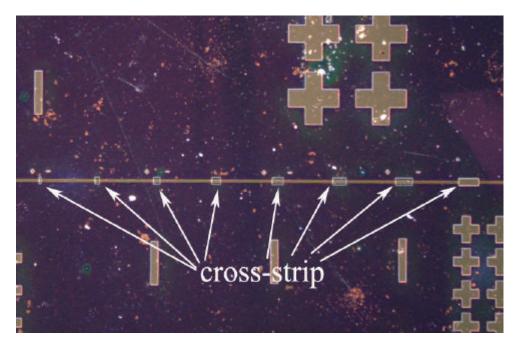

| 2.2    | Optical microscope images of sample configuration                                                                                  | . 30 |

| 2.3    | The schematic diagram of the electro-deposition cell                                                                               | . 31 |

| 2.4    | The EDS spectra of CoWP on Cu line on Si substrate                                                                                 | . 34 |

| 2.5    | A schematic diagram of EM test apparatus                                                                                           | . 35 |

| 2.6    | Measured values of resistance change for electroplated Cu line                                                                     | . 37 |

| 2.7    | The SEM image of Ta cross-strip after 45 hours EM test at 270°C, 1.5MA/cm <sup>2</sup> ; under forming gas ambient                 | . 40 |

|        | The EDS spectra of (a) Cu line, (b) void, and (c) hillock after 45 hours EM test                                                   | . 41 |

| 2.9    | The FIB images of Ta after 24 hours EM tested at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient; (a) void, and (b) hillock | . 43 |

| 2.10   | The SEM image of Ta cross-strip after 8 hours EM test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient                    | . 44 |

| 2.11   | The FIB image of Ta cross-strip after 8 hours EM test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient                    | 44   |

| 2.12 | The SEM image of $Si_3N_4$ cross-strip after 45 hours EM test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient                                                                                              | 45 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.13 | The SEM image of TaN cross-strip after 45 hours EM test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient                                                                                                    | 47 |

| 2.14 | The SEM image of TiN cross-strip after 45 hours EM test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient                                                                                                    | 48 |

| 2.15 | The SEM image of Cr cross-strip after 24 hours EM test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient                                                                                                     | 49 |

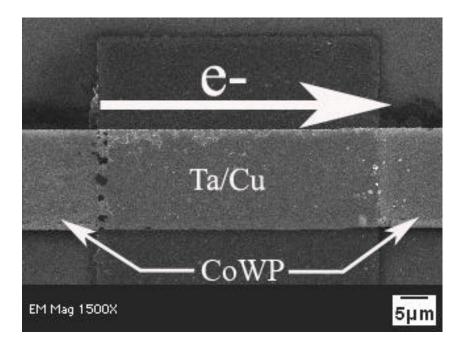

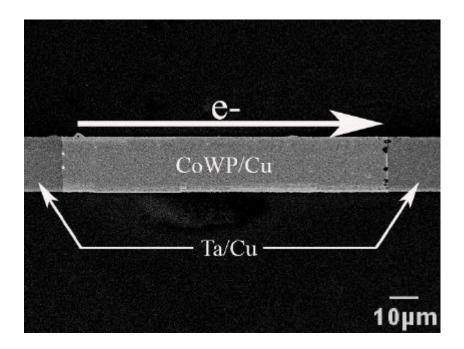

| 2.16 | The SEM images of CoWP cross-strip after 45 hours EM test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient; (a) 20um, and (b) 80um cross-strip lengths, respectively                                        | 51 |

| 2.17 | The SEM images of Ta cross-strip tested at 270°C, 1.0MA/cm <sup>2</sup> ; (a) 30nm after 44 hours test, and (b) 60nm after 48 hours test                                                                             | 54 |

| 2.18 | The basic layout of test structure; different cross-strip lengths                                                                                                                                                    | 55 |

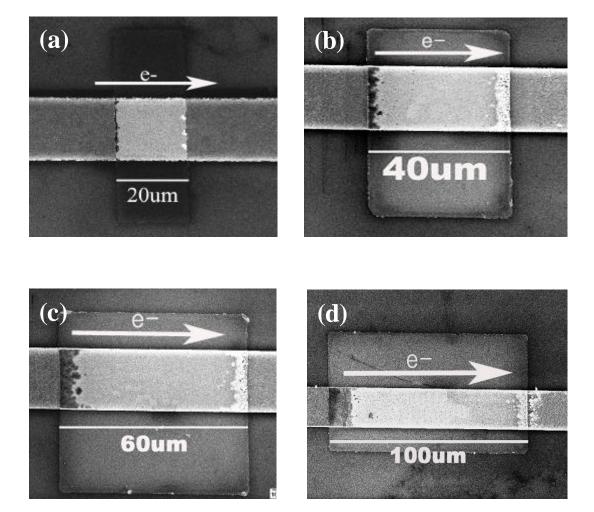

| 2.19 | The SEM images of $Si_3N_4$ cross-strip tested at 270°C, 1.0MA/cm <sup>2</sup> ;<br>(a) 20nm, (b)40um, (c)60um, and (d)100um after 36 hours test                                                                     | 56 |

| 2.20 | The SEM images of Ta cross-strip tested at 270°C, 1.5MA/cm <sup>2</sup> ; (a) forming gas, and (b) Ar gas amibient                                                                                                   | 59 |

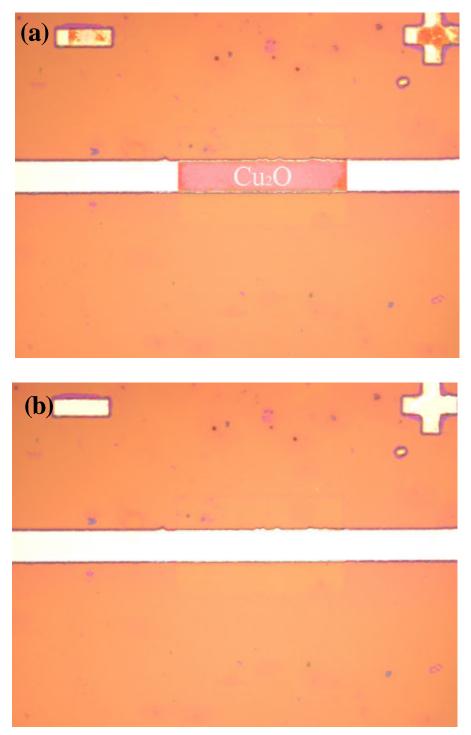

| 2.21 | The optical microscope images of $Cu_2O$ cross-strip; (a) before test, and (b) after 24 hours EM test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient                                                      | 61 |

| 2.22 | The microstructure of Cu after EM test; (a) free Cu surface region, and (b) cross-strip region                                                                                                                       | 65 |

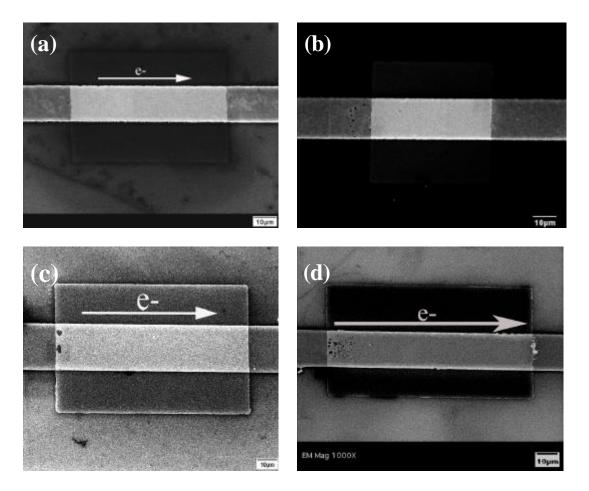

| 3.1  | SEM images of Ta cross-strip at different EM test temperatures and 1MA/cm <sup>2</sup> of current density (a) 170°C, 115 hour test, (b) 220°C, 115 hour test, (c) 270°C, 48 hours test, and (d) 320°C, 24 hours test | 79 |

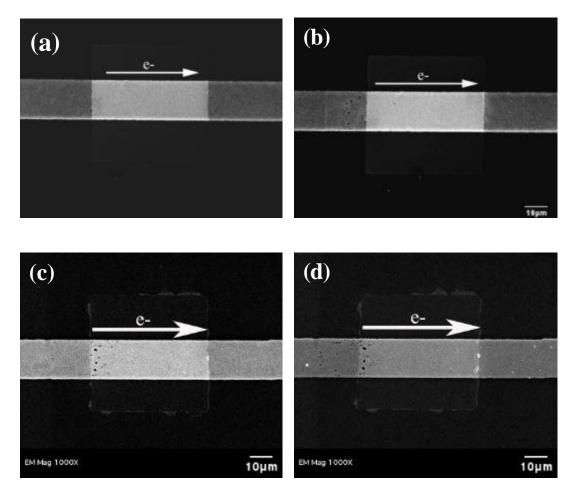

| 3.2  | SEM images of cross-strip of different current density at 220°C; (a) Ta, 1MA/cm <sup>2</sup> , 55 hours test, (b) Ta, 110 hours test, (c) Ta, 2MA/cm <sup>2</sup> , 55 hours test, and (d) 110 hours test            | 81 |

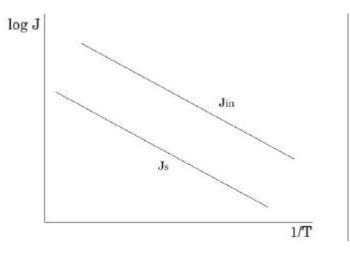

| 3.3  | Temperature dependence on EM flux (when $\Delta J_{in} = \Delta J_s$ )                                                                                                                                               | 84 |

| 3.4  | Temperature dependence on EM flux (when $\Delta J_{in} > \Delta J_s$ )                                                                     | 84 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

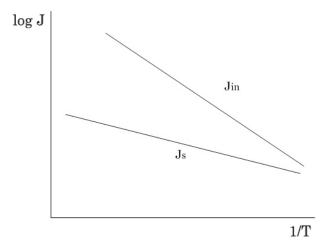

| 3.5  | Current density dependence on EM flux (when $\Delta J_{in} > \Delta J_s$ )                                                                 | 86 |

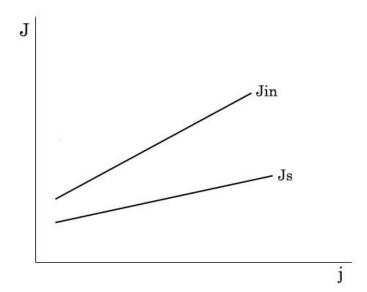

| 4.1  | The configuration of double passivation layer cross-strip test                                                                             | 92 |

| 4.2  | The configuration of under layer cross-strip test                                                                                          | 93 |

| 4.3  | SEM image of Ta cross-strip with $Si_5N_4$ over passivation after 100 hours test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient | 95 |

| 4.4  | SEM image of $Si_3N_4$ cross-strip with Ta over passivation after 100 hours test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient | 96 |

| 4.5  | SEM image of Ta cross-strip with CoWP over passivation after 100 hours test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient      | 98 |

| 4.6  | SEM image of CoWP cross-strip with Ta over passivation after 100 hours test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient      | 98 |

| 4.7  | SEM image of TaN cross-strip with CoWP over passivation after 48 hours test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient      | 99 |

| 4.8  | SEM image of Ta cross-strip with TaN over passivation after 100 hours test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient       | 00 |

| 4.9  | SEM image of Cr cross-strip with $Si_8N_4$ over passivation after 100 hours test at 270°C, 1.5MA/cm <sup>2</sup> under forming gas ambient | 01 |

| 4.10 | SEM image of Ta under cross-strip on $Si_3N_4$ after 100 hours test at 270°C, 1.0MA/cm <sup>2</sup> under forming gas ambient              | 03 |

| 4.11 | SEM image of $Si_3N_4$ under cross-strip on Ta after 100 hours test at 270°C, 1.0MA/cm <sup>2</sup> under forming gas ambient              | 04 |

| 4.12 | SEM image of Ta under cross-strip on SiO <sub>2</sub> after 100 hours test at 270°C, 1.0MA/cm <sup>2</sup> under forming gas ambient       | 05 |

| 4.13 | SEM image of $Si_3N_4$ under cross-strip on $SiO_2$ after 122 hours test at 270°C, 1.0MA/cm <sup>2</sup> under forming gas ambient         | 06 |

# LIST OF TABLES

| Table |                                           | Page |

|-------|-------------------------------------------|------|

| 2.1   | Bath composition and operating conditions | . 32 |

## CHAPTER 1

#### INTRODUCTION

#### 1.1 Research Objetive

With a miniaturization of microelectronic devices, the reliability of interconnect is becoming more critical than ever [1-5]. For this reason, as well as to increase the circuit performance, copper (Cu) interconnect replaced the conventional interconnect materials based on aluminum (Al) and its alloy. The Cu interconnects offer higher electrical conductivity and thus effectively reduces the signal delay in the microelectronic devices [6-9]. In addition, with higher melting temperature, the Cu interconnects tend to show generally better reliability than the Al interconnects. However, the introduction of the Cu for Integrated Circuit (IC) created several new technical and theoretical challenges. One of these is the electromigration (EM) reliability [10,11]. The EM, the atomic diffusion under high current density, has been the major source of interconnect failure in IC [12-15]. It is expected that the EM reliability will be more critical problem in the future devices mainly because of increased current density. In theory, the EM is a simple process, but failure induced by EM is a result of complex process. The failure is created by a local divergence of EM flux, which is linearly dependant on atomic mobility and EM force. The complexity stems from the fact that there are many possible EM path in Cu interconnects, namely the lattice, grain boundaries, interfaces, and surfaces. Furthermore, flux divergence varies with microstructure, making the understanding of failure mechanism exceedingly difficult. In Cu interconnects, it is believed that at least two EM mechanisms, grain boundary and surface/interface EM, are active in the temperature range of device used and accelerated reliability test [16-21].

Several published reports indicate that surface/interface EM may be the dominant mass transport mechanism leading to failure [13,17,20, 22-25], but there exists no direct evidence to support the interface EM and the role of surface/interface structure (material and thickness) on the interface EM is not well investigated.

It is true that, since the introduction of the Cu interconnects, the surface/interface EM in Cu interconnects has been extensively studied by many researchers. However, they all have been focused on the EM lifetime test, the result of which is affected greatly by various factors such as microstructure, processing and test structure [26-28]. Therefore, it is difficult to understand the interface EM behaviors in Cu and to determine what affects such behaviors. Hence, new investigative approach is necessary to isolate the interface (or surface) EM mechanism from other influential factors. For this reason, we developed a new methodology of investigating the interfacial EM in Cu thin film lines.

2

The study presents a new methodolo gy of investigating the surface/interface EM of Cu, and also presents the influences of interface materials on the interface EM mechanisms in Cu thin films studied by the developed methodology. The new method, so called cross-strip, utilizes, a strip of a second material patterned across a Cu line, thus creating an isolated area on the Cu surface. This method has been extensively used for studying alloying effect on aluminum (Al) EM [29-32]. In our tests, the cross-strip concept has been modified to investigate interface EM in Cu interconnects. Surface is the same condition but interface condition is different due to different passivation layers. The cross-strip creates the flux divergence of EM and allows to observe the nature of the divergence as it induce formation of hillocks and voids at the ends. In case of the passivating cross-strip we are using, the flux divergence is likely to be created by difference in interface EM rate. Although both grain boundary and interface EM are expected to occur [16-25], but their contribution to the marker formation (hillock and void) is far smaller than the interface EM.

With the developed investigative method, this study further aims to find: (1) the relative EM rate between surface and interface in Cu thin films, (2) difference in interface EM rate between two different passivation materials in Cu interconnects, and (3) the effects of temperature and current density on Cu EM. In order to accomplish these goals, this study examines: (1) different passivation materials, (2) different temperatures and current densities, and (5) different test configurations.

The interface materials chosen in our study includes tantalum (Ta), tantalum nitride (TaN), titanium nitride (TiN), chromium (Cr), cobalt tungsten phosphide (CoWP), silicon nitride (Si<sub>3</sub>N<sub>4</sub>), and silicon oxide (SiO<sub>2</sub>) films. They are chosen because they are interface materials of practical importance. They are either being used or considered as interface material in real interconnects. Ta, TaN and TiN films are used as adhesion or diffusion barrier layer, Si<sub>3</sub>N<sub>4</sub>, and SiO<sub>2</sub> films are used as dielectric and passivation layer, and CoWP film is used as a passivation layer in microelectronic devices.

This dissertation organized as follows: Chapter 1 presents the background information of this study, where the basic theory of EM and EM in interconnect, as well as the various other factors affecting EM are reviewed. Chapter 2 presents the results of single passivation layer cross-strip test. Chapter 3 presents the temperature and current density effects on Cu EM. Chapter 4 turns its focus to the double passivation layer cross-strip tests to support single passivation layer cross-strip test. And interface EM rates between two different passivation materials will be compared. Finally, chapter 5 summarizes the main findings and offers suggestion for future research directions.

#### 1.2 Background

#### 1.2.1 Cu interconnects

In recent years, great progresses in interconnect technologies have been made, and Cu interconnects have been used to take place Al interconnects. The transition to Cu as interconnect metal began with intensive research and development efforts in the early 1990's, which led to IBM's electroplated 0.22µm CMOS generation and Motorola's physical vapor deposited Cu product [33,34]. The transition to Cu interconnects have begun because that Cu offers many intrinsic advantages over conventional AI-based alloy interconnect, including higher electrical conductivity and higher mechanical strength. Cu is also expected to show better reliability because it has much lower grain boundary and lattice diffusivity than AI because of its higher melting temperature [35].

The current generation of Cu interconnects are generally manufactured using the dual-damascene method because Cu lacks the appropriate dry etch plasma chemistry needed to pattern the lines. In the damascene process, trenches and via holes are etched into the dielectric layer; then liners and Cu layers are deposited to fill in the pattern, followed by chemical-mechanical planarization (CMP). Similarly, Cu lines and vias can be formed simultaneously with a dual-damascene process flow. A simplified dual damascene process flow for Cu interconnect is illustrated schematically in Figure 1.1.

The advantages of damascene processing include patterning without metal etching and a three-dimensional network of interconnections called multilevel interconnection (MLI) is available for Cu damascene process to replace the Al interconnection network [36].

The use of the Cu interconnects has produced substantial enhancement in interconnect performance both in electrical and physical aspects. In case of Al interconnects, the interconnection network is two-dimensional planar configuration because damascene and CMP process is not available, therefore, it becomes more and more unsuitable for high performance interconnection because of the following reasons: (a) lack of space to provide interconnections for all devices in a two-dimensional planar configuration, (b) interconnect RC delay, and (c) reliability for large current densities. Such benefits increase when the multilevel interconnection is considered. In multilevel interconnection, the metal interconnections are not confined in one plane, therefore, RC delay can be reduced due to the reduced interconnection length and the increased cross-sectional area of interconnects.

For this reason, according to the prediction of Semiconductor Industry Association (SIA) National Technology Roadmap for Semiconductors (NTRS), as many as eight to nine levels of metals in a multilevel interconnection scheme for high performance chips can be used [1,40]. In this concept, as shown in Figure 1.2, several levels of Cu interconnect can be employed.

Figure 1.1 Simplified copper dual damascene process flow [37]

(a)

Figure 1.2 Multilevel interconnections; Demonstration by (a) Motorola, and (b) IBM [37-39]

#### 1.2.2 Reliability issues in Cu interconnects

The reliability of metal interconnect is a major concern for modern IC fabrication. With decreasing the device dimensions, the length of the interconnect increases while the interconnect line width decreases. These two factors lead to higher electrical resistance and higher current density in the metal interconnects [1-5]. For this reason, reliability problems such as EM become increasingly important to reliability problem in Ultra-large scale integrated (ULSI) circuits [10,11].

EM describes the development of structure damage caused by metal ion transport as a result of high-current stressing in thin metal film. As previously mentioned, Cu is expected to have high reliability in addition to low resistivity compared to AI-based metal interconnects. However, there still exists reliability issues in Cu interconnects, including the EM itself [10,11]. Many investigations suggest that the Cu interconnects is still prone to EM induced failures, although the resistance against EM failure is far better than the AI interconnects. Also, those studies suggest that the EM failure occurs in different mechanism from those in AI interconnects. Such difference is believed to related to the lack of passivation oxide in Cu. Unlike AI, Cu does not have a self-passivation layer. Exposed surfaces will continue to oxidize, leading to poor barrier adhesion and high resistance. Also, the lack of self-passivating oxide demands the use of artificial passivation materials (such as Ta and SiN), and such interfaces are not necessarily resistant against EM [12,13,17-20]. With continuing miniaturization of the Cu interconnect dimension, the question as to the extent of the interface EM has intensified and, in fact, has created significant concerns.

#### 1.3 Review of electromigration (EM) mechanism

EM in interconnects has been studied the late 1960's when it was first observed in wide AI-based interconnects [41]. As one of the main IC failure mechanisms, EM performance will continue to be one of the main issues in integrated circuit reliability for a relatively long time. Modern microelectronic devices use either Al or Cu thin films as interconnection materials, both of which are susceptible to physical failure by EM. Although the signal current itself is small, due to the sub-micron scale of the interconnects, current density is sufficient to induce EM. A small amount of EM in the interconnect can result in catastrophic circuit failure by void formation or hillock formation. Therefore, it is of great importance to accurately assess the effect of EM on interconnect reliability.

#### 1.3.1 Mechanism of electromigration (EM)

The EM refers the phenomena of atomic transportation in a conductor under the influence of high electrical current density. High current density provides driving force to atoms migrate to the direction of electron flow. The driving force for EM consist of the two forces acting on metal atoms [12, 42-46]. The first is the interaction of the applied electric field and the metal ions. This electrostatic force contains the interaction of the ion with valence Z and applied field as well as any electrostatic shielding from the surrounding electrons. This contribution is often referred to as the "direct" force. The direct force can be written as

$$F_{\rm D} = Z(1-k)e\vec{E}$$

$$=Z_D * e\vec{E},\tag{1.1}$$

where k describes the electrostatic shielding and  $Z_D^*$  is the effective charge caused by the electrostatic force  $F_D^*$ ,  $Z_D^* = Z(1-k)$ . The second contribution to the total force, F, arises from the momentum transferred to the ions from the electrons. This contribution is often referred to as the "electron wind" force.

The simple theoretical description of the wind force can be seen from the following discussion. In a given conductor, the number of collision per unit time between the electrons and diffusion ions,  $n_{collision}$ , is approximately given by

$$n_{collision} = n_e v_e \boldsymbol{S}_e \tag{1.2}$$

where  $n_e$  is the number density of electrons,  $v_e$  is the average electron velocity, and  $s_e$  is the cross section for scattering between an electron and a diffusion ion. In the scattering process, the electron transfers all of the momentum it gained since its previous collision. The average momentum transferred per collision is given by

$$\Delta p = e\vec{E}\frac{l_e}{v_e} \tag{1.3}$$

where *e* is the charge of an electron, *E* is the electric field and  $l_e$  is the mean free path of the electrons. The product of these two equations is the wind force

$$\vec{F}_{wd} = -n_e \boldsymbol{s}_e \left| \boldsymbol{e} \right| \vec{E} l_e \tag{1.4}$$

As defined in eq.(1.4) the wind force is directly proportional to the electric field applied to the metal. It is traditional to define an effective charge of the metal ions

$$F_{wind} = Z_{wd} * e\vec{E} \tag{1.5}$$

where  $Z_w$  is the valence of the diffusion ion.

The total force, F, is simply the sum of these two components.

$$\vec{F} = \vec{F}_D + \vec{F}_{wd}$$

(1.6)

$$= (Z_D * + Z_{wd} *)e\vec{E}$$

$$= Z * e\vec{E}$$

(1.7)

where  $Z^*$  is the effective charge number for the migrating metal ions describe in this system.  $Z^*$  can be either positive or negative depending on the direction along which migrating ions diffuse. Depending on which of the force is stronger, metal atoms toward the cathode or anode end of the conductor. However, for a good conductors  $Z^*$  is found to be in the range of ~ -10, indicating that the direct force is small compared to the wind force. It is generally believed that the contribution of the direct force is reduced substantially by screening effects by free electrons. Therefore, electron "wind" force is dominant and metal atoms migrate in the same direction as the electron flow [12,42-47].

Under the given driving force, the metal atoms move with rate controlled by the diffusivity. The atomic EM flux can then be obtained through the relation J= $\mu$ F, where  $\mu$  is the atomic mobility. The atomic mobility is related to the atomic diffusion coefficient, D, by the Nernst-Einstein equation,  $\mathbf{n} = nD/kT$ , where n is the mass density of the metal, k is the Boltzman's constant and T is the absolute temperature [48]. By substituting the applied electric field with the product of the current density, j, and the metal resistivity,  $\rho$ , the following equation is derived.

$$J_{e} = n(D/kT)Z * erj$$

$$= nv_e \tag{1.8}$$

where,  $J_e$ , is the atomic flux due to EM and  $V_e$  is the drift velocity due to EM. Drift velocity is a product of the mobility (D/kT) times EM driving force (F):

$$v = (D/kT)F \tag{1.9}$$

Hence, the drift velocity due to the EM force is give by

$$v = \frac{De \mathbf{r} j Z^*}{kT} \tag{1.10}$$

The atomic diffusion coefficient D is a function of temperature in Arrhenius equation as follows [49]:

$$D = D_o \exp(-\frac{E_a}{kT}) \tag{1.11}$$

where  $D_o$  is a proportionality constant (m<sup>2</sup>/sec), Ea is the activation energy (eV) associated with the diffusion mechanism (or path). At fixed temperature, the value of D is different for different diffusion paths.

Since the dependence of r on T is nearly linear, v/j follows Arrheniuns behavior. Therefore, the EM flux becomes

$$J = \frac{n}{kT} D_o e^{-Q/kT} e \mathbf{r} j Z^*$$

(1.12)

It can be seen that EM flux is determined by temperature in addition to electric current applied.

#### 1.3.2 EM in interconnects

The interconnects of modern semiconductor are highly dense and intricate networks containing millions of line segments terminating with vias and contacts. As the interconnect dimension becomes smaller, they become more susceptible to EM induced failures due to increase in current densities and surface/interface fraction. EM itself in interconnects can occurs through several different diffusion paths. These paths include diffusion through the bulk, grain boundaries, interfaces, and surfaces. The effective diffusivity can be written as the sum of the diffusivities associated with different paths. The following equation shows the effective diffusivity written as the sum of the bulk, grain boundary, interface, and surface [17,50,51].

$$D_{eff} = D_b + \sum_{j=1}^{n} D_{gb,j} \left(\frac{\mathbf{d}_{gb,j}}{d}\right) + D_i \left[2\mathbf{d}_i \left(\frac{1}{w} + \frac{1}{h}\right)\right] + D_s \left(\frac{2}{w} + \frac{1}{h}\right)$$

(1.13)

where the subscript b, gb, i, s refer to the bulk, grain boundary, interface, and surface, respectively;  $D_{eff}$  is the effective diffusivity, **d** is the width of the grain boundary, w is the width and h is the height of the interconnect.

With several mechanisms contribute to EM mechanism, the activation energy (Ea) for EM failure in interconnects can be a function of temperature since a particular diffusion mechanism dominated a temperature range. The bulk diffusion term can be ignored because the temperatures of practical importance are too low for the bulk diffusion to be significant compared to others. Thus, the most important diffusion mechanisms to be considered for Cu interconnects are the grain boundary diffusion and interface diffusion [17,50,51]. In that case, the drift velocity of Cu ions under EM can be expressed as

$$v_d = D_{eff} Z *_s erj/kT \tag{1.14}$$

where  $Z_{s}^{*}$  is a coefficient based on momentum transfer from electrons to copper atoms. In case of Cu interconnects, various studies suggest that the bulk and grain diffusion plays insignificant role, and thus eq.(1.13) reduces to

$$D_{eff} = D_i [2d_i (\frac{1}{w} + \frac{1}{h})]$$

(1.15)

where  $D_i$  is the interfacial diffusion.

Another important consideration of EM in interconnects is the presence of the stress-induced back flow, namely the 'Blech' effect [52,53]. If the particular metal line of interest is embedded in a stiff dielectric material like  $SiO_2$  the back flow force is created which opposed to the EM force. This force arises as atoms are depleted from the cathode and accumulated at the anode. The accumulation and depletion of mass in confined space creates the stress. In places where mass is accumulated, compressive stress is induced. In the opposite case, tensile stress is developed. In interconnects, these two places are closely spaced, resulting in a steep stress gradient. This stress gradient counteracts the EM force and reduces the net atomic flux, as illustrated in Figure 1.3.

In this configuration,  $\Delta s$  is the local gradient in the hydrostatic stress in Cu and its maximum value is a function of the surrounding structure. For stiff surroundings,  $\Delta s$  can reach a higher value than for a more compliant structure.

Figure 1.3 The schematic diagram illustrating net atomic flux and stress gradient

The net atomic flux in an interconnect due to the combined effects of the EM force and the stress gradient can be expressed as [52-58]:

$$J_{net} = nv_d = n(v_e - v_b)$$

$$= n(D/kT)(z * erj - \Delta s\Omega_e/L)$$

(1.16)

where  $v_e$  is atomic migration due to EM,  $v_b$  is atomic back flow due to and EMinduced stress gradient,  $v_d$  is the net drift velocity,  $\Delta s$  is the stress gradient,  $\Omega_a$  is the atomic volume, and L is the line length.

The back-stress affect can improve the EM resistance of metal lines if the product of the current density j, and line length, L, is equal to or less than a threshold value,  $\Gamma$ . If the current density is held constant then there arises a critical length,  $L_c$ ,

below which there will be no net EM flux. The threshold value and the critical length are expressed as

$$\Gamma = jL_c = \Delta s\Omega_a / Z * er \tag{1.17}$$

#### 1.4 EM failure in interconnects

#### 1.4.1 EM lifetime testing

The most common method for evaluating the EM reliability is a lifetime measurement under accelerated conditions (high temperature and high current density). EM performance is characterized by the mean time-to-failure (MTTF or t50), that is the time at which 50% of the test sample has failed cumulatively, and *s* that is the dispersion of time-to-failure distribution.

In 1969, Black conducted a series of accelerated testing designed to evaluate the temperature and current density dependence of the time to failure [55,56]. MTTF is defined as the 50 % point of the time to failure distribution.

$$MTTF = t50 = Aj^{-n} \exp\left(\frac{E_A}{kT}\right)$$

(1.18)

where t50 corresponds to the cumulative probability P=50%, A is technology-dependent and structure-dependent pre-exponential factor and is dependent on the material and conductor geometry, j is the current density (A/cm<sup>2</sup>), n is the current density exponent, where n varies between 1 and 2 depending on the mode of failure (during void formation or void growth).  $E_A$  is the activation energy of the EM associated with the diffusion mechanism, k is Boltmann's constant and T is the absolute temperature. The MTTF and s are obtained from the log-normal curve that is the best fit for EM time-tofailure. High MTTF and low s are desired for good EM performance. The chief benefit of lifetime test is the ability to test large numbers of specimens at the same time. However, it would be difficult to determining the mechanisms of EM failure solely using this method.

The main purpose of the EM lifetime testing is to determine the activation energy and current dependence of the failure rate for given interconnect structure. Such testing is necessary because the prediction of the interconnect reliability under use condition needs to be conducted for any given set of interconnects produced. In addition, the testing is conducted to identify the weak part of interconnects that needs to be improved for better reliability. The latter part is especially important for interconnect development because EM failure rate is affected greatly by many factors in interconnects and the reduction of the potential failure site can be achieved by EM testing. Many factors contributing to the EM failure rate, and such factors are related to site for flux divergence. Such places include locations with a change in current density and direction, interface between different materials, defects such as grain triple points, conductive and non-conductive contaminants, dopant precipitate and segregation, grain size variations, and so on.

#### 1.4.2 Various factors affecting Cu EM

EM failure rate is profoundly influenced by a number of factors. In thin film conductors, EM-induced flux divergence can be caused by inhomogeneity in local

structure and temperature because the variation of micro-structural parameters of thin film causes a non-uniform distribution of atomic flow rate. The magnitude of the atomic flux divergences depends on the degree of the structural and thermal inhomogeneities in the metallic thin films. The structural imperfections include point defects, dislocations, grain boundaries and triple points. The factors which influence the EM of Cu interconnects can be classified into those which impact Cu fine structures, such as Cu grain size, degree of crystal orientation, etc., and those relating to the condition of the interface between Cu and passivation layer.

#### 1.4.2.1 Grain size and line width

Since atoms are more loosely bounded at the grain boundaries than in the lattice, atoms migrate along grain boundaries more easily than through the lattice. Ideally, therefore, the EM failure rate should depend on the grain size (d) of metallic thin film. Such a dependence is well documented in case of Al interconnects, however, the dependence is found to be less pronounced in Cu interconnects. It is probably because the interface EM is most dominant in Cu interconnects.

Ideally, the grain size and linewidth affects the EM failure rate (if everything else equal) because it affects the flux divergence. In case of Al interconnects, the dependence is found to be very pronounced and shows slower failure rate both at wide and narrow lines. In case of wider lines, since the line contains many grains, the flux along the line is more uniform. With the reduction in degree of flux divergence, EM failure rate is reduced [57]. On the other hand, when the linewidth is extremely narrow,

the line structure becomes bamboo-like. In such a case, the EM can not proceed continuously through the grain boundary network but involve lattice or other diffusion paths. This leads to higher EM failure lifetime.

Various studies have investigated the EM failure rate dependence of the Cu interconnects on the grain size and the linewidth and revealed that the dependence is less pronounced than those found in Al interconnects. It appears that the less strong dependence seen in Cu interconnects originates from two sources. The first is the fact that the study of the width dependence (or size dependence) involves several unknown line structure factors. The Cu interconnects are made by damascene process, so that the microstructure developed in different trench widths is not the same. With such a limitation, it is extremely difficult to determine how EM rate (or the failure mechanism) changes with width and grain size. The second problem is related to the intrinsic properties of Cu interconnects, that is that the EM in Cu interconnects occurs also through interface. As the interface EM should affect the resulting EM failure data, the width or grain size dependence is straightforward but requires complex analysis to extract the contribution of each EM components to the lifetime. However, a few studies do indicate that the grain structure may influence the EM failure because the failure rate appears to vary with the texture.

#### 1.4.2.2 Texture

A few studies find that EM lifetime varies significantly with textures in Cu interconnects. For example, it is found that CVD Cu with (111) texture show much

longer lifetime than CVD Cu with (200) texture [24,59]. The varying EM failure rate with the texture is attributed to the possibility that the tighter tilting distributions of grains in (111) textured interconnects create slower atomic diffusion. However, whether such results can be related to grain structure effect or not is not clear yet because it is possible that interface EM still affects the result.

There are two ways to view the experimental results. The first is to relate the results to grain structure effect. In highly textured films, large portions of the grain boundaries are low-angle, where the atomic arrangement is relatively ordered and the grain boundaries are more uniform. Such microstructure reduces the grain boundary diffusion (and also the flux divergence) and thus reduces the failure rate. In randomly oriented grains, flux divergence is more likely to occur at the grain boundary junctions.

The second possibility is that the texture induces the formation of low diffusivity interfaces. It is known that self-EM on the low-miller index faces of Cu should be dominated by the wind force and it varies with surface orientation; -26e, -24e, and -22e for self-EM on Cu(100), Cu(110), Cu(111) respectively [60]. Furthermore, it is also known that the activation energy for surface diffusion differs with surface orientation, activation of (111) surface being much lower than on (100) or (110) surfaces [24,59]. As a result, different texture impart influence on the EM failure rate not by differing grain boundary EM rate but by differing interface EM rate.

### 1.4.2.3 Passivation layer

It is generally agreed that the surface/interface diffusion is the most active in Cu. Therefore, the passivation layer that creates interface with Cu is expected to play an important role in determining the EM reliability of Cu interconnects [26,27]. Various studies have reported that EM failure rate is affected significantly by the passivation material, thickness of passivation layer, interface condition of passivation/metal interconnects, stress condition, etc. While these studies show consistent results indicating that the interface EM is the most active EM mechanism in the Cu interconnects, they fail to show how interface EM is affected by interface condition. An important question to answer is what interface would provide better interface against EM failure, and such question is still not answered. With the complexity of EM mechanism in Cu interconnects, finding the answer is extremely difficult and requires lengthy and complex analysis. Due to this difficulty, the question is still remained unanswered in the interconnect community although the answer is increasingly important.

Complexity of EM failure analysis in Cu interconnects can be seen from following example. N. G. Ainslie et al. report that the EM failure rate is reduced by passivating the Cu interconnects [26,27]. Superficially, this result can be attributed to the suppression of surface diffusion that may provide faster diffusion path than the interface. However, it is not simple as what appears to be because the EM may be affected by the "Blech Effect". As shown in equation (2.7), the EM induced stressgradient counteracts the EM driving force, resulting in reduced mass flux. When Cu is not passivated, the surface is not constrained and the Cu is allowed to expand and contract. This makes the stress build-up to be small, if there is any. On the other hand, when the Cu is encapsulated with rigid dielectric materials, the free expansion and contraction is less allowed and much higher stress gradient can be resulted. Therefore, EM flux under confined condition would show much longer EM lifetime even if the interface EM were faster than the surface EM.

From above discussions, it is clear that the mechanism of EM in Cu interconnects is not well understood. Even the question as to the degree of surface EM compared to interface EM is not well arswered in the field. Furthermore, it is not known which interface would provide best interface for EM reliability. Such uncertainty of the mechanism makes the design and development of interface materials in microelectronics and demands elaborate investigation on the fundamental aspects of interface EM mechanism. Also clear is the fact that the conventional EM testing method is not likely to work for the desired purpose. The EM lifetime is a result of complex process with numerous influential factors involved. With such a method, it is nearly impossible to isolate one mechanism from other. This formed basis of our efforts in developing the "cross-strip" method.

# 1.5 Cross-strip test

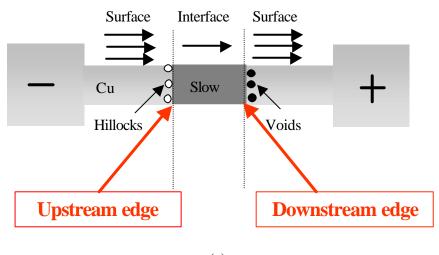

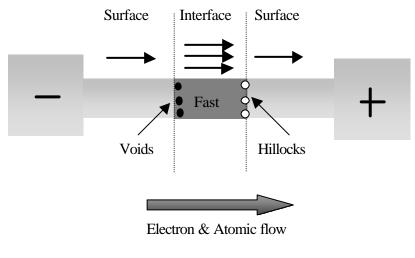

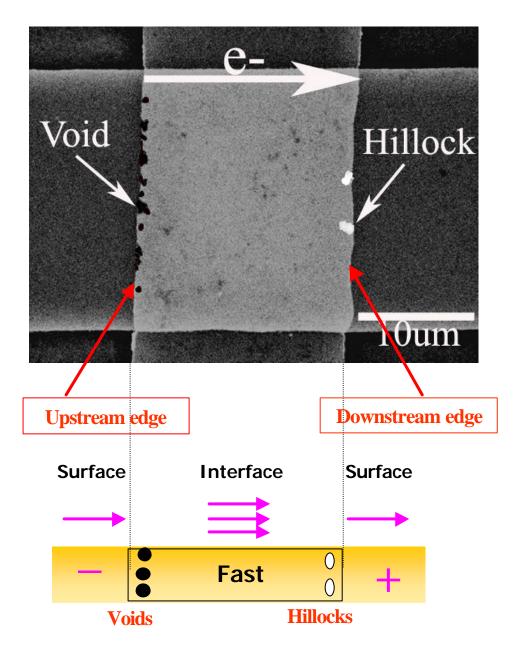

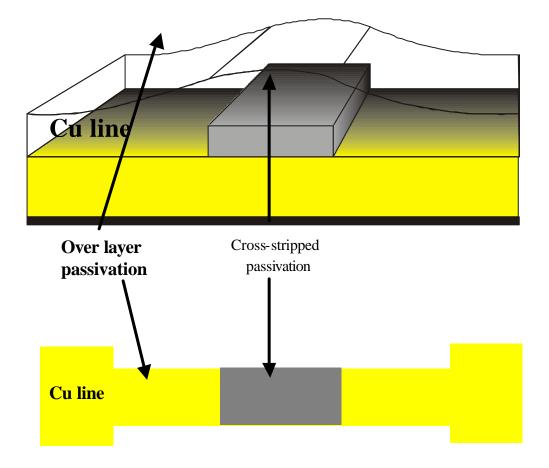

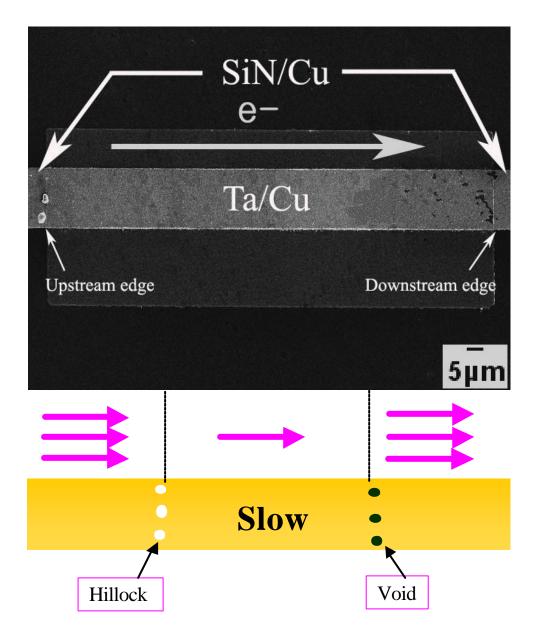

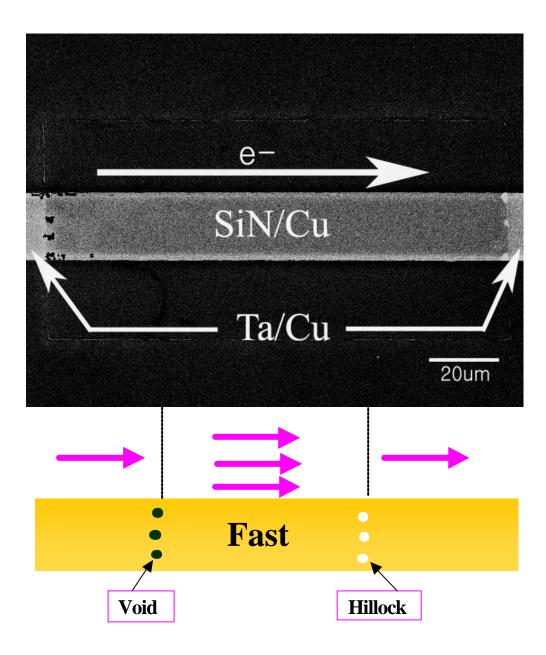

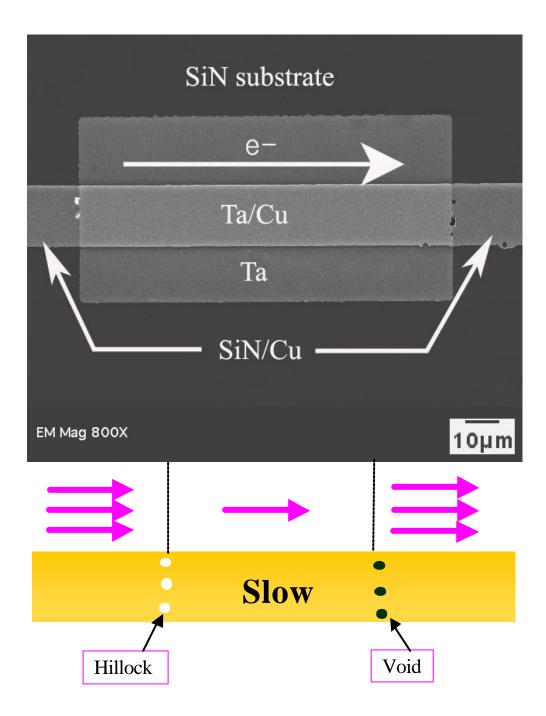

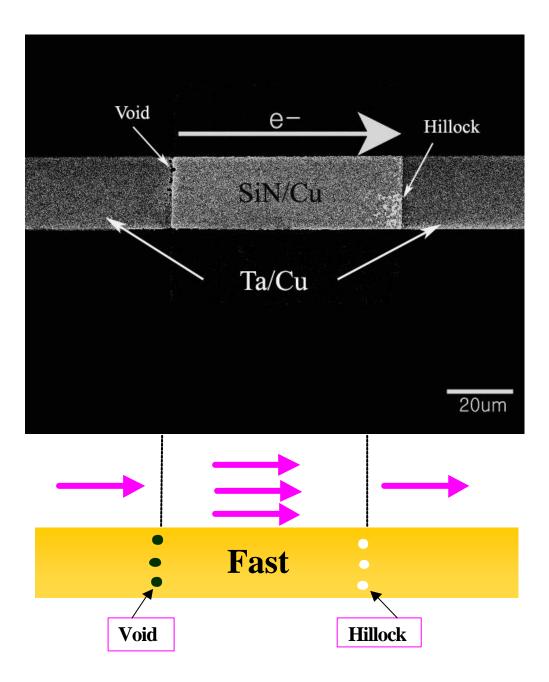

The concept of the cross strip test is simple and initially was introduced by Howard and Ross, which was further developed by others [29-32]. The cross-strip method was initially used to study the solute effect on EM mechanism, but the crossstrip test we developed here aims to test interface EM in reference to surface EM. As shown in Figure 1.4 a cross strip configuration consists of a Cu conductor line and a cross strip of passivation layer. During the EM test, electrical current passes through the Cu surface, passivation/Cu cross-strip, then Cu surface region again.

The passivation creates an artificial interface. Since all micro-structural features are the same between the cross-stripped passivation and unpassivated Cu surface except for the possibility of having different mechanical constraints, any markers formed by EM should indicate the relative difference between surface and interface EM rate.

The marker forms because the variation of surface/interface chemistry or other parameters over a film causes a non-uniform distribution of atomic flow rate. Therefore, non-zero atomic flux divergence exists at the places where the number of atoms flowing into the area is not equal to the number of atoms flowing out of that area per unit time. With the non-zero atomic flux divergence, there will be either a mass depletion (divergence>0) or accumulation (divergence<0), leading to formation of voids and hillocks.

The polarity of the markers and their amount, hillocks and voids, provides evidence for interface EM. If the passivation suppresses the EM, the EM rate is slower in the cross-strip region. In this case incoming flux is larger than outgoing flux at the upstream edge of cross-strip, resulting the formation of hillocks at the upstream (with respect to electron flow) edge and voids at the down stream edge of cross-strip. On the other hand, if passivation results in the faster EM rate in the interface than surface, hillock and void would with a reverse polarity.

(a)

(b)

Figure 1.4 The schematic diagram of cross-stripe sample configuration; (a) Surface EM > Interface EM, (b) Surface EM < Interface EM

# CHAPTER 2

### STUDY OF INTERFACE AND SURFACE ELECTROMIGRATION (EM) USING SINGLE CORSS-STRIP CONFIGURATION

#### 2.1 Introduction

As discussed in chapter 1, one of the main debates on EM mechanism lies on the question whether interface (or surface) EM play a role in Cu interconnects [13,17,20, 22-25]. Also debated is the choice of the interface materials that retards EM rate, if the interface is active part of EM path, because it will guide microelectronic industries to enhance the reliability of Cu interconnects. However, answers to such questions have not been provided in any previous studies. Our study aims to provide answers to those questions by characterizing of interface EM characteristics using cross-strip method. We create an artificial interface with different passivation layers, and the interface EM characteristics under different interface conditions are examined. Our experiments consist of the cross-strip configuration having various interface materials and compare the characteristics of interface in reference to the surface EM. Results from this study reveal that interface EM does exist and its extent varies with cross-strip materials, thickness, length, est ambient, and so on. Furthermore, it is found that the rate of interface EM is faster the surface EM in Cu interconnects. This chapter presents evidence supporting these findings and discusses their importance.

#### 2.2 Experiments

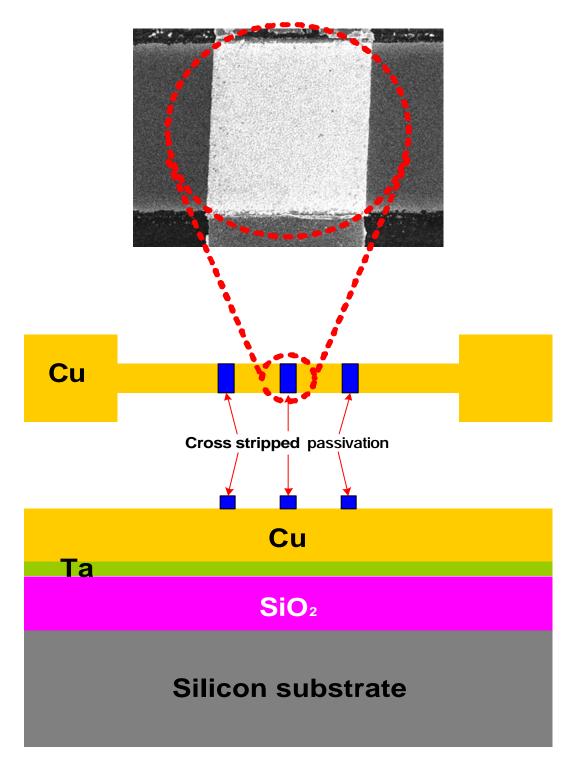

2.2.1 Single cross-strip sample configuration

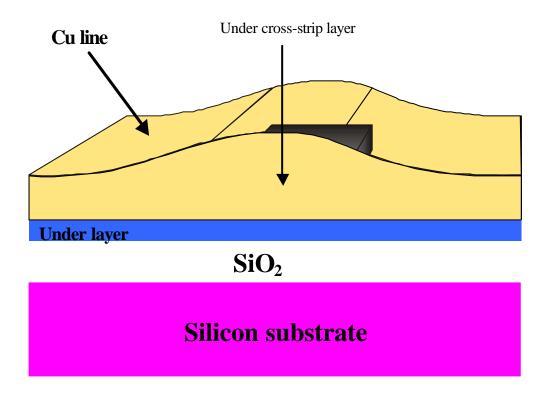

The sample configuration used in this study is based on the single cross strip structure. As shown in Fig.2.1, the single cross-strip configuration involves a base Cu line having local area covered with the passivating layers. Under this configuration, the markers should form as a result of the flux difference between the interface EM and surface EM. Therefore, this configuration enables us to determine whether a particular interface offers faster or slower EM path than the Cu surface. The test line is consisting of 3 parallel lines connected in series. Typically, the width of these lines is 20um, while their thickness is varied from 0.1 to 1.3um. One test pattern contains 8 individual crossstrip area. Their lengths are 20, 40, 60, 80, 10, 160, 200 and 300um. The variation in the strip length is introduced to examine the presence of the Blech effect. As discussed in Chapter 1.3.2, the EM driving force is affected by EM induced back-flow. If the back flow driving force exists, the kinetics of marker formation would vary with the length (or width and thickness) of the cross-strip. The 8 different lengths of cross-strip patterns are introduced to investigate such an effect.

Figure 2.1 A schematic diagram of sample configuration

### 2.2.2 Sample preparation

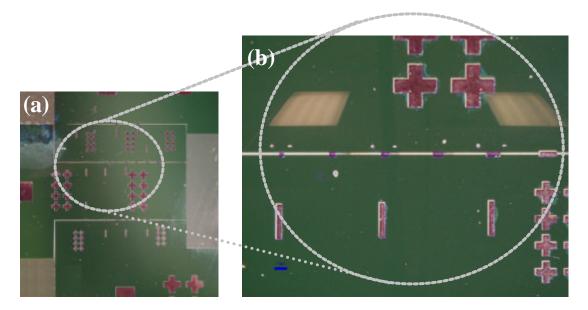

The samples needed for the single cross-strip testing are prepared in 3 steps: film preparation, line patterning, and cross-strip layer deposition. The Cu films used in this study are prepared either by using sputtering or electroplating. In this process, Si wafer is oxidized to form the 0.1um thick thermal SiO<sub>2</sub> layer. The formation of SiO<sub>2</sub> is needed to prevent Si from diffusion to Cu lines. Some wafers are coated with 15nm thick Ta layer after SiO<sub>2</sub> formation to enhance the adhesion of Cu to the substrate. The During line patterning, Ta layer is also removed except for the area underneath Cu lines. In this way, adhesion of the Cu line to Si substrate is enhanced while preventing the short-circuit among test lines.

The test lines are patterned using a standard lithography technique. It involves photo-resist application, exposure to pattern mask, developing and finally an etching. The etching of Cu films is done by using wet chemical etching method, and the etching solution used is a 1:1:2 solution of acetic acid (CH<sub>3</sub>COOH): hydro-peroxide (H<sub>2</sub>O<sub>2</sub>): deionized water (H<sub>2</sub>O) and 1:1:2 solution of hydrofluoric acid (HF): nitric acid (HNO<sub>3</sub>): de-ionized water (H<sub>2</sub>O) respectively.

The final step of the sample preparation is the creation of the cross-strip layer. For patterning of the cross-strip over layer, a similar photolithography technique as the one for the test line patterning is used, but the method employed is the lift-off process. In this process, the test line is coated with photoresist, which is then exposed to pattern mask. The area of the photoresist removed during developing process is the area where cross-strip layer is planned to be deposited. After deposition of the targeted overlayer (passivation material), the wafer is immersed in solvent to remove the photo-resist. Examples of the final test samples produced in these procedures are shown in figure 2.2. Figure 2.2 (b) show the magnified view of the cross-strip regions on the Cu line tested. Tantalum (Ta), tantalum nitride (TaN), titanium nitride (TiN), chromium (Cr), silicon nitride (Si<sub>3</sub>N<sub>4</sub>), silicon oxide (SiO<sub>2</sub>), Cuprous oxide (Cu<sub>2</sub>O), and cobalt tungsten phosphide (CoWP) films are used as the passivation layers. Except for Cu<sub>2</sub>O and CoWP, all the passivating layers are deposited using sputtering method. The Cu<sub>2</sub>O and CoWP layers are formed by electrochemical methods to achieve desired film quality and following sections detail the preparation methods.

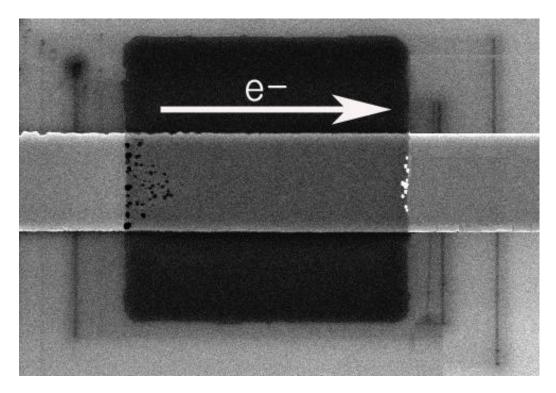

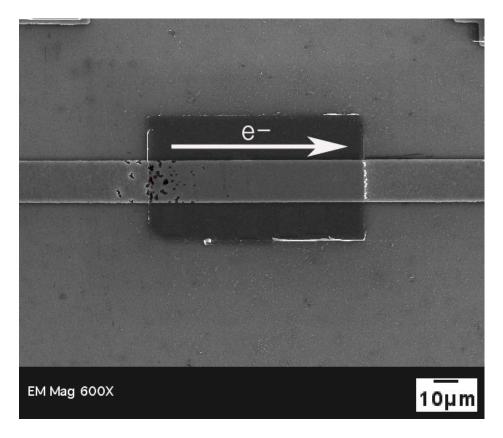

Figure 2.2 Optical microscope images of sample configuration

# 2.2.2.1 Cuprous oxide (Cu<sub>2</sub>O) cross-strip deposition

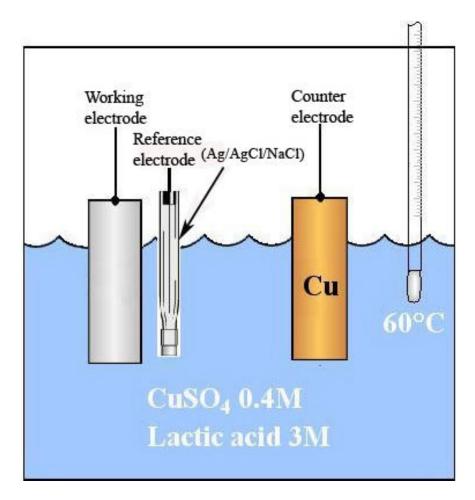

Cuprous oxide (Cu<sub>2</sub>O) cross-strip layer is grown on Cu line by the cathodic reduction of copper (II) lactate solution. The schematic diagram of electrodeposition cell is shown in figure 2.3.

Figure 2.3 The schematic diagram of the electro-deposition cell

The electrolyte consists of 0.4 M cupric sulfate (Fisher Scientific) and 3 M lactic acid (Aldrich). The pH of the bath is adjusted around 9 by the addition of sodium hydroxide [61,62]. The bath temperature is kept at  $60^{\circ}$ C and applied potential is – 0.4 V (vs SCE). The working electrode, which is used as cathode, is Cu line patterned sample. The anode is a rectangular piece of Cu. The reference electrode was a saturated calomel electrode (SCE). Electrodeposition of cuprous oxide film is carried out in a potentiostatic mode.

### 2.2.2.2 Cobalt tungsten phosphide cross-strip deposition

Cobalt tungsten phosphide (CoWP) cross-strip layer is grown on Cu line by electroplating deposition method. The plating bath conditions are showed in Table 2.1.

|                                                                                | CoWP bath (Mol/L) |

|--------------------------------------------------------------------------------|-------------------|

| CoCl <sub>2</sub> ·6H <sub>2</sub> O                                           | 0.1               |

| NaH <sub>2</sub> PO <sub>2</sub> ·H <sub>2</sub> O                             | 0.2               |

| Na <sub>3</sub> C <sub>6</sub> H <sub>5</sub> O <sub>7</sub> ·H <sub>2</sub> O | 0.3               |

| Na <sub>2</sub> WO <sub>4</sub> ·2H <sub>2</sub> O                             | 0.03              |

| (CH <sub>3</sub> ) <sub>2</sub> NH·BH <sub>3</sub>                             | 0.02              |

| рН                                                                             | 9.5               |

| pH adjusting agent                                                             | КОН               |

Table 2.1 Bath composition and operating conditions [63]

The solution for electroplating CoWP films comprises a source of tungsten ions such as sodium or ammonium tungstate, or phosphotungstic acid; a source of cobalt ions such as cobalt chloride or cobalt sulfate; and complexing agents, reducing agents, surfactants and chemicals used to adjust the pH of the bath solution. As reducing agent, hypophosphate and Dimethyl Amine Borane (DMAB) is used. The pH of this solution can be adjusted by the amount of potassium hydroxide (KOH) added to the bath. The CoWP films used in this study are deposited at the constant current of 1mA and room temperature.

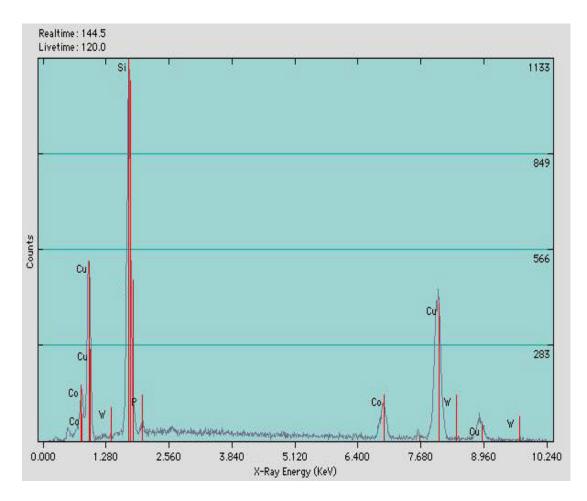

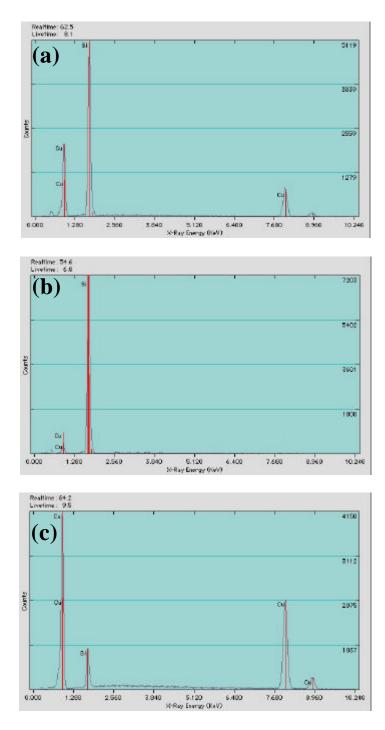

It is known that the amount of cobalt, phosphorous and tungsten in the CoWP films is highly dependent on the applied current density and the pH of the electroplating bath solution [64]. For example, cobalt tungsten phosphide films with less than 1 atomic percent tungsten forms if the pH is less than 6. Increasing the pH of the electroplating bath above 7 result in an increase in the amount of tungsten in the film above 1 atomic percent. In order to check the composition of the film produced in our method, the EDS (Energy Dispersive Spectroscopy) analysis is conducted and the result is shown figure 2.4. It can be seen that Cobalt (Co), tungsten (W), and phosphorous (P) are present in the film. Both Cu and Si peaks come from under layer of Cu line and Si substrate. The EDS analysis shows that the film contains a small amount of W along with residual amount of P.

Figure 2.4 The EDS spectra of CoWP on Cu line on Si substrate

### 2.2.3 Test procedure

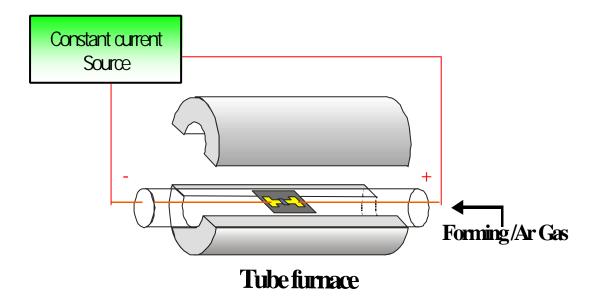

Prior to EM testing, all the samples are inspected under SEM to make sure that the testing samples are free of defects at as-prepared condition. The samples are then EM tested in a tube furnace while flowing the forming gas (10%H<sub>2</sub>/90%N<sub>2</sub>) or argon gas (99.9999%) in order to prevent oxidation of the Cu during testing. A schematic of EM test apparatus is shown in figure 2.5. A sample is placed at a place of the target test temperature and EM tested under a constant current condition. The EM tests is performed at stress condition of 1~2 MA/cm<sup>2</sup> current density and 170~320°C ambient temperature.

Figure 2.5 A schematic diagram of EM test apparatus

### 2.2.4 Joule heating

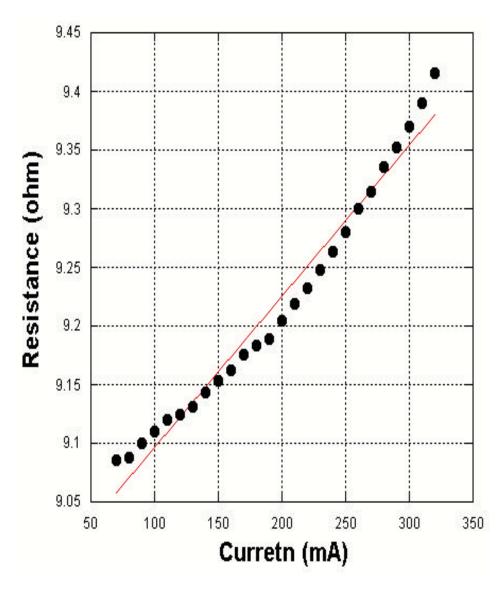

One of important aspects of the EM testing in our configuration is the level of the joule heating because joule heating can offset the temperature from the target test temperature and can cause erroneous results [6,65]. For this reason, the level of joule heating is characterized prior to EM testing. The amount of joule heating present in the sample can be estimated by measuring resistance change as a function of current density. The change in the temperature is reflected in the resistance because the resistance changes with temperature in proportional to a, the coefficient of thermal resistance of the test structure:

$$R = R_o (1 + \mathbf{a} \Delta T) \tag{2.1}$$

The joule heating characterization indicates that the average sample temperature increases to a moderate degree and varies with the thickness of the Cu film. In case of electroplated Cu, which is 1.3um thick, the increase in the line temperature is measured to be  $17^{\circ}$ C at j=1.0MA/cm<sup>2</sup>. On the other hand, sputtered Cu (0.1um thick) shows below 1°C increase at j=1.5MA/cm<sup>2</sup>. Figure 2.6 shows the measured values of resistance changes for electroplated Cu line (1.3um) as a function of applying current. In can be seen that the joule heating is minimum in most cases, and therefore it is concluded that the effect can be ignored.

Figure 2.6 Measured values of resistance change for electroplated Cu line

# 2.3 Results

There are a large number of variables tested with the single cross-strip configuration, and the variables include cross-strip materials, their thickness, test ambient and current density. While some variations exist in detail, all the results show a certain level of consistencies. In order for better understanding of the results we gained in our study, following statements can be provided as a summary:

- a) Our experiments present clear evidence that the interface and surface EM is active in Cu. This conclusion is drawn from the observation that the markers (void and pair) do form within reasonable time frame of EM.

- b) Regardless of the interface materials, it appears that the EM rate in interface is faster than the free surface EM. This is determined from the observations of the marker formation (void and hillock pair). In all materials tested, the markers form with polarity indicating that the interface EM rate is faster than the surface EM.

- c) Our results suggest that Blech effects also play a role in the interface (or surface EM mechanism). It is general trend that the marker formation is more pronounced as the width of the cross-strip increases.

Following sections summaries all the experimental results that lead to these conditions.

#### 2.3.1 Influence of interface materials

#### 2.3.1.1 Tantalum (Ta) cross-strip

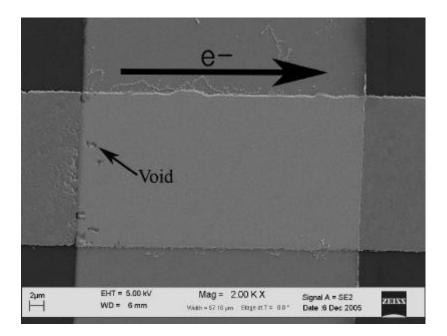

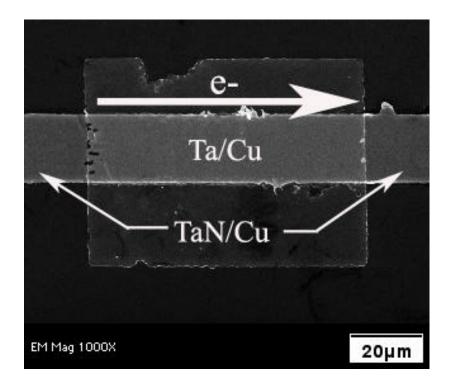

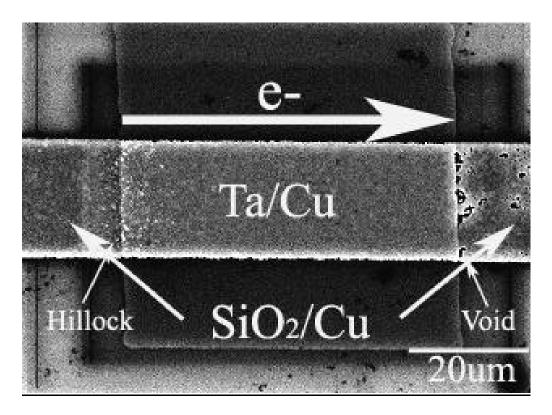

Sputtered Cu samples with 30nm Ta over layer cross-strip were EM tested under forming gas ambient. Figure 2.7 is a SEM image of the EM markers taken after 45 hours EM test at T=270°C and j=1.5MA/cm<sup>2</sup>. In these images, voids appear as dark contrast due to the lower secondary electron intensity. It can be seen that multiple voids are formed at the upstream edge of the cross-strip while hillocks are formed at the downstream edge of the electron flow.

The markers observed in this experiment are clearly due to the presence of the cross-strip. When other areas of the test line are inspected, there is no apparent evidence of markers forming by EM. Further more, even when the voids or hillocks are found, there are sporadic and not having systematic pair formation. In order to make confirmation that the marker formation seen under SEM is physically correct, the Energy Dispersive Spectroscopy (EDS) is used to determine the amount of Cu in the void and hillock area. Figure 2.8 shows the EDS spectra of void and hillock on the Cu line on Si substrate after 45 hours test; (a) Cu line without void and hillock, (b) void, and (c) hillock, respectively. When EDS spectra of Cu is compared in these areas, there is an intensity variation with the location. It can be seen that the peak intensity is weak in the voiding area and it is strong in the hillock area.

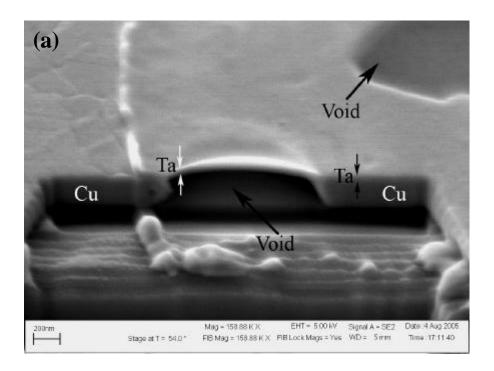

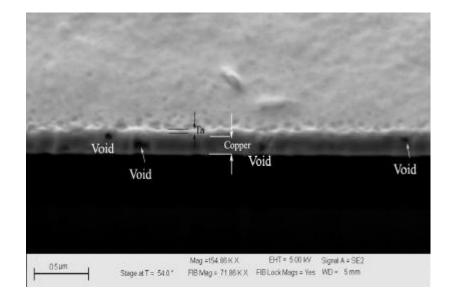

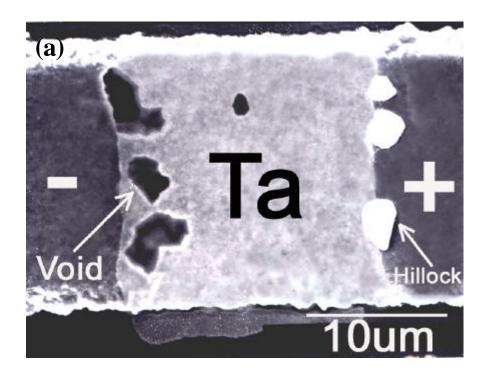

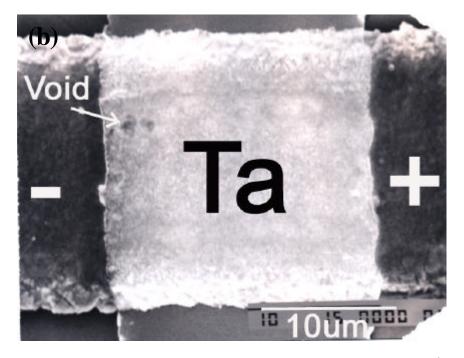

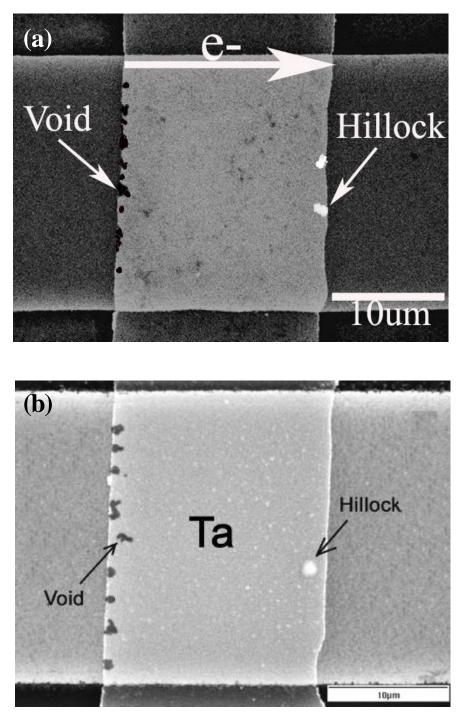

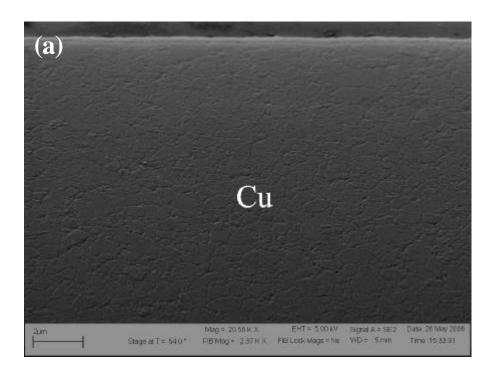

Additional experiment is conducted to further the confirmation. Figure 2.9 shows the cross-sectional view of the voiding area after 24 hour testing at 270°C. These

micrographs are taken after cross-sectioning the local area of interests using focused ion beam (FIB) and titled the sample  $54^{\circ}$  to expose the cross-sectional area.

Figure 2.7 The SEM image of Ta cross-strip after 45 hours EM test at  $270^{\circ}$ C, 1.5MA/cm<sup>2;</sup> under forming gas ambient

Figure 2.8 The EDS spectra of (a) Cu line, (b) void, and (c) hillock after 45 hours EM test.

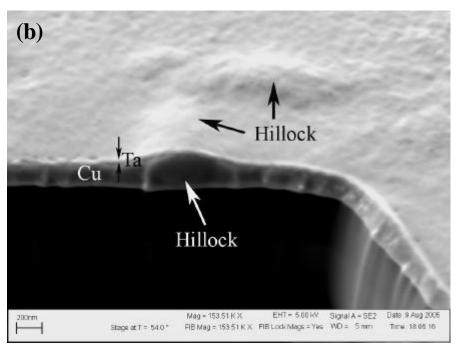

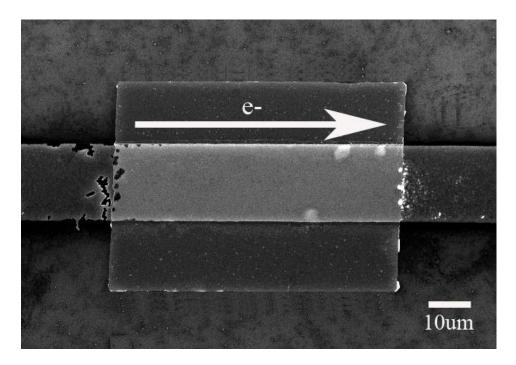

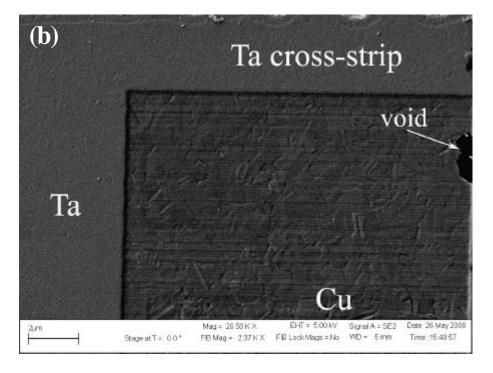

It can be seen that the voids at the upstream edge of the strip has a shape suggesting that they are nucleated at the interface between the Ta and Cu line and grow toward the underlying SiO<sub>2</sub> layer. A region of metal accumulation is also shown in figure 2.9 (b). Again, the hillocks appear to form at interface between Ta and Cu. The voids seen under Ta cross-strip in figure 2.9 (a) after 24 hours EM tested were grown too much excessive to allow investigation of the evolution. For this reason, SEM characterization of the sample tested for 8 hours is inspected, and the result is shown in figure 2.10. As marked as an arrow, the voids are not as intense as the ones in 24 hours sample but the presence of voids can be seen. These micrographs present evidences that void formation occurs at the interface between cross-strip/Cu interface and spread through the Cu film. A cross sectional view of another sample presented in figure 2.11 confirms that Cu is removed from the interface between Ta cross-strip and Cu. The polarity of the marker formation found in this experiment indicates that interface EM is very active in Cu thin films. With the given configuration, it is not possible whether the both interface and the surface is active path because the configuration allows us to observe only the flux difference between interface and surface EM. It is possible that one path is inactive and the other is active. However, it is that both are active but one path is more active than the other. The result also suggests that, between the two EM mechanisms, the interface EM is more active than the surface EM. Since Cu EM occurs in the direction of electron flow, the marker polarity indicates that the EM rate is faster at the cross-striped area than the rest of the Cu line.

Figure 2.9 The FIB images of Ta after 24 hours EM tested at  $270^{\circ}$ C, 1.5MA/cm<sup>2</sup> under forming gas ambient; (a) void, and (b) hillock

Figure 2.10 The SEM image of Ta cross-strip after 8 hours EM test at  $270^{\circ}$ C, 1.5MA/cm<sup>2</sup> under forming gas ambient

Figure 2.11 The FIB image of Ta cross-strip after 8 hours EM test at  $270^{\circ}$ C, 1.5MA/cm<sup>2</sup> under forming gas ambient

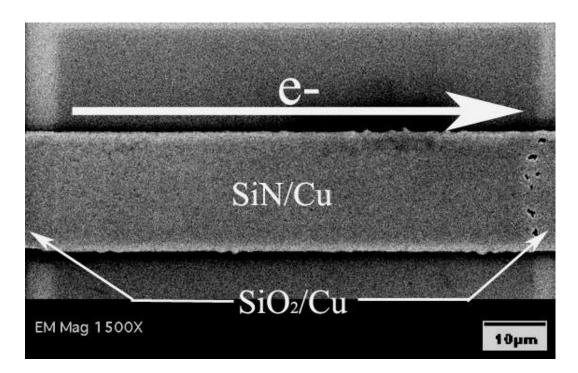

# 2.3.1.2 Silicon nitride (Si<sub>3</sub>N<sub>4</sub>) cross-strip

In case when the sputtered Cu samples  $30 \text{nm S} i_3 N_4$  cross-strip passivtion is EM tested under forming gas ambient, the markers are also formed with the same polarity as in the case of Ta. SEM micrograph shown in figure 2.12 presents an example of such results. It is seen that multiple voids are formed and aligned at the upstream edge while hillocks are formed at the downstream edge of the cross-strip. Similar to the case of Ta, this result indicates that Si<sub>3</sub>N<sub>4</sub> provides easier EM path than the free Cu surface.

Figure 2.12 The SEM image of  $S_BN_4$  cross-strip after 45 hours EM test at  $270^{\circ}C$ , 1.5MA/cm<sup>2</sup> under forming gas ambient

While the marker polarity is similar to the case of Ta, it is noted that the extent of the marker formation seems significantly increased with  $S_BN_4$  passivation under similar EM testing conditions (current density, temperature, EM time, and cross-strip width). Although qualitative, this result may indicate that the interface EM with  $S_BN_4$ passivation may be faster than the interface EM with Ta. In fact, this indication is consistent with the several previous studies because those studies finds that dielectric/Cu interface such as  $S_BN_4$ /Cu interface provides faster EM path than Ta/Cu interface [66-70]. Typically, Ta has better adhesion ability to Cu than  $S_BN_4$ , and therefore, Ta/Cu interface may form more ideal interface than  $S_BN_4$ . Studies on the interfacial diffusion activation energy also support this view, that is, that the stronger adhesion suppresses the interfacial EM because they find that the diffusion activation energy depends highly on bonding nature of the interfaces [67-71].

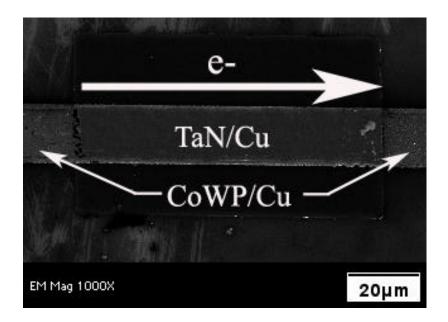

### 2.3.1.3 Tantalum nitride (TaN) cross-strip

EM test results of TaN cross-strip are shown in figure 2.13. The same polarity of marker formation, voids and hillocks, is also seen in samples with TaN cross-strip samples. Voids are formed at the upstream edge and hillocks are formed at the downstream edge of the cross-strip. Similar to other interfaces, this indicates that the TaN/Cu interface provides the faster EM paths than Cu surface. However, a minor difference is noted. It is found that void and hillock formation with TaN passivation is not confined within a strip area but extended to outside the strip.

Figure 2.13 The SEM image of TaN cross-strip after 45 hours EM test at  $270^{\circ}$ C, 1.5MA/cm<sup>2</sup> under forming gas ambient

### 2.3.1.4 Titanium nitride (TiN) cross-strip

EM test results of 30nm thick TiN passivation after 45 hours EM test are shown in figure 2.14. Similar to other interface materials, voids are found to form within the cross-strip area of the upstream edge and hillocks form on the downstream edge, indicating that the EM rate of Cu is higher in TiN/Cu interface than in the Cu surface. However, void formation is less extensive and more dispersed than the cases of  $S_BN_4$ and Ta.

Figure 2.14 The SEM image of TiN cross-strip after 45 hours EM test at  $270^{\circ}$ C, 1.5MA/cm<sup>2</sup> under forming gas ambient

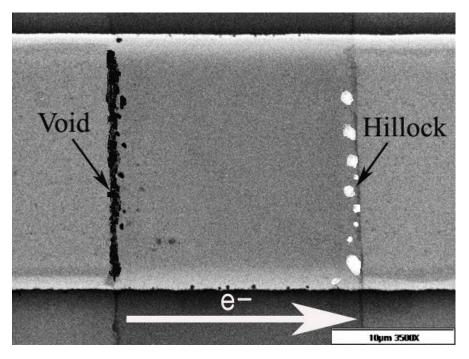

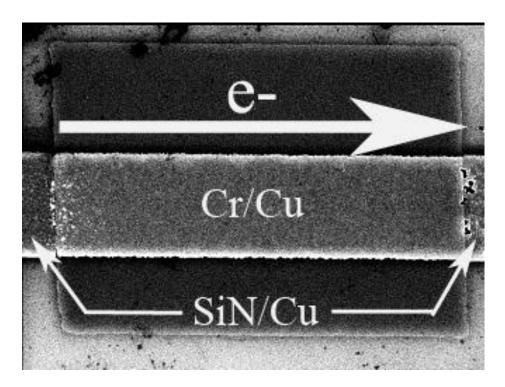

### 2.3.1.5 Chromium (Cr) cross-strip

Figure 2.15 shows marker formation for a cross-strip of Cr after 24 hours EM test. In general, polarity of marker formation is the same as those in the other single cross-stripped passivation results. Voids form at the upstream edge and hillocks form at the downstream edge of cross-strip. This result indicates that EM rate along Cr/Cu interface is higher than along free surface of Cu. However, unlike  $Si_BN_4$  and Ta passivation, void formation is not concentrated along the upstream edge of cross-strip but is more dispersed. Such a dispersed marker formation may be a result of the active diffusion. When the diffusion rate is low, the voids and hillocks should form without

possibility being diffused away from the flux divergence points. If the diffusion rate is high, diffusion would disperse vacancies and excessive atoms before nucleating voids and hillocks, resulting in the dispersed formation of the markers.

Figure 2.15 The SEM image of Cr cross-strip after 24 hours EM test at 270°C, 1.5MA/cm<sup>2</sup> under forming gas ambient

Such a view may be suffered by the observation that the area of marker formation is not confined to but extended to the outside the cross-stripped area. This is similar to the case of TaN passivation EM.

It is important to note here that the current configuration measures the EM rate difference not diffusion rate difference. It is true that the diffusion and EM is interrelated. However, it should be noted that the EM rate is not only affected by diffusion rate but also affected by the effective valance of the EM driving force. In case when the interface is with high diffusion rate and the effective valence, the marker formation should be extensive and also dispersed. On the other hand, when the interface is with high effective valence but the diffusion rate is slow, the markers should form in a confined space. We believe that the Cr belongs to the former case and TaN belongs to the latter case.

### 2.3.1.6 Cobalt tungsten phosphide (CoWP) cross-strip