## STUDY OF CONDUCTION BEHAVIOR IN DIELECTRICS IN CHIP LEVEL INTERCONNECTS:

#### DETECTION OF DEFECTS IN AL/SIO<sub>2</sub> INTERCONNECTS

by

PO-CHENG LU

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT ARLINGTON

December 2018

Copyright © by Po-Cheng Lu 2018

All Rights Reserved

#### ACKNOWLEDGEMENTS

First of all, I would like to express my deepest appreciation and gratitude to my advisor, Prof. Choong-Un Kim, for guiding me into the areas of microelectronics and providing instructions and encouragement throughout my research. He is the best mentor one can ever have. Without him, it would be impossible to finish the dissertation. I also acknowledge my committee members, Dr. Yaowu Hao, Dr. Kyung Suk Yum, Dr. Harry F. Tibbals and Dr. Nancy L. Michael, for their time and suggestions. I would also like to acknowledge Dr. Jiechao Jiang and David Yan from CCMB, Beth E. Robinson, Jennifer Standlee, Clare Schoemaker and Natalie R. Baires from MSE administrative office, Kermit Beird and Sam Williams from UTA MAE machine shop, for their help and support.

I would also like to acknowledge my group members and friends, Dr. Liangshan Chen, Dr. Huili Xu, Dr. Patricia A. Rodriguez-Salazar, Dr. Minyoung Kim, Dr. Yoonki Sa, Dr. Soo Kim, Dr. Valery Ouvarov-Bancalero, Geng Ni, Huandi Gu, Tapas Desai, Eunmee Kim, Himanshu Naik, Codie Mishler, Yang Li, Venkatakamakshi Supraja Giddaluri, Aniket Prakash Bhagwat, Sidharth Anand, Yu-Chi Cheng, Yi Ram Kim, Hossein Madanipour, Nai-Wen Pi, Hsiao-Chien Wu, Chuzhong Zhang and Yi Shen, for their support and friendship.

I would also like to thank my family, especially my parents, my brother and my parents-in-law, Chin-Sung Lu, Mei Lu Wu, Po-Han Lu, Guifen Zhang and Guorei Zhang, for their support and guidance.

Most importantly, none of this would have been possible without the unconditional love and support from my wife, Minghui Zhang. She has always believed in

Ш

me and supported me when I am facing difficulties. I also want to thank my son, William

Lu. His arrival makes my life even more wonderful.

This work is supported by Texas Instruments.

November 1, 2018

#### ABSTRACT

# STUDY OF CONDUCTION BEHAVIOR IN DIELECTRICS IN CHIP LEVEL INTERCONNECTS: DETECTION OF DEFECTS IN AL/SIO<sub>2</sub> INTERCONNECTS

PO-CHENG LU, PhD

The University of Texas at Arlington, 2018

Supervising Professor: Choong-Un Kim

This dissertation presents four different electrical measurement techniques to detect structural defects in Al/SiO<sub>2</sub> interconnects. These techniques, namely 1) polarity dependence measurement, 2) current voltage measurement, 3) two-point measurement and 4) discharge transient current measurement, can provide simple electrical parameters having direct relationship to defects state (type and quantity) in interconnect structure. All these measurement techniques use the MIM (metal-insulator-metal) structure such as the comb-serpentine structure commonly existing in integrated (IC) devices. This study also presents a newly discovered dielectric failure mechanism, that is the failure by a process of partial discharge dielectric breakdown phenomenon.

The goal of the charging polarity dependence measurement is to obtain a selfreferenced parameter indicative of structural defect distribution in metal lines. Electrical bias from two opposite direction is applied to sample (one direction is refer to positive bias, while opposite direction is refer to negative bias) in sequence and resulting leakage current is measured. In an ideal situation where metal/dielectric interface is defect free, the leakage current from both bias directions is expected to be identical because leakage current is proportional to electron injection area between metal and dielectric. With no defect, electron injection area from both electrodes are the same. However, if there exist defects in one side of metal line (either comb or serpentine side) more so than the other, electron injection area from both directions will be different, which will result in a net difference in leakage current. Based on this principal, by measuring leakage current difference under different bias direction, uneven distribution of interface defects can be characterized. This measurement can be extended to quantify the interface defect density, more specifically the voids in metal line, by conducting I-V measurement and comparing the forward and reverse current. The voids have two effects. Firstly, it reduces the interface area where electron injection occurs. Hence, injection of electron from this interface makes the leakage current to be smaller. On the other hand, since the void increases the local electrical field, it enhances the electron injection and thus current. Our study finds that the first effect is dominant when the field is low and the latter is more dominant when the field is high. Therefore, IV characteristics of the forward and reverse current shows that the interface with defect produces lower current (than the other direction) at low filed while the opposite happens when the field is high.

As for discharge transient current measurement, it gives a simple parameter that indicates the amount of structural defects in dielectric layer. Source of transient current observed in the research is likely impurities trapped in dielectric during deposition process. Upon bias, impurities are ionized and become mobile ions drifting in the direction of field to reach steady state (full polarization). When electric field is removed

VI

(short to ground) during discharging process, mobile ions return to equilibrium and generate discharge transient current. If there exist structural defects in dielectric, ion migration is hindered, resulting in a smaller amount of ion drift and thus the transient current. It is therefore reasonable to relate the total amount of transient charge (Q) to the defect density in dielectric layers. Our study confirms that there exists such a relation and that Q can be used as an indicating parameter for TDDB (time dependent dielectric breakdown) reliability of the dielectrics.

| ACKNOWLEDGEMENTS      | 4 |

|-----------------------|---|

| ABSTRACT              | 4 |

| LIST OF ILLUSTRATIONS | 4 |

# Chapter Page 1.3.2 Electromigration ...... 11 1.3.3 Stress Induced Voiding...... 13 1.3.4 Time Dependent Dielectric Breakdown ...... 17 1.4.2 Voltage Ramp Test ...... 19 1.4.3 Scanning Electron Microscope Inspection ...... 20

###

| 2.1 Background |            | 22 |

|----------------|------------|----|

| 2.1.1 Schottk  | y Emission | 23 |

#### TABLE OF CONTENTS

|    | 2.1.2 Fowler-Nordheim Tunneling                                     | 25 |

|----|---------------------------------------------------------------------|----|

|    | 2.1.3 Direct Tunneling                                              | 26 |

|    | 2.1.4 Charging Behavior of Dielectric                               | 26 |

|    | 2.1.5 Principle of Polarity Dependence Measurement Technique        | 28 |

|    | 2.1.6 Aging Treatment                                               | 30 |

|    | 2.2 Samples and Measurement System                                  | 30 |

|    | 2.2.1 Test Samples                                                  | 30 |

|    | 2.2.2 Measurement System                                            | 31 |

|    | 2.3 Test Strategy                                                   | 33 |

|    | 2.3.1 Sample Selection                                              | 33 |

|    | 2.3.2 Test Procedure                                                | 34 |

|    | 2.4 Result and Discussion                                           | 37 |

|    | 2.4.1 Leakage Current Seen in Research                              | 37 |

|    | 2.4.2 Conduction Mechanism Confirmation                             | 38 |

|    | 2.4.3 Average Leakage Current of As-received Samples                | 41 |

|    | 2.4.4 Polarity Difference of As-received Samples                    | 42 |

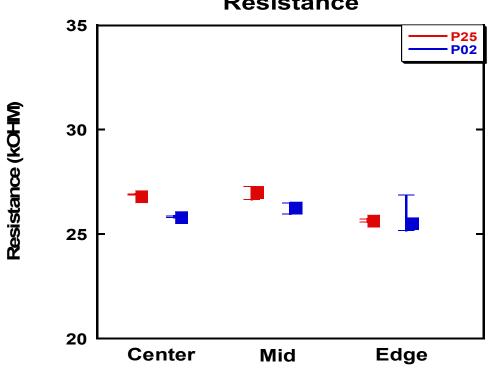

|    | 2.4.5 Resistance of As-received Samples                             | 46 |

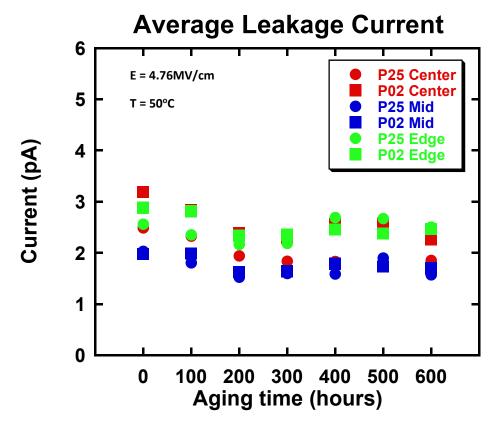

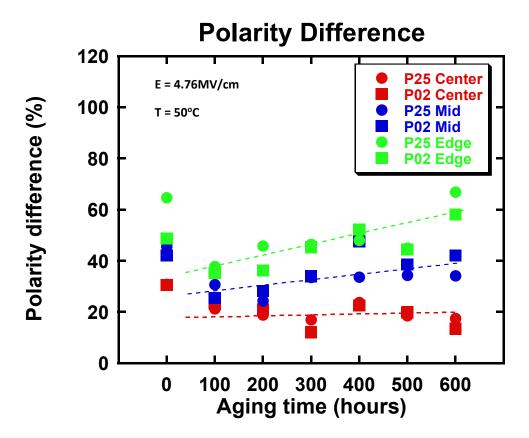

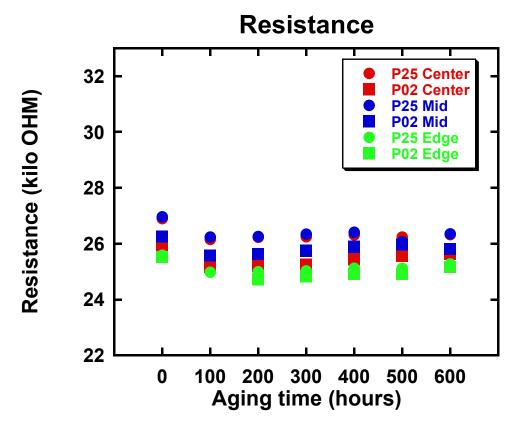

|    | 2.4.6 Average Leakage Current of Aging Samples                      | 48 |

|    | 2.4.7 Polarity Difference of Aging Samples                          | 49 |

|    | 2.4.8 Resistance of Aging Samples                                   | 50 |

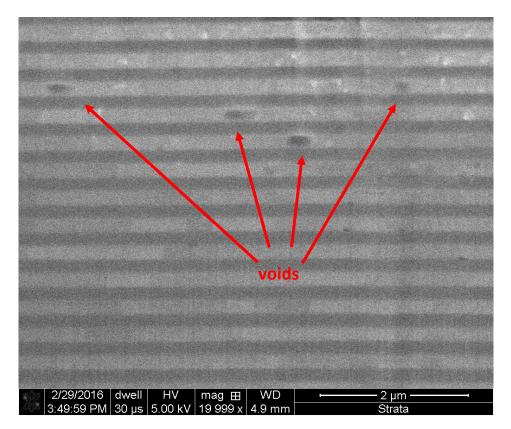

|    | 2.4.9 SEM Inspection on Aging Samples                               | 51 |

|    | 2.5 Summary                                                         | 53 |

| 3. | CURRENT VOLTAGE MEASUREMENT AND ITS SENSITIVITY TO STRUCTURAL DEFEC | TS |

|    | IN ALUMINUM LINES OF AL/SIO2 INTERCONNECTS                          | 56 |

| 3.1 Backgrou      | und                                                             | 56 |

|-------------------|-----------------------------------------------------------------|----|

| 3.2 Experime      | ental Setup and Test Strategy                                   | 57 |

| 3.2.1             | Test Samples                                                    | 57 |

| 3.2.2             | Measurement System                                              | 57 |

| 3.2.3             | Sample Selection                                                | 58 |

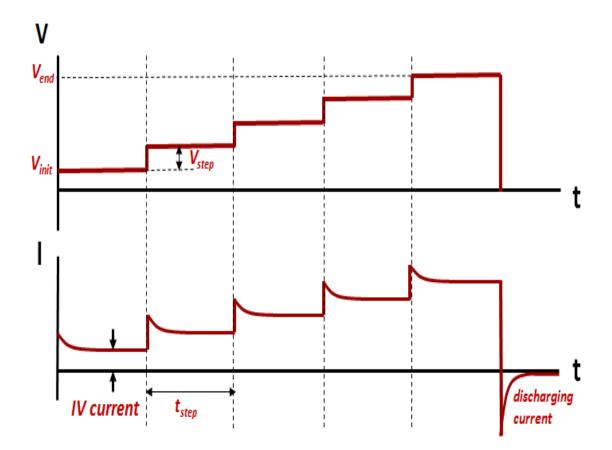

| 3.2.4             | I-V Curve Measurement Procedure                                 | 58 |

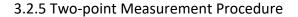

| 3.2.5             | Two-point Measurement Procedure                                 | 59 |

| 3.2.6             | Chemical Etching                                                | 60 |

| 3.3 Result ar     | nd Discussion                                                   | 61 |

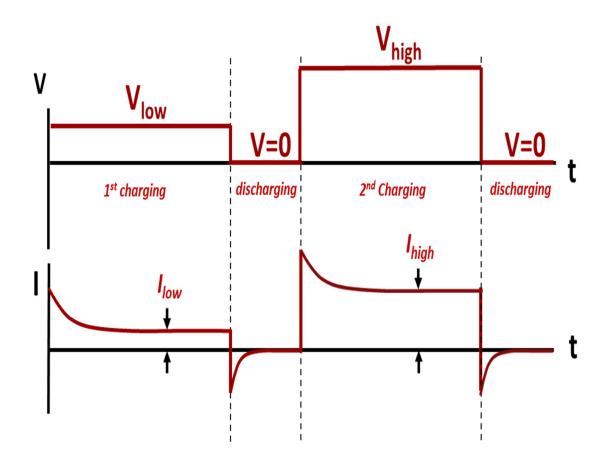

| 3.3.1             | I-V Curve Measurement of As-received Samples                    | 61 |

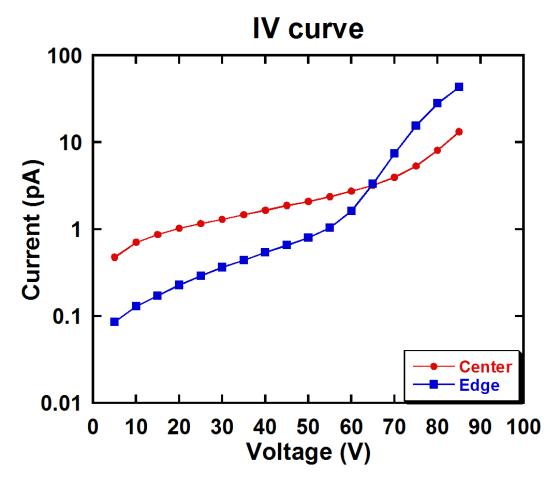

| 3.3.2             | SEM Inspection on As-received Samples                           | 64 |

| 3.3.3             | I-V Curve Measurement of Aging Samples                          | 66 |

| 3.3.4             | Two-point Measurement of As-received Samples                    | 70 |

| 3.3.5             | Two-point Measurement of Aging Samples                          | 71 |

| 3.4 Summary       | y                                                               | 77 |

| 4. DISCHARGE TRAN | SIENT CURRENT MEASUREMENT AND ITS SENSITIVITY TO                |    |

| STRUCTURAL DEF    | FECTS IN DIELECTRIC LAYERS OF AL/SIO <sub>2</sub> INTERCONNECTS | 79 |

| 4.1 Backgrou      | ınd                                                             | 79 |

| 4.1.1             | Thermally Stimulated Depolarization Current                     | 82 |

| 4.1.2             | Capacitance Measurement                                         | 83 |

| 4.1.3             | Time Dependent Dielectric Breakdown                             | 87 |

| 4.2 Experime      | ental Setup and Test Strategy                                   | 92 |

| 4.2.1             | Test Samples                                                    | 92 |

| 4.2.2             | Measurement System                                              | 92 |

| 2                                                                     | 4.2.3 Sample Selection                                                                                                                                                     | . 93                                                        |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 2                                                                     | 4.2.4 Discharge Transient Current Measurement Procedure                                                                                                                    | . 93                                                        |

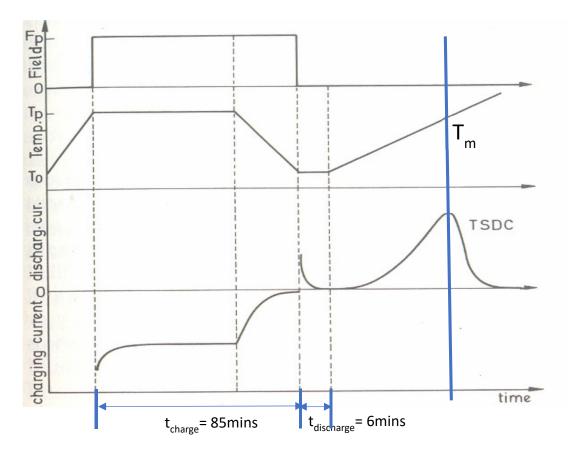

| 4                                                                     | 4.2.5 TSDC Measurement Procedure                                                                                                                                           | . 94                                                        |

|                                                                       | 4.2.6 Capacitance Measurement Procedure                                                                                                                                    | . 95                                                        |

| 4.3 Resu                                                              | ult and Discussion                                                                                                                                                         | . 96                                                        |

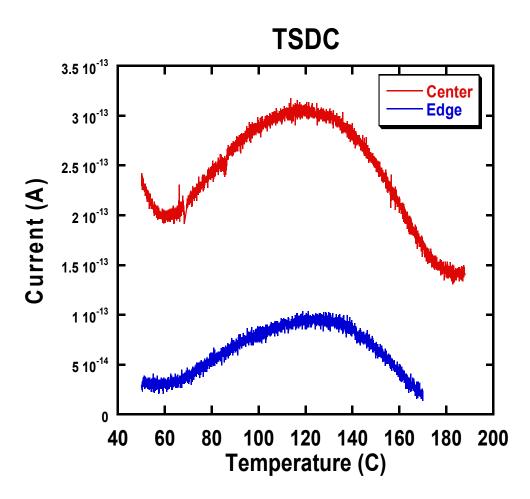

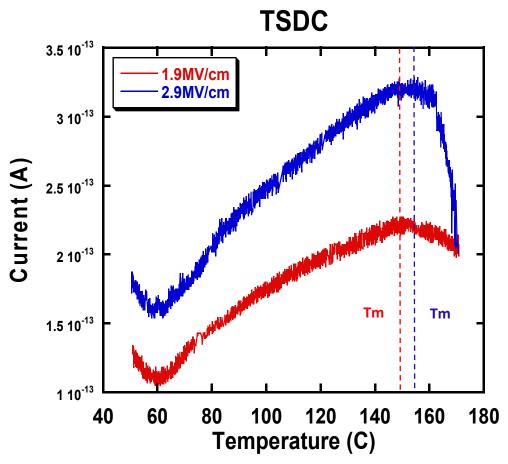

|                                                                       | 4.3.1 TSDC and Source of Charge Carriers                                                                                                                                   | . 96                                                        |

| 4                                                                     | 4.3.2 Discharge Transient Current and Factor Q of As-received Samples                                                                                                      | 5                                                           |

|                                                                       |                                                                                                                                                                            | 101                                                         |

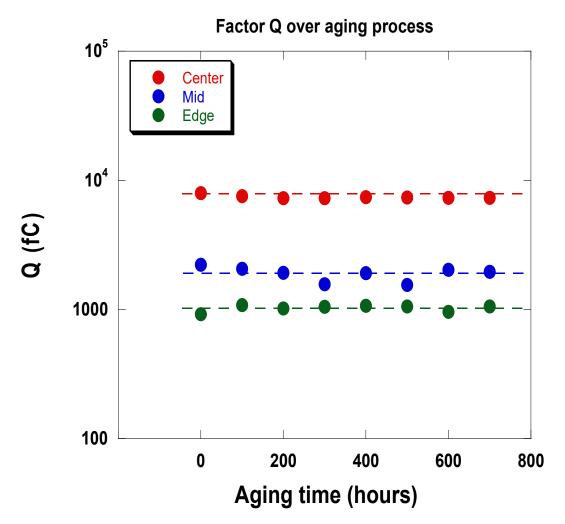

| 4                                                                     | 4.3.3 Discharge Transient Current and Factor Q of Aging Samples                                                                                                            | 113                                                         |

| 4                                                                     | 4.3.4 Source of Mobile Ions                                                                                                                                                | 114                                                         |

| 4                                                                     | 4.3.5 Capacitance Measurement of As-received Samples                                                                                                                       | 123                                                         |

| 4                                                                     | 4.3.6 Time Dependent Dielectric Breakdown Test of As-received Sampl                                                                                                        | es                                                          |

|                                                                       |                                                                                                                                                                            |                                                             |

|                                                                       |                                                                                                                                                                            | 127                                                         |

| 4.4 Sum                                                               | ımary                                                                                                                                                                      |                                                             |

|                                                                       |                                                                                                                                                                            |                                                             |

| 5. PARTIAL DIS                                                        | imary                                                                                                                                                                      | 133                                                         |

| 5. PARTIAL DIS                                                        | mary<br>CHARGE DIELECTRIC BREAKDOWN SEEN IN LOW VOLTAGE AL/SIO <sub>2</sub>                                                                                                | 133<br>137                                                  |

| 5. PARTIAL DIS<br>INTERCONNI<br>5.1 Back                              | imary<br>CHARGE DIELECTRIC BREAKDOWN SEEN IN LOW VOLTAGE AL/SIO2<br>ECTS                                                                                                   | 133<br>137<br>137                                           |

| 5. PARTIAL DIS<br>INTERCONNI<br>5.1 Back<br>5.2 Expe                  | Imary<br>CHARGE DIELECTRIC BREAKDOWN SEEN IN LOW VOLTAGE AL/SIO2<br>ECTS                                                                                                   | 133<br>137<br>137<br>140                                    |

| 5. PARTIAL DIS<br>INTERCONNI<br>5.1 Back<br>5.2 Expe                  | Imary<br>CHARGE DIELECTRIC BREAKDOWN SEEN IN LOW VOLTAGE AL/SIO2<br>ECTS<br>kground<br>erimental Setup and Test Strategy                                                   | 133<br>137<br>137<br>140<br>140                             |

| 5. PARTIAL DIS<br>INTERCONNI<br>5.1 Back<br>5.2 Expe                  | CHARGE DIELECTRIC BREAKDOWN SEEN IN LOW VOLTAGE AL/SIO <sub>2</sub><br>ECTS<br>kground<br>erimental Setup and Test Strategy<br>5.2.1 Test Samples                          | 133<br>137<br>137<br>140<br>140<br>140                      |

| 5. PARTIAL DIS<br>INTERCONN<br>5.1 Back<br>5.2 Expe                   | Imary<br>CHARGE DIELECTRIC BREAKDOWN SEEN IN LOW VOLTAGE AL/SIO2<br>ECTS<br>kground<br>erimental Setup and Test Strategy<br>5.2.1 Test Samples<br>5.2.2 Measurement System | 133<br>137<br>137<br>140<br>140<br>140<br>140               |

| 5. PARTIAL DIS<br>INTERCONNI<br>5.1 Back<br>5.2 Expe                  | CHARGE DIELECTRIC BREAKDOWN SEEN IN LOW VOLTAGE AL/SIO <sub>2</sub><br>ECTS                                                                                                | 133<br>137<br>137<br>140<br>140<br>140<br>140<br>141        |

| 5. PARTIAL DIS<br>INTERCONNI<br>5.1 Back<br>5.2 Expe<br>2<br>5.3 Resu | CHARGE DIELECTRIC BREAKDOWN SEEN IN LOW VOLTAGE AL/SIO2<br>ECTS                                                                                                            | 133<br>137<br>137<br>140<br>140<br>140<br>140<br>141<br>141 |

| 5.4 Summary 145                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 6. CONCLUSIONS AND FUTURE WORK                                                                                                                  |

| 6.1 Polarity Dependence Measurement and Its Sensitivity to Structural Defects in Aluminum Lines of Al/SiO <sub>2</sub> Interconnects            |

| 6.2 Current Voltage Measurement and Its Sensitivity to Structural Defects in Aluminum Lines of Al/SiO <sub>2</sub> Interconnects                |

| 6.3 Discharge Transient Current Measurement and Its Sensitivity to Structural Defects in Dielectric Layers of Al/SiO <sub>2</sub> Interconnects |

| 6.4 Partial Discharge Dielectric Breakdown Seen in Low Voltage Al/SiO <sub>2</sub><br>Interconnects                                             |

| REFERENCES               | . 153 |

|--------------------------|-------|

| BIOGRAPHICAL INFORMATION | . 161 |

#### LIST OF ILLUSTRATIONS

| Figure Page                                                                                 |

|---------------------------------------------------------------------------------------------|

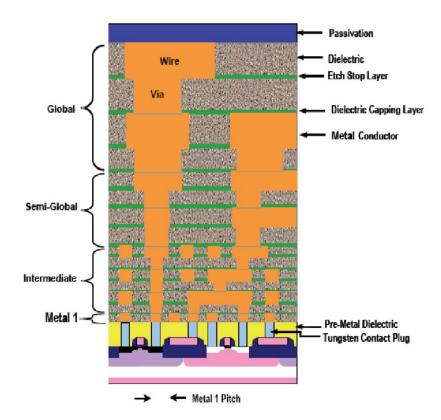

| 1.1 Typical cross-section of interconnect structure in IC chip                              |

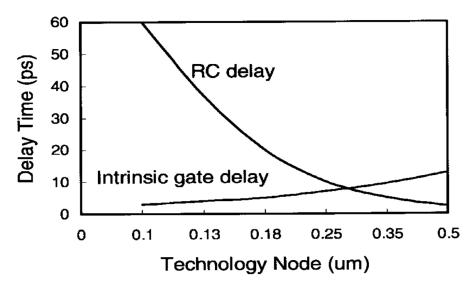

| 1.2 Gate delay versus interconnect RC delay5                                                |

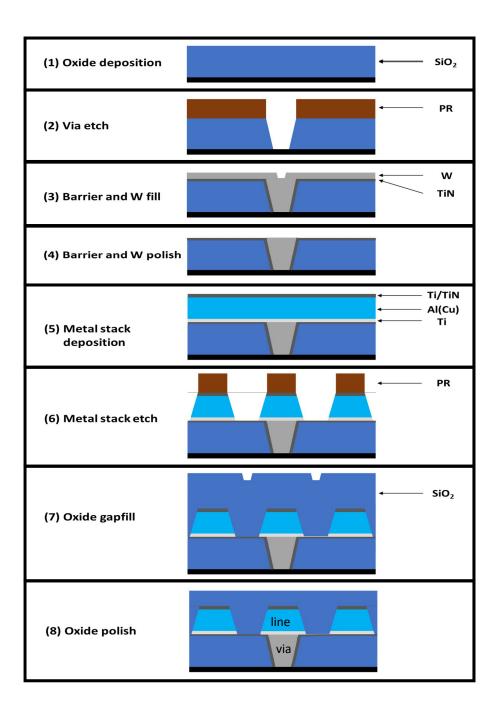

| 1.3 Schematic of cloisonné fabrication process                                              |

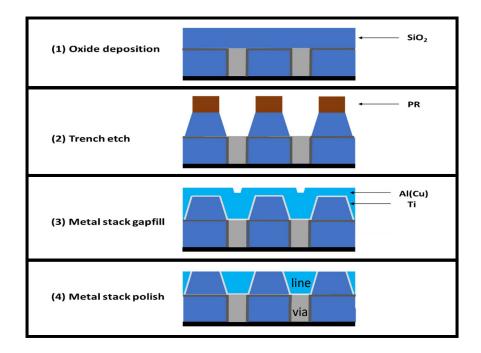

| 1.4 Schematic of damascene fabrication process for line fabrication                         |

| 1.5 Schematic of trench-first dual damascene fabrication process                            |

| 1.6 SEM image of Al/SiO2 interconnect with crack propagating inside dielectric 10           |

| 1.7 Schematic of electromigration 11                                                        |

| 1.8 Hillock/voids in metal line due to EM 12                                                |

| 1.9 Schematic of void developed by stress migration in Al line                              |

| 1.10 Schematic of temperature effect on void size and void formation speed 15               |

| 1.11 SEM image of interconnect with stress induced voids                                    |

| 1.12 Schematic of TiN acting as shunts to prevent open circuit of AI metal line 17          |

| 1.13 Schematic of a typical TDDB failure                                                    |

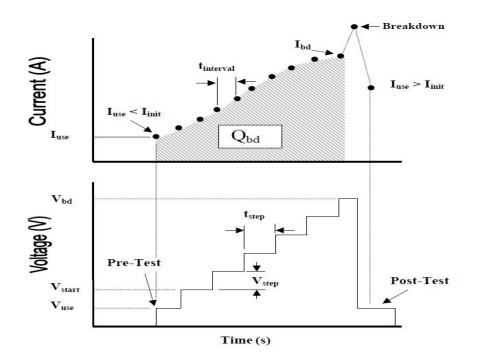

| 1.14 Schematic of voltage ramp test 20                                                      |

| 1.15 Schematic of top-down view and cross-section view SEM inspection 21                    |

| 1.16 Top-down view SEM of Al/SiO <sub>2</sub> interconnect 21                               |

| 1.17 Cross-section view SEM of Al/SiO <sub>2</sub> interconnect 21                          |

| 2.1 Schematic of defect in metal line at metal/dielectric interface from cross section view |

| 2.2 Classification of conduction mechanisms in dielectric                                   |

| 2.3 Schematic of Schottky emission                                                          |

| 2.4 Schematic of Fowler-Nordheim emission                                                   |

| 2.5 Schematic of direct tunneling                                                           |

| 2.6 Schematic of dielectric charging behavior 27                                            |

| 2.7 Schematic of leakage current in ideal condition                           | . 28 |

|-------------------------------------------------------------------------------|------|

| 2.8 Schematic of leakage current when one electrode contains defects          | . 29 |

| 2.9 Top-down view of test pattern with capping layer removed                  | . 30 |

| 2.10 Schematic of top-down view comb-serpentine structure                     | . 31 |

| 2.11 Schematic of cross section view MIM structure                            | . 31 |

| 2.12 Measurement system                                                       | . 32 |

| 2.13 Schematic of electric connection between probe station and HP 4140B unit | . 33 |

| 2.14 Schematic of sample selection based on die location                      | . 34 |

| 2.15 Schematic of electrical connection between sample and probe              | . 35 |

| 2.16 Schematic of polarity dependence measurement procedure                   | . 36 |

| 2.17 Current data from P02 center sample                                      | . 37 |

| 2.18 Schottky emission curve fit                                              | . 39 |

| 2.19 F-N tunneling curve fit                                                  | . 40 |

| 2.20 Average leakage current versus sample location                           | . 42 |

| 2.21 Leakage current under positive and negative bias from a center sample    | . 43 |

| 2.22 Leakage current under positive and negative bias from a mid-sample       | . 44 |

| 2.23 Leakage current under positive and negative bias from an edge sample     | . 44 |

| 2.24 Polarity difference versus sample location                               | . 46 |

| 2.25 Resistance versus sample location                                        | . 47 |

| 2.26 Average leakage current versus aging time                                | . 48 |

| 2.27 Polarity difference versus aging time                                    | . 49 |

| 2.28 Resistance versus aging time                                             | . 50 |

| 2.29 Top-down view SEM on edge sample (600 hours aging)                       | . 51 |

| 2.30 Top-down view SEM on edge sample (600 hours aging)                       | . 52 |

| 2.31 Top-down view SEM on edge sample (600 hours aging)                       | . 52 |

| 3.1 Schematic of I-V curve measurement                                        | . 58 |

| 3.2 Schematic of two-point measurement                                        | . 59 |

|-------------------------------------------------------------------------------|------|

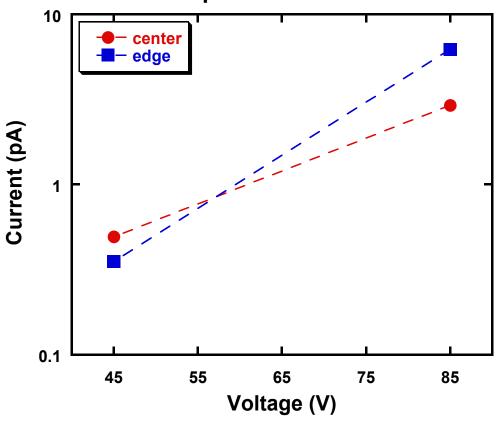

| 3.3 Typical I-V curve data from center and edge sample                        | . 61 |

| 3.4 Schematic of defect existing in metal line                                | . 62 |

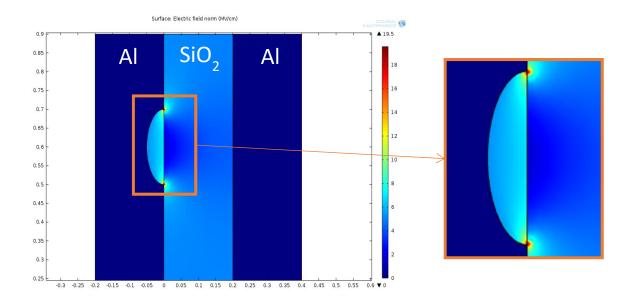

| 3.5 Simulation of electric field distribution around void                     | . 63 |

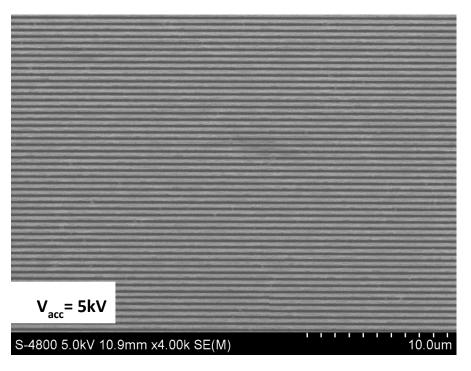

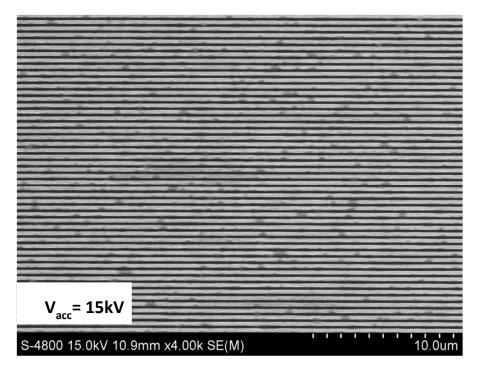

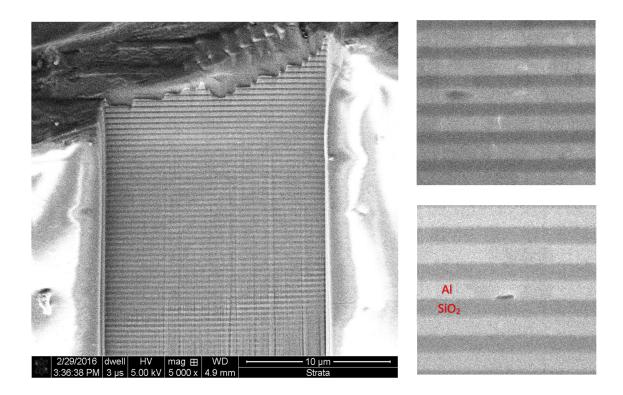

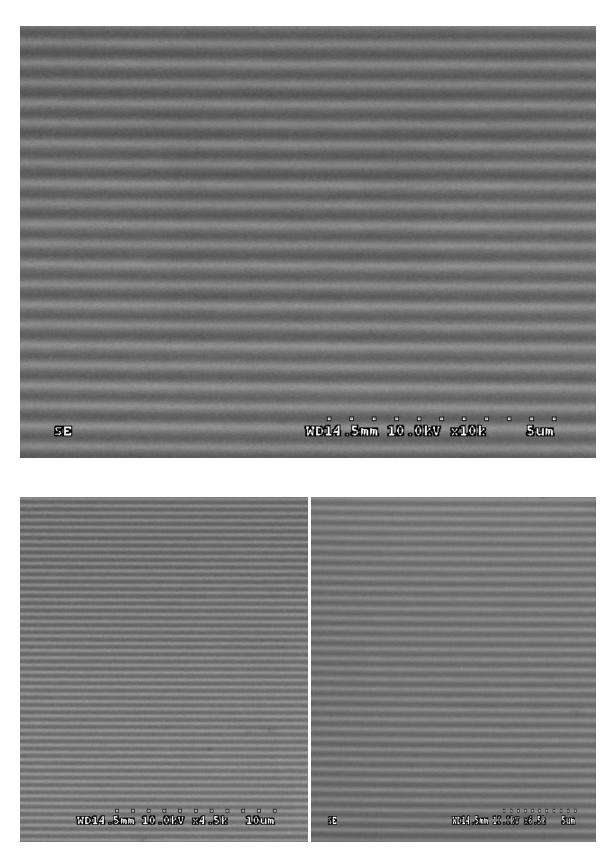

| 3.6 Top-down view SEM on edge sample at low acceleration voltage              | . 64 |

| 3.7 Top-down view SEM on edge sample at high acceleration voltage             | . 65 |

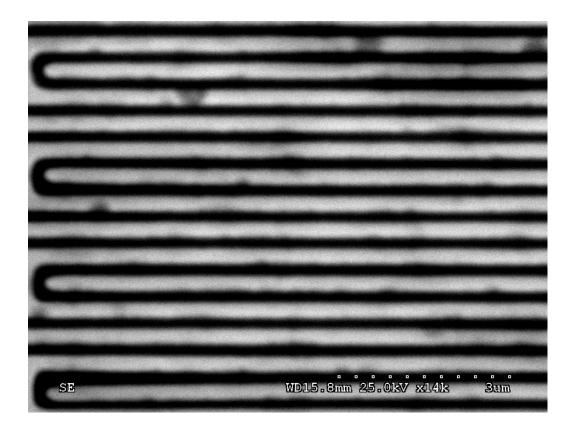

| 3.8 Top-down view SEM on edge sample at as-received condition                 | . 66 |

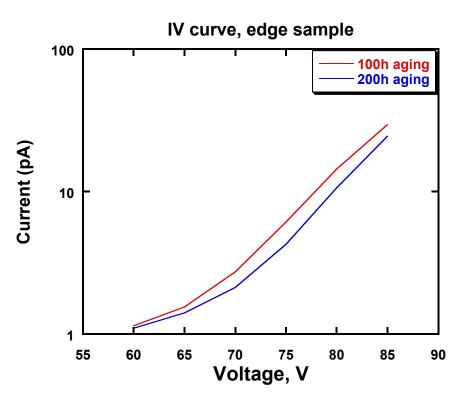

| 3.9 Typical I-V curve of edge sample after 100 and 200 hours aging            | . 67 |

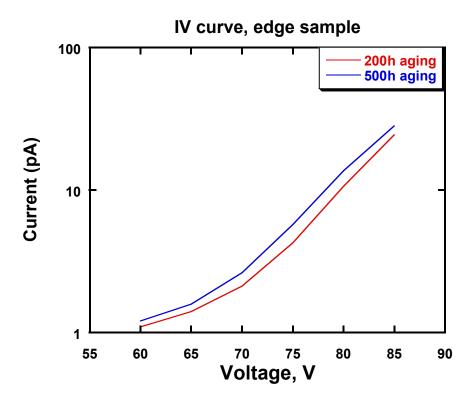

| 3.10 Typical I-V curve of edge sample after 200 and 500 hours aging           | . 67 |

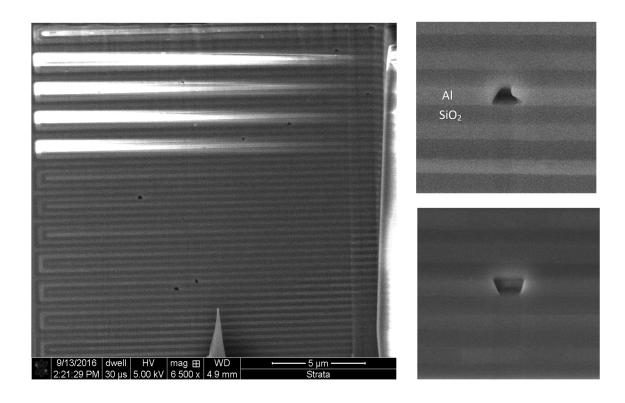

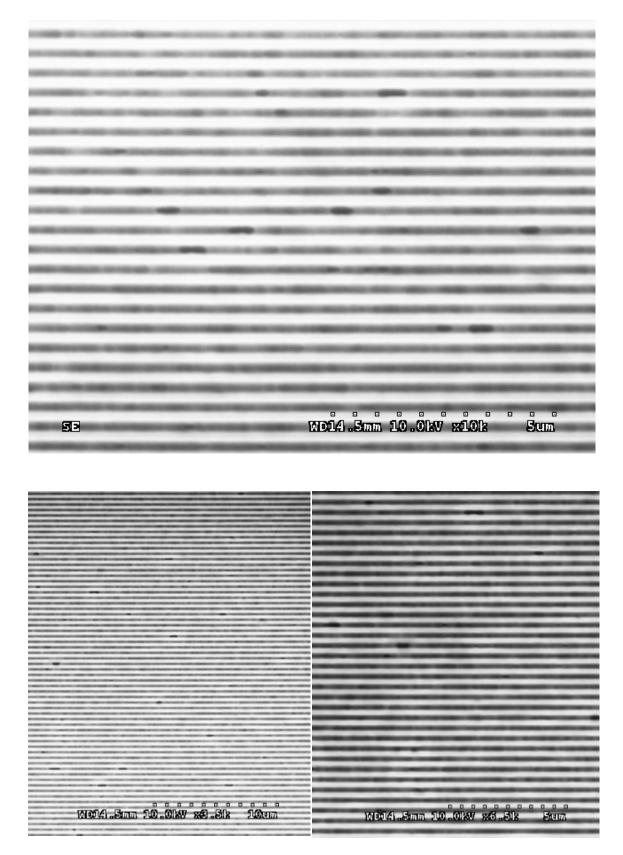

| 3.11 Top-down view SEM of edge sample at as-received condition                | . 69 |

| 3.12 Top-down view SEM of edge sample after 500 hours aging                   | . 69 |

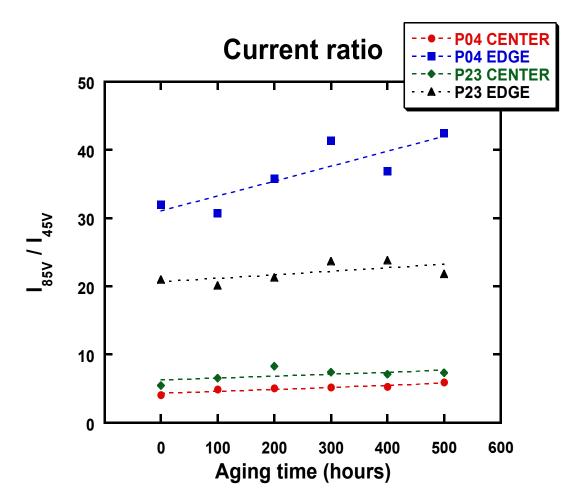

| 3.13 Two-point measurement of center and edge sample at as-received condition | . 70 |

| 3.14 Current ratio versus aging time of center and edge samples               | . 72 |

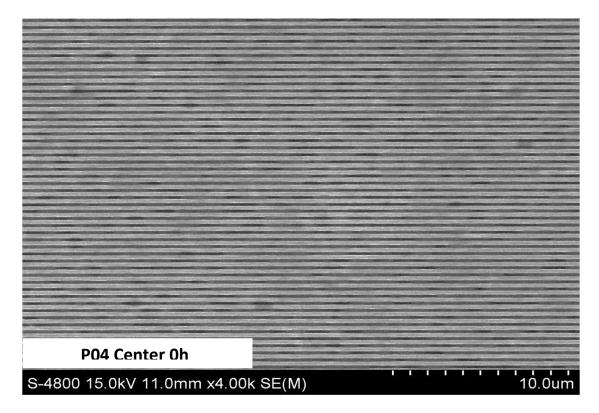

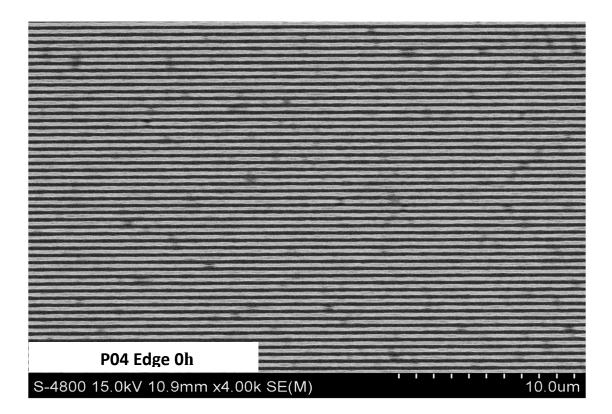

| 3.15a SEM of center sample at as-received condition                           | . 74 |

| 3.15b SEM of edge sample at as-received condition                             | . 74 |

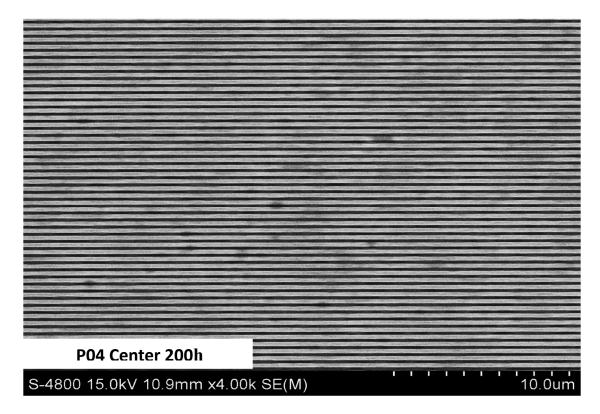

| 3.16a SEM of center sample after 200 hours aging                              | . 75 |

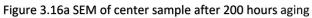

| 3.16b SEM of edge sample after 200 hours aging                                | . 75 |

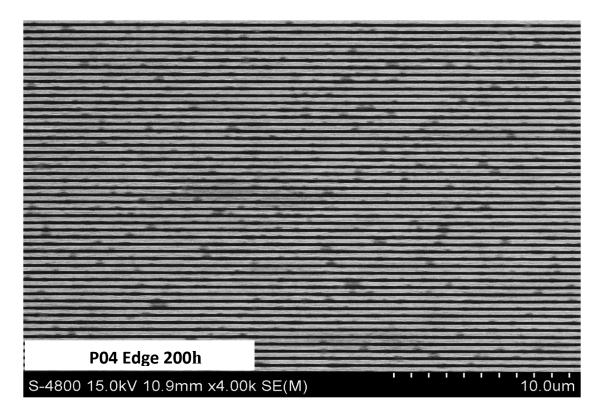

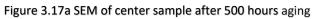

| 3.17a SEM of center sample after 500 hours aging                              | . 76 |

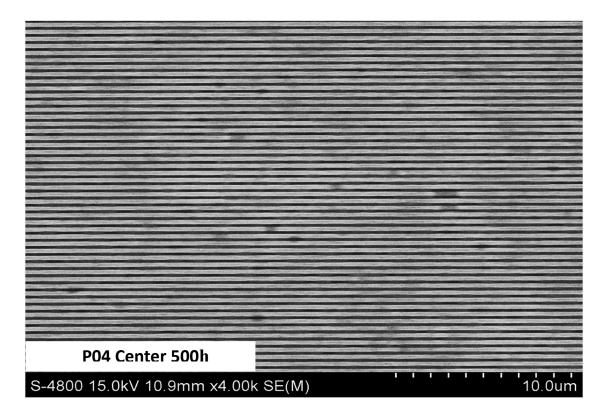

| 3.17b SEM of edge sample after 500 hours aging                                | . 76 |

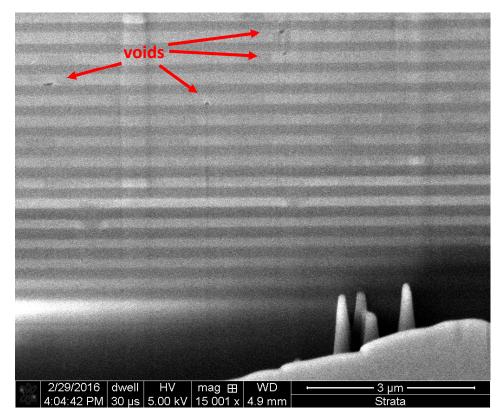

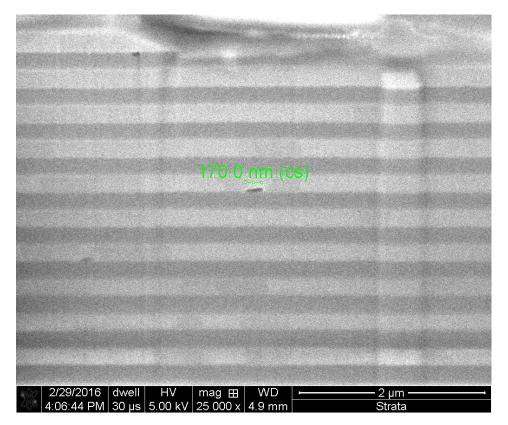

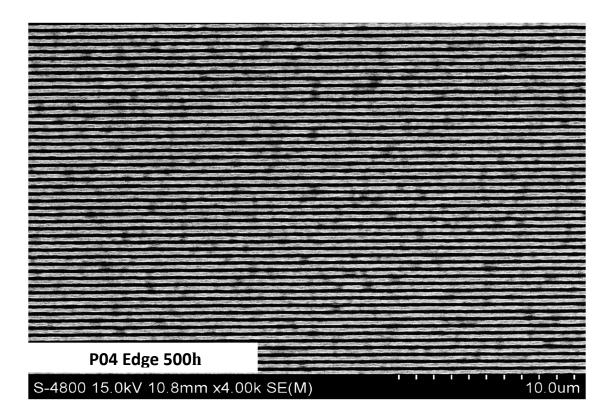

| 4.1 Voids in dielectric under SEM inspection                                  | . 80 |

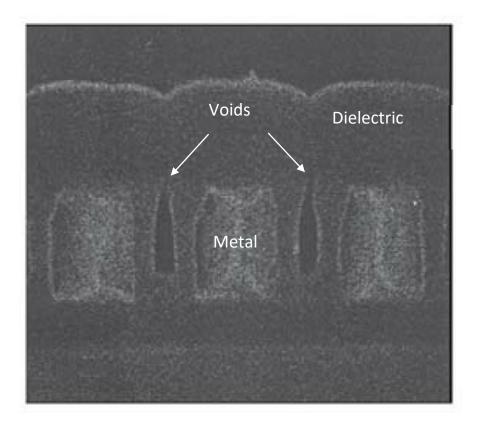

| 4.2 Schematic of electronic polarization                                      | . 84 |

| 4.3 Schematic of ionic polarization                                           | . 85 |

| 4.4 Schematic of dipolar polarization                                         | . 86 |

| 4.5 Schematic of space charge polarization                                    | . 87 |

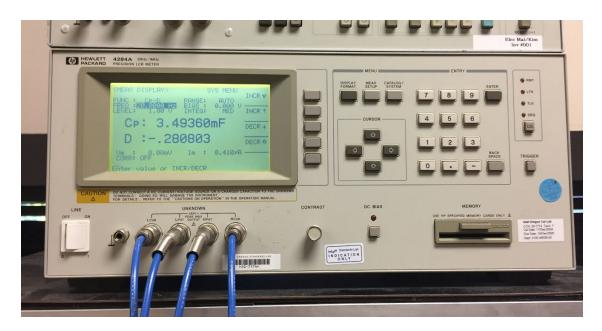

| 4.6 HP 4284A LCR meter                                                        | . 93 |

| 4.7 Schematic of discharge transient current measurement procedure            | . 94 |

| 4.8 Schematic of TSDC measurement procedure                                    | 95  |

|--------------------------------------------------------------------------------|-----|

| 4.9 TSDC data of samples from center and edge location                         | 96  |

| 4.10 TSDC data of samples under different applied electric field               | 98  |

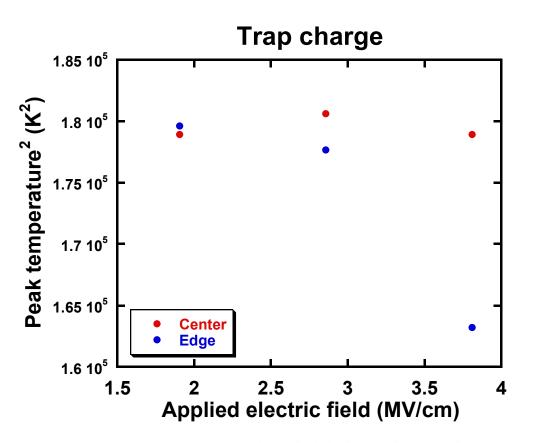

| 4.11 Temperature versus electric field plot for trap charges confirmation      | 100 |

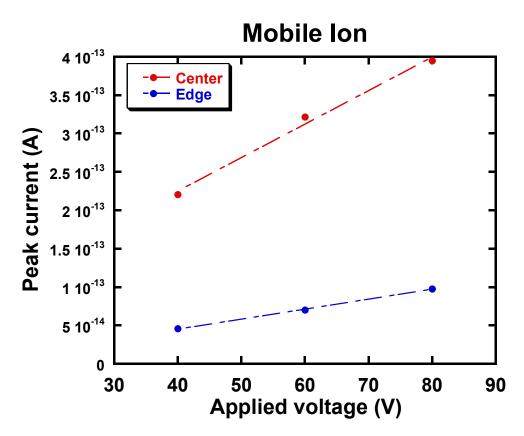

| 4.12 Peak current versus applied voltage plot for mobile ions confirmation     | 101 |

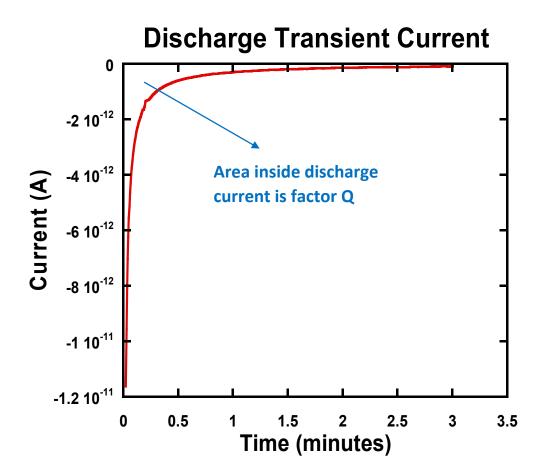

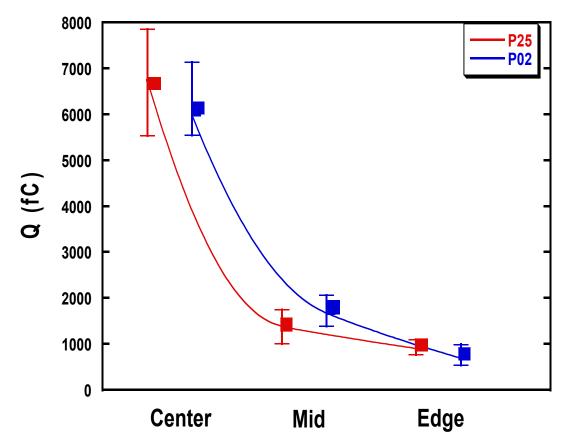

| 4.13 Typical discharge transient current and factor Q                          | 102 |

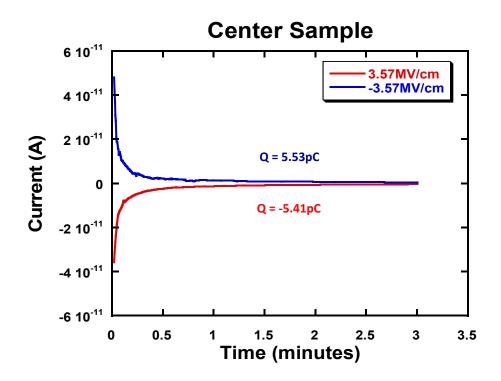

| 4.14 Typical discharge transient current and factor Q of center sample         | 103 |

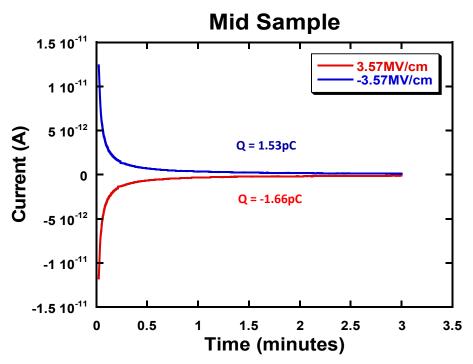

| 4.15 Typical discharge transient current and factor Q of mid sample            | 104 |

| 4.16 Typical discharge transient current and factor Q of edge sample           | 104 |

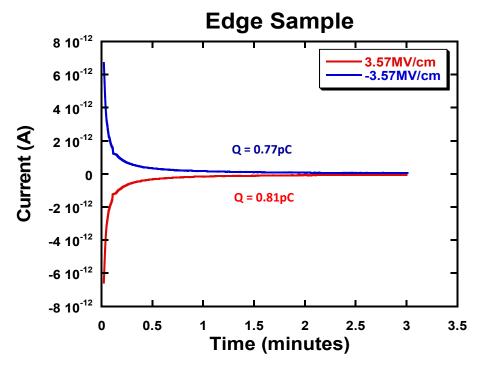

| 4.17 Schematic of charging/discharging process for sample with/without defects | 106 |

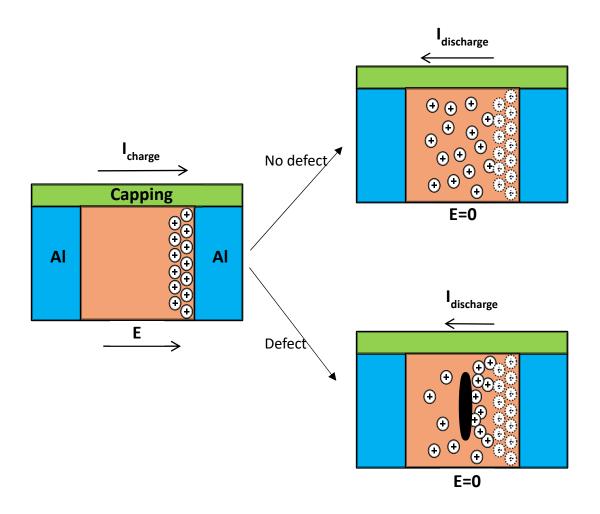

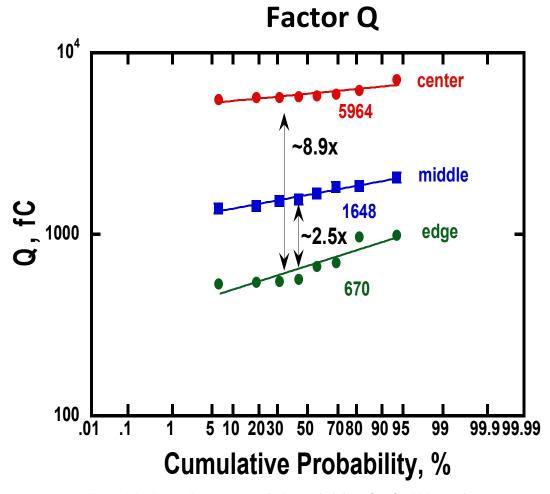

| 4.18 Factor Q data of samples from different locations                         | 108 |

| 4.19 SEM images of sample taken from center location                           | 110 |

| 4.20 SEM images of sample taken from edge location                             | 111 |

| 4.21 Factor Q versus cumulative probability of wafer P25 samples               | 112 |

| 4.22 Factor Q versus aging time of center, mid and edge samples                | 114 |

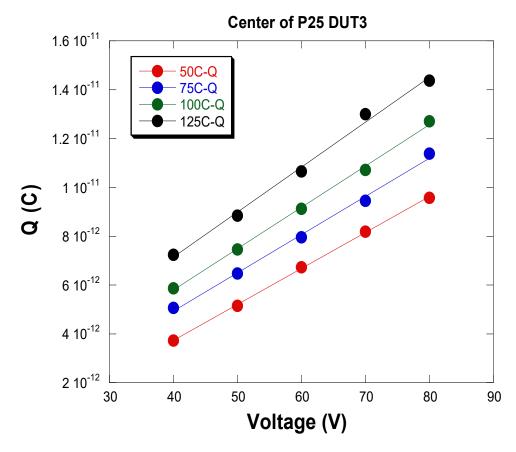

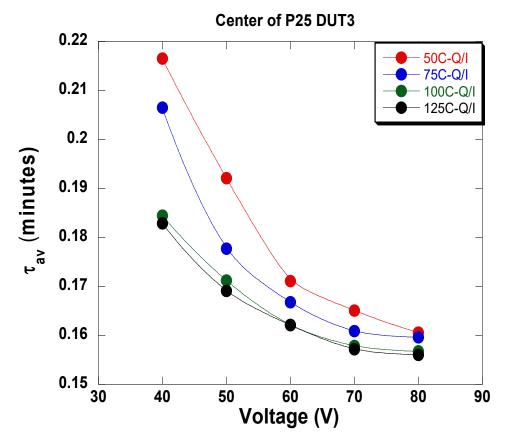

| 4.23 Factor Q versus applied bias from center sample                           | 116 |

| 4.24 Factor Q versus applied bias from edge sample                             | 117 |

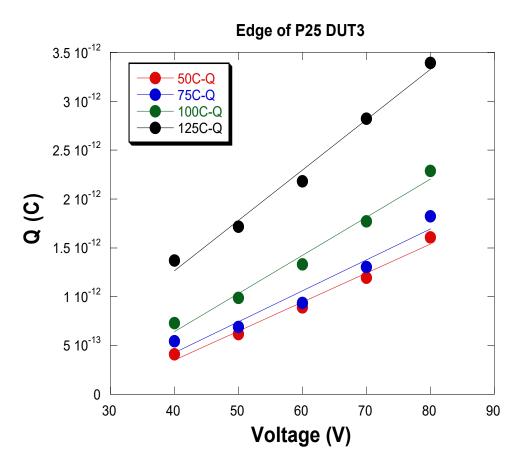

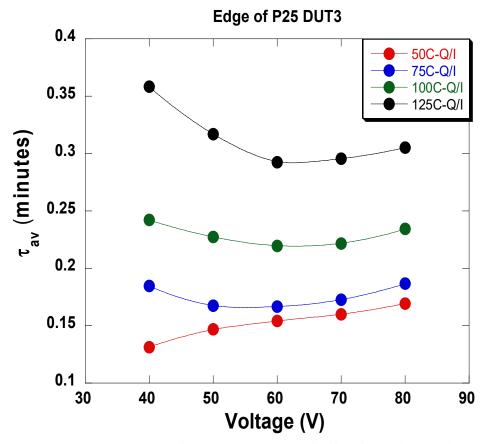

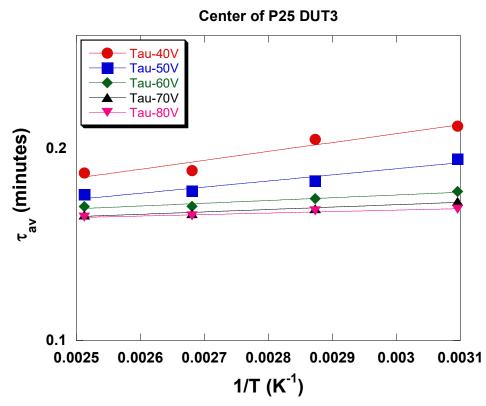

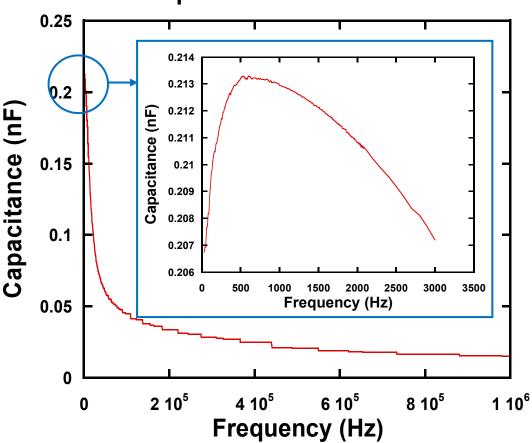

| 4.25 Average relaxation time versus applied bias from center sample            | 118 |

| 4.26 Average relaxation time versus applied bias from edge sample              | 119 |

| 4.27 Average relaxation time versus applied bias from center sample            | 120 |

| 4.28 Average relaxation time versus applied bias from edge sample              | 120 |

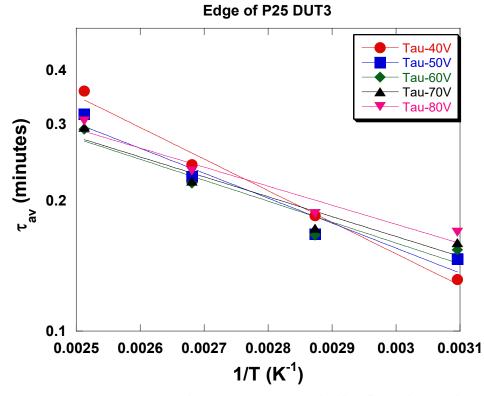

| 4.29 Activation energy versus applied electric field                           | 121 |

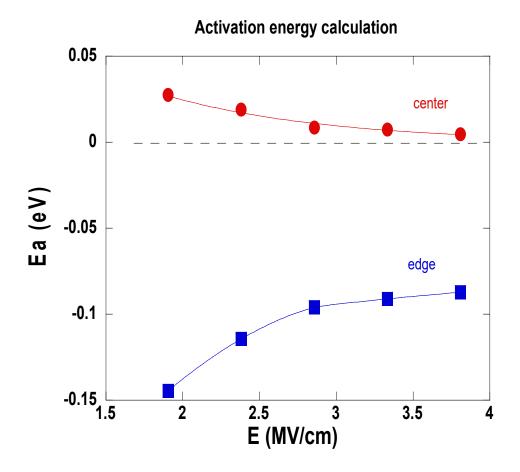

| 4.30 Typical capacitance versus AC frequency data seen in the study            | 123 |

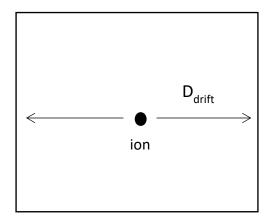

| 4.31 Schematic of ion under AC bias                                            | 125 |

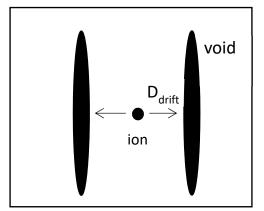

| 4.32 Schematic of ion with defects under AC bias                               | 125 |

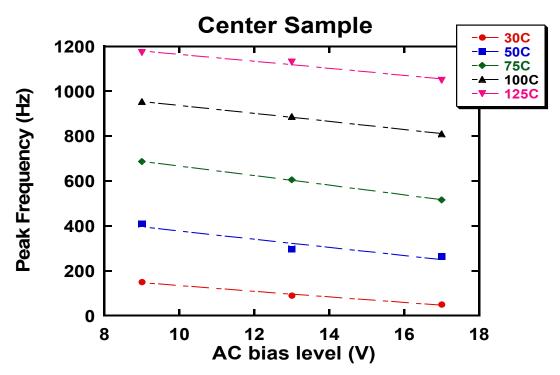

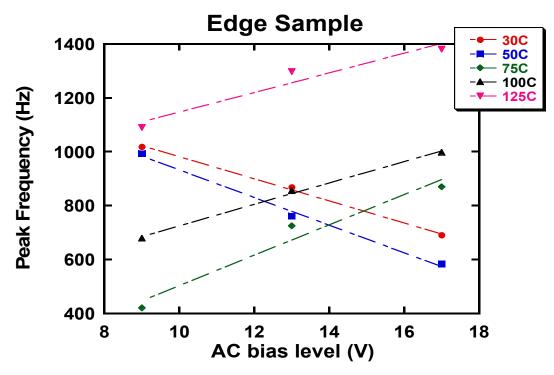

| 4.33 Peak frequency versus AC bias level for center sample                     | 126 |

| 4.34 Peak frequency versus AC bias level for edge sample                   | 126 |

|----------------------------------------------------------------------------|-----|

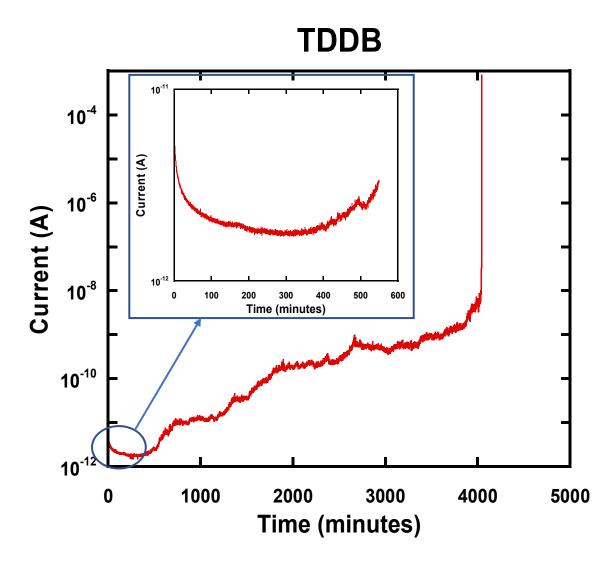

| 4.35 Typical TDDB data seen in the research                                | 128 |

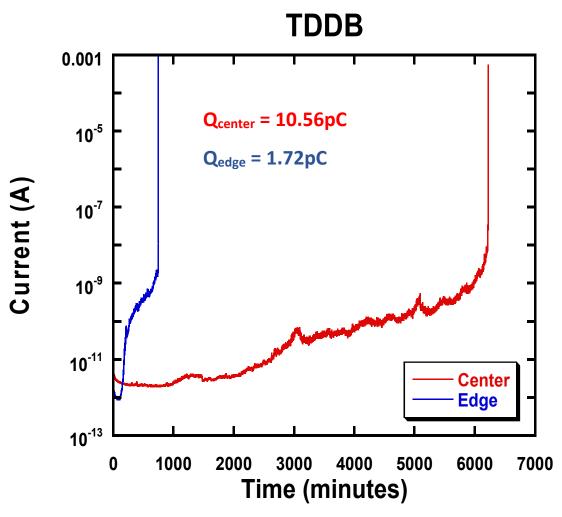

| 4.36 TDDB data of center and edge samples                                  | 130 |

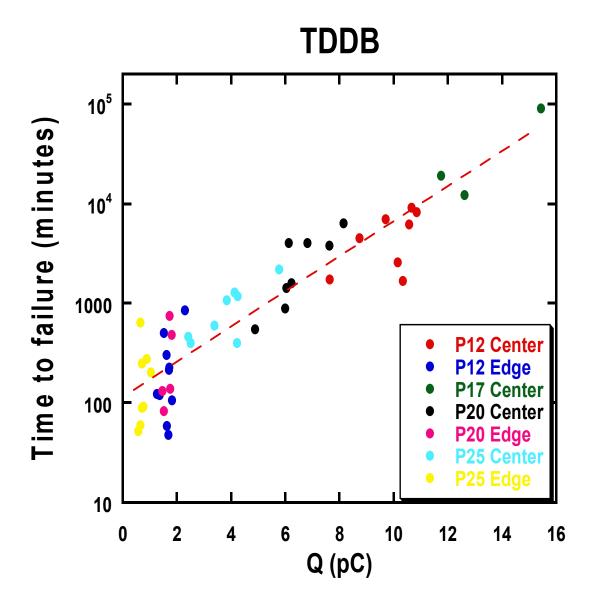

| 4.37 TDDB data of center and edge samples from 4 wafers                    | 132 |

| 5.1 Schematic of PDDB in dielectric                                        | 138 |

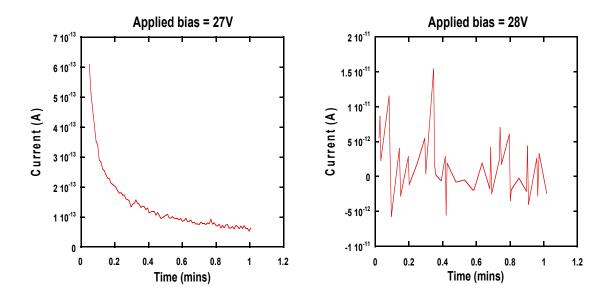

| 5.2 Abnormal leakage current data                                          | 141 |

| 5.3 Abnormal leakage current data of sample under different bias direction | 142 |

| 5.4 SEM image of sample showing abnormal charging behavior                 | 143 |

| 5.5 Leakage current data of a sample under different voltage               | 144 |

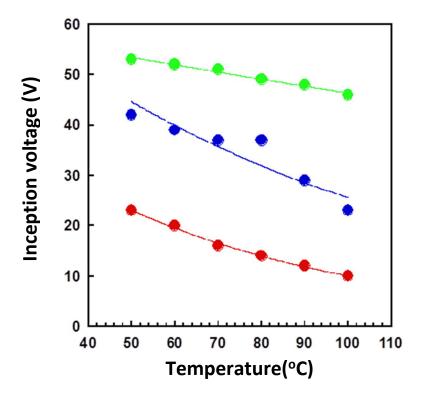

| 5.6 Inception voltage versus test temperature of three samples             | 145 |

|                                                                            |     |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Research Motivation and Achievements

Al/SiO<sub>2</sub> interconnect has been used widely in IC devices due to its low resistivity, excellent adhesion between metal lines/dielectrics and easy deposition process. As interconnects continues to scale down, achieving defect-free interconnects is increasingly difficult, becoming of a major concern. Defects in interconnect can be created during interconnect processes but also can develop at use condition by processes like electromigration, stress migration, time dependent dielectric breakdown, and a few others. Regardless of the processes, defects in either metals or dielectrics lead to a device failure and need to be eliminated or reduced.

Equally challenging to integrating interconnects without defect is their detection when they are present in either metal lines or dielectrics. In IC industry, conventional methods of detecting defect in interconnect are microscopic detections and electrical measurements. The advantage of SEM and TEM detections is that number of defects per area can be calculated and used as a parameter to determine the quality of interconnects. However, it is time inefficient, resource consuming and, most importantly, destructive to test devices. The advantage of electrical measurements are their simplicity and time efficiency. However, electrical measurement done by industry such as pattern capacitance and voltage ramp are influenced by many factors other than the defects, making the measurements to be prone to error in terms of detecting defects under

1

concern. Furthermore, electrical measurement is insensitive to defects in Al/SiO<sub>2</sub> interconnects, often yielding very weak or no relationship between electrical parameter and defects in interconnects.

The objective of this research is to find alternative electrical detection methods that provide simple electrical parameters which have a direct relationship to defects in interconnects. Therefore, several types of electrical measurement techniques including polarity dependence measurement, current-voltage curve (I-V curve) measurement, twopoint measurement and discharge transient current measurement are proposed and their capabilities to detect defects in interconnects are developed in this study.

In this research, several measurement techniques are proposed and studied, and found a few electrical parameters indicative of defects in Al/SiO<sub>2</sub> interconnects, which is far more sensitive than the conventional techniques. Specifically, polarity dependence of the leakage current is found to be effective in revealing voids in Al metal lines. In case of I-V curve measurement with polarity change in bias, it is found to be very sensitive to structural defects (voids) in Al metal lines. We simplified the IV method to make it to be more practical by taking two-point leakage current as a parameter. Although the parameter does not reveal much about the physics behind the condition in given structure and materials, it does provide a simple parameter that can be used for detection of voids in metal lines. Our study also finds that structural defects in dielectrics can be characterized by the use of the discharge transient current measurement. The total stored charge developed during charging state can be measured accurately during

2

discharging process and the total charge (Q) is found to be extremely sensitive to defects locating in SiO<sub>2</sub> dielectrics.

In order to shed light on the physics behind our techniques, background information related to Al/SiO<sub>2</sub> interconnects structure/processing, defects and conduction mechanism are briefly introduced in this chapter. What is also discussed is the pros and cons of the conventional characterization techniques used in IC industries.

#### <u>1.2 Technology of Al/SiO<sub>2</sub> Interconnects</u>

#### 1.2.1 Al/SiO<sub>2</sub> Interconnects

Figure 1.1 Typical cross-section of interconnect structure in IC chip [1]

IC (integrated circuit) chip is made of a set of compact electronic devices (transistor, resistor, capacitor, etc.) that are interconnected and located on semiconductor substrate. Therefore, interconnects refer to wires that connect each electronic devices in a chip. Conventional interconnects consists of AI as metal lines and SiO<sub>2</sub> as inter/intra layer dielectrics. Al/SiO<sub>2</sub> interconnect structure contains two essential parts: metal wires (AI-Cu alloy where AI is >97.5%, Cu is added to improve electromigration resistance [19,23]) that connect individual electronic devices and insulating dielectrics (SiO<sub>2</sub>) that isolate and mechanically support metal wires. A typical interconnect structure is demonstrated in Figure 1.1.

There is a constant demand for IC device miniaturization because performance improvements depend on the size of the devices in a chip. Working speed of IC chip is essentially determined by the delay in two places: the gate of transistors and interconnects (by RC delay), as seen in Figure 1.2. When device size is large, gate delay is the dominant factor that affects the device operation speed. However, reduction in devices size makes the gate length to be smaller, results in the delay caused by the interconnect to be more dominant because it makes the resistance to increase in metal lines and capacitance to increase in dielectric layers [2]. To overcome RC delay limit, Cu/PLK interconnects have been developed and implemented to a few advanced devices like microprocessors [3-6]; yet majority of IC devices still use Al/SiO<sub>2</sub> interconnects [7] to take advantage of their superior reliability and processability.

4

Figure 1.2 Gate delay versus interconnect RC delay [2]

#### 1.2.2 Al/SiO<sub>2</sub> Interconnect Processing

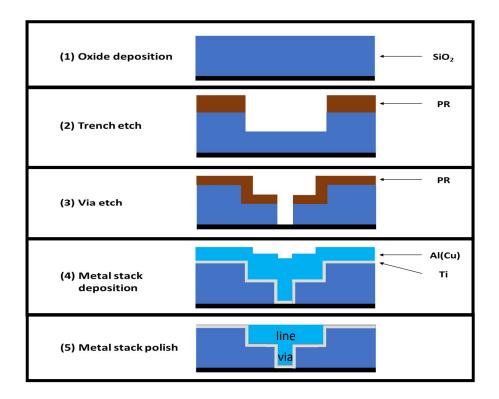

There are three types of fabrication process in Al/SiO<sub>2</sub> metallization: cloisonné fabrication process [8], damascene fabrication process [9,10] and dual damascene fabrication process [11]. For cloisonné fabrication process and damascene fabrication process, vias and lines are fabricated separately, but for dual damascene fabrication process, vias and lines are fabricated through a single process.

Cloisonné fabrication process is the most common process used in Al/SiO<sub>2</sub> metallization. In the process, vias are fabricated first and lines are fabricated later. Figure 1.3 is a schematic of a typical cloisonné fabrication process. Process starts with SiO<sub>2</sub> depositing onto substrate through chemical vapor deposition (CVD) process (step 1).

Figure 1.3 Schematic of cloisonné fabrication process

Then photoresist (PR) is coated onto oxide layer and patterned through lithography process. After that, area without PR is removed by reactive ion etching (RIE) process (step 2). Once trench of via is produced, PR is removed by cleaning process. Barrier layers like

(TiN) and Tungsten (W) are then deposited onto oxide layer through CVD process (step 3), followed by chemical mechanical polishing (CMP) process to result in via fabrication (step 4). After the via, Ti, Al and TiN (or Ti) are deposited by physical vapor deposition (PVD) or CVD process in sequence to create metal stack (step 5). The metal stack is then patterned with PR and etched through RIE process to create desired trench (step 6). After removal of PR, dielectric layer (SiO<sub>2</sub>) is deposited through CVD process to isolate Al metal lines (step 7). After CMP planarization, lines are fabricated (step 8).

Damascene process is used to fabricate Cu/PLK interconnects [12]. In actuality, damascene process is initially developed for Al/SiO<sub>2</sub> interconnects and is still used in the industry. First step of the process is via fabrication and it is identical to cloisonné fabrication process. Second step of the process is line patterning. Figure 1.4 is the schematic of typical damascene process for line fabrication.

Figure 1.4 Schematic of damascene fabrication process for line

As is shown in Figure 1.4, the process starts with deposition of dielectric layer (SiO<sub>2</sub>) through CVD process (step 1). Wafer is then patterned with PR through lithography process and etched by RIE process to create desire trench (step 2). It is then followed by the deposition of Ti and Al onto wafer by PVD or CVD process in sequence (step 3). After CMP planarization, Al metal lines are created (step 4).

As is previously discussed, cloisonné and damascene process require approximately the same number of steps to fabricate a planar interconnect level. Therefore, the cost of both processes does not show significant difference. However, cost of damascene process can be further reduced by the improved procedure known as the dual damascene which vias and lines are fabricated in a single step. Figure 1.5 shows the typical trench-first dual damascene fabrication process.

Figure 1.5 Schematic of trench-first dual damascene fabrication process

According to Figure 1.5, first step is to deposit oxide layer onto substrate (step 1). Wafer is then patterned with PR through photolithography process and etched by RIE process to create trench for metal line (step 2). Once trench is formed, another set of PR is patterned onto wafer and trench of via is produced by RIE etching (step 3). Deposition of Ti and Al by PVD or CVD in sequence complete the metal layer process (step 4). After CMP, via and line are fabricated (step 5).

#### <u>1.3 Common Failure Mechanisms Seen in Al/SiO<sub>2</sub> Interconnects</u>

As size of interconnects is scaling down to increase the performance of IC chips, defects in interconnects has become a major reliability concern in industry. Defects in interconnect can result from different mechanisms but can be categorized into two. The first is process related such as trapping voids and cracking. The second is the defects developed at use condition that includes the mechanism like electromigration in metal lines, stress migration induced voiding in metal lines, time dependent dielectric breakdown in dielectrics. These defects reduce the lifetime of interconnects and limit the reliability of the IC devices. Some of the common failure mechanisms seen in Al/SiO<sub>2</sub> interconnects are briefly introduced in this section.

#### 1.3.1 Cracking

Cracking is one of the common failure mechanisms seen in interconnects and is known to result in delamination of capping layer and  $AI/SiO_2$  interconnects [13] or facture of SiO<sub>2</sub> dielectric [14]. Capping layer (usually SiN) refers to the protective layer deposited

on top of interconnects to protect them from the environment. Crack can initiate at the flaws in capping layer thin film or SiO<sub>2</sub> dielectric and propagate through metal/dielectric interfaces (delamination) or dielectrics (cracks). This process is driven by thermal expansion mismatch in materials in the structure. There are three cracking modes [15,16]. Mode I crack is also known as the crack opening mode where a tensile stress normal to the plane of crack is applied. Mode II cracking is also known as the in-plane shear mode where a shear stress is parallel to the plane of crack and perpendicular to crack tip. Mode III cracking, also known as out-of-plane shear mode, occurs by a shear stress that is parallel to the plane of crack tip. Among all different crack modes, mode I is

Figure 1.6 SEM image of Al/SiO2 interconnect with crack propagating inside dielectric [14]

most commonly seen in interconnects [13] and Figure 1.6 is a SEM image of  $AI/SiO_2$  interconnect with crack propagating inside  $SiO_2$  dielectric.

1.3.2 Electromigration

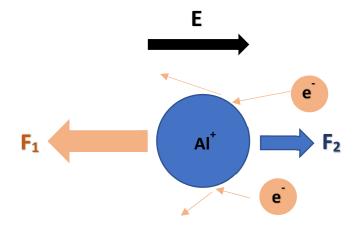

Figure 1.7 Schematic of electromigration

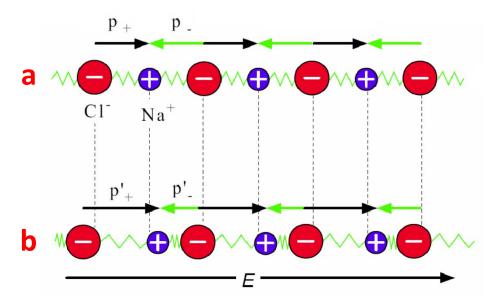

Electromigration (EM) is a phenomenon which metal ions are migrating towards opposite direction of applied electric field due to collision with electrons flowing inside metal lines [17-21] and Figure 1.7 is a schematic of electromigration in Al metal lines. As indicated by Figure 1.7, Al ions are subjected to two opposite driving forces ( $F_1$  and  $F_2$ ).  $F_1$  is created by momentum transfer between electrons and Al ions. This force is known as wind force with same direction to electron flow.  $F_2$  is created by effect of external electric field on Al ions. This force is known as field force with direction opposite to electron flow. When current density is high enough ( $10^{5}$ - $10^{6}$  A/cm<sup>2</sup>) [22],  $F_1$  is much larger than  $F_2$  and Al ions will move in same direction as electron flow. Therefore, EM can be considered as a diffusion induced by wind force and diffusion flux of EM is governed by equation

$$J = \frac{D*C}{k*T} * z * e * \rho * j \tag{1}$$

First part of equation (1) governs kinetics where *D* is diffusion coefficient, *C* is concentration, *k* is Boltzmann constant and *T* is temperature. Second part of the equation (1) governs driving force where *z* is effective valence, *e* is electron charge,  $\rho$  is flux density and *j* is current density.

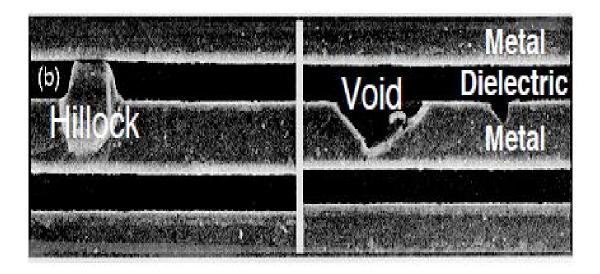

Figure 1.8 Hillock/voids in metal line due to EM [7]

In Al/SiO<sub>2</sub> interconnects, during electromigration, Al ions will migrate towards direction of electron flow and accumulate at anode. Therefore, hillocks will grow on anode side and voids will develop on cathode side, as seen in Figure 1.8. Since hillocks are deposition of conductive Al atoms, development of hillocks will lead to short circuit between different metal wires. Voids are empty spaces that are lacking atoms and do not conduct electric current. Therefore, as voids develop, cross-section of conduction path is reduced and this will increase current density and joule heat created by current. This will further accelerate growth rate of voids and eventually lead to open circuit of metal wires.

In either case, EM will decrease reliability of Al/SiO<sub>2</sub> interconnects and mean time to failure (MTTF) is govern by equation [20,21]

$$MTTF = \frac{A}{j^n} * \exp\left(\frac{E_a}{k*T}\right)$$

(2)

where A is a constant that is related to properties and geometry of metal lines, *j* is current density, *n* is current exponent,  $E_a$  is activation energy, *k* is Boltzmann constant and *T* is temperature.

#### 1.3.3 Stress Induced Voiding

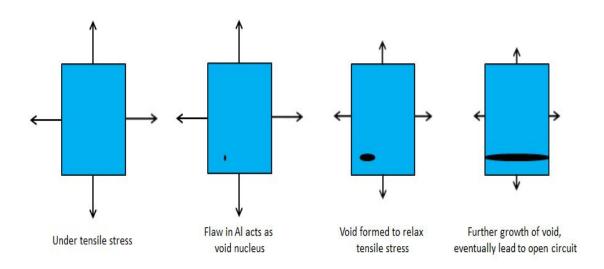

Figure 1.9 Schematic of void developed by stress migration in Al line

In 1980s, in order to further scale down interconnects to improve performance, narrow Al lines with line width comparable to line thickness were introduced. Soon it was discovered that voids can develop in wafers that were put in oven at high temperature, or even on shelves at room temperature [24-26]. This void formation mechanism is known as stress induced voiding or stress migration. As Al line width and line thickness decreased, stress induced voiding will occur more easily.

Basic mechanism of stress induced voiding is related to the difference in coefficient of thermal expansion (CTE) between metal lines and surrounding dielectric materials [27-31]. For Al/SiO<sub>2</sub> interconnect, aluminum line has a much larger CTE than SiO<sub>2</sub>. During fabrication of lines, aluminum lines are encapsulated in dielectrics at high temperature. This temperature is known as stress free temperature because there is no stress associated with Al lines and surrounding dielectrics. After cooling down to room temperature, due to huge CTE misfit of Al and SiO<sub>2</sub>, Al lines are subjected to a triaxial tensile stress that is larger than yield strength of Al. However, under uniform tension, aluminum lines are in equilibrium state and no atom diffusion will occur. But if any flaw exists in aluminum line, it can serve as void nucleus. Since stress around nucleus is lower, aluminum atom will diffuse away from nucleus. Therefore, by growing the void, tensile stress can be relaxed (as shown in Figure 1.9).

There are two factors that can affect the speed of void formation and the size of voids. The first factor is the tensile stress that is proportional to difference between operating temperature T and stress free temperature  $T_0$ . As discussed in previous paragraph, due to CTE mismatch of metal lines and dielectrics, lower operating temperature will create to a higher CTE mismatch, which leads to higher tensile stress for Al lines. The second factor is diffusivity of atoms, which is proportional to operating temperature. Atomic diffusivity *D* is governed by equation

14

$$D = D_0 * \exp\left(\frac{-E_a}{kT}\right) \tag{3}$$

where  $D_0$  is temperature independent preexponential,  $E_a$  is activation energy for diffusion, k is Boltzmann's constant and T is temperature.

Operating temperature, T

Figure 1.10 Schematic of temperature effect on void size and void formation speed [13]

Figure 1.10 is a schematic that represents relationship between operating temperature and the two factors that are affecting void size and formation speed. Figure 1.10 indicates that these two factors are working against each other, CTE stress decreases as operating temperature increases and atomic diffusivity increases when temperature decreases. However, there is a middle point (150°C to 200°C) where void size and formation speed can reach their maximum value.

Conventional method used to monitor stress induced voiding activity is to measure the electrical resistances of metal lines as a function of time. Failing criterial is set to be 20% increase in resistance compares to time zero value. Median time to failure (MTF) of stress induced voiding is then governed by equation [32]

$$MTF = \frac{C}{(T_0 - T)^N} * \exp\left(\frac{E_a}{kT}\right)$$

(4)

where *MTF* refers to average time needed for half of the test wafers to fail, *C* and *N* are fitting parameters,  $T_0$  is stress free temperature, *T* is operating temperature,  $E_a$  is activation energy and *k* is Boltzmann's constant.

Figure 1.11 SEM image of interconnect with stress induced voids [32]

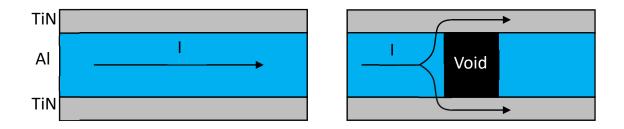

Figure 1.11 is the SEM image of an interconnect that is in the early stage of stress induced voiding activity. As voids further develop, metal lines will be discontinued and interconnect will experience open circuit failure. However, stress induced voiding activity can be mitigated by several methods that were originally developed to improve EM failure resistance. First method is to add tiny amount of Cu into Al to from Al-Cu alloy, it is reported that by doing so, diffusion rate of Al atoms can be reduced by two orders of magnitude [19]. Second method is to implement materials with low diffusivity, such as W and TiN, into the interconnects as adhesion layer between metal lines and dielectrics [33]. If metal lines are opened due to voids, these materials can act as shunts and still conduct electric current (Figure 1.12). Third method is to replace long Al lines with short Al lines. Since volume of metal lines that needs to be relaxed is reduce, stress migration effect is less severe [34].

Figure 1.12 Schematic of TiN acting as shunts to prevent open circuit of Al metal line

#### 1.3.4 Time Dependent Dielectric Breakdown

Time dependent dielectric breakdown (TDDB) refers to the breakdown that occurs after a long-time application of relatively low electric field (lower than dielectric strength of materials) due to the degradation of dielectric overtime [35-39]. Initially, TDDB is a phenomenon mostly seen in front-end-of-line transistors due to high electric field associated with thin gate oxides. However, as integrated circuit continue to scale down, electric field across interconnect has greatly increased and TDDB has become major concern in back-end-of-line interconnects as well.

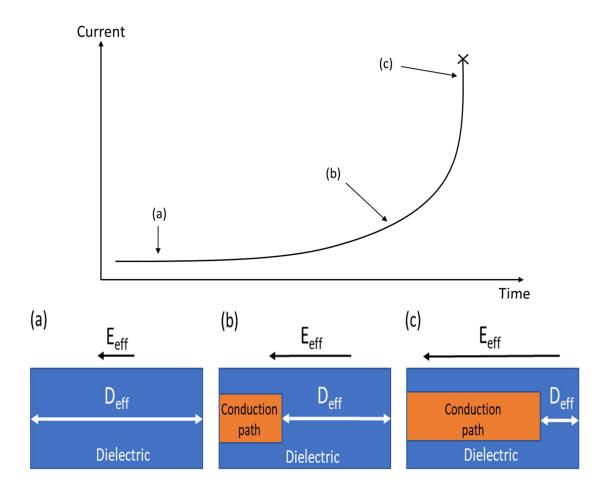

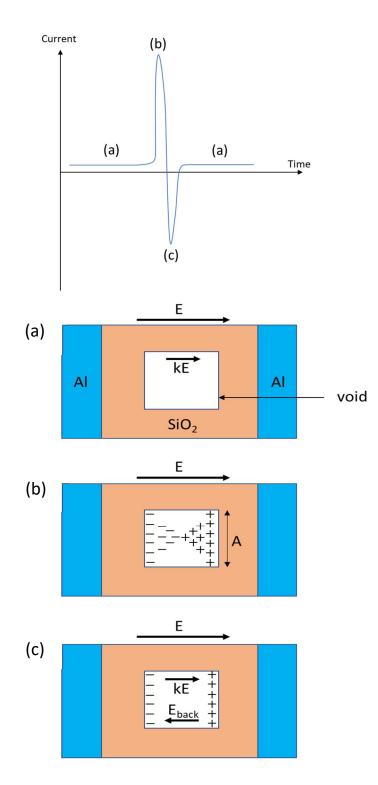

Figure 1.13 Schematic of a typical TDDB failure

Figure 1.13 is the schematic of a typical TDDB failure. In the figure, leakage current of dielectric is plotted as function of operation time. Based on leakage current, TDDB development can be divided into three stages: (a) early stage (b) short circuit development stage (c) final breakdown stage. Initially, SiO<sub>2</sub> dielectric is intact and effective dielectric width D<sub>eff</sub> is equal to dielectric width D (Figure 1.13a). At this stage, leakage current does not vary with operation time. However, after operated for a long time, part of dielectric starts to degrade and lose its insulating properties. Therefore, a conduction path starts to form inside dielectric and D<sub>eff</sub> is reduced. Since electric field equals to voltage divided by width, with D<sub>eff</sub> reduced, E<sub>eff</sub> is increased and leakage current increases (Figure 1.13b). As dielectric degrades over time, conduction path is further elongated and leakage current continue to increase until a critical point where E<sub>eff</sub> is larger than dielectric strength of SiO<sub>2</sub> and dielectric breakdown will occur, resulting in a spike increase of leakage current (Figure 1.13c). To understand and prevent TDDB, source of dielectric degradation has to be investigated. Several different mechanisms had been proposed to explain the phenomenon of dielectric degradation and these mechanisms will be discussed in chapter 4.

#### 1.4 Conventional Defect Detection Methods

#### 1.4.1 Line Resistance Measurement

Line resistance measurement is a common technique used to evaluate stress induced voiding and electro migration void formation. Resistance of metal lines is monitored during operation and if resistance is increased by 20% compares to its original value, metal line is considered as failure. Advantage of this technique is its simplicity. However, this technique is not very sensitive to defects as measured resistance is an average value of the whole metal line but no only the area that contains voids.

#### 1.4.2 Voltage Ramp Test

Voltage ramp test is conducted by the industry as it reveals dielectric properties through measurement of breakdown voltage. As indicated by Figure 1.14, basic

19

procedure is to apply voltage to sample for certain amount of time, then increase voltage step by step until sample breaks down. The applied voltage that breaks the sample is known as breakdown voltage and it is proportional to the physical properties of dielectrics [40]. However, there are many factors that contribute to breakdown voltage, which makes it insensitive to structural defect in dielectric

Figure 1.14 Schematic of voltage ramp test [40]

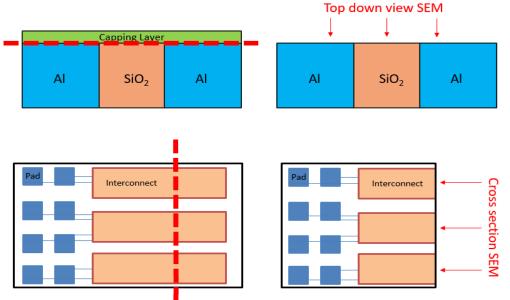

# 1.4.3 Scanning Electron Microscope Inspection

Scanning electron microscope (SEM) inspection can reveal the quality of interconnects. There are two types of SEM inspections: top-down view SEM and cross-section view SEM. Figure 1.15 is a schematic of both SEM inspections. Based on SEM view direction, either capping layer (top down view) or excessive interconnect (cross

section view) needs to be removed. It can be done through chemical etching, focus ion beam etching, ion milling, chemical mechanical polishing, etc.

Figure 1.15 Schematic of top-down view and cross-section view SEM inspection

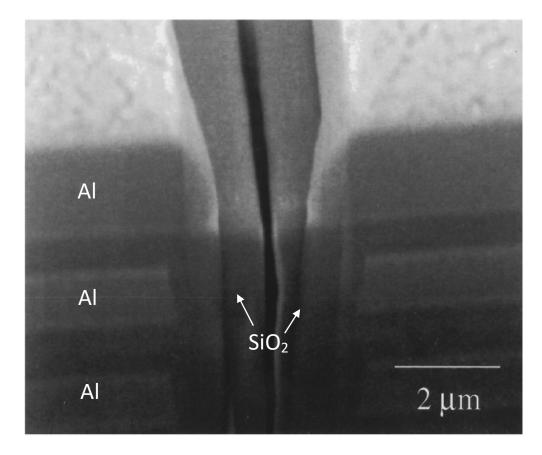

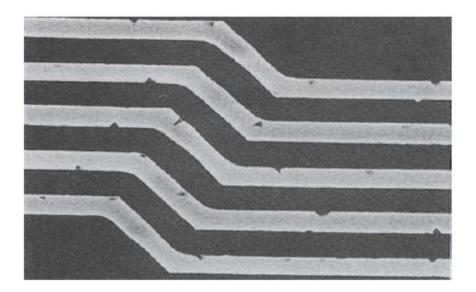

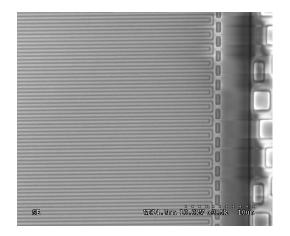

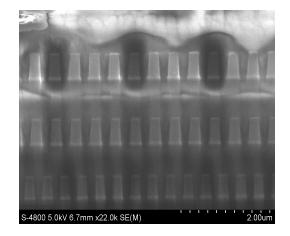

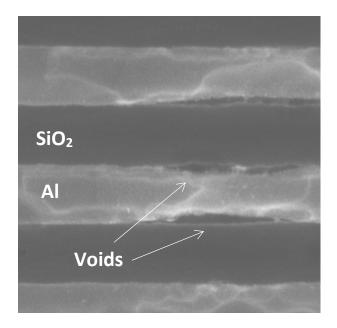

Top-down view SEM images gives better overview of defect distribution in single metal layer while cross-section view SEM images can show multiple metal layers simultaneously (Figure 1.16 and 1.17). Despite all the advantages that SEM inspection has, it is a destructive and time-consuming technique.

Figure 1.16 Top-down view SEM of Al/SiO<sub>2</sub> interconnect

Figure 1.17 Cross-section view SEM of Al/SiO<sub>2</sub> interconnect

#### **CHAPTER 2**

# POLARITY DEPENDENCE MEASUREMENT AND ITS SENSITIVITY TO STRUCTURAL DEFECTS IN ALUMINUM LINES OF AL/SIO<sub>2</sub> INTERCONNECTS

#### 2.1 Background

The purpose of this measurement technique is to provide a self-reference parameter (*polarity difference*) that can be used to determine defect distribution in metal line (Figure 2.1). This detection technique is based on measuring leakage current of dielectrics under electric field. Leakage current refers to current that flows through insulating dielectrics under applied electric field due to different conduction mechanisms. Samples with and without defect are expected to show different level of leakage current

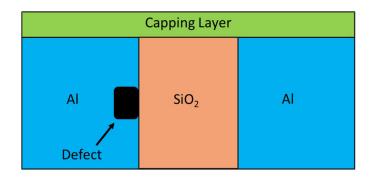

Figure 2.1 Schematic of defect in metal line at metal/dielectric interface from cross section view

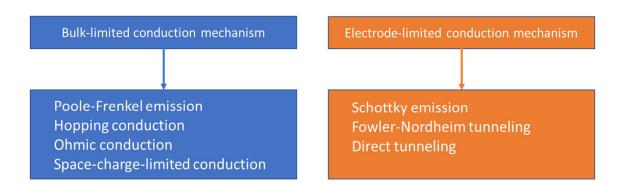

Based on how current is transported, conduction mechanism can be divided into two categories: bulk-limited conduction mechanisms and electrode-limited conduction mechanisms [41-50]. If current transportation is determined by properties of dielectric bulk, the conduction mechanism is bulk controlled. If current transportation is determined by properties of metal/dielectric interface, the conduction mechanism is electrode controlled. Figure 2.2 shows typical conduction mechanisms under different categories.

Figure 2.2 Classification of conduction mechanisms in dielectric

Since this measurement technique are focusing on detecting defects at interface of metal/dielectric, bulk-limited conduction mechanisms are considered to have similar effect on samples with/without defect at interface as intrinsic dielectric properties of samples should be the same. Therefore, in this measurement technique, electrodelimited conduction mechanisms are much more important and the conduction mechanism that is major contributor to leakage current must be determined.

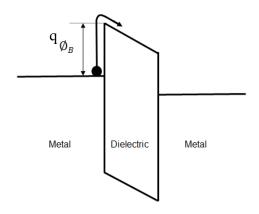

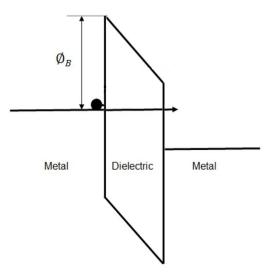

# 2.1.1 Schottky Emission

Schottky emission occurs when electron obtains enough energy through thermal activation to overcome potential barrier at metal/dielectric interface and emits into dielectric [51, 62]. Besides electron obtaining enough energy to overcome potential barrier, barrier height can also be reduced by image force. When electron in dielectric is close to metal/dielectric interface, it will sense an electrostatic field that acts as if an equal but opposite charge is locating at metal side of metal/dielectric interface at mirror image position. Electron and its image charge will attract each other and reduce potential barrier height, which will allow more electron to overcome barrier. Therefore, there are three factors that will strongly affect current density of Schottky emission: potential barrier height of metal/dielectric interface, applied electric field and temperature. Figure 2.3 is a schematic of Schottky emission at metal/insulator interface. The difference in Fermi level of two metals is due to applied electric field.

Current density of Schottky emission is [52-54]

$$J = A^* T^2 \exp\left[\frac{-q\left(\phi_B - \sqrt{qE/4\pi\varepsilon_r\varepsilon_0}\right)}{kT}\right]$$

(5)

$$A^* = \frac{4\pi qk^2 m^*}{h^3} = \frac{120m^*}{m_0}$$

(6)

where J is current density,  $A^*$  is effective Richardson constant,  $m_0$  is free electron mass,  $m^*$  is effective electron mass in dielectric, T is absolute temperature, q is electron charge,  $q\phi_B$  is barrier height, k is Boltzmann's factor, h is Planck's constant,  $\varepsilon_0$  is permittivity in vacuum,  $\varepsilon_t$  is optical dielectric constant and E is electric field across dielectric.

Figure 2.3 Schematic of Schottky emission

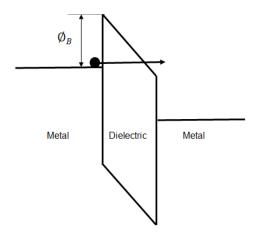

#### 2.1.2 Fowler-Nordheim Tunneling

F-N tunneling occurs when electron penetrates energy barrier at metal/dielectric interface even if it does not have sufficient energy [55,59-61]. According to quantum physics, even if electron does not have enough energy to overcome potential barrier, it still has a chance to penetrate the triangular area of potential barrier created by high electric field [56]. The most impactful factor in F-N tunneling is applied electric field while temperature has little effect. Typical electric field for F-N tunneling to occur is >2MV/cm [57]. Figure 2.4 is a schematic of F-N tunneling.

Figure 2.4 Schematic of Fowler-Nordheim emission

Current density is of F-N tunneling is [52]

$$J = \frac{q^{3}E^{2}}{8\pi hq\phi_{B}} \exp\left[\frac{-8\pi (2qm_{T}^{*})^{1/2}}{3hE}\phi_{B}^{3/2}\right]$$

(7)

where J is current density, q is electron charge,  $q\phi_B$  is barrier height, h is Planck's constant and E is electric field across dielectric.

# 2.1.3 Direct Tunneling

Direct tunneling is another tunneling mechanism which electron penetrates through rectangular area of potential barrier directly. It happens when dielectric width is extremely narrow (<3.5nm for  $SiO_2$  dielectric) [52]. Figure 2.4 is a schematic of direct tunneling.

Figure 2.5 Schematic of direct tunneling

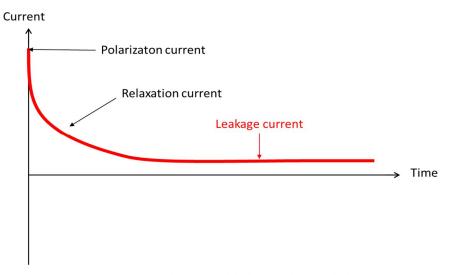

## 2.1.4 Charging Behavior of Dielectric

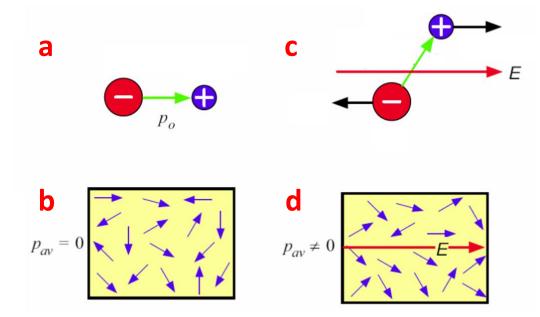

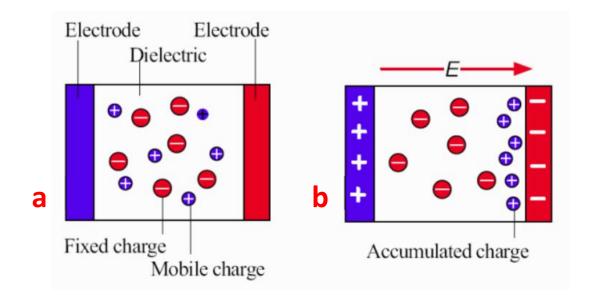

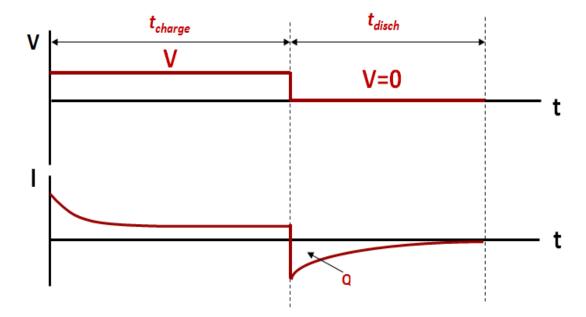

Leakage current is the current that flows through dielectric when an external electric field is applied to the dielectric. The process of applying an electric field to dielectric is called dielectric charging process. Figure 2.6 is a schematic of typical charging behavior of dielectric. As shown in the figure, charging behavior of dielectric can be divided into three regions. Initially current is high, then it will gradually decrease over time and eventually become stable at certain level. When electric field is first applied to dielectric, polarization current will arise. Polarization current is generated by dipole movement, namely electronic, ionic and orientational polarization, due to external electric field. However, once dipole is fully aligned by electric field, polarization current will disappear. Therefore, this type of current is undetectable by regular instrument as dipole align time is <10<sup>-6</sup> S. Second region of charging behavior is where relaxation current is dominant. This type of current is created by the movement of mobile charge inside dielectric. When an electric field is applied, mobile ion with positive charge will migrate to the cathode side of dielectric and mobile ions drift to certain position, they will reach equilibrium state and migration stops. The last region of dielectric charging is mainly leakage current. At this stage, all dipoles and ions are in equilibrium state and do not contribute to current flowing through dielectric. Based on applied temperature, electric field and dielectric properties, one or multiple conduction mechanisms may be contributing to leakage current simultaneously.

Figure 2.6 Schematic of dielectric charging behavior

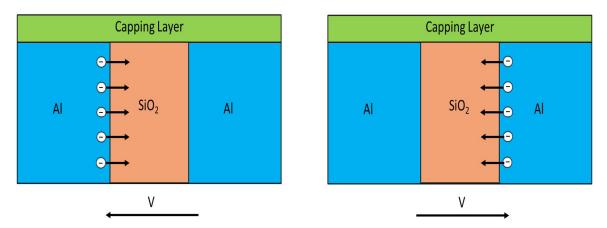

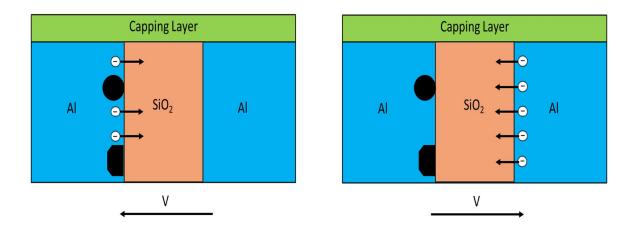

2.1.5 Principle of Polarity Dependence Measurement Technique

Key idea of this measurement technique is to measure the difference in leakage current under different bias. Leakage current can be calculated from equation

$$I = A * J(E)$$

(8)

Where A is electron injection area from electrode and J(E) is current density created by electric field. For samples with same fabrication process, conduction mechanism is expected to be the same as metal and dielectric properties are identical. Therefore, J(E) is expected to be similar for samples with same fabrication process. On the other hand, electron injection area may be different for samples with same fabrication process due to defects existing in metal lines. In ideal scenario where interconnect structure is defect free, under same electric field intensity, leakage current from both bias directions is expected to be identical in terms of quantity (Figure 2.7). This is because in defect free interconnect, electron injection area from both electrodes are identical.

Figure 2.7 Schematic of leakage current in idea condition

However, if one of the electrodes has defects such as voids, injection path will be blocked and therefore electron injection area from both electrodes will be different, which will result in different amount of leakage current based on bias direction (Figure 2.8). Based on the mechanism, electrode which contains defects is expected to have smaller amount of leakage current.

Figure 2.8 Schematic of leakage current when one electrode contains defects

Polarity difference is then calculated by equation

Polarity difference =

$$[(|I_{negative}| / |I_{positive}|) - 1] * 100$$

(9)

Where I<sub>negative</sub> is leakage current under negative bias and I<sub>positive</sub> is leakage current under positive bias. Compare to sample with no defect (ideal scenario polarity difference should be 0%), sample with defects at electrodes will have higher polarity difference. Polarity difference can show not only difference in defect amount, but also defect distribution. Samples with more defect concentrated at one electrode is going to have a higher polarity difference compare to sample with defect evenly distributed at two electrodes.

## 2.1.6 Aging Treatment

Aging treatment (also known as heat treatment) are known to create stress induced voids inside AI metal lines due to CTE mismatch between AI and surrounding SiO<sub>2</sub>. As sample went through aging treatment, it is expected to develop defects in metal lines over time. Therefore, sample's polarity difference is expected to increase with aging time. By comparing result from as-received samples and aging samples, a better understanding of the mechanism can be achieved.

# 2.2 Samples and Measurement System

2.2.1 Test Samples

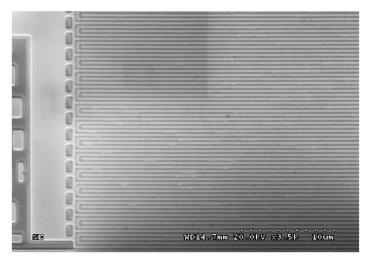

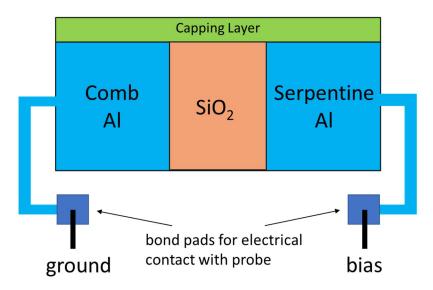

Wafers provided by Texas Instruments were used in the research. Samples taken from wafers contain  $AI/SiO_2$  interconnects (dielectric width = 0.21um, metal line thickness = 0.19um) which were patterned in a specific way known as comb-serpentine pattern (Figure 2.9).

Figure 2.9 Top-down view of test pattern with capping layer removed

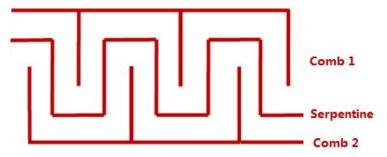

Comb and serpentine Al lines are isolated by SiO<sub>2</sub> dielectrics. In Figure 2.10, comb 1 and comb 2 are electrically connected. Therefore, a simplified metal-insulator-metal (MIM) structure as Figure 2.11, which both metal lines can be considered as electrodes, can be used for all the discussion in later paragraph. When a positive electric bias is applied to serpentine electrode and comb electrode is shorted to ground, an electric field with direction from serpentine electrode to comb electrode is formed.

Figure 2.10 Schematic of top-down view comb-serpentine structure

| Capping Layer |                  |                    |

|---------------|------------------|--------------------|

| Comb side Al  | SiO <sub>2</sub> | Serpentine side Al |

Figure 2.11 Schematic of cross section view MIM structure

# 2.2.2 Measurement System

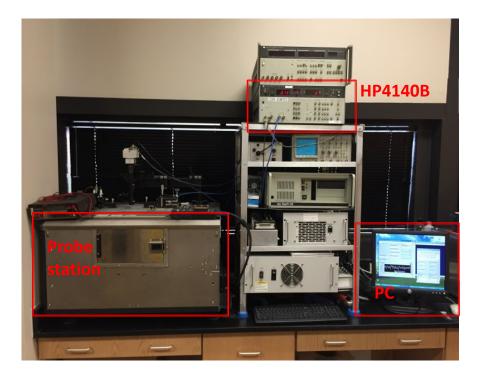

Figure 2.12 is the data acquisition system which contains a HP 4140B PA meter/DC source, probe station and a PC with LABVIEW DAQ system. HP 4140B unit generates DC voltage from -100 to 100V and collect leakage current from DUT (device under test) with

picoampere (10<sup>-15</sup>A) resolution. Probe station is where DUTs are tested during measurement.

Figure 2.12 Measurement system

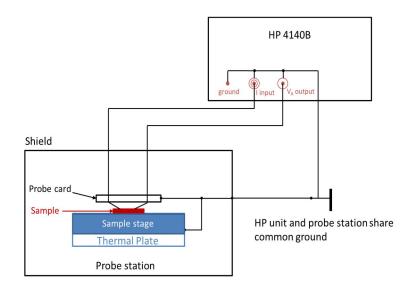

Figure 2.13 shows a schematic of electric connection between probe station and HP 4140B unit. Probe station is made of aluminum which acts as a shield blocking electrical noise from environment. Thermo plate below sample stage can heat up to 250°C. LABVIEW DAQ software is used to translate analog data output from HP4140B unit to digital data which is readable by PC. Besides electrical measurement system, there are some conventional instruments used in the research due to the need to confirm the result obtained from electrical measurement, such as high temperature oven, focus ion beam and SEM.

Figure 2.13 Schematic of electric connection between probe station and HP 4140B unit

#### 2.3 Test Strategy

#### 2.3.1 Sample Selection

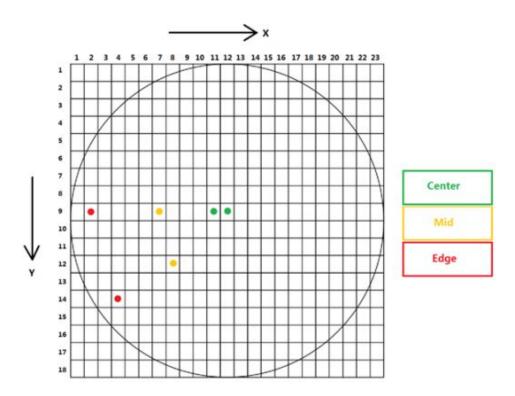

Purpose of this research is to determine if proposed electrical measurement technique can detect defect in metal lines at metal/dielectric interface. Therefore, is it important to test both samples with defect and samples without defect to compare to results. When a whole wafer is considered, usually dies from edge position of the wafers has worse properties compare to center dies [63,64]. By comparing dies from different locations, leakage current difference may be observed. Figure 2.14 is a schematic of sample selection based on wafer location. Coordinate of the samples taken from wafer is marked as (x,y). For example, center samples in Figure 2.14 is marked as (11,9) and

(12,9). For this research, several different wafers were chosen. Therefore, it is important to select samples from same coordinate to give a meaningful comparison.

Figure 2.14 Schematic of sample selection based on die location

# 2.3.2 Test Procedure

As mentioned in previous paragraph, test structure contains comb metal line (comb Al electrode), serpentine metal line (serpentine Al electrode) and dielectric. During measurement, serpentine electrode is always connected to electrical bias source while comb electrode is connected to ground (Figure 2.15). In future discussion, positive bias refers to applying a positive voltage to serpentine electrode and the direction of electric field/current flow is from serpentine electrode to comb electrode (electrons are flowing in opposite direction). Negative bias refers to applying a negative voltage to serpentine electrode and the direction of electric field/current flow is from comb electrode to serpentine electrode.

Figure 2.15 Schematic of electrical connection between sample and probe

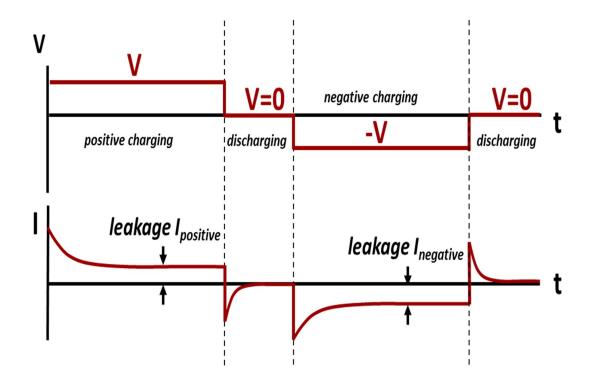

A typical polarity dependence measurement contains four phases: positive charging, discharging, negative charging and then another discharging. Figure 2.16 is a schematic of the procedure. During positive charging phase, a positive bias is applied to sample for certain amount of time and current data is collected simultaneously. Once current stops to decay and remains at a stable level, that current level is considered as the level of leakage current. During discharging phase, bias is removed and both electrodes are connected to ground. Dielectric is then discharged and returned to equilibrium state. During negative charging phase, a negative bias is applied to sample and leakage current data is collected. After that, sample went through another discharging phase.

After samples go through polarity dependence measurement at as-received condition, they are sent into oven for aging treatment to create stress induced voiding. Temperature of the oven is set to 185°C and aging time is 100 hours. After 100 hours samples are taken out and cooled to room temperature. Another polarity dependence measurement will then be conducted on the samples. Repeat this process for several times and collect leakage current data and polarity difference data.

In this research, 2 wafers are selected (wafer P02 and P25). On each wafer 3 locations are picked (center, mid and edge). At center location 4 samples are tested, at mid and edge locations 8 samples are tested. A total of 8 center samples, 16 mid samples and 16 edge samples are tested in the research. Applied voltage is +/- 100V, charging time is 10 minutes, discharging time is 3 minutes and test temperature is 50°C

Figure 2.16 Schematic of polarity dependence measurement procedure

#### 2.4 Result and Discussion

#### 2.4.1 Leakage Current Seen in Research

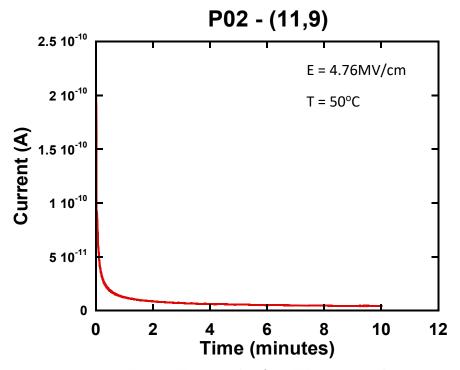

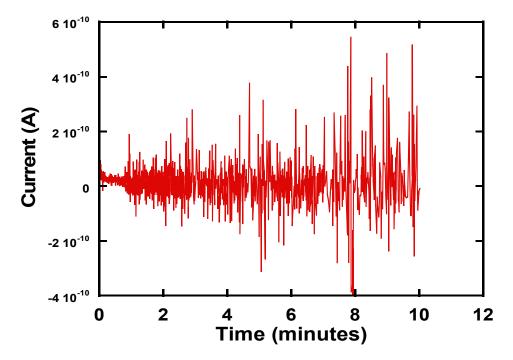

Under applied electric field, leakage current data from dielectric is collected. Figure 2.17 is a current versus charging data collected from one of the samples from wafer P02. Current decays over time rapidly in the first 10 seconds. During this period, relaxation current created by movement of mobile ions is the dominant current seen in measurement. Initially current level is high because all mobile ions are drifting inside dielectric under electric field, ions with positive charges are drifting towards negative electrode while ions with negative charges are drifting towards positive electrode. But once mobile ions start to reach side wall of dielectric, movement of ions will be reduced and relaxation current starts to decay.

Figure 2.17 Current data from P02 center sample

From 10 seconds to 6 minutes, current seen in the measurement is a mixture of relaxation current and leakage current. Relaxation part of the current is the reason why current is still decaying at a relatively slow speed. After 6 minutes, most of the relaxation current are fully decayed and current seen in the measurement is mostly contributed by leakage current. Therefore, average current collected when charging time reaches 10 minutes is considered as leakage current of the sample in this research.

# 2.4.2 Conduction Mechanism Confirmation

As mentioned in previous paragraph, there are several conduction mechanisms that might contribute to leakage current. Therefore, it is important to identify which mechanism is the main contributor to leakage current difference seen in the samples.

Since samples are from wafers with identical fabrication process, dielectric properties of samples should be identical. This means bulk limited conduction mechanisms have same contribution to all samples. On the other hand, electrode limited conduction mechanisms are affected by metal/dielectric interface properties. Defects existing in metal lines near metal/dielectric interface is going to impact interface properties. Therefore, electrode limited conduction mechanisms are more likely to contribute to the polarity difference seen in samples.

Typical electrode limited conduction mechanisms include: Schottky emission, F-N tunneling and direct tunneling. Direct tunneling is not likely to contribute to leakage current in this case because it only occurs when thickness of SiO<sub>2</sub> dielectric is narrower than 3.5nm [52] while samples measurement in this research has a dielectric thickness of

38

210 nm. Schottky emission is affected by temperature and applied electric field. It is commonly seen in dielectric with higher operating temperature (>300K) [52, 65]. F-N tunneling is affected by electric field but not temperature, and thus more commonly seen in dielectric under high electric field and low temperature [52, 66].

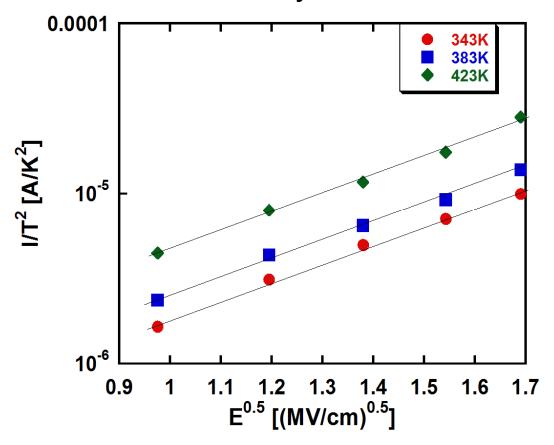

To identify which mechanism is the main contributor to current difference seen in polarity dependence measurement, a simple curve fit measurement can be done. According to Chiu *et al.* [65, 66], when main contributor of leakage current is Schottky emission, ln ( $I/T^2$ ) should have a linear relationship with  $E^{1/2}$ . When main contributor of leakage current is F-N tunneling, ln ( $I/E^2$ ) should have a linear relationship with 1/E.

**Schottky Curve Fit**

Figure 2.18 Schottky emission curve fit

Figure 2.18 and 2.19 are curve fit for Schottky emission and F-N tunneling, respectively. Y axis of both curve fits are logarithmic scale of ten. Curve fit of Schottky emission does show a linear relationship between  $I/T^2$  and  $E^{1/2}$  under log scale. F-N curve fit, on the other hand, does not show a liner relationship between  $I/E^2$  and 1/E under log scale. Curve fit of F-N tunneling appears to have two different components, first components is from 0.2 to 0.35 \* 1/E where  $I/E^2$  decreases with 1/E and second component is between 0.35 to 0.7 \* 1/E where  $I/E^2$  increases linearly with 1/E. Curve fit result indicates that main contributing conduction mechanism of leakage current seen in the measurement is Schottky emission.

**F-N Curve Fit**

Figure 2.19 F-N tunneling curve fit

This result is as expected. According to Chiu *et al.* [52], contribution to leakage current from F-N tunneling mechanism will only be significant when potential barrier thickness is smaller than 10 nm. Since dielectric width of sample is 210 nm, to reduce the thickness of triangular area of potential barrier to 10nm will require an extremely high electric field (>10 MV/cm). It is likely that dielectric breakdown will occur before F-N tunneling starts to have a significant effect on leakage current.

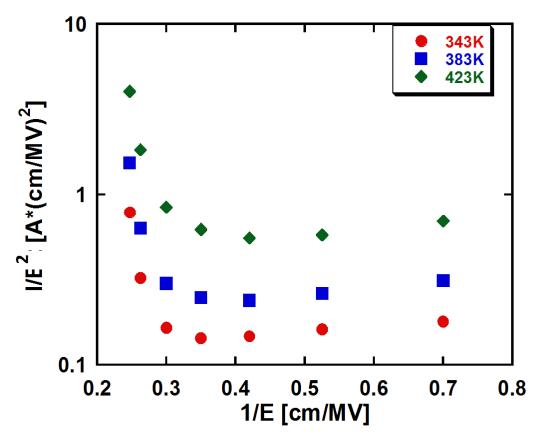

2.4.3 Average Leakage Current of As-received Samples

Average leakage current is

Average leakage current =

$$(|I_{negative}| + |I_{positive}|) / 2$$

(10)

where Inegative is leakage current under negative bias and Ipositive is leakage current under positive bias. When sample contains a huge number of defects at metal electrodes, it is expected to show lower average leakage current compare to sample contains no defect. This is due to electron injection area difference mentioned in previous paragraph. When sample contains no defect, electron injection area from both metal electrodes is identical and leakage current level is high. But when a huge number of defects exist at metal electrodes, electron injection area is greatly reduced, and thus current reduced. Therefore, average leakage current can serve as an indicator of interconnect properties. However, leakage current is not only affected by interface injection area, other factors such as dielectric properties and interface roughness will have impacts on current as well, and thus average leakage current is only sensitive to huge number of defects. When for average leakage current to show huge difference, hence average leakage current level is expected to be similar for samples from different location at as-received condition.

Figure 2.20 Average leakage current versus sample location

Figure 2.20 is average leakage current data collected from as-received samples. Each data point in center location represents the average of 4 samples and each data point in mid and edge location represents the average of 8 samples. Average leakage current data from different location does not show a huge difference, which indicates this measurement may not be sensitive enough to defects in metal lines.

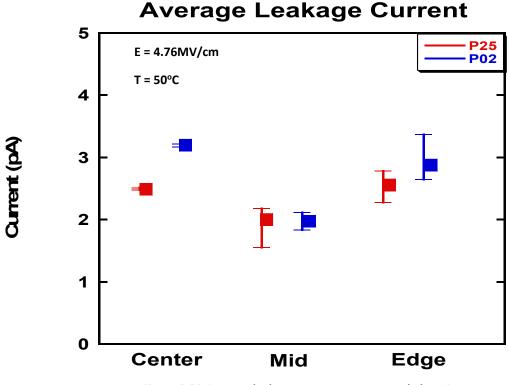

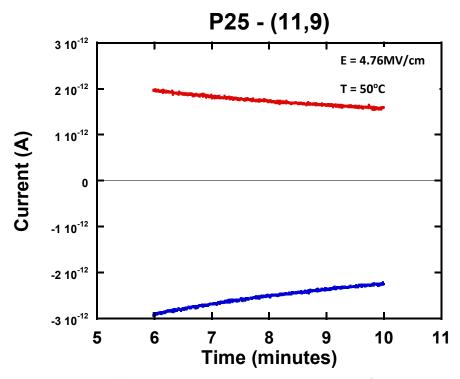

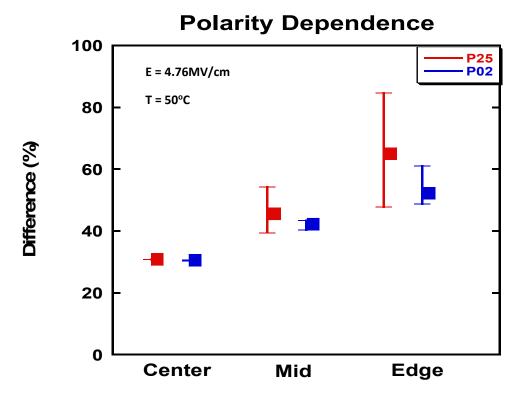

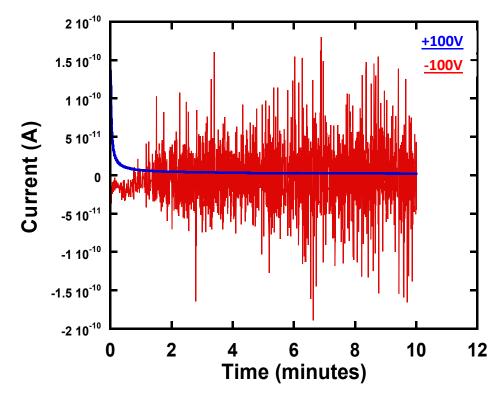

# 2.4.4 Polarity Difference of As-received Samples

Polarity difference is the difference between leakage current under positive bias and negative bias. Unlike average leakage current measurement which is only sensitive to huge number of defects in metal electrodes, polarity dependence measurement is designed to detect tiny amounts of defect. Difference between average leakage current measurement and polarity dependence measurement is that previous measurement provides a parameter (average leakage current) that is affected by lots of factors while later measurement provides a self-reference parameter (polarity difference) which is only sensitive to defect distribution at metal electrodes. Therefore, polarity dependence measurement is expected to capture difference in defect distribution even when number of defects is small.

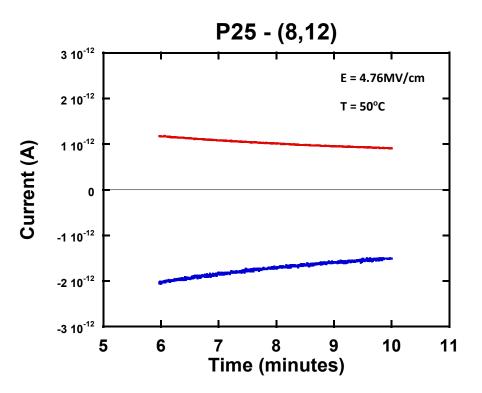

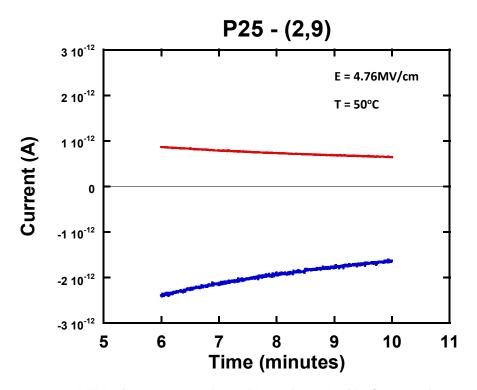

Figure 2.21, 2.22 and 2.23 are example leakage current data collected from asreceived samples taken from center, mid and edge location, respectively. In figures, only 6~10 minutes data are shown as it is where leakage current is dominant.

Figure 2.21 Leakage current under positive and negative bias from a center sample

Figure 2.22 Leakage current under positive and negative bias from a mid sample

Figure 2.23 Leakage current under positive and negative bias from an edge sample