# ACTIVE FLYBACK BASED BATTERY MANAGEMENT SYSTEM WITH PROPORTIONAL BALANCING FOR USE IN AN ELECTRIC RACE CAR

by

# MATTHEW MARTIN

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

THE UNIVERSITY OF TEXAS AT ARLINGTON  ${\rm August~2016}$

Copyright © by MATTHEW MARTIN 2016 All Rights Reserved

| To all of my friends and family that supported me throughout my scholastic career, |

|------------------------------------------------------------------------------------|

| including my father Doug, my mother Betty, Kyrsten, Isaac, David, and Donald.      |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

# ACKNOWLEDGEMENTS

First off, I would like to thank my supervising professor Dr. David Wetz for his support in this endeavor and dedication to me as a graduate student. None of this would have been possible if it were not for his dedication to making sure I had all of the proper tools, parts, software, and most importantly time to keep the project moving forward.

I would also like to extend a special thanks to several of my lab mates who, at some point or another, dedicated some time to helping me work through a problem or decide on a direction. Isaac Cohen, Donald Dodson, Chris Williams, and Clint Gnegy-Davidson, thank you all for the help and support! I literally could not have done it without you guys.

I would also like to thank Dr. Bob Woods and the entire Formula SAE racing team here at The University of Texas at Arlington for motivating me to become a better engineer and for being an inspiration and an outlet that breeds creativity.

Lastly I would like to thank my family for sticking by my decisions and supporting me to the very end. I could not have made it to where I'm at if it were not for my father Doug, my mother Betty, and Kyrsten. Thank you guys!

July 29th, 2016

# ABSTRACT

## MATTHEW MARTIN, M.S.

The University of Texas at Arlington, 2016

Supervising Professor: David A. Wetz

Battery management systems are responsible for many tasks, most important of which is maintaining balance amongst the cells in a series string to prevent excess aging and unsafe operating conditions |1||2|. In lithium-ion battery packs, traditionally, and almost exclusively in the world at large today, balancing is achieved by switching a resistor in parallel with high cells to bleed energy out of them and dissipate it as heat. This tactic is not only 100 percent inefficient, but it is slow due to power dissipation restrictions typically thermally imposed within a system, and it is only effective at preventing over-voltage conditions. This thesis serves to outline the design, simulation, and implementation of an active battery management system for deployment in an electric race car, such as to minimize battery requirements (and therefore weight), optimize aging, and maximize the usable capacity of a given battery pack. High level simulations were performed from a pure energy transfer perspective to assess the potential of such a system, showing a strong inclination towards the potential effectiveness of the system. Given the unique constraints imposed on the isolated DC/DC converters used to transfer energy within the battery string, low level simulations were performed to validate the feasibility from a hardware perspective. Hardware that supports up to 2.5A balance currents was designed, constructed,

$\mathbf{v}$

and objectively validated against the simulations. An embedded operating system was developed, with a modular hardware abstraction layer, a flexible scheduler, and many support functions, on which an active battery management state machine was built. Lastly, tests were performed in order to compare real world results to high and low level simulation results. Findings have shown that active balancing is not only more effective at bleeding off high cells during recharge imbalance, but balancing can be performed throughout the entire cycle to supplement weak cells in order to extend the capacity of the battery as well as to offset the aging rate towards the stronger cells.

# TABLE OF CONTENTS

| A( | CKNO | OWLEDGEMENTS                                            | iv   |

|----|------|---------------------------------------------------------|------|

| ΑI | BSTR | ACT                                                     | V    |

| LI | ST O | F ILLUSTRATIONS                                         | ix   |

| LI | ST O | F TABLES                                                | xi   |

| Ch | apte | r F                                                     | Page |

| 1. | INT  | RODUCTION                                               | 1    |

|    | 1.1  | Lithium Ion Battery Parameters and Behavior             | 1    |

|    | 1.2  | Electric Racecar Battery Requirements                   | 6    |

|    | 1.3  | Existing Systems and Topologies and their Short Comings | 12   |

|    | 1.4  | FlyBMS Overview                                         | 15   |

| 2. | MO   | DELING AND SIMULATION                                   | 17   |

|    | 2.1  | SOC Based Active Balancing MATLAB Simulation            | 17   |

|    | 2.2  | Simple mathematical model of a flyback converter        | 26   |

|    | 2.3  | Component level Spice simulation of flyback stage       | 36   |

| 3. | HAI  | RDWARE DESIGN                                           | 44   |

|    | 3.1  | Component Selection                                     | 44   |

|    | 3.2  | Printed Circuit Board Design                            | 50   |

| 4. | FIR  | MWARE DESIGN                                            | 60   |

|    | 4.1  | SimSTOS - Simple Soft Time Operating System             | 60   |

|    | 4.2  | Battery Management State Machine                        | 67   |

| 5. | DES  | SIGN VERIFICATION                                       | 70   |

|    | 5.1  | Measurement Noise                                       | 70   |

| 5.2     | Final Results                | 72 |

|---------|------------------------------|----|

| 5.3     | Future advancements          | 76 |

| Append  | dix                          |    |

| A. Firm | nware: Balance State Machine | 81 |

| REFEI   | RENCES                       | 91 |

| BIOGF   | RAPHICAL STATEMENT           | 93 |

# LIST OF ILLUSTRATIONS

| Figure |                                                                       | Page  |

|--------|-----------------------------------------------------------------------|-------|

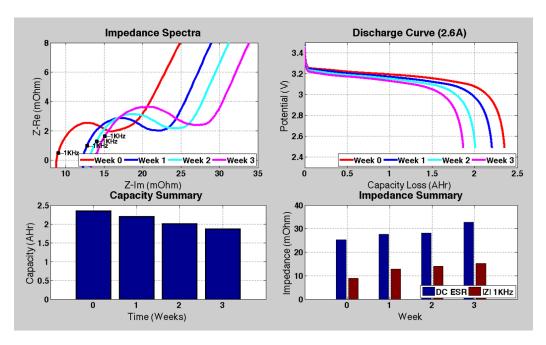

| 1.1    | Example of the effects of storage temperature on capacity, ESR, and   |       |

|        | frequency response of lithium-ion cells stored at 70°C                | 6     |

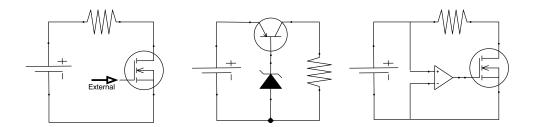

| 1.2    | Example of passive balancing topologies. (Left) Bleed resistor with   |       |

|        | externally driven MOSFET. (Middle) Pass transistor biased with zener  |       |

|        | diode. (Right) Bleed resistor with locally driven MOSFET using com-   |       |

|        | parator                                                               | 13    |

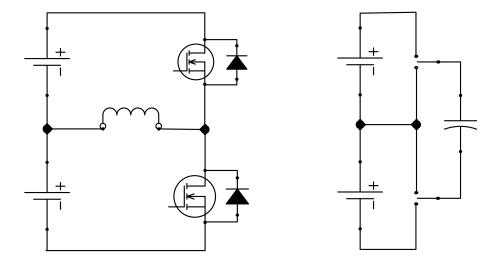

| 1.3    | Example of active balancing topologies. (Left) Inductor based boost   |       |

|        | mode active balancing. (Right) Capacitor based charge shuttle active  |       |

|        | balancing                                                             | 14    |

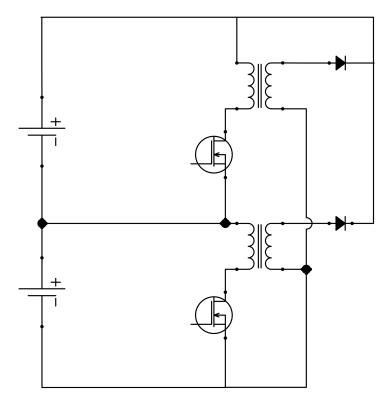

| 1.4    | Example of an active flyback based balancing topology                 | 16    |

| 2.1    | MATLAB simulation result that validates the active flyback BMS system | n. 23 |

| 2.2    | Mapping of voltage imbalance to applied duty cycle for each cell      | 24    |

| 2.3    | MATLAB simulation result showing oscillations with original loop tim- |       |

|        | ing and duty cycle mapping                                            | 25    |

| 2.4    | MATLAB simulation result showing BMS operation across a sweep of      |       |

|        | various cell parameters                                               | 39    |

| 2.5    | Basic flyback converter topology applied in the FlyBMS                | 40    |

| 2.6    | Modified flyback converter topology applied in the FlyBMS, with added |       |

|        | output dissipation resistor                                           | 40    |

| 2.7    | LTSpice simulation of proposed flyback balance circuit                | 41    |

| 2.8    | LTSpice single cell simulation results with output resistor           | 41    |

| 2.9  | LTSpice single cell simulation results without output resistor              | 42 |

|------|-----------------------------------------------------------------------------|----|

| 2.10 | LTSpice simulation of full 10 cell balance system                           | 43 |

| 3.1  | Isolated MOSFET driver topology applied in the FlyBMS                       | 47 |

| 3.2  | FlyBMS embedded system power supply topology                                | 51 |

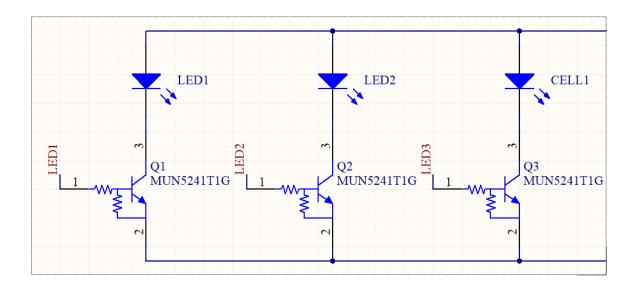

| 3.3  | FlyBMS embedded system LED driver topology                                  | 52 |

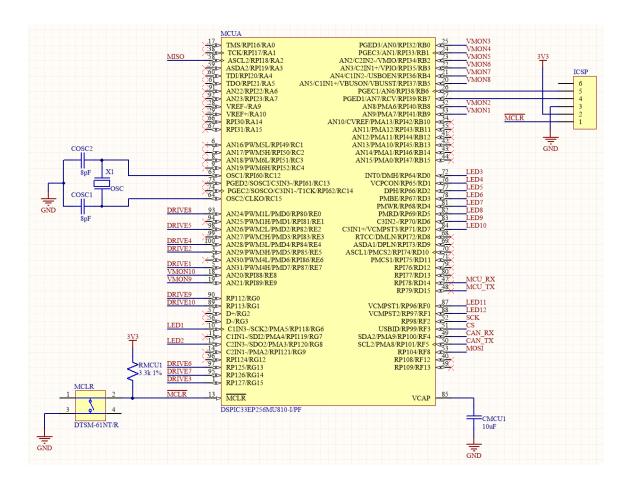

| 3.4  | FlyBMS embedded system microcontroller topology                             | 53 |

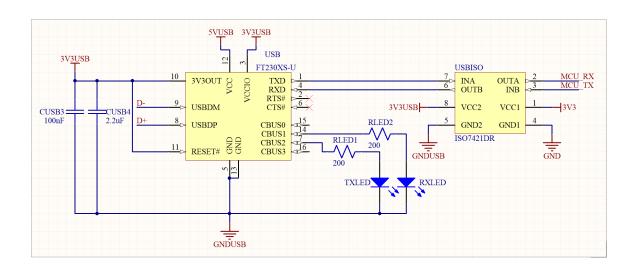

| 3.5  | FlyBMS embedded system isolated USB host interface topology $$              | 54 |

| 3.6  | FlyBMS embedded system cell interface topology                              | 55 |

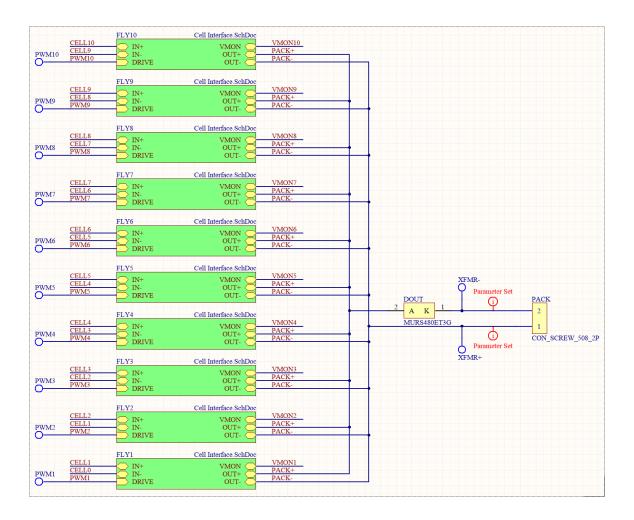

| 3.7  | FlyBMS embedded system cell interface multi-channel implementation          | 56 |

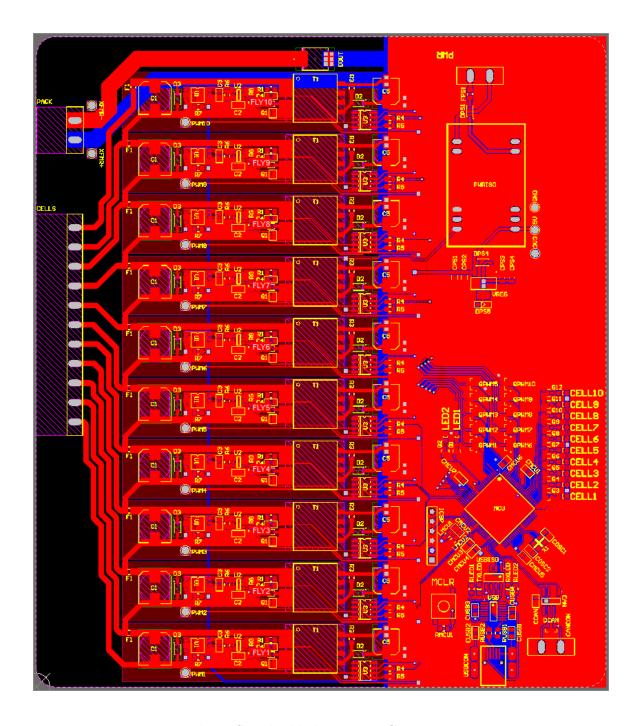

| 3.8  | FlyBMS embedded system PCB 2D representation                                | 58 |

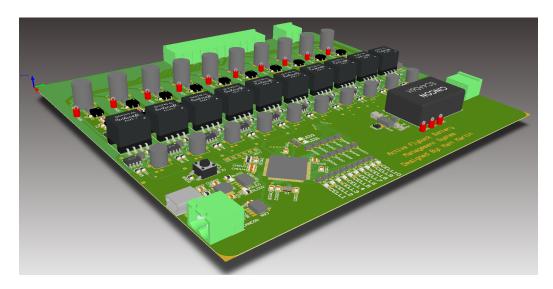

| 3.9  | FlyBMS embedded system PCB 3D representation                                | 59 |

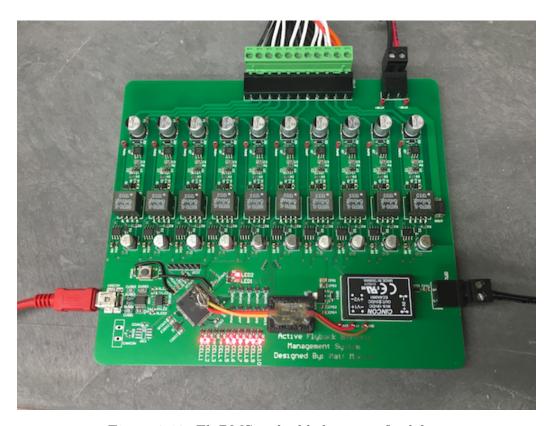

| 3.10 | FlyBMS embedded system final form                                           | 59 |

| 4.1  | SimSTOS architecture layout                                                 | 62 |

| 4.2  | SimSTOS display driver example usage                                        | 63 |

| 4.3  | SimSTOS serial interface driver example usage                               | 64 |

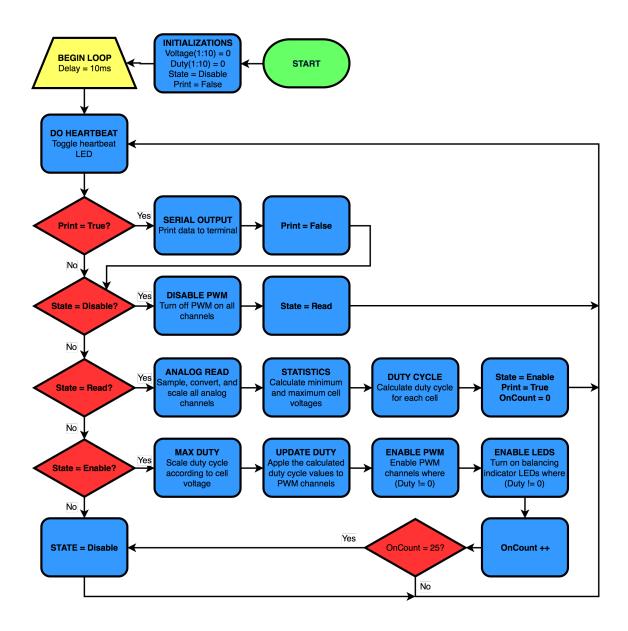

| 4.4  | Balancing state machine flowchart                                           | 69 |

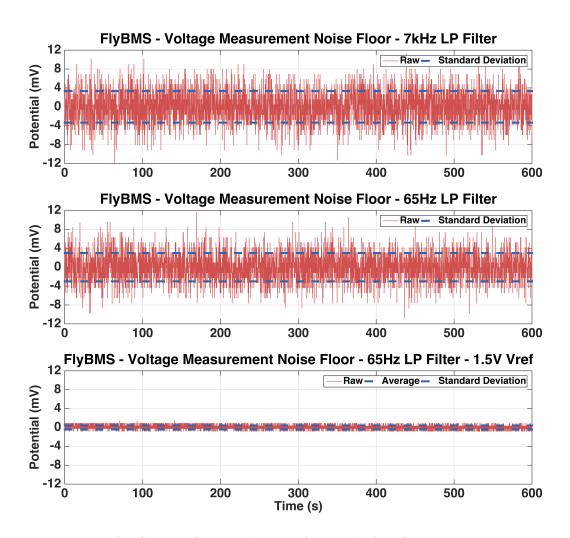

| 5.1  | ADC noise floor analysis before and after filtering and external references | 73 |

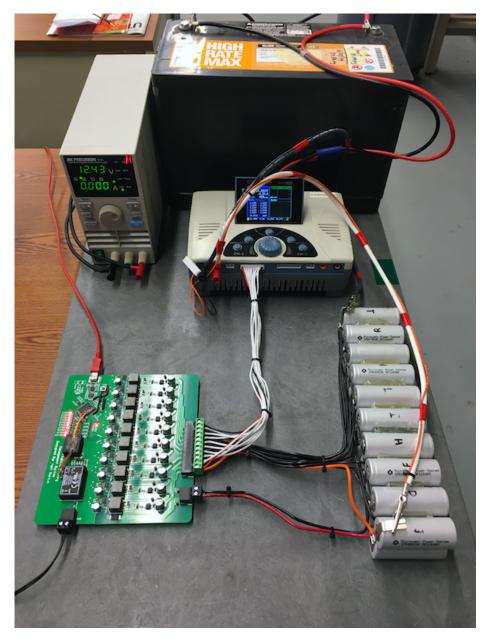

| 5.2  | Battery module constructed for testing                                      | 74 |

| 5.3  | Test setup showing FlyBMS, battery module, and iCharger                     | 79 |

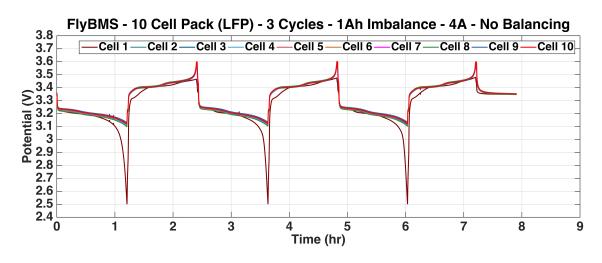

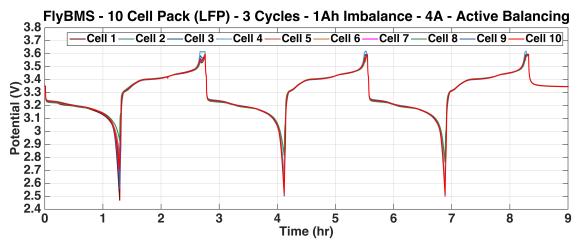

| 5.4  | FlyBMS initial balance comparison results                                   | 80 |

# LIST OF TABLES

| Table |                                                                      | Page |

|-------|----------------------------------------------------------------------|------|

| 2.1   | Mapping of voltage discrepancy ranges to applied duty cycle for each |      |

|       | channel's flyback converter                                          | 20   |

| 5.1   | Measured cell parameters for battery pack used in testing            | 75   |

# CHAPTER 1

#### INTRODUCTION

# 1.1 Lithium Ion Battery Parameters and Behavior

Before diving in to the whys and hows of active battery management, it is necessary to cover some of the basics of lithium-ion batteries and their relevant terminology. Below is a list of some of the most relevant terms and their functional description as it pertains to high level system design, as well as few key points regarding degradation in lithium-ion cells.

Capacity: Capacity is nothing more than a metric used to communicate how much energy is stored within the cell. Capacity is represented using the units of 'Ah', representing the current-time capabilities of the battery. A 1Ah battery will last approximately 1 hour with a 1A continuous discharge rate. The same cell would only last one tenth of an hour at a 10A discharge rate. Obviously then, higher capacity cells have more energy stored, but it is very important to understand that higher energy stored does not directly equate to the cell being capable of supplying the energy faster.

State of Charge: Most often abbreviated to SOC, state of charge is used to represent the percent of energy remaining in a given battery. Numerically, it is a normalized representation of the capacity remaining divided by the total full charge capacity. It provides a convenient means of describing a battery's capacity independent of the actual capacity of the battery in question. For example, a battery with a full charge capacity of 6Ah that has had 3Ah removed would be at 50 percent SOC.

Similarly, a 10Ah battery with 8Ah removed would be at 20 percent SOC.

$$SOC = \frac{Ah_{Remaining}}{Ah_{Total}} \tag{1.1}$$

Power Density: Sometimes known as specific power when calculated with mass, power density is an absolute metric that is used to show how much relative power a specific cell can provide as a function of it's volume. This is a key metric of study when sourcing batteries for a high pulsed power applications, such as an electric race car. Typically speaking, batteries are not as power dense as some other storage elements, such as super-capacitors or ultra-capacitors, but recent developments in high power capable lithium-ion chemistries have began closing this gap. The equation for power density is shown in 1.2

$$P_{Density} = \frac{A_{Max} * V_{Nominal}}{Volume} \tag{1.2}$$

Energy Density: Sometimes known as specific energy when calculated with mass, the energy density of a battery is a numerical representation of the amount of energy stored in relation to it's volume. Energy density is another specially useful metric for comparison in a sizing study of an electric race car battery. Maximizing energy density means you are maximizing the amount of energy stored on the vehicle while keeping weight to a minimum. The typical order of operation for a sizing

study is to narrow down your choices based on power requirements, and them finalize based on energy density, though other things such as cell geometry and cooling considerations should also take a role. The equation for energy density is shown in 1.3.

$$E_{Density} = \frac{Ah_{Nominal} * V_{Nominal}}{Volume} \tag{1.3}$$

Equivalent Series Resistance: Commonly referred to as 'ESR', it is a single lumped parameter used to simply describe the electrical and thermal behavior of the battery. It is the effective operational resistance of the battery, responsible for the voltage rise and drop under load as well as the joule heating of the cell as a function of current. Typically, ESR is measured and specified by manufacturers by superimposing a small (5mV-20mV) 1kHz sinusoidal voltage on the open circuit (at rest) potential of the battery and measuring the subsequent current, and then using the applied voltage and current waveforms to calculate an average resistance. This is referred to as the 1kHz ESR. A more practical value for the ESR however is the DC ESR, which is also sometimes included in data sheets, and depicts the actual resistance of the cell in DC operational conditions. For example, if a designer knows they are going to be discharging the cell at approximately 1A constant current, and the cell has an internal DC ESR of 100m, the power dissipated in the cell would be 100mW. They also know that the voltage drop within the cell would be 100mV. DC ESR is typically characterized by performing two full discharges of the cell, one at a rate low enough to cause practically no joule heating, and one at a nominal rate from the data sheet, and dividing the average voltage difference by the average current difference, as can be seen in Equation 1.4.

$$ESR_{DC} = \frac{\overline{V_{diff}}}{\overline{I_{diff}}} \tag{1.4}$$

C Rate: C rate is a unitless parameter used to communicate a current as a function of a particular cell's capacity (Equation 1.5. For example, if someone told you to discharge a 1Ah cell at 1C, you would discharge it at 1A, and the discharge would be complete in approximately 1 hour. If they said to discharge the same cell at 60C, you would discharge it at 60A, and the discharge would complete in approximately 1 minute. This allows manufacturers to easily specify maximum and minimum parameters of their cells in terms that scale with the pack size, and allows designers to immediately gauge stress levels placed on a cell without having to look up the exact particulars of that cell. For example, an engineer should immediately know that a 1C discharge for a lithium-ion cell is relatively relaxed, while a 10C discharge is a stressful operating scenario.

$$CRate = \frac{A_{Applied}}{Capacity} \tag{1.5}$$

Capacity Fade: Commonly referred to as 'aging' in lithium-ion cells, capacity fade is the main method of degradation in lithium-ion cells. For lithium-ion cells, "end of life" (EOL) is usually classified at a 20 percent reduction in capacity. Capacity of

any given cell is reduced over time due to many different mechanisms: age, operating rate, and operating temperature. Age alone is the most negligible capacity degradation factor in a lithium-ion cell, typically on the order of fractions of a percent of the cell's capacity per year. This mechanism is typically ignored. Operational rate, however, can be a very large part of the degradation of a cell as time progresses. Higher operational C-rates will degrade cells much faster than lower C-rates, and degradation rate typically increases exponentially with operational C-rate. For example, a cell rated for 10,000 cycles per the manufacturer could be expected to operate to the full 10,000 cycles if operated at 1C or less, but if operated at 10C, it would be unreasonable to expect it to operate much past 100 cycles, unless the chemistry is specifically engineered for operating at very high operational rates. Temperature is also a very prominent degradation mechanism that designers should consider, though it is a bit of a 'dark art' to predict the behavior at a given temperature. As a rule of thumb, operating a cell in ambient conditions at or below half of the manufacturers recommended maximum operating temperature will yield negligible temperature dependent aging over the life of the cell. However, even just storing a lithium-ion cell at ambient temperatures at or near the cell's recommended maximum operating temperature will severely impact the capacity of the cell. In fact, tests have been performed at UTA that show that just four weeks of storage at 70°C for a commercial off-the-shelf (COTS) Lithium-Iron Phosphate cell rated for a maximum operating temperature of 70°C will bring the cell to EOL, as shown in Figure 1.1. This will vary from cell to cell, but the overall effect is still largely dominant.

ESR Growth: ESR growth is another aging mechanism that changes battery behavior as a function of the same influential parameters as capacity fade. The main difference is that capacity fade in and of itself majorly impacts the functionality of the

Figure 1.1: Example of the effects of storage temperature on capacity, ESR, and frequency response of lithium-ion cells stored at  $70^{\circ}$ C

cell within the target system, whereas growth of the ESR typically does not directly influence the operation of the system. The main detriment to growth of the cell's ESR is an increase in joule heating, which in turn further increases the capacity fade due to ever increasing operating temperatures. Generally, a system designer does not need to consider growth of the ESR as a function of time, unless the system is operated at extremely high rates, such that the voltage drop across the ESR is significant enough to further reduce the effective capacity due to premature voltage cutoff.

# 1.2 Electric Racecar Battery Requirements

For the purpose of this thesis, a battery management system specific to an electric race car, which will compete in the 2017 Formula SAE electric car competition, will be designed. This is an important consideration, because one of the main sources

of constraints for such a car is the current year rules, and these rules change frequently. In the 2016 rules, the sections relevant to the design of the battery management system are: EV1.1.1, EV1.1.2, EV1.2.7, EV1.2.8, EV3.6.2, EV3.6.3, EV3.6.4, EV3.6.5, and EV3.6.6 [3].

EV1.1.1 and EV1.1.2: These rules imply two things, namely that when the high voltage system (tractive system) is deactivated, the maximum voltage permitted anywhere on the vehicle is 60V DC, and that when high voltage is active, the maximum voltage permitted anywhere on the vehicle is 300V DC. In other words, the maximum battery voltage for the car is 300V DC, and it must be able to be broken down into 60V segments. Assuming that the full charge cell voltage is either 3.6V or 4.2V (depending on the exact chemistry), the segments are limited to no more than 16 or 14 cells in series respectively. In order to design a universally applicable system, it will be assumed that the maximum number of cells in a given segment will be 10, limiting segment voltage to no more than 36V or 42V respectively, both of which are well within the rules.

EV1.2.7 and EV3.6.5: These rules state that the low voltage and high voltage system must be completely galvanically isolated. In the case of the battery management system, both systems will be present on the same board, so it is imperative that the design and PCB layout account for complete galvanic isolation (with at least 3/8" gap or a rated component) between the two systems. A previous BMS design at UTA has already proven the feasibility of such a configuration, so for the purpose of this thesis, only the operational functionality will be considered. Final layout will occur in the future when the next team finalizes a battery pack design.

EV1.2.8: This rule states that regardless of their location within the high voltage system, all components in the high voltage system must be rated to the full voltage. In other words, each BMS board must be designed to operate on either the bottom (most negative) segment, or on the top (most positive segment), without failure of the galvanic isolation. It is important here to remember that, per the FSAE organization, the main intent of the rules is to portray intent. Following explicitly, this rule requires that every single component on each and every one of the BMS boards must be rated to over 200V, but that is not the intention. The rule is written as though the team will be buying some form of isolated BMS system, so it is therefore only a requirement that the BMS system as a whole be designed to operate at the full voltage of the high voltage system, and not each and every component within.

EV3.6.2, EV3.6.3 and EV3.6.6: These rules state that the battery management system (BMS) is also responsible for thermal management of the battery cells. In order to prevent an extremely dangerous event where the cells are critically over their maximum temperature rating, it is necessary to monitor the temperature of the hottest part of the cells. If an over temperature occurs, it is the responsibility of the BMS to open the main relays and isolate the battery pack from the rest of the system. Per these rules, the BMS must monitor at least 30 percent of the cells, and the measurement points must be either on the negative terminal (typically, but not exclusively, the hottest part of a given cell due to the thermal resistance resulting from the construction method of the cells) or on the negative bus bar of a given cell, within 10mm of the terminal. Per the rules then, and given the design decision to design around 10-cell segments, there needs to be no less than three temperature sensor inputs per segment in the final system. Temperature measurements are nothing more than voltage measurements of a buffered and possibly amplified/conditioned

temperature sensor, so for the purpose of this thesis, temperature measurements will be left out. It will be the responsibility of the future team that is implementing this BMS to account for the additional analog inputs, though the final firmware will have support for it.

EV3.6.4: This rule states that, for any BMS where a single board is to be measuring and managing more than 1 cell, all of the inputs from the battery segment must be protected by either a fuse or a fusible link wire. Per the rule, fusing must occur either in the conductor, wire, or PCB trace that is directly connected to the cell. In other words, if there are connectors, distribution blocks, or any other kinds of nodes between the cell connection and the BMS connection, fusing must occur before the intermediate node. For the purpose of this design, it will be assumed that, just as in the past, the BMS will directly interface with the battery bus bars via spring loaded terminals. The BMS board will mount directly to the top of the segment, and will have contacts protruding from the bottom of the board that sit on the battery bus bars directly. Fusing then will occur on the BMS board via properly rated SMD fuses. The fuses will be specified such that they open below the maximum rating of any of the traces or discrete components in the circuit.

Once the rules have been addressed, and a plan put in place for conformance, it is necessary to address the other constraints of the system's design that are imposed by specifics of operating in a race car environment. Many other factors will influence the design decisions of the BMS, such as peak balance current required to be effective at the expected operating rates, required battery capacity for a given event or series of events, and additional weight added via BMS components vs energy storage weight savings. While these may seem like very complex considerations, they are

actually relatively simple to estimate based on previously calculated data, and can only be optimized via data collection once implemented into an actual vehicle due to the nature of the calculated data. For starters, required balance current and required capacity have been previously calculated by the UTA racing team using track data from a previous year's combustion car. Their findings indicate that the average current expected from the battery packs as a whole will be approximately 81A, which during a 20 lap endurance event with 60s average lap times, corresponds to 25Ah of battery capacity required, as shown in Equation 1.6.

$$CapacityReq = I_{avg} * RunTime = 81A * \frac{20Laps * 60sec}{3600} = 25Ah$$

(1.6)

Obviously this assumes many things, first and foremost that the weight of the car as well as the car's dynamics will be close enough to the combustion car's that the throttle input will be directly relatable. However, it is expected that, due to the increased weight of the electric car, the average current will be higher than this. Lithium-ion batteries typically experience no more than a 1 percent capacity and/or ESR discrepancy for cells manufactured within the same batch, so it is reasonable to design the maximum balance current such that it can compensate for a 1 percent imbalance in capacity throughout a cycle. If we assume a worst case scenario average battery current of 100A, that would correspond to a maximum average balance current of only 1A at the 1 percent mark. Average currents much beyond 2.5A would likely require much heavier and/or robust components within the BMS, so it is desirable to minimize the target average balance current as much as possible, but the

weight/complexity cost up to the 2.5A point is relatively constant, so a maximum balance current of 2.5A was chosen. This means that, at the 1 percent discrepancy mark, the BMS could support up to a 250A system, and that at the worst case scenario average current of 100A, the BMS can account for up to a 2.5 percent discrepancy in the cells. It is important to realize that this weight/complexity cost is primarily driven by the selection of available isolated flyback transformers and ultra-low gate threshold MOSFETs, and that with a high volume custom solution, scaling would be much more linear.

The last thing to consider goes hand in hand with what has been previously stated regarding cell discrepancies, though it is still important to discuss because it highlights the true beauty of an active BMS that can not only balance during charge, but can also balance during discharge. Assume that as an absolute worst case scenario, you have a two cell string of batteries, and one battery is a 10Ah cell while the other is a 5Ah cell. Without balancing, the pack as a whole would only be a 5Ah pack, because they would never reach the limits at the same time due to the lower capacity cell always dictating the lower and upper limits. Also note that a traditional balancing system could easily get the cells in unison at 100 percent state of charge, but as soon as the discharge begins, the cells will separate and the charge-only balance algorithm will not do anything to compensate. This also means that both cells will always see the same aging due to current, but the weaker cell will see much greater aging due to the depth of discharge it is seeing as compared to the second. In an active BMS system, as soon as discharge begins, and the cells begin to separate, the BMS will begin moving energy from the higher capacity cell to the lower capacity cell. This does two things: it offsets the effective current between the two cells, and it alters the effective capacity of each cell. The higher capacity cell will see a higher average current, and therefore will age faster as a function of discharge current, and it will also see a higher depth of discharge as its energy is moved into the weaker cell, also increasing the aging effects. The opposite is true for the weaker cell, and the process should continue until the cells are matched, though in this extreme example, that would correspond to over a 50 percent reduction of capacity for the higher cell, and it would be deemed dead. An active BMS then becomes an extremely valuable tool in maintaining battery health!

## 1.3 Existing Systems and Topologies and their Short Comings

Many battery management system topologies exist which all accomplish the same thing: passive balancing via a pass transistor and/or a bleeding resistor. These range anywhere from simple 'dumb' zener diode biased transistor bleed circuits, to more complex comparator driven over-voltage detectors that bleed energy using a MOSFET and dissipation resistor, some of which are exampled in Figure 1.2. While some of these, like the zener biased pass transistor, do have some dynamic response qualities in that the balance current becomes proportionate to the amount of over-voltage, none of the all analog systems are smart enough to tailor the balance current to the level of imbalance among the cells. At best, a current proportional to the voltage over the threshold can be produced, but this is still a static threshold that does not move. Even if the cells are perfectly balanced once the threshold is reached, all of the balancing circuits will be active, and the charger must be smart enough to account for this 'extra' current when performing the CC-CV charge algorithm and subsequent cut off.

Figure 1.2: Example of passive balancing topologies. (Left) Bleed resistor with externally driven MOSFET. (Middle) Pass transistor biased with zener diode. (Right) Bleed resistor with locally driven MOSFET using comparator

The shortcomings of passive charge-only balancing schemes and topologies are no secret [4]. Discharge currents are typically orders of magnitude higher than recharge currents in high power systems, so most of the imbalance takes place during discharge where the balancing circuitry is not active. Even when the balance circuitry is active, for most passive designs, the balance current is binary: it's either on or off, and only varies proportionately with cell voltage. This means that higher levels of imbalance in some cells are treated no differently than lower levels of imbalance. It becomes obvious that an active system that can not only move energy from one cell to other cells in the pack, but can do so proportionately, both during charge and discharge, would be a much more efficient and effective means of maintaining balancing in the system. There is vast amounts of literature related to such active battery management schemes, ranging from capacitively coupled charge shuttling systems [5], to coupled inductor hybrid DC-DC converter systems [6]. Several of these topologies are exampled in Figure 1.3.

The inductor based boost mode balancer uses a boost converter topology to charge the inductor using the bottom switch, and the body diode in the top switch allows for charge to transfer to the top cell once the bottom switch is turned off.

Figure 1.3: Example of active balancing topologies. (Left) Inductor based boost mode active balancing. (Right) Capacitor based charge shuttle active balancing

While this topology is very convenient in that parts count is low, and the energy transfer rate can be very high, this is a very limited scheme. Energy can only be shuttled one cell at a time, and the system becomes much more complex when the topology is extended for bidirectional energy flow [7]

The capacitor based charge shuttling topology, while extremely simple to implement, and arguably the most efficient of the active topologies, is also severely limited. Balancing is achieved by operating all of the switches simultaneously, each either in the high position or the low position. Cells that are higher than the capacitor voltage when switched will charge the capacitor, and cells that are lower than the capacitor when switched will discharge the capacitor, effectively moving charge from higher cells to lower cells until perfect balance is achieved. Balancing therefore is inherently uncontrollable, in that every cell in the stack is operated on identically and balancing is either on or off, and the energy transfer rate is directly proportional to the size of

the capacitors and the switching frequency [8][9]. It is also increasingly less effective as the voltage on the cells equalize, and energy transfer is extremely "elastic" in that it is very slow to moved charge from many cells into a single weak cell.

There are many other active topologies as well, and each has its shortcomings, whether it be the power limitations in capacitor based systems, to the complexity and weight limitations in hybrid DC-DC converter based systems. Even systems specifically synthesized to minimize parts count, such as the single switch Sepic topology [10] come with the trade-offs of relatively slow balancing and very complex control schemes. One system stands out though: the isolated flyback system [11].

# 1.4 FlyBMS Overview

This thesis then focuses on the design and implementation of an isolated flyback based active battery management system, with a novel proportional balance control scheme unique to this design. The isolated flyback based active balance system is inherently isolated, inherently modular, requires no custom components, and can easily be operated in open loop mode (though some protection was found to be paramount in overall robustness, as will be discussed later). A simple flyback based balancer is exampled in Figure 1.4.

In this system, the transformer primaries are all tied directly to each cell, and the secondaries are all in parallel across the entire battery stack. Switches on the primary side (MOSFETs) charge the transformer, and switches on the secondary side (diodes) rectify the transformer output. Energy taken out of a single cell is boosted to the full pack voltage and dumped back into the entire string. Using a properly

Figure 1.4: Example of an active flyback based balancing topology

designed control system, energy can be taken from a specific subset of cell(s) and moved into other specific subsets of cell(s), giving the designer complete freedom to manage the state of charge of every cell in the pack all the while dissipating orders of magnitude less energy as heat than a typical passive bleed system. One other key aspect of such a system is that the duty cycle of the driving signal can be varied in order to vary the balance current, so the designer not only has the freedom to move energy from and to anywhere in the stack, they can do so at virtually any rate, giving them the ability to target specific corrections. A system can be configured to only target minor voltage imbalance, voltage imbalance coupled with state of charge imbalance with tracking, and even a mode where overall health is not considered unless a cell has become a major limiting factor in overall pack capacity.

# CHAPTER 2

#### MODELING AND SIMULATION

# 2.1 SOC Based Active Balancing MATLAB Simulation

In order to study the feasibility of an active balance system that can move energy from a single cell into the entire stack, a high level energy transfer simulation was developed using MATLAB. The goal of the simulation was to study the electrical behavior of the cells from a strict energy transfer point of view, as well as to early identify any potential pitfalls with such a balance algorithm. The simulation is built around a 10-cell battery pack, has the ability to cycle the pack under a constant current profile or a constant power profile, uses a lookup table built from a lithium-ion charge and discharge curve, and can be run with or without the balancing algorithm. The simulation was built on an integration loop with a 10ms timing, with a three operation state calculation set per iteration of the simulation. The inputs to the simulation are initializations for cell voltage, cell stage of charge, cell balance duty cycle, cell ESR, and external current set point.

The first loop operation is to calculate the net change in overall pack capacity. For this operation, external current is integrated over the loop timing to yield a net capacity change for the pack as a whole, which is then applied to the state of charge of each individual cell's SOC tracking vector (Equation 2.1). For this step, external current is either represented by a constant in the case of a constant current charge/discharge mode, or by a current dictated by the total pack voltage and the

power set point in the case of constant power charge/discharge mode.

$$SOC(i+1) = SOC(i) + \frac{I_{ext} * T_{step}}{3600}$$

(2.1)

The second operation calculates net changes in each cell's individual SOC as a function of the balance current for each individual channel, where balance current is defined as the isolated current being sourced out of an individual cell. Since each cell has an individual flyback converter capable of up to 2.5A, the maximum balance current was set to a constant 2.5A. Each converter's duty cycle is also variable, and can operate at any current between 0A and 2.5A, so it was necessary to form a function that could determine the duty cycle of each cell's converter based on some parameter, and then convert that to a balance current. It was decided that, since the lowest cell will always be the limiting factor during charge and discharge, the balance current for a given cell should be proportionate to the voltage difference between said cell and the lowest cell in the pack. Equation 2.2 shows this relationship, and also serves to show that the balance current for the lowest voltage cell in the pack will always be zero. Duty cycle is then translated to current as a function of max balance current, as shown in Equation 2.3.

$$Duty(i, cellnum) = getDuty(Voltage(i, cellnum), Vmin(i))$$

(2.2)

$$CellCurrent = (-1 * Duty(i, cellnum) * MaxBalanceCurrent)$$

(2.3)

The translation from cell voltage discrepancy to duty cycle is a very dynamic relationship that depends on many things, such as voltage resolution in the final system, the noise floor in the final system, and hysteresis effects due to instantaneous changes in cell voltage due to the ESR. As will be discussed later, in order to make the system truly universal, balance currents must be applied "softly" when the voltage discrepancies are small, because large jumps in balance current will result in large drops across the cell's ESR, which will then cause race conditions (software oscillatory condition where previous decision directly impact the outcome of subsequent decision, independent of the actual system) in the balance algorithm and subsequent oscillations in the BMS state machine. However, it is also necessary to ramp the balance current quickly as the voltages deviate further in order to be able to react to real changes in the cell voltages should one cell begin separating quickly from the average voltage. For these reason, it was decided to use an exponentially increasing duty cycle, that ramps balance current exponentially as a cell's voltage descrepancy climbs. In order to prevent 10ms oscillations in the applied duty cycle and subsequent balance current, a simple exponential mapping was used to map voltage deviations to duty cycles, as depicted in Table 2.1. The final form of this table was narrowed down after many tests were performed within the simulation, and further refined in hardware during the hardware testing phase. The mapping function also accounts for simple limiting, where duty cycle is set to zero in the event that a cell is completely dead in order to prevent cell damage.

The final operation in the simulation loop is to relate the newly calculated SOC vector to a new voltage for each cell, to be used in the next iteration of the simulation

Table 2.1: Mapping of voltage discrepancy ranges to applied duty cycle for each channel's flyback converter

| *                 |                 |

|-------------------|-----------------|

| Range1 = .001V    | Duty1 = .05     |

| Range2 = .0015V   | Duty2 = .11     |

| Range3 = .002V    | Duty3 = .18;    |

| Range 4 = .0025 V | Duty4 = .25;    |

| Range5 = .003V    | Duty $5 = .32;$ |

| Range6 = .0035V   | Duty $6 = .39;$ |

| Range7 = .004V    | Duty7 = .46;    |

| Range8 = .0045V   | Duty8 = $.53$ ; |

| Range9 = .005V    | Duty9 = .6;     |

| Range 10 = .006 V | Duty10 = .67;   |

| Range11 = .008V   | Duty11 = .74;   |

| Range12 = .010V   | Duty12 = .81;   |

| Range 13 = .013V  | Duty13 = .88;   |

| Range14 = .016V   | Duty14 = .95;   |

| Range15 = .020V   | Duty15 = 1;     |

|                   |                 |

loop. The lookup table for this SOC relationship was formed by performing a very slow C/10 discharge and charge of an existing lithium-ion cell, from 100-0 percent SOC and 0-100 percent SOC respectively. The extremely low rate was chosen in order to obtain curves that are effectively independent of voltage variations due to the cell's ESR. The functions that perform these mappings are shown in Equations 2.5 and 2.7 respectively.

$$index = find(CHARGESOC(:, 2) == SOC, 1);$$

(2.4)

$$Voltage = CHARGESOC(index, 1); (2.5)$$

$$index = find(DISCHARGESOC(:, 2) == SOC, 1);$$

(2.6)

$$Voltage = DISCHARGESOC(length(DISCHARGESOC) - index, 1); (2.7)$$

The 10ms simulation loop runs continuously over a predefined period of time. Charge and discharge are defined simply by the cell voltage and SOC boundaries. If any cell reaches its maximum voltage or 100 percent SOC during the simulation, the external current applied becomes negative to represent a discharge, and if any cell reaches its minimum voltage or 0 percent SOC during the simulation, the external current applied becomes positive to represent a charge. The simulation also contains an aging parameter that linearly increases the ESR of the cells by a predefined amount to simulate aging within the cells. This scaling (shown in Equation 2.8) is proportionate not only to the number of cycles, but also by the external current applied, and is applied upon completion of every complete cycle of the pack, and is useful for observing BMS behavior over not only short term voltage discrepancies due to individual differences, but over long term discrepancies that become more prominent over time as the cells age and the voltage developed across the ESR during cycling grows.

$$ESR = ESR * I_{external} * AgeFactor$$

(2.8)

The high level simulation results were paramount in fine tuning the overall functionality of the system. Beyond the fundamental validation of feasibility of an active system, many parameters were optimized to improve overall performance, as well as to ensure extensibility of the system to any power level and/or lithium chemistry. Parameters considered during this testing were: control bandwidth of the BMS state

machine, effects of different chemistries and their respective voltage curves, mapping of the voltage differentials to balance currents, and the effects of varying ESRs both statically as well as over time.

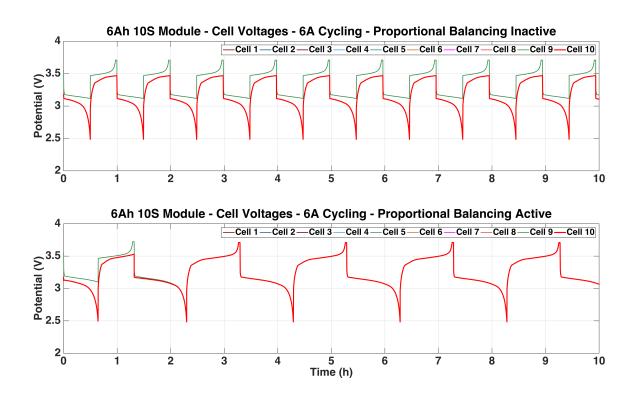

To start with, overall feasibility of the active system was validated. Control bandwidth was set to 10Hz (100ms), aging parameters were set to zero, duty cycle was mapped linearly to voltage imbalance, battery capacity was set to 6Ah, and the simulation was set to run in a constant current cycle mode with a set point of 6A (1C). All cells except for cell 10 were initialized with a matched ESR of  $10\mathrm{m}\Omega$ , and all but cell 10 were initialized to 100 percent SOC. Cell 10 was initialized to 50 percent SOC and  $15\mathrm{m}\Omega$  in order to force a full balance current initially as well as to force a permanent cell voltage discrepancy, such that BMS behavior could be easily validated both against capacity imbalance, as well as against ESR mismatch. After much trial and error with functionality of the simulation, a 10 hour simulation was run, both with and without active balancing. As is shown in Figure 2.1, the active system has proven to be functional. In the top plot, the battery pack is cycled within the limitations of the cells. The capacity window (window of usable capacity due to SOC imbalance in the pack) is equal to 3Ah due to the fact that one of the cells was initially at 50 percent SOC, and without balancing, the discrepancy is constant. In the bottom plot, however, the BMS corrects for the initial capacity discrepancy within the first two cycles, and the ESR mismatch is accounted for on a cycle-by-cycle basis to maximize the usable capacity.

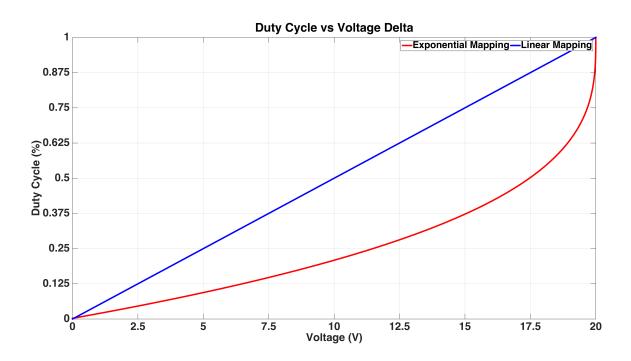

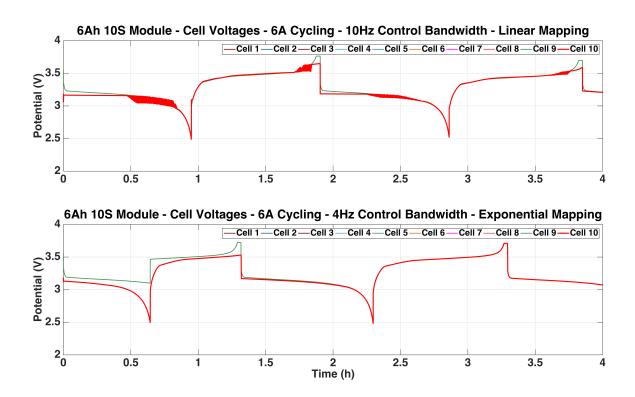

The next step towards utilizing the simulations for system tuning was to tune the balance current (duty cycle) mapping and the control bandwidth of the BMS state machine. During initial testing of the simulation, it was found that with lower

Figure 2.1: MATLAB simulation result that validates the active flyback BMS system.

power cells (ESR >  $20\mathrm{m}\Omega$ ) if the loop timing was too low, or the balance current was too high at small voltage discrepancies, the BMS state machine would enter an oscillatory condition. Every iteration of the state machine would toggle the balance duty cycle between 0 percent and 100 percent. To counteract this, two changes were made. The first change was to redefine the duty cycle mapping from a linear function to an exponential function. Initially, the duty of each cell was increased by 10 percent (150mA) for every 5mV that particular cell was above the lowest cell. This meant that for every 5mV of voltage discrepancy, an additional 150mA of load current was placed on a given cell by the balance circuitry, which would then cause additional voltage drop across that cell's ESR, which explained why it was more prominent on higher ESR cells. To counteract this, duty cycle mapping was reconfigured to increase

exponentially with the voltage discrepancy, such that small imbalances only resulted in very small balance currents, but large imbalances could still be reacted with full balance current. This duty cycle remapping, accompanied by a slower 4Hz control bandwidth that allowed the battery's natural voltage hysteresis to settle once balance current was enabled, made the system much more robust and tolerant to high ESR cells. Figures 2.2 and 2.3 example these changes and their effects respectively.

Figure 2.2: Mapping of voltage imbalance to applied duty cycle for each cell

The last parameter that was evaluated with the simulation was chemistry, ESR, capacity, and cycle rate independence. Many different lithium-ion chemistries exist, and each has a unique voltage curve. For testing purposes, I chose to evaluate curves from the Lithium Iron Phosphate (LFP) chemistry and the and the Lithium Manganese (IMR) chemistries respectively, because they have the most contrasting curve

Figure 2.3: MATLAB simulation result showing oscillations with original loop timing and duty cycle mapping

of any chemistry. LFP has the flattest voltage curve of any chemistry, only slightly varying in voltage in the 80-20 percent SOC range, while IMR has a very linear voltage curve in the same range. Testing was performed by simply discharging one of each of these chemistries at a low rate, building a normalized voltage vs SOC charge and discharge lookup table for each, and redefining the look up tables for battery voltage within the simulation. It was quickly found that, for the more linear IMR chemistry, if the balance current was not applied softly initially, oscillations similar to the high bandwidth oscillations would occur. Changing the exponential duty cycle mapping from a 2nd order exponential to a 4th order exponential in order to further "soften" the activations of the balance system almost completely remedied this, and the remaining instability will be addressed in the final embedded system should they

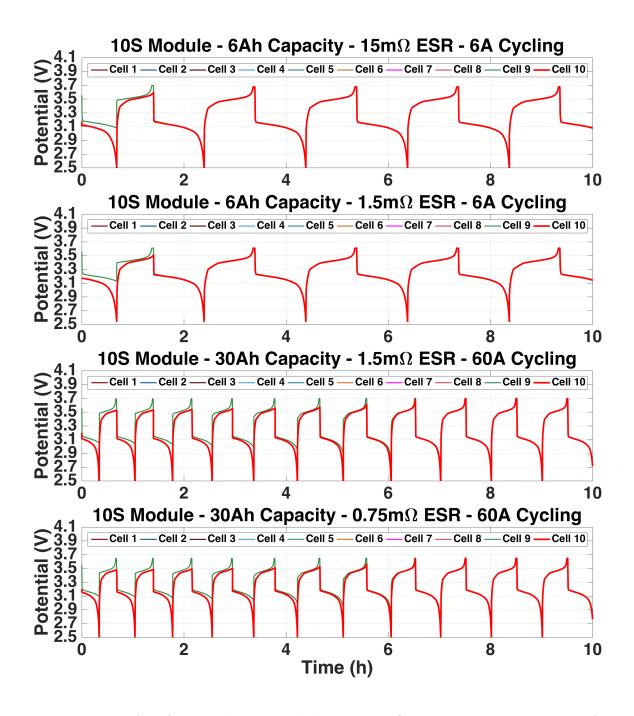

arise. Results from a sweep of capacities, cycle rates, and cell ESR are shown in Figure 2.4, and shows that the BMS operation is not compromised across a host of various cell parameters. The next step in system design was to design and construct the flyback balancer stage.

## 2.2 Simple mathematical model of a flyback converter

The flyback topology is a simple topology, with relatively straight forward solutions in both continuous conduction mode (CCM - transformer primary current never goes to zero) as well as discontinuous conduction mode (DCM - transformer allowed to fully desaturate between switching). Closed loop control of a flyback converter, however, can be much more challenging. The designer must consider not only the means of which to measure output voltage and/or current in an isolated manner, but the control loops have to also consider transformer saturation for robust performance. For the sake of simplicity, an open loop control mode will be implemented, and the transformer will be operated in DCM in order to avoid saturation of primary inductance of the transformer. In other words, rather than measuring output voltage and/or current on a cycle by cycle basis and compensating for the error by adjusting the duty cycle, output current will be mapped in software to a specific duty cycle at a specific input voltage.

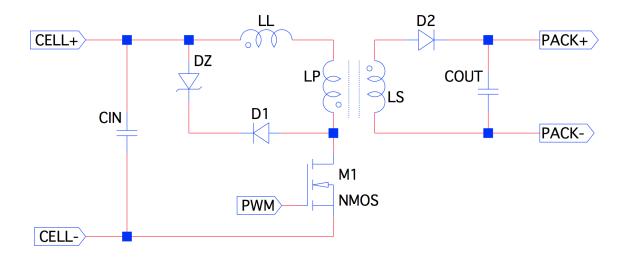

Figure 2.5 shows the basic topology that will be implemented. There are many variants of the flyback topology, and many great resources available regarding their design. The Art of Electronics [12] is an example of a great reference material for any engineer with a strong background in electronics, and it was the main reference for the flyback design presented here. In the figure, CIN represents the input filter

capacity of the flyback stage, LL, LP, and LS represent the leakage, primary, and secondary inductance of the transformer respectively, D1 and DZ make up the clamp circuit that will protect the MOSFET, M1 represent the MOSFET that is the main switch, D2 represent that output rectification diode, and COUT represents the output filter. The required specifications for theses components as well as many other relevant parameters are solved for next, followed by explanations for each component choice in the system. The first step towards solving for the parameters of any system is to identify your constraints as well as your constants.

In order to simplify the design of the flyback balancing stage, a decision was made to start by choosing a transformer, since there were not many options available for small yet relatively high power density transformers with a gain of at least 4. Most of the part selection justification will be in a later section, but the transformer characteristics drive the overall design, so it had to be sourced first. The transformers chosen were small transformers explicitly designed by Coilcraft for use in flyback converters, with a maximum primary current of 7A and a 1:4 turns ratio. The specifications given in Equations 2.9 to 2.14 summarize the key parameters of this transformer that will be used in the design. The switching frequency and voltage ranges are also defined.

Transformer Parameters

$$L_P = 4\mu H \tag{2.9}$$

$$L_L = 116nH \tag{2.10}$$

$$L_S = 64\mu H \tag{2.11}$$

$$R_P = 12m\Omega \tag{2.12}$$

$$R_S = 500m\Omega \tag{2.13}$$

$$I_{P,Max} = 6.5A$$

(2.14)

(2.15)

System Constraints

$$F_{SW} = 80kHz \tag{2.16}$$

$$T_{SW} = \frac{1}{F_{SW}} = 12.5\mu s \tag{2.17}$$

$$V_{In,Min} = 2.5V$$

(2.18)

$$V_{IN,Max} = 4.2V \tag{2.19}$$

$$V_{Out,Min} = 25V (2.20)$$

$$V_{Out,Max} = 42V (2.21)$$

The primary side of the transformer is nothing more than an ordinary inductor, and when a voltage is applied across an inductor, current ramps until a saturation point is reached, at which point the current is DC. In order to maximize energy transfer while still operating in DCM, it is desired to turn the main switch on just long enough to allow the transformer primary to reach saturation, turn it off just long enough to allow the secondary current to reach zero, and then repeat. This approach

allows all of the energy that is put into the primary side from an individual cell to be rectified on the secondary side and placed back into the pack, with the exception of any energy that is stored into the uncoupled leakage inductance which will be discussed later. This energy can be easily solved for, as well as the resulting average primary (balance) current at maximum duty cycle..

$$E_{In} = 0.5 * L_P * I_{P,Max}^2 = 84.5 \mu J \tag{2.22}$$

$$I_{SW,Avg} = \frac{E_{In} * F_{SW}}{V_{In,Max}} = 1.61A$$

(2.23)

Since we also know that we want to operate in DCM, we know that the beginning of every switching period on the primary side will start at zero current. We also know that we never want to exceed the maximum current rating of the primary side of the transformer. These two constraints allow us to easily identify the maximum on time of the primary switch in order to avoid exceeding the ratings on the primary. It is important to recognize from Equation 2.24 that the maximum on time changes with input voltage. This also implies that, if we are going to maximize the switching frequency of the system in order to minimize ripple current, we must consider every scenario of input voltage to be sure that the transformer is always allowed sufficient time to desaturate. This is how the 80kHz switching frequency was chosen, because  $12.5 \mu$ s is the minimum switching period that allows for full saturation and desaturation of the primary side at all input voltages.

$$T_{On,Max} = L_P * \frac{dI_P}{V_{In}} = L_P * \frac{I_{P,Max} - 0}{V_{In}}$$

(2.24)

Using the same principle as was applied to determine the input (and subsequent output) energy, we can also calculate the energy stored in the leakage inductance. The leakage inductance is a parameter used to account for the inductance on either the primary or secondary side of the transformer that is not coupled across the transformer. It is best visualized exactly as it is shown in Figure 2.5 (LL), in series with the primary side of the transformer. The energy in this inductance will not be transferred to the secondary side, and the voltage developed across it when the current goes to zero will be apparent on both sides of the transformer, reflected by the turns ratio. To prevent this voltage from becoming the limiting factor in the primary switch and secondary diode part choice, it must be dissipated in a controlled manner. We will discuss how to specify the voltage of this clamping circuit (DZ and D1) later, but first we must determine how much energy will be stored in this inductance so that we can specify a power requirement for the snubber components. This can be done by scaling the total energy in by the ratio of leakage inductance to total primary inductance.

$$E_{LL} = E_{In} * \frac{L_L}{L_P} = 9.8\mu J \tag{2.25}$$

From this energy, we can now find the power requirements of the snubber diode (DZ). Power can be found by integrating the energy over time, which becomes very simple since this is a switching circuit. It is important to note here that this simple

calculation considers the scenario where all of the inductive energy in the leakage is snubbed, but in practice we want to snub as little as possible for efficiency sake. As will be shown later, only roughly twenty percent of the leakage inductance energy will be dissipated to protect the MOSFET, so this calculation shows a worst case scenario.

$$P_{Dis,DZ} = E_{LL} * F_{SW} = 1.3W (2.26)$$

Knowing how much energy is being put into the transformer, and how much will not transfer due to uncoupled leakage, we can then solve for how much energy will be transferred to the secondary side. We can use the same technique used to solve for input energy to relate input energy to output energy using the secondary inductance. It is important to realize that the leakage inductance only appears on one side of the transformer, so we do not need to account for it again on the secondary side. We can also use the secondary energy calculation to calculate the peak current of the rectification diode (D2) on the secondary side, which occurs when the pack voltage is at its minimum. This assumption only holds true due to the fact that we will be mapping duty cycle to input voltage such as to keep the average primary current, and therefore input energy, constant. From equations 2.27 and 2.28 we can see we will need a diode with at least 1A of peak current capability to have some factor of safety.

$$E_{Out} = E_{In} - E_{LL} = 88.1 \mu J \tag{2.27}$$

$$I_{D2,Peak} = \frac{E_{Out} * F_{SW}}{V_{Out,Min}} = 493mA$$

(2.28)

The next step then is to solve for the voltages that will be seen at the primary and secondary side of the transformer during the on and off period of the switch. These calculations will not only allow us to specify the minimum required voltage ratings of the input switch and output diode, but we can also use it to specify a clamp voltage that will minimize the power dissipated in the clamp circuit while ensuring that the MOSFET remains protected. We will start with the voltages during the on period of the switch.

When the switch is on, the voltage across the primary is equal to the input voltage, which is reflected to the secondary side via the turns ratio. This appears as a negative voltage on the secondary side, which is why no current flows on the secondary side while the switch is on. This also means that the rectification diode on the secondary side is responsible for holding off the output voltage as well as the additional voltage developed across the secondary.

$$V_{S,Min} = -1 * V_{In,Max} * \frac{L_s}{L_P} = -15.75V$$

(2.29)

$$V_{D2,Max} = V_{Out,Max} - V_{S,Min} = 57.75V (2.30)$$

When the switch is off, just as how the primary voltage was reflected to the secondary side while current was flowing in the primary, secondary voltage will be reflected to the primary side while current is flowing in the output rectification diode. We can simply reflect the peak secondary voltage back to the primary side.

$$V_{P,Max} = \frac{V_{D2,Max}}{\frac{L_P}{L_S}} = 11.2V \tag{2.31}$$

We can see then, that the switch needs to be able to survive a minimum of 11.2 V in order to survive the voltage reflected as a function of the normal flyback operation. However, we also need to account for the voltage developed across the leakage to be able to properly specify a MOSFET as well as a snubber circuit.

$$V_{Leak} = L_L * \frac{I_{P,Max}}{T_{SW} - T_{On,Max}} = 9.1V$$

(2.32)

This voltage, added to the input voltage and the reflected secondary voltage, is the peak voltage which the switch should be able to survive. The percentage of the leakage voltage which will be allowed to be present is also what will scale the power dissipation in the snubber circuit.

$$V_{DS,Peak} = V_{P,Max} + V_{Leak} + V_{In,Max} = 24.5V$$

(2.33)

From these equations, we can see than that the MOSFET drain-source voltage needs to be rated to no less than 25V. We also know that the MOSFET needs to be able to handle at least 6.5A to carry the peak drain current voltage. The last parameter that needs to be considered for the MOSFET is the gate threshold voltage. Because the MOSFET is on the primary side, and the control circuitry will be isolated completely from the battery, the MOSFET will be driven with an isolated driver circuit. The simplest way to accomplish this is with a complementary output (Push-Pull) optocoupler, which will pull the gate between 0V and cell voltage. This implies then, that the MOSFET must be capable of fully turning on at even the minimum cell voltage of 2.5V. Only a handful of MOSFETs exist that can carry greater than 6.5A, are rated for a drain voltage of 25V or greater, and have the drain resistance full specified at voltages as low as 2.5V, the only manufacturer with a full line of such MOSFETs is Vishay, so a suitable switch was chosen from their lineup. The driver topology will be discussed in full in a later section, but the drain voltage of the chosen switch is 40V, so the snubber should only be chosen such as to clamp the developed primary voltage to less than 40V. The clamp diode (DZ) was chosen to be a 21V TVS diode, that breaks down at approximately 28V and clamps at 38V, and is rated for 1 Watt of power dissipation, which together should be more than enough to protect the switch.

The last flyback parameter to consider is the minimum off time required to keep the converter in DCM. Since the flyback is going to operate in DCM, it is imperative to ensure that adequate time is allowed for the transformer secondary current to ramp to zero during the switch off time, such that all of the energy put into the primary side during the on time is rectified and transferred back into the battery during the off time.

$$T_{Off,Min} = L_S * \frac{I_{D2,Peak}}{V_{Out,Min}} = 1.3\mu s$$

(2.34)

This time, in conjunction with the maximum calculated on time, can then be used to determine the total time period required to reach saturation on the primary side and subsequently desaturate fully on the secondary side. This time will determine the maximum switching frequency, shown in Equation 2.36. An important thing to realize here is that the final design should incorporate some additional delay. Many parameters are involved in determining stability of switching nodes in switching circuits, and designers should always expect some oscillations at the switch node and allow adequate time to damp them, which is part of the rational for an increased switching period.

$$T_{SW,Min} = T_{On,Max} + T_{Off,Min} = 8.5\mu s$$

(2.35)

$$F_{SW,Max} = \frac{1}{T_{SW,Min}} = 120kHz \tag{2.36}$$

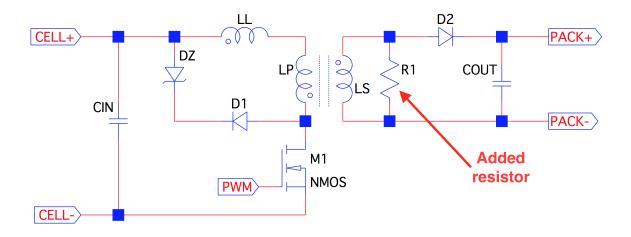

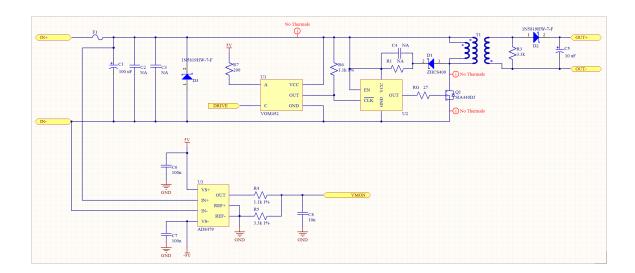

Regarding the design, one final consideration must be entertained. Typically in a switch mode power supply, where a flyback would typically be implemented, the output voltage is defined by the output of the converter. If the converter is off, the output voltage will drop to zero, allowing the transformer to fully desaturate. In this system, however, the output voltage can never fall below the total pack voltage, because the output is tied directly to the battery stack. Thus far, the design has been structured such that when the switch is turned on, the primary is charged, and when the switch is turned off, the secondary is discharged, and the snubber dissipated the excess energy in the leakage. In theory then, all of the transformer's stored energy is accounted for, allowing operation in DCM. However, because the output can only rectified while the secondary voltage is greater than the battery voltage, all of the voltage developed on the secondary cannot be rectified, and the leakage energy is not the only energy remaining in the transformer once the rectification diode stops conducting. From experience, it is expected that the remaining uncoupled energy will begin to oscillate between the primary and secondary, and will continue to do so until it is either dissipated or naturally damped. To prevent this excess energy from creating oscillations, it is necessary to provide a continuous conduction path on either the primary or the secondary. The simple approach is to place a resistor across the secondary, such that minimal energy is dissipated during output diode conduction, but the excess energy is dissipated during the additional off time facilitating complete desaturation of the transformer. This modified flyback topology is shown in Figure 2.6 with the additional dissipation resistor (R1). The actual value of this resistor was tuned in the spice simulation, which is discussed in the next section.

# 2.3 Component level Spice simulation of flyback stage

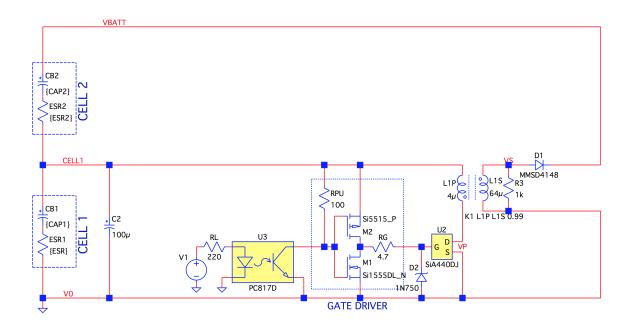

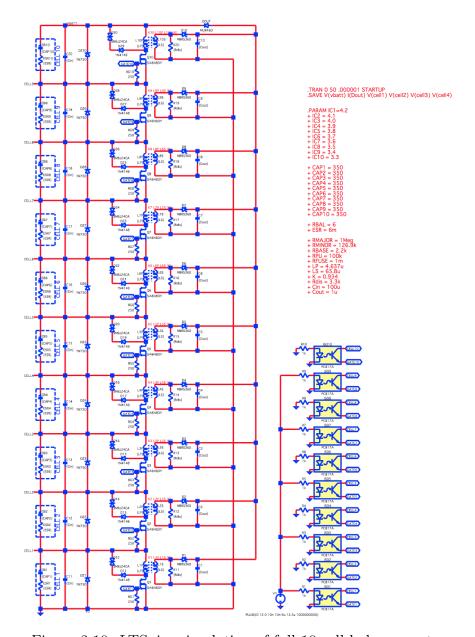

Once the necessary flyback component parameters were determined, a component level spice simulation was developed, first for one single cell, and later for a full 10 cell balance system. The parameters used were sourced directly from the mathematical model derived in the previous section, and the components used were either models directly taken from the manufacturers of the components chosen or were modeled to as closely resemble the real components as possible. The simulation was developed in LTSpice, which is a free schematic capture and spice simulation engine from Linear Technologies. The simulation topology for a single cell simulation is shown in Figure 2.7.

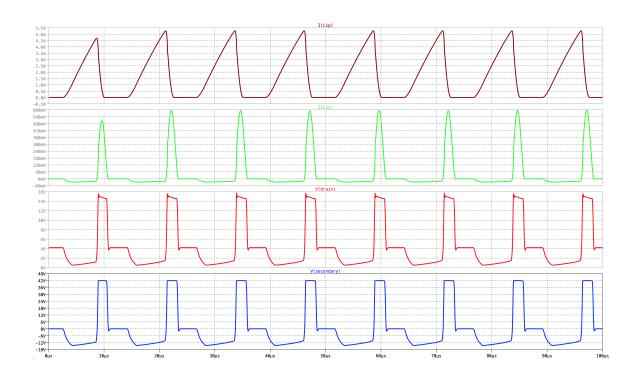

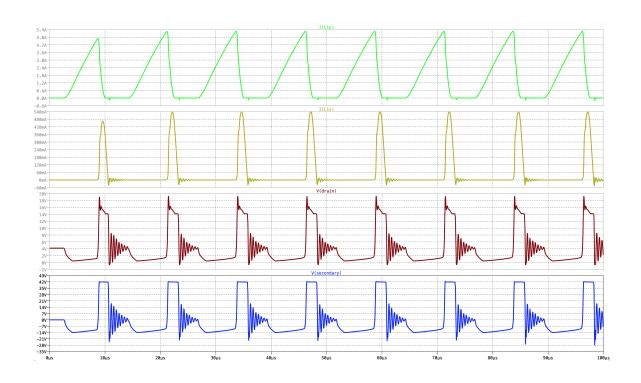

To validate the flyback components, the single cell simulation was run for only a few pulses. In the simulation, the primary current peaked at 5.5A, the secondary current peaked at 600mA, and the primary (drain) and secondary voltages were nearly exactly the expected values. Some experimentation was also performed with the output dissipation resistor removed to observe the behavior, and as expected, the trapped energy in the transformer cause extremely high frequency oscillations. Both of these results are exampled in Figures 2.8 and 2.9.

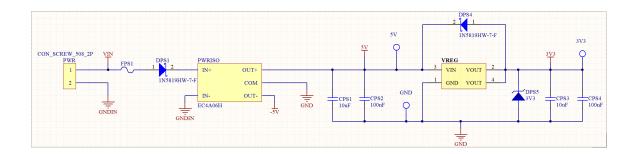

For dexterity and sake of completeness, the simulation was then scaled to a full 10 cell simulation. The goal of this full scale simulation was to identify any point of contention when scaling the system, such as interaction of the converters with one another, effects of added series resistance with fuses, and the effects of the snubber circuitry and the additional output diodes. This topology is shown in Figure 2.10, which also shows the addition of fuse resistance, snubber circuitry, and an additional secondary output rectification diode whose purpose is to prevent high current charging of the output capacitances when the pack is connected to the BMS.

This simulation was configured to run for 1800s, with the duty cycle set to 100 percent. The duty cycle was only applied to half of the cells, every other cell in the stack, so that the effects of the cells with balancing enabled could be compared to those without it. This simulation also was used to verify that the power dissipation within all of the components would not exceed the ratings of the chosen parts over a long period of time. Every component was found to be within the limits of the parts chosen, and energy transfer was clearly observed, as the voltages of the cells with balancing inactive increased and those with balancing active decreased.

Figure 2.4: MATLAB simulation result showing BMS operation across a sweep of various cell parameters

Figure 2.5: Basic flyback converter topology applied in the FlyBMS

Figure 2.6: Modified flyback converter topology applied in the FlyBMS, with added output dissipation resistor

Figure 2.7: LTSpice simulation of proposed flyback balance circuit

Figure 2.8: LTSpice single cell simulation results with output resistor

Figure 2.9: LTSpice single cell simulation results without output resistor

Figure 2.10: LTSpice simulation of full 10 cell balance system

## CHAPTER 3

#### HARDWARE DESIGN

### 3.1 Component Selection

Having fully characterized the flyback system as implemented allows for us to fully specify the components in the final design. For each component in the system, a part was sourced that is fully rated to the constraints from chapter 2, was in stock, and was easily workable into an all surface-mount board topology. These component selections are outlined next.

Flyback Transformer: The flyback transformer had to be chosen in advance, such that the rest of the converter could be designed around it. The CoilCraft part chosen met the gain requirements, met the primary and secondary current requirements, met the primary and secondary voltage requirements, had more than adequate isolation ratings between the primary and secondary, and is an 8 pin surface mount part.

Primary Switch: The primary switch requirements are simple. The switch should be able to be driven at 80kHz with minimal switching losses, it should be able to switch a load of up to 10A (for some safety factor) with minimal conduction losses, it should be rated for gate threshold voltages as low as 3.0V, and should be able to survive drain to source voltages in excess of 24.5V. These are very specific requirements for a MOSFET, specifically the low gate threshold and high current capability, and only one manufacturer has a full line of such qualified devices - Vishay.

The MOSFET chosen has a drain to source voltage rating of 40V, has a very low gate charge (6.9 nC) which will facilitate high frequency switching with low gate drive requirements, and the  $R_{DS,On}$  is specified at only 35 m  $\Omega$  at a gate voltage of just 2.5V [13]. The only downside of this particular switch is the package. The only available package is a very small SC-70 surface mount package, that will not only be intolerant to any power dissipation should the switch be inadvertently placed in the linear region during testing, but will also be intolerant to improper soldering, which may be a point of contention during the prototyping phase.

Snubber Circuit: Having the MOSFET narrowed down, we can now choose parts for the snubber circuit. From the math in the previous section, it was determined that the maximum drain to source voltage that will be present on the MOSFET is 24.5V, which is well within the ratings of the MOSFET chosen. To ensure maximum efficiency then, it should only be necessary for the snubber circuit to conduct in the event that a drain to source voltage transient greater than 24.5V occurs. For this reason, a 21V TVS diode was chosen as the snubber diode, which has an initial breakdown voltage at approximately 26.7V, a final breakdown voltage of 38.9V, and a maximum continuous power dissipation of 2W. Since this is a unidirectional part, a second adequately rated Schottky diode was placed in series that would prevent the TVS from becoming forward biased and bypassing the transformer. Both parts are SOD-123 SMD package parts, which should allow for compact packaging.

Output Rectifier: Knowing the peak current, the peak secondary voltage of the transformer, and the peak battery voltage, we can specify the output rectification diode. This diode must be rated to handle the peak pulsed current of the secondary, and must be capable of holding off the the peak voltage developed at the secondary

during the switch off period. Math derived previously shows that the peak current in the secondary will be equal to approximately 500mA, but the simulation showed 600mA, so the minimum pulsed current rating of the diode should be no less than 500mA with an adequate factor of safety. The average current will be roughly 35 percent of the peak, so the average forward current should be no less than 350mA. The peak voltage developed at the secondary will be equal to approximately 58V, so it should also have a maximum repetitive reverse voltage of 60V and a maximum non-repetitive reverse voltage of no less than 75V, both with an adequate factor of safety. From these parameters, a Schottky diode was chosen that has a peak non-repetitive reverse voltage of 100V, a peak repetitive reverse voltage of 75V, a peak current capability of 4A, and a continuous forward current rating of 500mA. The package is once again SOD-123 SMD, so it should also allow for simple packaging.

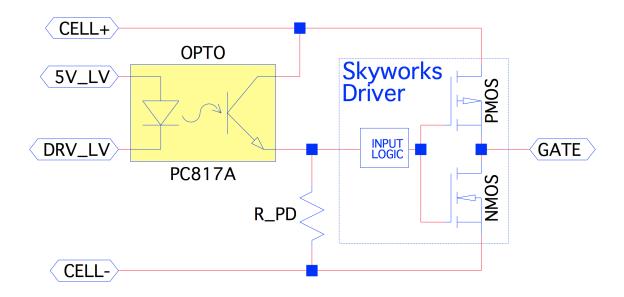

Isolated MOSFET Driver: In order to properly meet the requirement put in place by the rules, for the control circuitry to be completely isolated from the battery, it is necessary to develop an isolated driver stage that is not only able to decouple the control circuitry from the MOSFET, but is also able to drive the MOSFET from the cell voltage with minimal voltage drop in the driver circuit. To accomplish this, a suitable high frequency and low voltage capable MOSFET driver IC was sourced from Skyworks that is specially designed with a CMOS totem pole output capable of driving extremely low voltage MOSFETs [14]. This IC can operate between 2.0V and 5.5V, is capable of driving the MOSFET gate high or low at up to 2A, has an ultra-low logic threshold on the input, and includes a separate enable pin that can be used to locally disable the MOSFET using external detection circuitry for one of many various faults. The only remaining challenge then is isolation, which was simply accomplished using a pull down on the input to the driver accompanied by an

open drain optocoupler capable of pulling this enable pin high. This driver stage is depicted in Figure 3.1.

Figure 3.1: Isolated MOSFET driver topology applied in the FlyBMS

Isolated Feedback: In order for the controller, which is isolated from the battery pack, to make informed decisions regarding the state of the cell, there needs to be some form of isolated voltage measurement circuitry. In the final implementation, the controller on each BMS board will talk to each other through an isolated CAN bus, and each board will be able to talk to a host PC through an isolated USB interface, so the safety isolation is already accounted for. The isolation between the pack and the controller is just a second layer of protection, but it is not strictly defined that it is a highly hardened galvanic isolation layer. To simplify the voltage measurements then, very simple differential amplifiers were applied across the input of each cell to take the differential cell voltages and convert them to single

ended voltages at the controller for measurement. Rather than implementing these differential amplifiers in discrete components, which would have inherent mismatch and subsequently suffering common mode performance regardless of part tolerances, it was decided to implement purpose built differential amplifier IC. The ICs chosen from Analog Devices have a maximum common mode voltage range of 600V DC, a very low offset voltage for offset error, and have a common mode rejection ratio close to 100 dB. This single IC has all of the differential mode resistance built into the die, and they are laser trimmed for absolute accuracy, so it takes the place of more than 10 discrete components and has twice the expected performance of a discrete solution.