### INVESTIGATION OF DEGRADATION IN ADVANCED

ANALOG MOS TECHNOLOGIES

by

## MD. IQBAL MAHMUD

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT ARLINGTON

December 2013

Copyright © by Md. Iqbal Mahmud 2013

All Rights Reserved

### Acknowledgements

All praises be to the almighty Allah. My sincere gratitude goes to my advisor, Prof. Zeynep Çelik-Butler for her outstanding contribution towards my research. She has provided me with close guidance over the years, and always inspired me to go for extra mile. She has always been available, and willing to have a discussion, even on a weekend. She sacrificed her time for me whenever I needed guidance, and showed my strengths and weaknesses very patiently. I improved my presentation skill by attending biweekly teleconferences with our industry liaisons, and I had my advisor always with me to help. I feel fortunate to get exposure to industry mentors from Texas Instruments and Freescale Semiconductor Inc., who were accessible whenever I required suggestion. I would like to thank Prof. Donald Butler for his frequent suggestions, and my committee members Professors Dereje Agonafer, Samir Igbal and Ali Davoudi. I thankfully acknowledge Dr. Samir Igbal's mentorship and friendly interaction over the years. I feel honored to work with Dr. Jeff Smith, Sameer Pendharkar, Dr. Hal Edwards and Dr. Akram Salman during my summer internship in Texas Instruments. Dr. Hal Edwards has always been an inspiration for me since the last year. I also want to acknowledge my past and present colleagues Dr. Shahriar, Dr. Tanvir, Dr. Nuditha, Dr. Murali, Dr. Suraj, Moinuddin, Bhargav and Mohamed for their help and useful discussion. I would like to thank all the staff members of Nanofab at the University of Texas at Arlington, as well.

Finally, I would like to express my earnest gratitude to my dear parents, Md. Ishaq and Mrs. Mazeda Begum, my affectionate brothers Mamun and Masud, and my only sister Maya. I am indebted to them for their endless love for me and most importantly, for the encouragement and mental support they provided me all these years. No matter how far they live, they are always in my heart.

December 9, 2013

iii

#### Abstract

# INVESTIGATION OF DEGRADATION IN ADVANCED ANALOG MOS TECHNOLOGIES

Md. Iqbal Mahmud, PhD

The University of Texas at Arlington, 2013

### Supervising Professor: Zeynep Çelik-Butler

The focus of this work is to study the noise and degradation in advanced high and low voltage analog Metal Oxide Semiconductor Field Effect Transistors (MOSFET). Medium and high voltage transistors, especially lateral double diffused MOS (LDMOS) FETs are known as the workhorse for present day RF and analog mixed signal smart power applications. In presence of multiple in-plane Si-SiO<sub>2</sub> interfaces in asymmetric LDMOS devices, additional defects are created in those interfaces. The trappingdetrapping of charge carriers by these traps lead to increased low frequency noise (LFN) degradation in LDMOS compared to CMOS transistors. Hence, LFN sets a performance limit and increases the reliability concern in LDMOS devices. The majority of applications of LDMOS devices are in high frequency analog circuits and equipment, for example, in cellular communications, whereas 1/f noise is generally known to be important for frequencies up to 10 kHz. However, when the spectrum is up-converted to higher frequencies, noise gets amplified as well due to different nonlinearities in the system. This in effect, increases the phase noise in communication system and other reliability concerns during device operation. This can result in significant performance degradation of the system itself at the operational frequencies. This is why the study of 1/f noise degradation in medium and high voltage LDMOS is vital from the industry point of view.

iv

On the lower voltage side, analog submicron transistors are extensively utilized for obtaining high gain and bandwidth, while consuming low on-state power in analog to digital (and vice-versa) interfaces, in communication systems and in industrial electronics. Continuous downscaling of advanced submicron area low voltage analog MOSFETs requires rigorous in-depth study of the gate-oxide reliability. As compared to their highvoltage counterparts, these smaller devices have the oxide thickness of a few nanometers. This makes them vulnerable to individual defects in the Si-SiO<sub>2</sub> interfaces more severely than the high-voltage devices. Hence, it is necessary to identify, quantify, individually characterize and accurately model electrically active defects (charge trapping and scattering centers) in scaled analog and mixed signal (AMS) devices. In this regard, random telegraph signal (RTS) noise measurement to characterize single charge carrier switching events in time domain, is of significant importance in present-day submicron device technologies, because of its versatility and inherent non-destructiveness to devices, as far as the device degradation is concerned.

For LDMOS, the DC stress induced degradation characteristics of differently processed devices are studied in this work along with the noise performance. It is illustrated in this work that modeling the DC degradation alone cannot fully explain the physical mechanisms for LDMOS degradation. Hence, *1/f* noise was utilized as a non-destructive characterization tool to quantitatively evaluate the device reliability and degradation at time-zero and after they were subjected to stress-induced degradation. Correlation has been established between low frequency noise and DC stress-induced degradation. From that, a simple but well-defined approach has been delineated to separate the individual resistance and noise components in different regions of these devices. The effect of extended drain drift region scaling on *1/f* noise performance is

studied for different foundry-fabricated devices. An early lifetime prediction method for LDMOS is also reported here using 1/f noise measurements.

This work represents the first ever physics-based 1/f noise model for LDMOS devices, and demonstrates that the developed model can correctly predict the experimentally observed noise behavior in the linear region of operation in fresh devices as well as in stressed devices. The model is based upon the correlated carrier number and mobility fluctuation theory known as the Unified 1/f Noise Model, but has been modified to account for the fluctuations in the extended drain as well as the channel. Unlike the Unified 1/f Noise Model, non-uniform trap distribution has been taken into account with respect to the position in the gate oxide and in the band-gap energy.

In case of low voltage analog CMOS, we have demonstrated the RTS noise measurement and analysis technique to isolate each individual physical defect, and to characterize the trap properties both quantitatively and qualitatively. Multiple level RTS have been observed in submicron NMOS transistors at room temperature. From our analysis, we could ascertain the presence of two active traps, which are found to be responsible for four level RTS generation. Two different types of active traps- donor and acceptor, responsible for RTS generation, have been identified simultaneously for the first time in the same NMOS transistors at room temperature. A numerical computation method has been developed to separate fluctuations due to each trap, and to calculate the trap properties such as the mean capture and emission times, trap energy, capture cross-section and the distance into the oxide from the interface.

# Table of Contents

| Acknowledgements                                                          | iii  |

|---------------------------------------------------------------------------|------|

| Abstract                                                                  | iv   |

| List of Illustrations                                                     | xi   |

| List of Tables                                                            | xxi  |

| List of Symbols                                                           | xiii |

| Chapter 1 Introduction                                                    | 1    |

| 1.1 Preface and Motivation                                                | 1    |

| 1.2 Degradation in Scaled Down Analog MOSFETs                             | 3    |

| 1.2.1 Scalability and Applications of high Voltage and Low Voltage Analog |      |

| MOSFETs                                                                   | 3    |

| 1.2.2 Degradation Study Techniques in Analog Transistors                  | . 5  |

| 1.3 Noise in Semiconductor Devices                                        | 6    |

| 1.3.1 Dominant Low Frequency Noise Sources: 1/f Noise and RTS Noise       | 7    |

| 1.3.2 Other Noise Sources: Thermal Noise, G-R Noise and Shot Noise        | 9    |

| 1.4 1/f noise in Medium and High Voltage LDMOS Transistors                | 11   |

| 1.4.1 Introduction to LDMOS                                               | 11   |

| 1.4.2 Sources of 1/f Noise in LDMOS                                       | 12   |

| 1.4.3 1/f Noise Measurement as a Non-Destructive Degradation Analysis     |      |

| Technique                                                                 | 13   |

| 1.5 RTS Noise in Low Voltage Analog Transistors                           | 15   |

| 1.6 Summary                                                               | 16   |

| Chapter 2 Electrical Stressing and Noise Measurement                      | 19   |

| 2.1 Introduction                                                          | 19   |

| 2.2 Device Specifications                                                 | 20   |

| 2.3    | Noise Measurement Procedure                                    | 21 |

|--------|----------------------------------------------------------------|----|

| 2.4    | Stressing and DC Measurements                                  | 27 |

| 2.5    | Standalone DNWell Resistor Noise Measurements                  | 30 |

| 2.6    | Summary                                                        | 34 |

| Chapte | er 3 Analysis of Stress Induced Degradation in LDMOS           | 35 |

| 3.1    | Introduction                                                   | 35 |

| 3.2    | Effect of stress on DC and Noise Characteristics               | 35 |

| 3.3    | Separation of Resistance Components                            | 42 |

| 3.4    | Separation of Noise Components                                 | 45 |

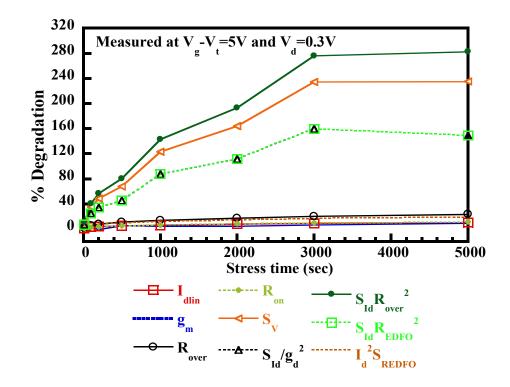

| 3.5    | Stress Duration Dependence of 1/f noise                        | 49 |

| 3.6    | A Quantitative Analysis on the Dominant Noise Sources in LDMOS | 53 |

| 3.7    | Scaling of 1/f Noise in LDMOS                                  | 54 |

| 3.8    | Early Lifetime Prediction of LDMOS Devices                     | 55 |

| 3.9    | Conclusion                                                     | 57 |

| Chapte | er 4 LDMOS Low Frequency Noise Modeling                        | 58 |

| 4.1    | Introduction                                                   | 58 |

| 4.2    | 1/f Noise Theories for Conventional MOS Devices                | 58 |

| 4.3    | The Unified 1/f Noise Model                                    | 60 |

| 4.4    | Unified 1/f Noise Model Verification for LDMOS                 | 63 |

| 4.5    | Origin of Deviation from the Unified 1/f Noise Model           | 64 |

| 4.6    | Development of New LDMOS Noise Model                           | 66 |

| 4      | .6.1 1/f Noise in the Channel                                  | 67 |

| 4      | .6.2 1/f Noise in the Gate-Overlap Region                      | 68 |

| 4      | .6.3 Modification to the Existing Unified 1/f Noise Model      | 70 |

| 4      | .6.4 Proposed Functional Form of LDMOS Noise Model             | 72 |

| 4.7 LDI     | MOS Noise Model Implementation and Verification                     | 74  |

|-------------|---------------------------------------------------------------------|-----|

| 4.7.1       | Extraction of Noise Model Parameters                                | 74  |

| 4.7.2       | Number of Fitting Parameters In Noise Modeling                      | 78  |

| 4.7.3       | Comparison with Other Existing LDMOS Noise Models                   | 78  |

| 4.8 Effe    | ective Oxide Trap Density Variation with Stressing Time             | 79  |

| 4.9 Det     | ermination of Interface Trap Density                                | 82  |

| 4.10 Dor    | ninant 1/f Fluctuation Mechanism                                    | 83  |

| 4.11 Ori    | gin of Lifetime Degradation in LDMOS                                | 87  |

| 4.12 Dev    | viation from U-Shaped Oxide Trap Energy Distribution                | 88  |

| 4.13 Noi    | se in Saturation Region                                             | 90  |

| 4.14 Dis    | cussion and Summary                                                 | 91  |

| 4.15 Cor    | nclusions                                                           |     |

| Chapter 5 F | RTS Noise in Submicron Analog Devices                               |     |

| 5.1 Intr    | oduction                                                            |     |

| 5.2 Mot     | tivation for Investigation of Multilevel RTS in Analog Devices      |     |

| 5.3 Lite    | rature Review on Origin of Multilevel RTS                           | 97  |

| 5.4 RT      | S Analysis Methods                                                  |     |

| 5.4.1       | Time Domain Analysis                                                |     |

|             | 5.4.1.1. Mean Capture and Emission Times                            | 101 |

|             | 5.4.1.2. Determination of Trap Type and Distance from the Interface | 103 |

|             | 5.4.1.3. RTS Amplitude                                              | 106 |

| 5.4.2       | Frequency Domain Analysis                                           | 107 |

| 5.5 Exp     | perimental Setup                                                    | 109 |

| 5.5.1       | Device Specifications                                               | 109 |

| 5.5.2       | Time Domain Measurement                                             | 110 |

| 5.5.3 F      | requency Domain Noise Measurement                                | 111 |

|--------------|------------------------------------------------------------------|-----|

| 5.5.4 0      | C-V Measurements                                                 | 112 |

| 5.6 Sum      | mary                                                             | 114 |

| Chapter 6 RT | S Analysis and Extraction of Trap Properties                     | 115 |

| 6.1 Introd   | duction                                                          | 115 |

| 6.2 Deve     | elopment of an Algorithm for Multilevel RTS Analysis             | 115 |

| 6.2.1 C      | Comparison with Existing Analysis Techniques for Multilevel RTS  | 119 |

| 6.2.2 F      | Proposed Algorithm for Analyzing Multilevel RTS with Envelope    |     |

| т            | Fransitions                                                      | 120 |

| 6.2.3 A      | Applicability and Limitations of the Proposed Analysis Technique | 131 |

| 6.3 Extra    | action of Other Trap Properties                                  | 132 |

| 6.3.1 E      | Determination of Mean Capture and Emission Time                  | 132 |

| 6.3.2 E      | Determination of Trap Type                                       | 133 |

| 6.3.3 C      | Computation of Trap Energy and Location                          | 134 |

| 6.3.4 C      | Capture Cross-Sections                                           | 137 |

| 6.3.5 S      | Scattering Coefficient and Physical Origin of Multilevel RTS     | 138 |

| 6.4 Discu    | ussion and Summary                                               | 142 |

| 6.5 Conc     | clusions                                                         | 144 |

| Chapter 7 Co | onclusions and Summary                                           | 145 |

| Appendix A M | Nathcad Implementation of LDMOS Surface Potential                | 148 |

| Appendix B N | Natlab Program Code for Multilevel RTS Analysis                  | 150 |

| References   |                                                                  | 159 |

| Biographical | Information                                                      | 169 |

### List of Illustrations

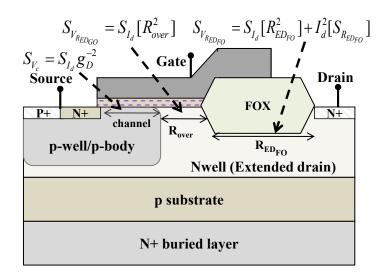

| Figure 1-1 Cross-sectional schematic for an LDMOS showing the channel, gate oxide             |

|-----------------------------------------------------------------------------------------------|

| overlap region and the extended drain drift regions 12                                        |

| Figure 1-2 A typical noise spectra in frequency domain with a Lorentzian fitting. The y-      |

| axis is arbitrarily scaled to a higher magnitude than the actual device noise                 |

| Cross-sectional schematic for an LDMOS showing the channel, gate oxide                        |

| overlap region and the extended drain drift regions                                           |

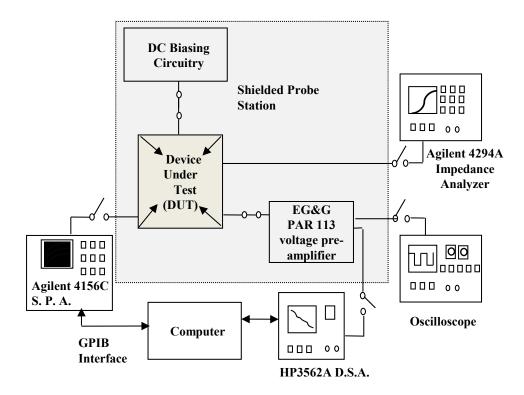

| Figure 2-1 A schematic representation showing the setup for 1/f noise, RTS noise, DC          |

| characteristics and C-V characteristics measurement23                                         |

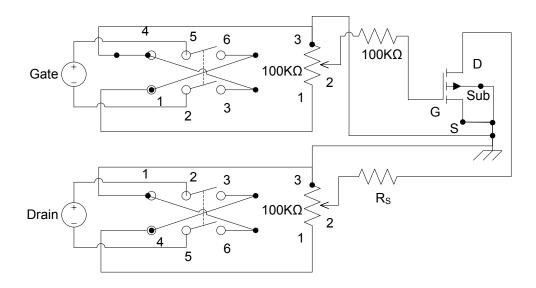

| Figure 2-2 A schematic representation of the DC biasing circuitry used in the                 |

| experimentation for both 1/f noise measurements in LDMOS, and RTS noise in                    |

| low voltage submicron analog transistors24                                                    |

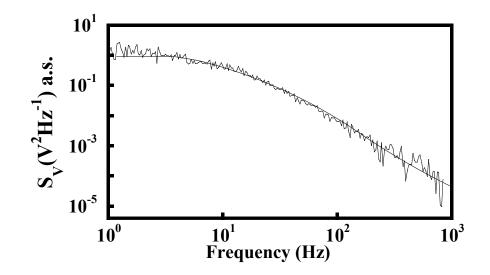

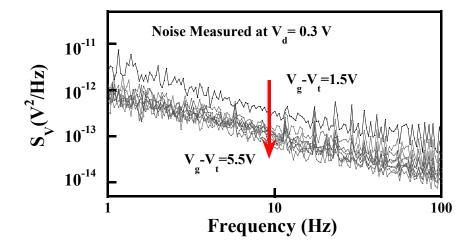

| Figure 2-3 Measured drain-source voltage noise power spectral density for a 30 V rated        |

| LDMOS at gate overdrive voltages of 1.5-5.5 V before stress24                                 |

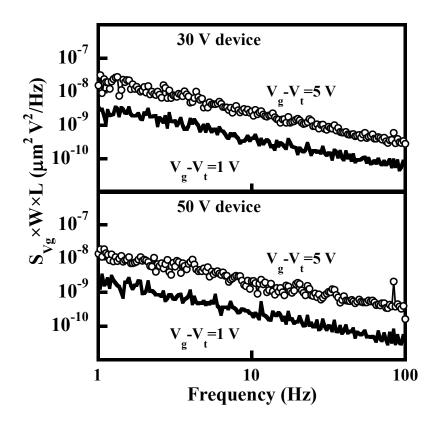

| Figure 2-4 Input referred noise for different LDMOS devices at $V_d$ =0.3 V before stressing. |

| The noise measurements were done for several more decades of frequencies                      |

| which are not shown here25                                                                    |

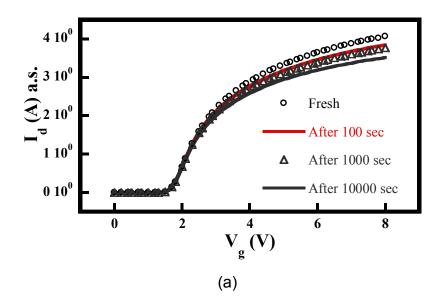

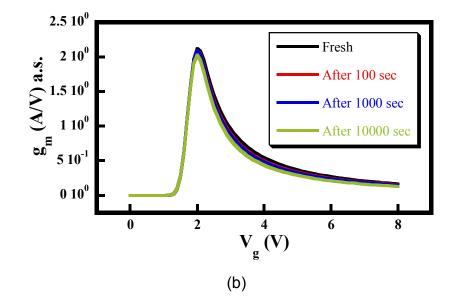

| Figure 2-5 (a) Measured drain current (b) transconductance as a function of gate voltage      |

| after different stressing times for a 40 V-rated device stressed at $V_{\rm d}$ =40 V and     |

| <i>V<sub>g</sub></i> =4 V                                                                     |

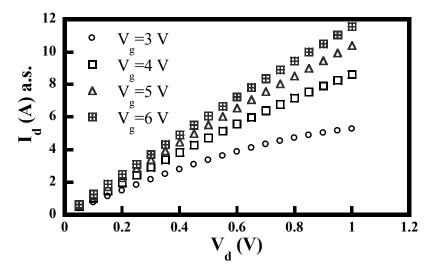

| Figure 2-6 A typical output characteristics for a 40 V NLDMOS device at room                  |

| temperature. Only linear region measurement results are shown at different gate               |

| biases                                                                                        |

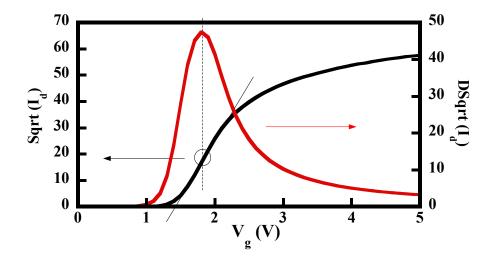

| Figure 2-7 An example of threshold voltage extraction method, which is applicable for                                    |

|--------------------------------------------------------------------------------------------------------------------------|

| both LDMOS and low voltage CMOS. A tangent is drawn on the Sqrt ( $I_d$ ) curve                                          |

| i.e. on $\left(\sqrt{I_d} ight)$ at the gate voltage where DSqrt ( $I_d$ ) i.e $\left(d\sqrt{I_d}\left/dV_g ight)$ is at |

| maximum, as highlighted by the circle on the vertical line. The intercept of the                                         |

| tangent on the x-axis identifies the threshold voltage. Y axes are arbitrary here                                        |

|                                                                                                                          |

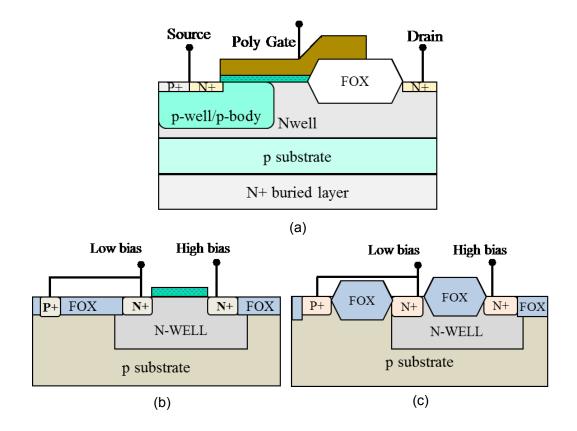

| Figure 2-8 Explaining the standalone DNWell resistors concept from an LDMOS. (a) The                                     |

| LDMOS itself. DNWell resistors are shown in (b) under the gate oxide, and in (c)                                         |

| under the field oxide                                                                                                    |

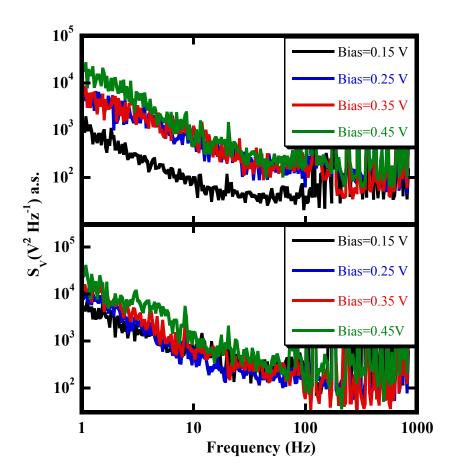

| Figure 2-9 Bulk resistance fluctuations in the form of PSD in a standalone DNWell                                        |

| resistor under the gate oxide (top) and that under the field oxide (bottom). Y axis                                      |

| is arbitrarily scaled                                                                                                    |

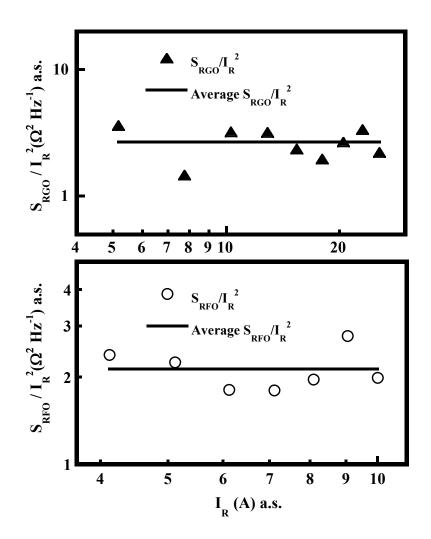

| Figure 2-10 Measured (top) $S_{R_{GO}}$ and (bottom) $S_{R_{FO}}$ as a function of resistor current ( $I_R$ )            |

| are shown after normalization with the current which were then arbitrarily scaled                                        |

|                                                                                                                          |

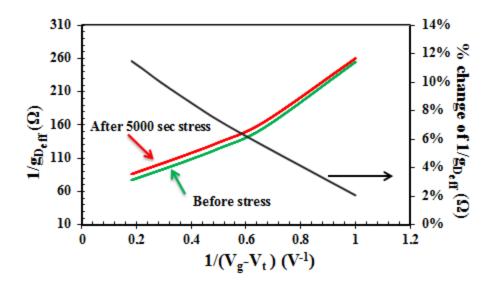

| Figure 3-1 Overall measured resistance of the LDMOS as a function of gate bias before                                    |

| and after 5,000 sec stress. The device was a 40 V transistor which was stressed                                          |

| at $V_g$ =4 V and $V_d$ =40 V. The resistance apparently remains unchanged with                                          |

| stress at low gate bias voltages                                                                                         |

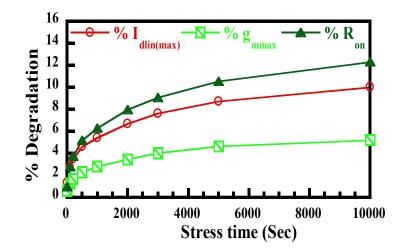

| Figure 3-2 DC degradation behavior for a 30 V device stressed at $V_g$ =5 V and $V_d$ =30 V                              |

| up to 10,000 sec. $R_{on}$ measured at $V_g$ =4.5 V and $V_d$ =0.3 V. The rate of initial                                |

| degradation (till 500 sec) is very sharp, and tends to behave sub-linearly                                               |

| thereafter                                                                                                               |

Figure 2-7 An example of threshold voltage extraction method, which is applicable for

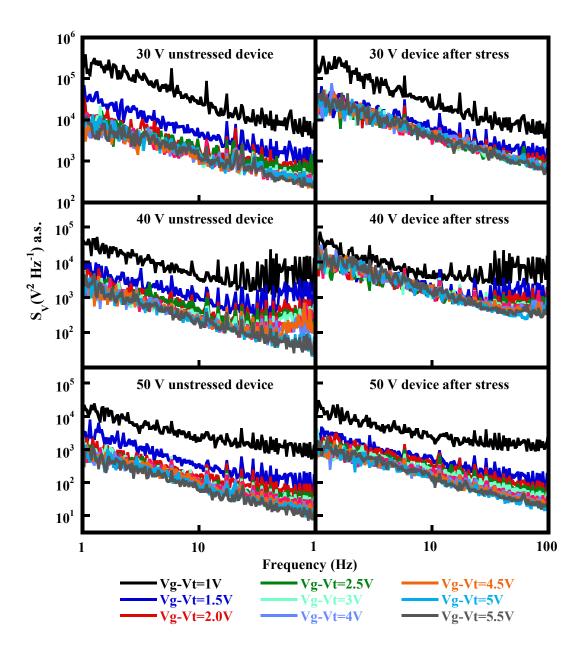

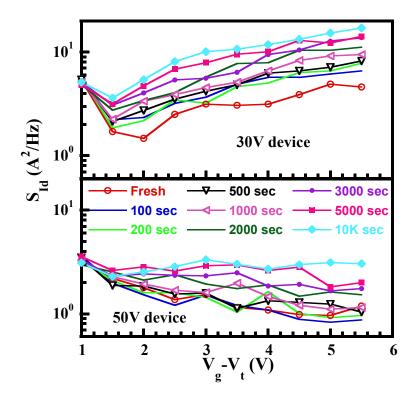

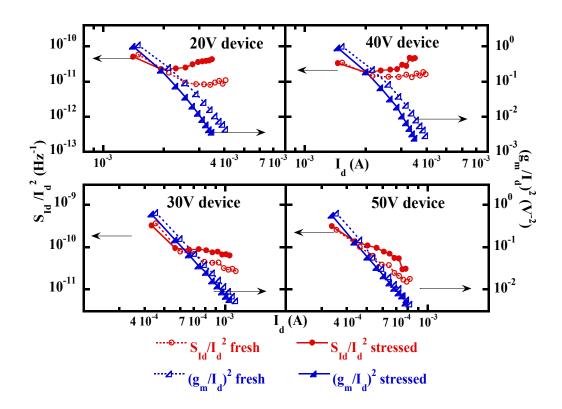

Figure 3-3 Noise power spectra for 30 V, 40 V and 50 V devices before and after 5,000 sec stress. Stress conditions were: for 30 V device  $V_g$  =5 V and  $V_d$  =30 V; for 40 V device  $V_g$  =4 V and  $V_d$  =40 V and for 50 V device  $V_g$  =5 V and  $V_d$  =53 V......39

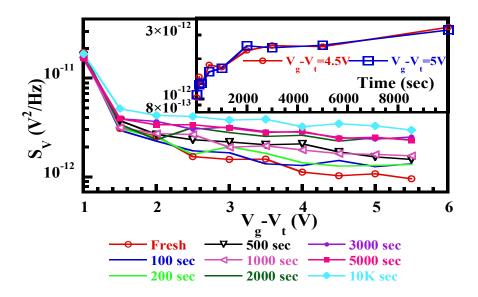

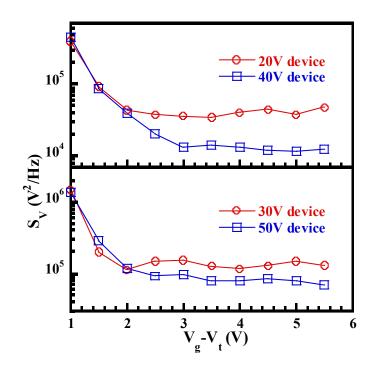

Figure 3-4 Measured noise PSD,  $S_V$  at 1 Hz for a 30 V device at different gate overdrive voltages, from fresh (unstressed) condition up to 10,000 sec stress in eight steps. The stressing condition was  $V_g$  =5 V and  $V_d$  =30 V. The inset shows  $S_V$  at 1 Hz

- as a function of stressing time ......40

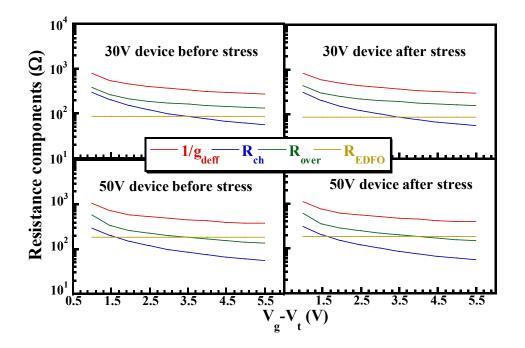

- Figure 3-8 Different resistance components as a function of gate voltage before and after stress. 30 V device was stressed at  $V_g$  =5 V and  $V_d$  =30 V while 50 V device was

| at $V_g$ =5 V and | V <sub>d</sub> =53 V4 | 4 |

|-------------------|-----------------------|---|

|-------------------|-----------------------|---|

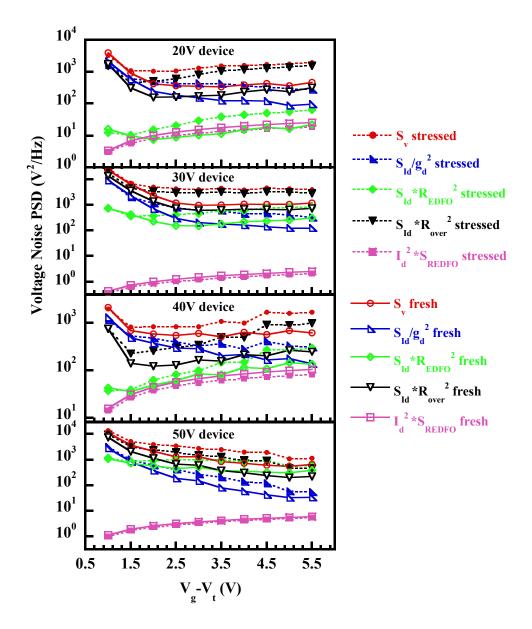

Figure 3-9 Different noise components contributing to the measured noise, before and after 5,000 sec stress. Open symbols-solid lines are for fresh devices and closed

| symbols-dotted lines are for stressed devices. The bulk fluctuation component                  |

|------------------------------------------------------------------------------------------------|

| $I_d^2 S_{R_{ED_{FO}}}$ is the lowest contributor. Y scale is arbitrary                        |

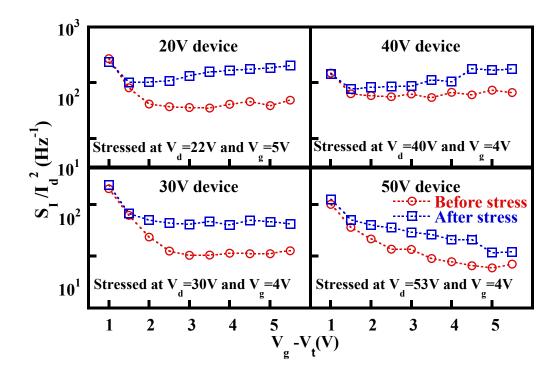

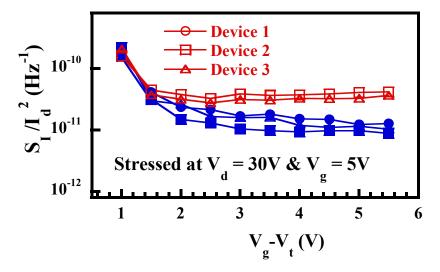

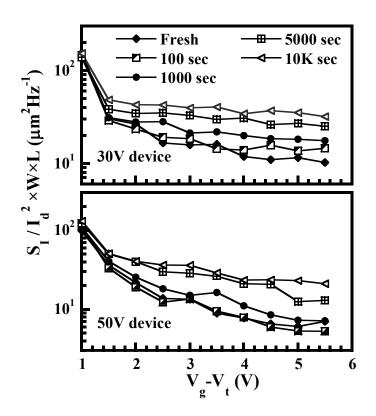

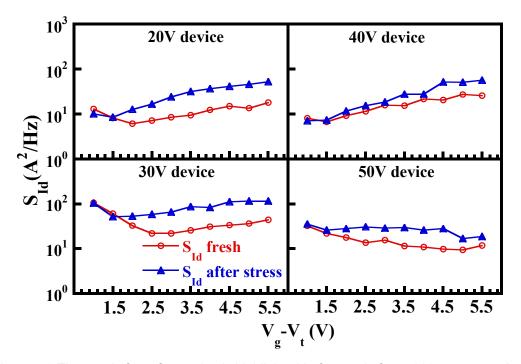

| Figure 3-10 Drain-current normalized $S_i$ as a function of gate bias in different rated       |

| devices at $V_d$ =0.3 V. Stressing conditions are: for 30 V device $V_g$ =5 V and $V_d$        |

| =30 V and for 50 V device $V_g$ =4 V and $V_d$ =53 V. Y axes are scaled to arbitrary           |

| magnitude level                                                                                |

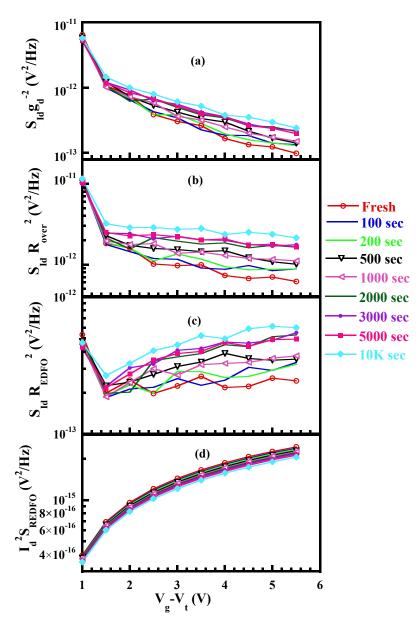

| Figure 3-11 Individual voltage noise components contributing to the measured noise in          |

| Fig. 3. Voltage noise PSD (a) in the channel, (b) in the extended drain under the              |

| gate oxide-overlap region (in accumulation), (c) due to fluctuation in the extended            |

| drain under the field oxide induced by $S_{I_d}$ , (d) due to bulk resistance fluctuations     |

| inherent in the extended drain under the field oxide of the LDMOS51                            |

| Figure 3-12 Extracted drain current noise PSD at 1 Hz for 30 V and 50 V devices from           |

| fresh (unstressed) condition up to 10,000 sec stress in steps. Y axis is arbitrarily           |

| scaled to the same magnitude level in both the devices. A trend of increase in                 |

| noise is found at high gate biases52                                                           |

| Figure 3-13 Effect of FOX size scaling on noise behavior in different LDMOS at their           |

| respective unstressed conditions. For two identical devices with the same                      |

| channel and overlap length, increase in the FOX length improves noise                          |

| performance (lowers the noise magnitude). The noise magnitude is arbitrarily                   |

| normalize54                                                                                    |

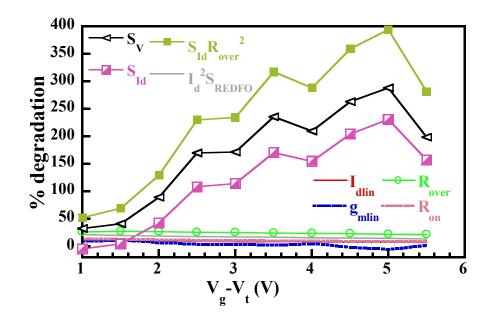

| Figure 3-14 Percentage DC and noise parameter degradation comparison after 10,000              |

| sec stress in a 50 V device at $V_g$ =4 V and $V_d$ =53 V. $S_v$ and $S_{\rm REDFO}$ represent |

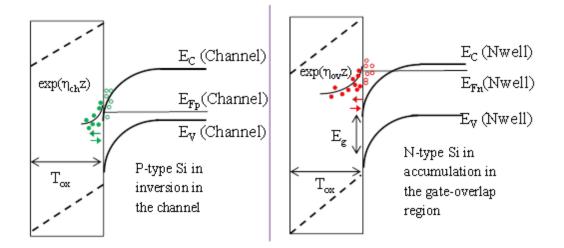

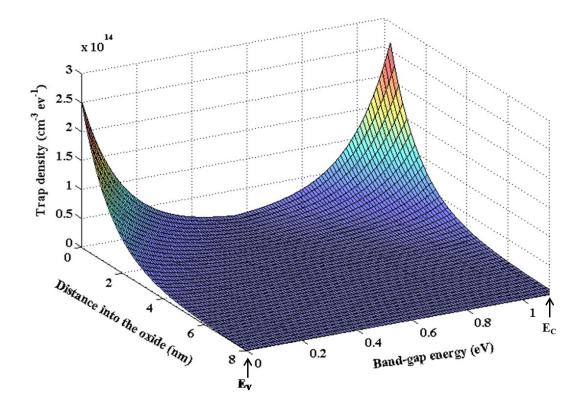

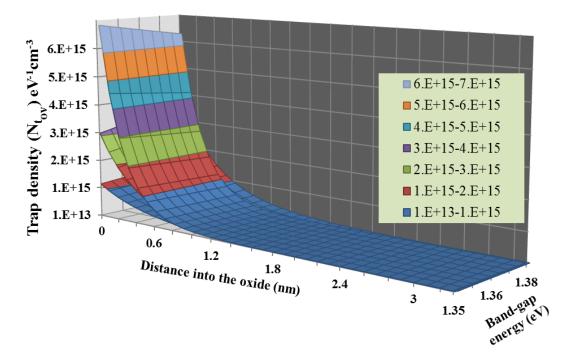

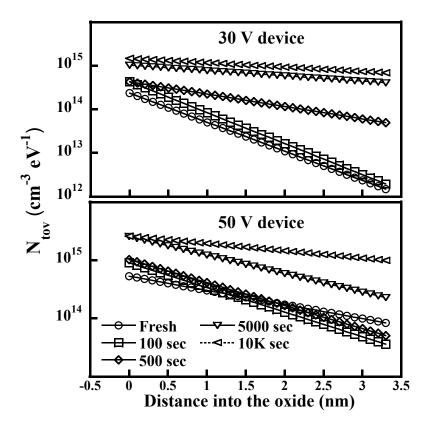

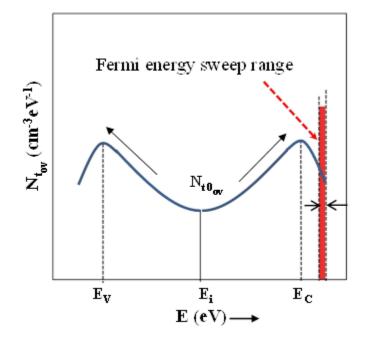

| Figure 4-4 A 3-D representation of the oxide trap density for the overlap region plotted as                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a function of energy and distance into the oxide using Equation (4.21). Energy is                                                                                          |

| measured from the valence band ( $E$ =0 at $E_{_V}$ of Si). $N_{_{ot_{ov}}}$ , $\eta_{_{ov}}$ , $\lambda_{_{ov}}$ ,and $\xi_{_{ov}}$ are                                   |

| chosen as $6.1 \times 10^{12}$ (cm <sup>-3</sup> eV <sup>-1</sup> ), -1.91×10 <sup>7</sup> cm <sup>-1</sup> , 7.3 eV <sup>-1</sup> and 7.3 eV <sup>-1</sup> , respectively |

| for this plot72                                                                                                                                                            |

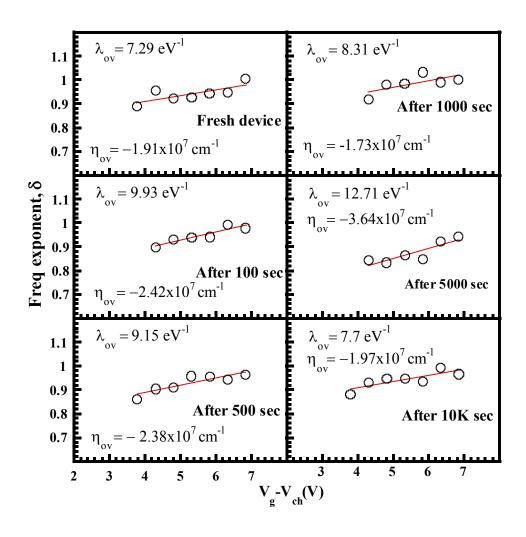

| Figure 4-5 The experimental values of frequency exponent $\delta$ plotted as a function of gate                                                                            |

| bias. The device was stressed at $V_g$ =4 V and $V_d$ =40 V for 10,000 sec. From a                                                                                         |

| linear fitting for each different stress time, $\lambda_{_{ov}}$ and $\eta_{_{ov}}$ parameters are obtained                                                                |

|                                                                                                                                                                            |

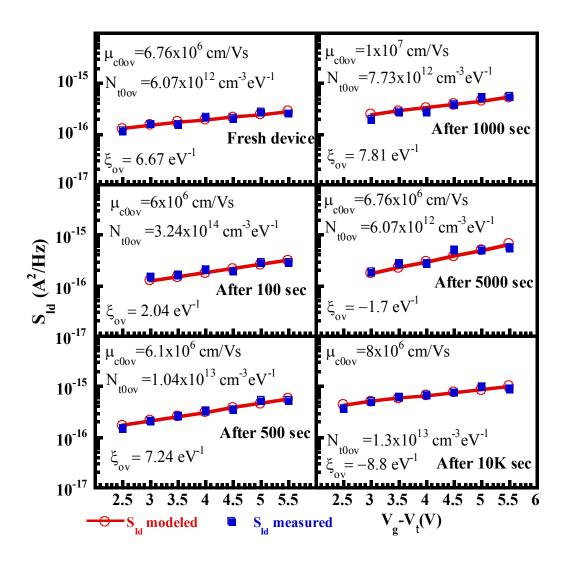

| Figure 4-6 Verification of the proposed noise model at high gate biases with the $S_{I_d}$ at 1                                                                            |

| Hz obtained experimentally. The data fitting presented here are for the same 40V                                                                                           |

| device stressed at $V_g$ =4 V and $V_d$ =40 V as in Figure 4-4. Other devices also                                                                                         |

| showed similar behavior77                                                                                                                                                  |

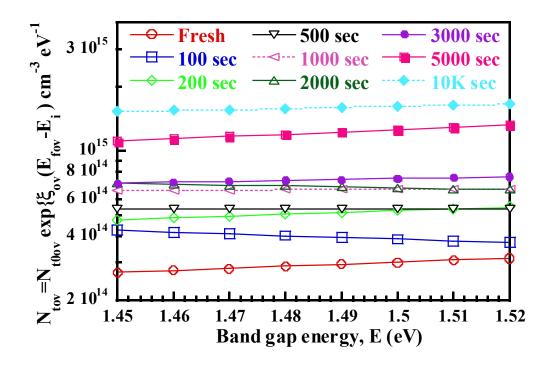

| Figure 4-7 Extracted trap density distribution at the Si-SiO <sub>2</sub> interface in the gate overlap                                                                    |

| obtained from the developed LDMOS noise model in a 30 V device stressed at                                                                                                 |

| $V_g$ =5 V and $V_d$ =30 V. The quasi-Fermi level sweeps from 1.47~1.50 eV range                                                                                           |

| above the valence band-edge and active traps are located within this range for                                                                                             |

| this device in the experimental conditions79                                                                                                                               |

| Figure 4-8 The extracted oxide trap density for a 40 V device stressed at $V_{\rm g}$ =4 V and $V_{\rm d}$                                                                 |

| =40 V before stress and after 500 sec and 3,000 sec stress within the measured                                                                                             |

| frequency range of 1-100 Hz. Horizontal axis shows the distance into the oxide                                                                                             |

| and depth axis shows the corresponding band-gap energy with respect to the                                                                                                 |

| valence-band edge. Trap density increases with stressing time for different-rated                                                                                          |

| LDMOS devices. For simplicity, the trap distribution after other stress times are                      |

|--------------------------------------------------------------------------------------------------------|

| not shown                                                                                              |

| Figure 4-9 Overlap region active oxide trap density at a constant energy of 1.471 eV from              |

| the Si valence band edge for two different devices. Stress conditions are                              |

| mentioned in Table 3-182                                                                               |

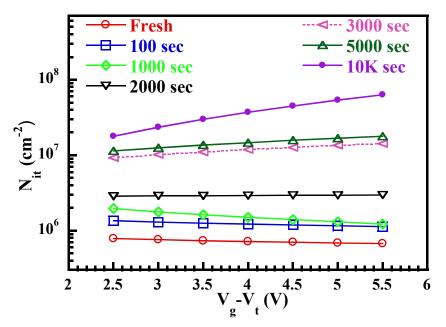

| Figure 4-10 Increasing trend of interface trap density with stressing time for a 30 V device           |

| stressed at $V_g$ =5 V and $V_d$ =30 V. Other devices also showed similar tendency of                  |

| trap variation                                                                                         |

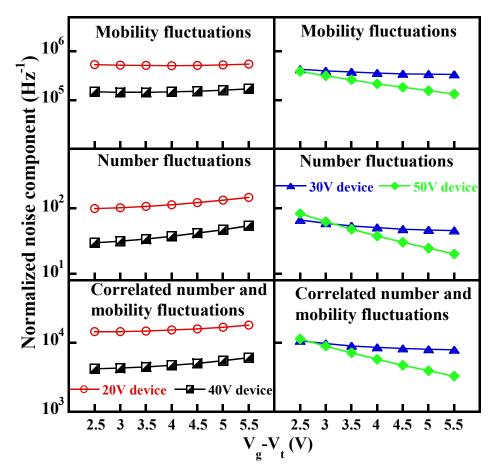

| Figure 4-11 Drain current normalized 1/f noise components of the measured drain current                |

| power spectral density as a function of gate overdrive voltages for fresh devices.                     |

| Y axis is arbitrarily scaled85                                                                         |

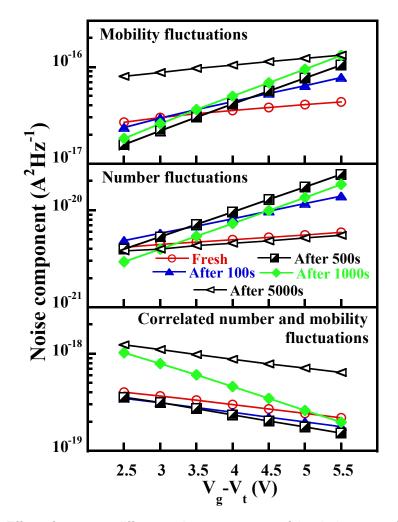

| Figure 4-12 Effect of stress on different noise components of the drain current fluctuation            |

| in a 30 V device stressed at $V_g$ =5 V and $V_d$ =30 V                                                |

| Figure 4-13 Exponential trap distribution profile at the Si-SiO <sub>2</sub> interface of gate-overlap |

| region. Due to strong accumulation, position of Fermi level and therefore the                          |

| active traps are above the conduction band edge of Si. $N_{_{t0_{ov}}}$ is the mid-gap trap            |

| density and $\xi_{ov}$ defines the energy dependence of the traps (eV <sup>-1</sup> ):                 |

| $N_{t_{ov}} = N_{t_{ov}} \exp\left[\zeta_{ov} \left(E_{f_{ov}} - E_{i}\right)\right] \dots 89$         |

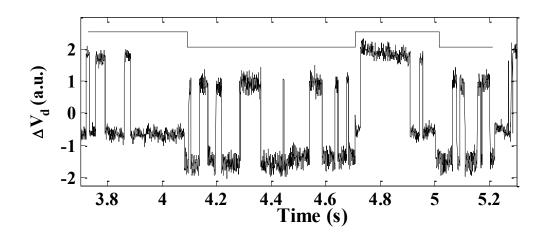

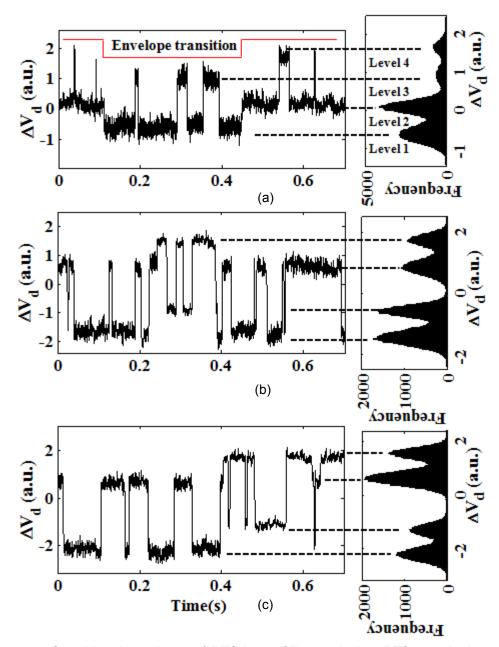

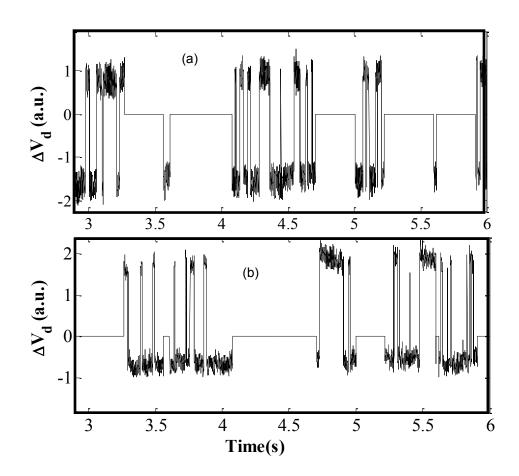

| Figure 5-1 A typical four level RTS obtained from the 1.5 V NMOS devices which showed                  |

| multilevel RTS. The RTS magnitudes are shown as the drain voltage fluctuation                          |

| ( $\Delta V_d$ ) in arbitrary units. The trend of the envelope switching is shown on the top           |

|                                                                                                        |

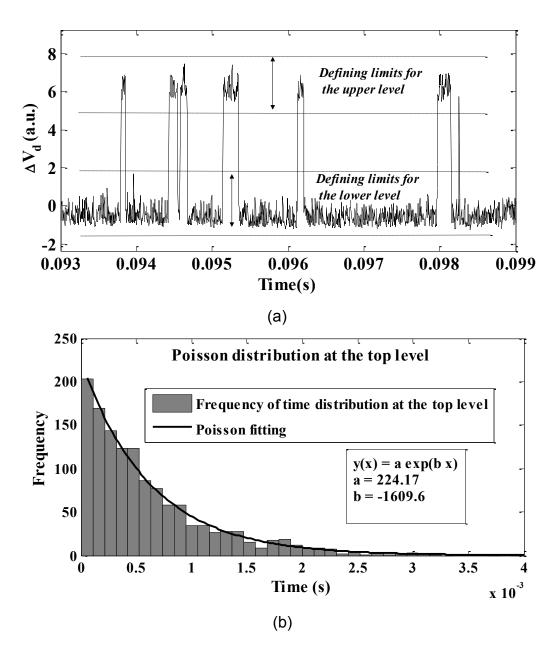

| Figure 5-2 Defining voltage limits for the top and bottom levels of the RTS. (b) Time      |

|--------------------------------------------------------------------------------------------|

| distribution of the top level along with a Poisson fitting. The RTS was measured           |

| at $V_g$ =0.702 V and $V_d$ =0.2 V                                                         |

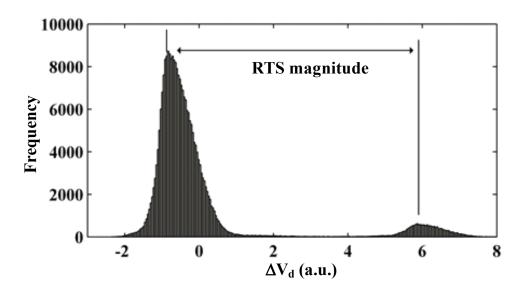

| Figure 5-3 Histogram for the amplitudes of the time domain RTS in Figure 5-2. Extraction   |

| method for the RTS magnitude is also shown as the difference of two maxima                 |

|                                                                                            |

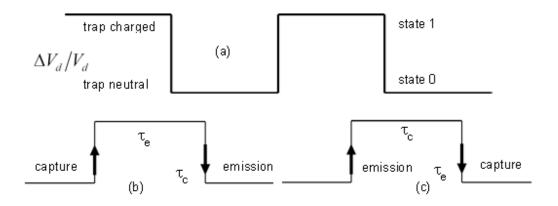

| Figure 5-4 Schematic identification of donor and acceptor traps for electron trapping-     |

| detrapping. (a) State 0 is where the trap is neutral and state 1 is after the trap is      |

| charged. Capture and emission process and corresponding mean capture and                   |

| emission times are shown for an (b) acceptor trap and (c) donor type trap 104              |

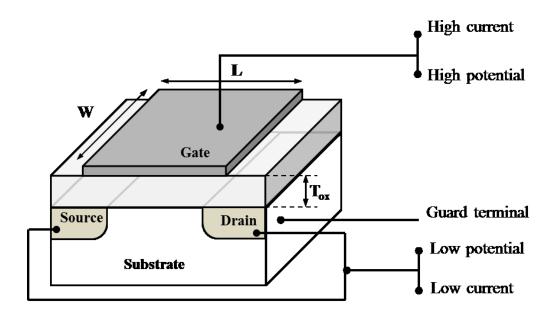

| Figure 5-5 Split C-V measurement set up schematic diagram 113                              |

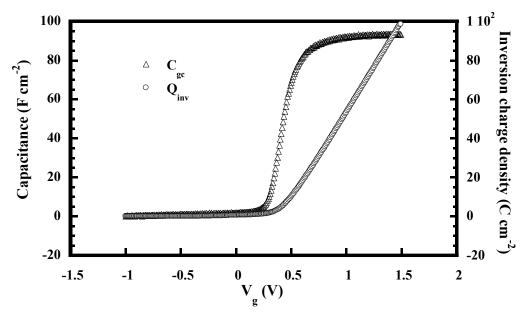

| Figure 5-6 C-V measurement result from an NMOS. The left axis shows the measured           |

| $C_{\rm gc}$ capacitance (after correcting for stray capacitance) and the right axis shows |

| the calculated inversion carrier density. Both the axes are scaled by an equal             |

| number                                                                                     |

| Figure 6-1 Gate bias dependence of RTS in an OT type device. RTS magnitudes are            |

| arbitrarily scaled. A small window of RTS are shown which were measured at $V_d$           |

| =0.4 V and (a) $V_g$ =0.7 V, (b) $V_g$ =0.8 V and (c) $V_g$ =0.9 V. For each time domain   |

| signal, the corresponding amplitude distribution is shown on the right as                  |

| histograms117                                                                              |

| Figure 6-2 A portion of RTS trace found in an ST type device. RTS magnitudes are           |

| arbitrarily scaled. RTS measured at $V_d$ =0.2 V and $V_g$ =0.682 V and the                |

| corresponding amplitude distribution is shown on the right as histogram118                 |

| Figure 6-3 Flow chart of the proposed algorithm121                                         |

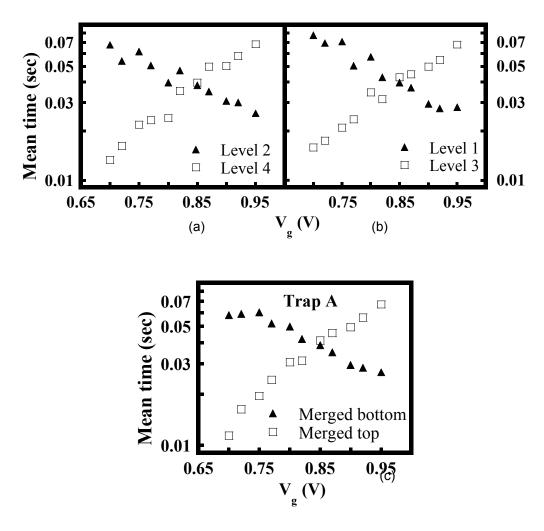

- - (b) switching within the upper envelope only for the OT device. RTS was

- measured at  $V_d$  =0.4 V and  $V_g$  =0.82 V......126

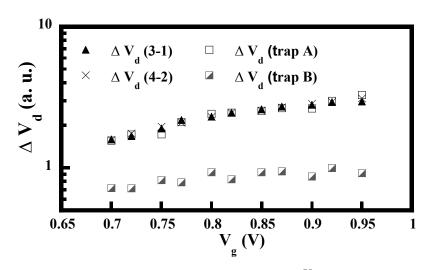

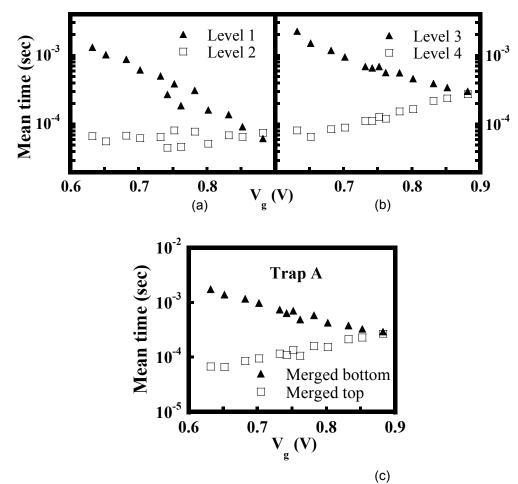

- Figure 6-9 After the envelopes are separated by the method as illustrated in Figure 6-8, mean times are shown (a) for levels 2 and 4 in the upper envelope and (b) for

| levels 1 and 3 in the lower envelope.(c) Mean times for trap A for the OT device           |

|--------------------------------------------------------------------------------------------|

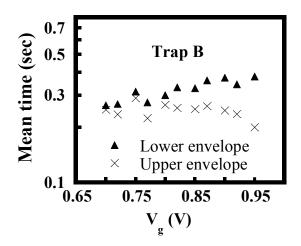

| as a function of gate bias. All the measurements were done at $V_d$ =0.4 V 128             |

| Figure 6-10 Mean times for trap B for the OT device as a function of gate bias. RTS were   |

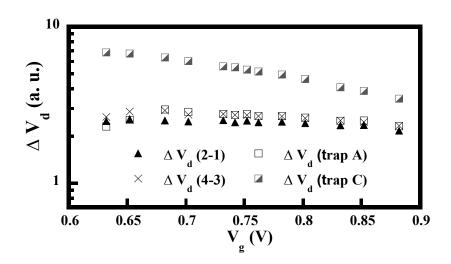

| measured at $V_d$ =0.4 V129                                                                |

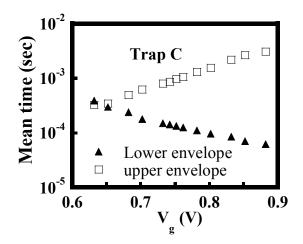

| Figure 6-11 Mean times as a function of gate bias (a) for levels 1 and 2 in the lower      |

| envelope and (b) for levels 3 and 4 in the upper envelope. (c) Mean times for trap         |

| A for the ST device as a function of gate bias. RTS were measured at $V_{\rm d}$ =0.2 V    |

|                                                                                            |

| Figure 6-12 Mean times for trap C for the ST device as was shown in Figure 6-2. RTS        |

| were measured at $V_d$ =0.2 V                                                              |

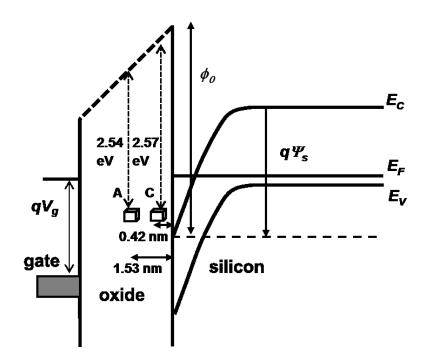

| Figure 6-13 Energy band diagram at the source end of the channel showing the position      |

| and energy for each trap for the ST type device. Both trap A and trap C are                |

| above the conduction band edge of Si in this case                                          |

| Figure 6-14 Energy band diagram at the source end of the channel for the OT type           |

| device. Trap A is located above the conduction band edge and trap B is near the            |

| valence band edge of Si135                                                                 |

| Figure 6-15 Determination of trap location into the oxide from capture to emission time    |

| ratio for (a) traps A and B in case of OT device (RTS measured at $V_d$ =0.4 V) and        |

| (b) traps A and C in case of ST type device (RTS measured at $V_d$ =0.2 V). The            |

| slope from each line gives the trap distance into the oxide                                |

| Figure 6-16 Relative surface electron mobility and drain voltage fluctuations for both the |

| traps plotted as a function of drain bias for the ST device. Measurements were             |

| taken at $V_g$ =0.702 V                                                                    |

|                                                                                            |

Figure 6-17 Dependence of screened Coulomb scattering coefficient on gate bias for the

| (a) OT type device (RTS measured at $V_d$ =0.4 V) and (b) ST type device (RTS |

|-------------------------------------------------------------------------------|

| measured at $V_d$ =0.2 V)141                                                  |

# List of Tables

| Table 2-1 Stressing Conditions for Different LDMOS Devices, Corresponding to Their    |    |

|---------------------------------------------------------------------------------------|----|

| Worst Degradation Condition, Respectively                                             | 29 |

| Table 3-1 Percentage Increase of Parameters at High Gate Biases After Stress. All the |    |

| Data are for the Measurements at $V_g - V_t$ =5.5 V and $V_d$ =0.3 V                  | 49 |

| Table 4-1 Spatial Distribution of Traps into the Oxide                                | 88 |

| Table 6-1 Summary of the Trap Properties for ST and OT Type Devices1                  | 41 |

### LIST OF SYMBOLS

| $C_{gc}$                             | gate to channel capacitance of MOSFET (Fcm <sup>-2</sup> )                |

|--------------------------------------|---------------------------------------------------------------------------|

| $C_{ox}$                             | gate oxide capacitance of MOSFET (Fcm <sup>-2</sup> )                     |

| Ε                                    | any energy level (eV)                                                     |

| $E_{C}$                              | energy at the conduction band edge (eV)                                   |

| $E_{fov}$                            | quasi Fermi energy for electron in the gate-overlap region (eV)           |

| $E_{f \max}$                         | energy at the effective maximum spatial distribution of active traps (eV) |

| $E_g$                                | bandgap energy (eV)                                                       |

| $E_i$                                | intrinsic Fermi level energy (eV)                                         |

| $E_{T}$                              | trap energy level (eV)                                                    |

| $E_{_F}$                             | Fermi energy level for electron (eV)                                      |

| $E_{_V}$                             | valence band edge (eV)                                                    |

| $E_x$                                | electric field along the channel (Vcm <sup>-1</sup> )                     |

| $\Delta E_B$                         | barrier energy for capture by a trap (eV)                                 |

| $\Delta E_{CT}$                      | trap binding energy (eV)                                                  |

| $E_{C_{ox}}$                         | oxide conduction band energy (eV)                                         |

| f                                    | frequency (Hz)                                                            |

| $f_t$                                | trap occupancy function                                                   |

| $g_{\scriptscriptstyle D}$           | conductance of the LDMOS channel (A $V^{-1}$ )                            |

| $g_{\scriptscriptstyle D_{e\!f\!f}}$ | LDMOS effective device conductance (A $V^{-1}$ )                          |

| $g_{\scriptscriptstyle m}$ | transconductance (A V <sup>-1</sup> )                                                 |

|----------------------------|---------------------------------------------------------------------------------------|

| $g_{m\max}$                | transconductance in the MOSFET linear operation region (A $V^{^{-1}}$ )               |

| h                          | Planck's constant (eV-s)                                                              |

| $I_d$                      | drain current (A)                                                                     |

| $I_{dlin}$                 | drain current in the MOSFET linear operation region (A)                               |

| $\Delta I_d$               | drain current fluctuations (V)                                                        |

| $I_g$                      | gate current (A)                                                                      |

| $I_R$                      | current in a DNWell resistor (A)                                                      |

| к                          | dielectric constant                                                                   |

| $k_{\scriptscriptstyle B}$ | Boltzmann's constant (eV K <sup>-1</sup> )                                            |

| $L_c$                      | MOSFET channel length (µm)                                                            |

| $L_D$                      | Debye length (cm)                                                                     |

| $L_{ov}$                   | length of the gate oxide-overlap region (µm)                                          |

| $L_{ED_{FO}}$              | length of the field oxide region (µm)                                                 |

| n                          | inversion charge carrier concentration (cm <sup>-3</sup> )                            |

| Ν                          | charge carrier density in semiconductor device (cm <sup>-2</sup> )                    |

| $N_c$                      | inversion carrier charge density in the channel (cm <sup>-2</sup> )                   |

| $N_{it_{ov}}$              | active interface trap density at the gate-overlap region $Si-SiO_2$ interface         |

|                            | (cm <sup>-2</sup> )                                                                   |

| $N_{ov}$                   | charge carrier density in accumulation in the gate-overlap region (cm <sup>-2</sup> ) |

| $N_{ot_c}$           | number of occupied traps per unit area in the gate oxide in the channel                             |

|----------------------|-----------------------------------------------------------------------------------------------------|

|                      | region (cm <sup>-2</sup> )                                                                          |

| $N_{ot_{ov}}$        | number of occupied traps per unit area in the gate-overlap region oxide                             |

|                      | (cm <sup>-2</sup> )                                                                                 |

| $N_{t_c}$            | oxide trap density in the channel (cm <sup>-3</sup> eV <sup>-1</sup> )                              |

| $N_{t_{ov}}$         | oxide trap density in the gate-overlap region (cm <sup>-3</sup> eV <sup>-1</sup> )                  |

| $N_{t0_{ov}}$        | mid band-gap trap density at the interface ( $z=0$ ) (cm <sup>-3</sup> eV <sup>-1</sup> )           |

| N(x)                 | inversion layer charge carrier density at distance x from the source                                |

|                      | (cm <sup>-2</sup> )                                                                                 |

| $\Delta N_c$         | charge carrier density in the channel within $W \Delta x_c$ area (cm <sup>-2</sup> )                |

| $\Delta N_{ov}$      | charge carrier density in the gate-overlap region within $W \Delta x_{ov}$ area (cm <sup>-2</sup> ) |

| $\Delta N_{ot_c}$    | number of occupied traps in the channel in $W \Delta x_c$ area                                      |

| $\Delta N_{ot_{ov}}$ | number of occupied traps in the gate oxide in $W \Delta x_{ov}$ area                                |

| q                    | elementary electronic charge (C)                                                                    |

| $Q_{ot_c}$           | insulator trap charge per unit area in the channel (Ccm <sup>-2</sup> )                             |

| $R_{ch}$             | LDMOS channel resistance ( $\Omega$ )                                                               |

| $R_{GO}$             | resistance of the standalone DNWell resistor having a gate oxide ( $\Omega$ )                       |

| $R_{FO}$             | resistance of the standalone DNWell resistor having a field oxide ( $\Omega$ )                      |

| R <sub>on</sub>      | on-resistance of LDMOS (Ω)                                                                          |

| $R_{_{ED_{GO}}}$     | bulk resistance in the extended drain under the gate oxide ( $\Omega$ )                             |

| $R_{_{ED_{FO}}}$                                        | bulk resistance in the extended drain under the field oxide $\left(\Omega\right)$                                                                          |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>over</sub>                                       | bulk resistance in the extended drain under the gate oxide ( $\Omega$ )                                                                                    |

| $R_{sp}$                                                | spreading resistance ( $\Omega$ )                                                                                                                          |

| $S_s$                                                   | subthreshold slope (V <sup>-1</sup> )                                                                                                                      |

| S                                                       | Huang-Rhys parameter                                                                                                                                       |

| $S_{I}$                                                 | drain current noise power spectral density (A <sup>2</sup> Hz <sup>-1</sup> )                                                                              |

| $S_{I_d}$                                               | current noise power spectral density generated at the Si-SiO $_{\rm 2}$ interface in                                                                       |

|                                                         | the channel and in the gate-overlap region $(A^2 Hz^{-1})$                                                                                                 |

| $S_{\Delta I_{d_c}}(x,f)$                               | power spectral density of the local current fluctuations in the channel ( $A^2$                                                                            |

|                                                         | Hz <sup>-1</sup> )                                                                                                                                         |

| $S_{\Delta I_{d_{ov}}}(x,f)$                            | power spectral density of the local current fluctuations in the gate oxide-<br>overlap ( $A^2 Hz^{-1}$ )                                                   |

| $S_{\Delta I_{dFO}}(x,f)$                               | power spectral density of the local current fluctuations in the field oxide region ( $A^2 Hz^{-1}$ )                                                       |

| $S_{\Delta N_{t_c}}(x,f)$                               | power spectral density of the mean square fluctuations in the trapped charge carriers over the area $W \Delta x_c$ (Hz <sup>-1</sup> )                     |

| $S_{\Delta N_{t_{ov}}}(x,f)$                            | power spectral density of the fluctuations in the number of the occupied traps over the area $W \Delta x_o$ in the gate-overlap region (Hz <sup>-1</sup> ) |

| $S_{\scriptscriptstyle R_{\scriptscriptstyle ED_{GO}}}$ | bulk resistance fluctuation under the gate oxide in the extended drain                                                                                     |

|                                                         | $(\Omega^2 Hz^{-1})$                                                                                                                                       |

| $S_{\scriptscriptstyle R_{\scriptscriptstyle ED_{\scriptscriptstyle FO}}}$ | bulk resistance fluctuation under the field oxide in the extended drain           |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|                                                                            | (Ω <sup>2</sup> Hz <sup>-1</sup> )                                                |

| $S_{\scriptscriptstyle R_{\scriptscriptstyle FO}}$                         | bulk resistance fluctuation in the standalone DNWell resistor under the           |

|                                                                            | field oxide ( $\Omega^2 Hz^{-1}$ )                                                |

| $S_{\scriptscriptstyle R_{\scriptscriptstyle GO}}$                         | bulk resistance fluctuation in the standalone DNWell resistor under the           |

|                                                                            | gate oxide ( $\Omega^2 Hz^{-1}$ )                                                 |

| $S_{_V}$                                                                   | drain voltage noise power spectral density (V <sup>2</sup> Hz <sup>-1</sup> )     |

| S <sub>Vc</sub>                                                            | voltage noise power spectral density from the channel ( $V^2 Hz^{-1}$ )           |

| $S_{_{V_{fb}}}$                                                            | noise power spectral density for flat-band voltage fluctuations ( $V^2 Hz^{-1}$ ) |

| $S_{_{V_{R_{EDFO}}}}$                                                      | voltage noise power spectral density from the extended drain under the            |

|                                                                            | field oxide region $(V^2 Hz^{-1})$                                                |

| $S_{_{V_{R_{ED_{GO}}}}}$                                                   | voltage noise power spectral density from the extended drain under the            |

|                                                                            | gate oxide region $(V^2 Hz^{-1})$                                                 |

| t <sub>inv</sub>                                                           | inversion layer thickness (nm)                                                    |

| Т                                                                          | temperature (K)                                                                   |

| $T_{ox}$                                                                   | thickness of gate oxide (nm)                                                      |

| $V_{ch}$                                                                   | voltage drop across the channel (V)                                               |

| $V_d$                                                                      | drain to source voltage (V)                                                       |

| $\Delta V_d$                                                               | magnitude of the drain voltage fluctuation (V)                                    |

| V <sub>FB</sub>                                                            | flat-band voltage (V)                                                             |

| $V_{g}$                                                                    | gate to source voltage (V)                                                        |

| $V_t$                   | threshold voltage (V)                                                      |

|-------------------------|----------------------------------------------------------------------------|

| $\Delta V_t$            | threshold voltage fluctuation (V)                                          |

| $\mathcal{V}_{th}$      | average thermal velocity for channel carriers (cms <sup>-1</sup> )         |

| W                       | MOSFET device width (µm)                                                   |

| x <sub>c</sub>          | distance from the source toward the drain in the channel (cm)              |

| X <sub>ov</sub>         | distance from the channel/drain junction in the gate-overlap region (cm)   |

| $x_{ED_{FO}}$           | distance from the bird's beak in the extended drain toward the drain       |

|                         | contact (cm)                                                               |

| $\Delta x_c$            | infinitesimal distance from the source toward the drain in the channel     |

|                         | (cm)                                                                       |

| $\Delta x_{ov}$         | infinitesimal distance from the channel/drain junction in the gate-overlap |

|                         | region (cm)                                                                |

| $\Delta x_{_{ED_{FO}}}$ | infinitesimal distance from the bird's beak in the extended drain toward   |

|                         | the drain contact (cm)                                                     |

| x                       | distance along the channel (cm)                                            |

| $x_{T}$                 | trap distance into the gate oxide from the $Si-SiO_2$ interface (nm)       |

| у                       | distance in the width dimension (cm)                                       |

| Ζ                       | distance into the gate dielectric (cm)                                     |

| Z <sub>max</sub>        | maximum spatial distribution of the active traps (nm)                      |

| $lpha_{_H}$             | Hooge's coefficient                                                        |

| $lpha_{c}$              | screened Coulomb scattering coefficient for the channel (Vs)               |

| $lpha_{ov}$                     | screened Coulomb scattering coefficient for the gate-overlap region (Vs)                                |

|---------------------------------|---------------------------------------------------------------------------------------------------------|

| δ                               | frequency exponent as in $1/f^{\delta}$                                                                 |

| $\phi_0$                        | electron affinity difference between Si and $SiO_2$ (eV)                                                |

| γ                               | carrier tunneling coefficient in the gate dielectric (cm <sup>-1</sup> )                                |

| $\boldsymbol{\mathcal{E}}_{0}$  | permittivity of free space (Fcm <sup>-1</sup> )                                                         |

| $\mathcal{E}_{Si}$              | permittivity of Si (Fcm <sup>-1</sup> )                                                                 |

| $\eta_{\scriptscriptstyle ov}$  | fitting parameter that determines dielectric trap density distribution as a                             |

|                                 | function of $z$ (cm <sup>-1</sup> )                                                                     |

| $\lambda_{_{ov}}$               | fitting parameter that defines the effect of dielectric band-bending on the                             |

|                                 | trap density that the tunneling electron encounters in the dielectric layer                             |

|                                 | (eV <sup>-1</sup> )                                                                                     |

| $\xi_{ov}$                      | fitting parameter for energy dependence of traps (eV <sup>-1</sup> )                                    |

| $\mu_c$                         | effective channel carrier mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> )                   |

| $\mu_{c0_{ov}}$                 | mobility fluctuation fitting parameter for the gate-overlap region (cmV <sup>-1</sup> s <sup>-1</sup> ) |

| $\mu_{e\!f\!f}$                 | effective carrier mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> )                           |

| $\mu_{\scriptscriptstyle latt}$ | mobility due to lattice scattering $(cm^2V^{-1}s^{-1})$                                                 |

| $\mu_{others}$                  | mobility due to other scattering phenomena $(cm^2V^{-1}s^{-1})$                                         |

| $\mu_{ov}$                      | effective carrier mobility in the gate-overlap region $(cm^2V^1s^{-1})$                                 |

| $\mu_{ox}$                      | mobility due to oxide charge scattering $(cm^2V^{-1}s^{-1})$                                            |

| $\sigma$                        | capture cross-section (cm <sup>2</sup> )                                                                |

| $\sigma_{_0}$                   | capture cross-section pre-factor (cm <sup>2</sup> )                                                     |

| τ                    | trapping time constant in the gate dielectric (s)       |

|----------------------|---------------------------------------------------------|

| $\overline{	au}_c$   | mean capture time (s)                                   |

| $\overline{	au}_{e}$ | mean emission time (s)                                  |

| $	au_o$              | trapping time constant at the Si-SiO $_2$ interface (s) |

| Ψ                    | Si surface potential at any position in the channel (V) |

| $\psi_s$             | Si surface potential at the $SiO_2$ interface (V)       |

| ω                    | angular frequency (radians s <sup>-1</sup> )            |

### Chapter 1

### Introduction

### 1.1 Preface and Motivation

This dissertation consists of two distinct sections. The first section is on the investigation of degradation in medium and high voltage lateral-double-diffused metal oxide semiconductor field-effect transistors (LDMOSFET) or the LDMOS. The second section discusses individual characterization of semiconductor/gate dielectric defects using multilevel random telegraph signal (RTS) noise in analog MOS transistors.

Carrier fluctuation leading to low frequency noise (LFN) degradation with electrical stressing can be a major reliability concern in integrated power devices [1], affecting the Si/SiO<sub>2</sub> interface and gate oxide reliability, and possibly impacting the device lifetime. In analog and mixed signal (AMS) applications, low frequency noise, also known as 1/f noise or flicker noise, serves as a figure-of-merit for the reliability as it often sets the sensitivity limit for the transistor or even for the circuit itself. It will be evident in this dissertation that LFN measurement is a powerful diagnostic tool because of its versatility, i.e can be applied to devices with smaller (submicron) to long channel dimensions or even to advanced high power devices, e.g. LDMOS. Although a lot of research is being carried out on the LDMOS breakdown voltage improvement, hot carrier degradation, safe operating area (SOA) and on-resistance optimization [2, 3], there had been no comprehensive study on LDMOS low frequency noise characteristics.

In this work, we investigated the LFN behavior of different voltage-rated reduced surface field (RESURF) LDMOS devices. We separated the individual resistance and 1/f noise components in different regions in this asymmetric device from the study of DC stress induced degradation. Although 1/f noise theory is well established and understood for conventional enhancement MOSFETs, there has been no such model proposed for

the 1/f noise in LDMOS transistors. Hence, a physics-based LDMOS noise model could be an essential addendum for analog integrated smart power circuit design. Such a model should accurately predict the LFN behavior for the devices before stress as well as after stress. Moreover, the model has to be generalized, i.e. applicable for LDMOS with different physical structure and design layout. This dissertation reports on our developed novel, physics-based 1/f noise model, which incorporates the trapping–detrapping of carriers in the proximity of Si/SiO<sub>2</sub> interfaces of the channel and the extended drain to account for the charge carrier number and mobility fluctuations. Stressing time dependence of the measured noise and individual noise components is described. The accuracy of the model is verified with respect to stressing time. Finally, we show that our model can predict the oxide trap density of LDMOS transistors and stress time dependence of the active traps.

Second part of this dissertation discusses methodology towards a measurementdriven RTS noise characterization to explore individual charge carrier capture/emission at the semiconductor/gate dielectric interface and in the dielectric that incorporates the effects of multiple traps/defects and their interaction. The goal/objective is to (1) devise a methodology for individually identifying and characterizing electrically active defects (traps), specifically carrier trapping and scattering states, in MOS structures; (2) extract each trap location, capture and emission time constants, capture cross-section, screened scattering coefficient and type (acceptor/donor); (3) develop analysis strategy for the above properties associated with the traps; and (4) find the physical origin of creation and activation of these defects as charge carrier traps. We obtained a four level RTS as a function of gate bias in different analog NMOS devices and developed a methodology to extract the number of traps along with the required trap properties.

### 1.2 Degradation in Scaled Down Analog MOSFETs

Amidst the quest for alternative technology, device and materials, semiconductor industry is still primarily dependent on conventional MOSFET performance and dimension scaling to enhance integrated circuit performance at a reduced operation cost. Since Moore's law was introduced in 1965, semiconductor industry is continuously increasing the transistor density by reducing the device dimensions (typically the gate length reduction). From the decade of 1960's, the gate length has been shrunk from hundreds of micrometers to less than 45 nm in modern day technology [4]. However, MOS technology was immediately associated with the limitations of short channel effects, right from the beginning of scaling [5]. Since then, device degradation has been observed in the form of, for example, increase in the subthreshold conduction, increase in sourcedrain resistance leading to decreased mobility, exponential increase in gate leakage current (tunneling) and off-state power consumption. To overcome this predicament, several alternative materials like high-k gate stack technology, use of III-V materials instead of Si as the substrate etc. have been explored to improve the device performance. However, amongst all of these alternatives, Si-SiO<sub>2</sub> substrate-dielectric technology has still sustained throughout the decades due to lower manufacturing cost and excellent device performance. Moreover, scaling in Si based technology is still possible by implementing novel architectures and by having proper reliability studies, especially in analog technologies. Reliability and degradation study is therefore, is of utmost importance in the arena of integrated scaled-down devices.

### 1.2.1 Scalability and Applications of High Voltage and Low Voltage Analog MOSFETs

In high power analog operations, for example in RF amplifiers (used in wireless radio base stations, aerospace or in defense broadcast), LDMOS is the most prevailing device technology, extensively utilized for frequencies ranging approximately from 10

MHz to 3.8 GHz [6]. From the industry point of view, LDMOS has significant advantages over Si bipolar transistors and devices made of alternative material (e.g. GaN) based high power amplifiers because of ruggedness, outstanding efficiency and high gain. On the other hand, necessity of low voltage analog transistors is realized in innumerable real life applications because of their continuous time operation and gain. For example, any digital to analog (D/A) or analog to digital (A/D) conversion to interface with outside world is fundamentally analog. The superiority of analog devices is evident in signal processing compared to their digital device counterpart, because of lower on-chip power consumption and the gain [7]. Hence, low voltage analog MOSFETs are incorporated with the integrated CMOS processes in semiconductor industries. It should be apparent that analog design and scalability is sometimes more challenging and difficult compared to well-defined lithography-driven digital processes, because of numerous complex fabrication processes as well as introduction of several alternate substrate materials involved in analog process to achieve the desired device performance. In addition to that, scaling of digital transistor significantly impacts analog device performance and analog device scalability as well in the long run [8]. This is because, with the same expected device performance constraint from analog devices after scaling, when the power supply voltage is scaled down for digital applications, threshold voltage for the analog devices does not scale down complementarily. A possible reason is the DIBL (drain induced barrier leakage) effect, which impacts directly on the gain and useful bandwidth of the output signal. Hence, it is well known in industry that "if you can do it in digital - don't do analog" [9].

#### 1.2.2 Degradation Study Techniques in Analog Transistors

So far we have discussed the scalability issues with high and low voltage analog MOSFETs. Due to the operating conditions of devices and ICs, devices are stressed or wear out over time, which results in various short term and long term performance and reliability problems. Some of the degradation effects are irreversible like dielectric breakdown, while some are recoverable (to some extent) in the off-state. Degradation due to dielectric breakdown can be instantaneous and catastrophic like electrostatic discharge (ESD) failure or can be due to trap build up in the oxide bulk or at the Si-SiO<sub>2</sub> interface over time, known as time dependent dielectric breakdown (TDDB). The defects cause gate leakage current through the dielectric, which either results in threshold voltage shift or in the permanent device failure because of dielectric breakdown. It should be apparent that the study of TDDB or ESD stress in MOSFETs is for most part, a destructive measurement approach. Charge pumping [10] is a well-known degradation analysis technique, by which spatial distribution of interface traps can be investigated. However, it entails prior knowledge of MOSFET doping and potential profiles, which may not be always accessible. Moreover, this experimental technique is usually unable to probe the damaged region deeper into the oxide and remains useful only in identifying shallow traps (close to the Si-oxide interface) in the middle of Si band gap [11]. This technique is not suitable in SOI devices, where there is usually no available contact from the bulk [12]. Since the device size will continue to shrink, the charge pumping current, which is proportional to gate area, will be difficult to measure. Negative and positive bias temperature instability (NBTI and PBTI) are other important degradation metrics for PMOS and NMOS, respectively in VLSI circuits. The electrical PBTI or NBTI stress (for example in  $V_g$  <0 in NBTI stress) on the transistor, generates traps at the Si-SiO<sub>2</sub> interface, which increases  $V_r$ , degrades channel mobility and increases parasitic

capacitances. However, the shortcoming of NBTI (or PBTI to some extent) is again not being a fully non-destructive approach, since the damage due to interface traps can sometimes be partially alleviated when the stress is reduced/ released [13].

Hot carrier injection (HCI), is another severe degradation mechanism that causes defect generation in the dielectric and also at the Si–SiO<sub>2</sub> interface near the drain side due to carrier heating resulting into impact ionization. Unlike NBTI/PBTI stress, HCI causes faster degradation in the form of  $V_t$  shift, impedes high frequency switching and reduces the device performance drastically and more importantly, the recovery in HCI is sometimes impossible. Therefore, an alternative technique is essential to investigate the analog device degradation in a non-destructive approach.

#### 1.3 Noise in Semiconductor Devices

Electronic 'noise' in solid state devices refers to the random voltage, current or resistance fluctuations. This is a stochastic process where the metric or characteristic under observation changes randomly over time. An example is the low frequency noise, whose mean value and the standard deviation are constant when calculated at different time intervals (hence LFN is a stochastic 'stationary' phenomena). Generally, it occurs due to the presence of localized defects in microstructures (whether it is a MOSFET, BJT or diode etc.), regardless of the device dimensions, albeit electrical noise does not necessitate the presence of physical defects in a solid state device. In the following subsections, four most significant noise sources in electronic devices will be addressed. Among them, *1/f* noise and RTS noise are the topics of discussion in this dissertation.

#### 1.3.1 Dominant Low Frequency Noise Sources: RTS Noise, G-R Noise and 1/f Noise

RTS noise in solid state devices are observed in small area transistors when the charge transport is governed by the charging and discharging of defects resulting in discrete random voltage or current fluctuations with time. This is sometimes referred to as popcorn or burst noise (a term used before 1980's). If only an active trap is present around the Fermi level (within about  $3k_{B}T$  to be precise), a simple two level RTS will evolve. This is mostly observed by authors in submicron MOSFETs at room temperature and at lower temperatures [14-16]. It is also likely to have several trapping centers to be active at the same time to generate multi-level RTS, which is the superposition of the random fluctuations from all of the traps. Systematic analysis of RTS can provide important information about the properties of each defect like trap type, physical location and capture cross-section. With RTS measurement, it is possible to identify both processinduced traps and those introduced after the device is stressed. RTS noise due to process-induced traps was first observed by Kandiah and Whiting in 1978 [17]. They are generated from the imperfections during device fabrication, and are therefore, dependent on the foundry processing. Hot carrier stress induced trap was reported to be more effective in trapping-detrapping compared to process induced traps by Fang et al. in 1991 [18]. With the aggressive downsizing of MOS technology, RTS noise is expected to dominate as a device design concern; not only for analog devices, but also in digital memory devices like Static Random Access Memory (SRAM), Ferroelectric RAM (FRAM) or Dynamic RAM (DRAM) devices. According to [4], at 22-nm SRAM technology node and beyond, RTS noise will be large enough to increase the variability of noise sources above the minimum supply voltage limitation of scaling. This might then make the future design margin or scaling probability to be negative for SRAM [4].

7

Generation-recombination (G-R) noise has distinct similarity to RTS noise as both of them show Lorentzian power spectral density (PSD) in frequency domain. In semiconductors, it originates due to random capture and emission of charge carriers from conduction or valence band to the defect state, analogous to RTS noise case. This G-R noise therefore, can be observed as a superposition of several RTS noise from one or more traps with identical time constants. In relatively large devices, RTS noise can be part of G-R noise, which would be indistinguishable from G-R noise and also 1/f noise component will be observed at the same time in real time domain measurement [11]. Just like RTS noise, G-R noise is also bias and temperature sensitive [11]. The maximum G-R noise occurs for a defect center with energy at the Fermi level, resulting in equal capture and emission time constants, and the noise spectrum becomes [19]:

$$S_V(f) = 4\overline{\Delta N^2} \frac{\tau^2}{1 + (2\pi f\tau)^2}$$

(1.1)

where *N* is the charge carrier density and  $\tau$  is the characteristic time constant for the charges. This reveals that the G-R noise is constant at low frequencies and falls off after the corner frequency (*f*) at  $1/f^2$  rate. There is also another noise source, known as  $1/f^2$  noise, whose frequency exponent is close to 2 (in fact in the range of 1.8–2.2) and the physical mechanism for this type of noise is different than that for 1/f noise [20]. An example is the electromigration in metal lines.

On the other hand, if the number of active traps is high, the superposition of the random telegraph signals (Lorentzian's) from individual defect states in the gate-oxide will result in 1/f noise. This means that both 1/f noise and RTS noise have the same physical origin in MOSFETs [15]. However, 1/f noise is more universal i.e. can be observed in any metal, semimetal, BJT, diode or even in organic systems (of course, the physical origin

will be different in those systems). As the name suggests, 1/f noise has a power spectral density of  $1/f^{\delta}$  with  $\delta$  is typically unity or ranges from 0.7-1.4. At low frequencies in relatively larger area devices, 1/f noise has the most significant impact in generating device electrical noise. By means of LFN measurements, localized defects can be probed more sensitively than using other electrical characterization tools [12]. Nevertheless, RTS and 1/f noise are the two most significant noise sources in transistors and hence, we will focus on these two topics in the subsequent parts of this dissertation.

## 1.3.2 Other Noise Sources: Thermal Noise and Shot Noise

In any electronic device, there are two sources of electrical noise: intrinsic noise and extrinsic noise [12]. Thermal noise and shot noise are the most important examples of intrinsic noise in electron devices. This kind of noise can be observed within a device even without the presence of defects or any traps [12]. On the other hand, extrinsic noise sources need the electrical conduction mechanism by the charge carriers to have communication with physical defects. Generation recombination noise, RTS and *1/f* noise are the examples of such noise sources, as discussed above.

## Thermal noise

Thermal noise, also known as Johnson noise or Nyquist noise is present in any conducting material (metal or semiconductor) operating at above absolute zero temperature. This is generated due to thermal agitation of charge carriers, even without the presence of external bias. The power spectral density for thermal noise is defined as:

$$S_V(f) = 4k_B T R \tag{1.2}$$

where R is the device resistance. Thermal noise is generally independent of frequencies, except at extremely high frequencies, where a quantum correction factor restricts the thermal noise power from becoming theoretically infinite [11], and the thermal noise is then expressed as:

$$S_{V}(f) = 4 \frac{hf}{e^{hf/k_{B}T} - 1}R$$

(1.3)

where *h* is the Planck's constant and *f* is the frequency. In the typical frequency range for noise measurement  $hf \ll k_B T$ , and we can simply consider Equation (1.2) to be applicable. Thermal noise therefore, appears as a plateau in the power spectrum.

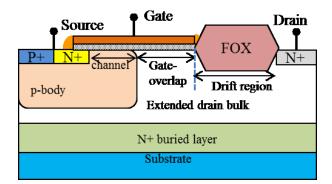

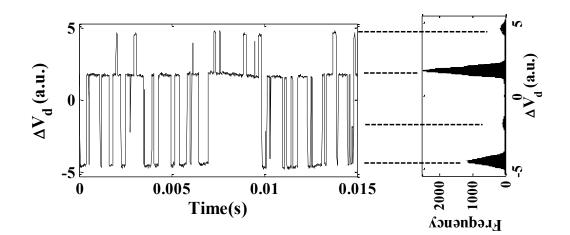

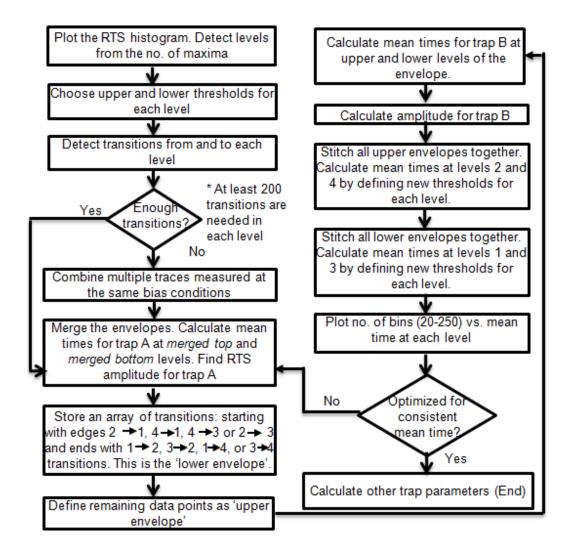

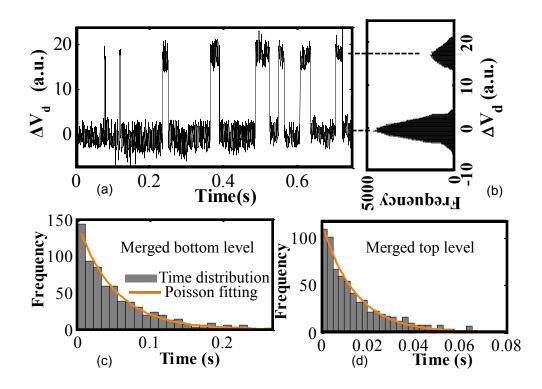

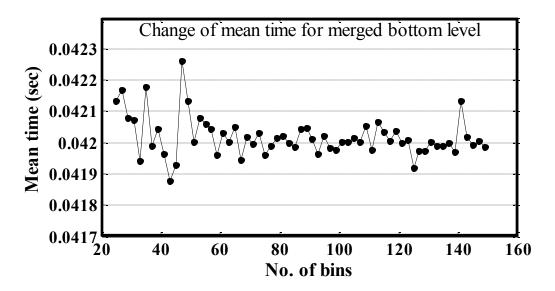

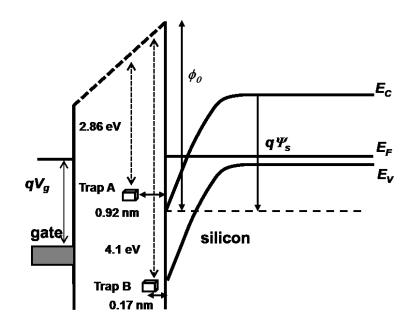

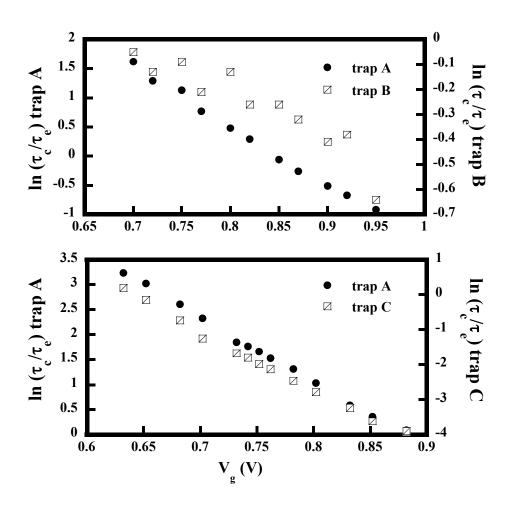

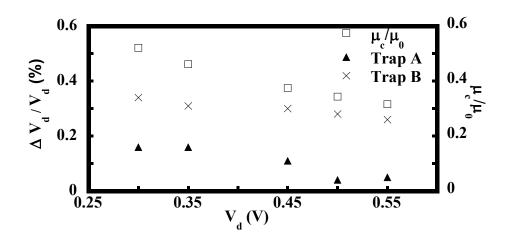

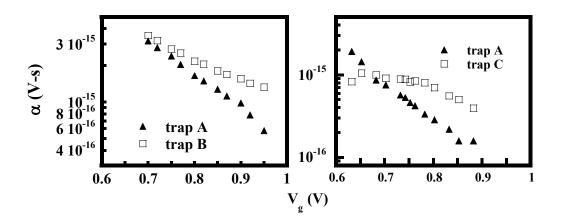

### Shot noise