# RELIABILITY OF ADVANCED DIELECTRICS IN GATE OXIDE AND DEVICE LEVEL PACKAGING IN MEMS

by

# MOHAMMAD SHAHRIAR RAHMAN

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT ARLINGTON

December 2009

Copyright © by Mohammad Shahriar Rahman 2009

All Rights Reserved

#### **ACKNOWLEDGEMENTS**

I would like to express my deepest gratitude to my advisor, Prof. Zeynep Çelik-Butler. She has been a great advisor, a strong motivator, and a great inspiration to my work. I feel very fortunate to have had her as my Ph.D. advisor, to have had the opportunity to work with her and to have had her helpful advice for the last four years. She has been always available and willing to have a discussion, even on her busiest day. I would also like to thank my co-supervisor Prof. Donald Butler for the helpful directions in RF MEMS project, and the committee members Professors J.-C. Chiao, Dereje Agonafer, Samir Igbal and Dr. Sergio Pacheco. I would like to specifically thank Dr. Pacheco for serving in my committee. He was my mentor in RF MEMS project from Freescale Semiconductor. I am honored to work with him in this project. I want to acknowledge my past and present colleagues Dr. Aameer, Dr. Rana, Dr. Tanvir, Dr. Murali, Dr. Siva, Erkin, Suraj, Bhargav, Gaviraj and Rohit in Noise and Sensor Lab for their help and useful discussion. My special thanks to Dr. Tanvir Morshed for training me on noise measurement setup and Dr. Murali Chitteboyina for training me on cleanroom equipments and RF characterizations. The cleanroom staff at the University of Texas at Arlington has been very helpful and I would like to make a special mention of Dennis Bueno, Eduardo Maldonado and Dr. Fatima Amir.

I would like to express my deepest appreciation to my dear parents, Matiur Rahman and Shirin Rahman and my brothers Rubaiyat Rahman and Tanzim Rahman. They have been my greatest motivators. I thank them for their endless love and constant support; no matter where they are, they are close to my heart. Last, but for certain not least, thanks to my wife Shafina Rahman for her love, caring and unending support in everything that concerns my life.

November 10, 2009

#### ABSTRACT

# RELIABILITY OF ADVANCED DIELECTRICS IN GATE OXIDE AND DEVICE LEVEL

# PACKAGING IN MEMS

Mohammad Shahriar Rahman, PhD

The University of Texas at Arlington, 2009

Supervising Professor: Zeynep Celik-Butler

The focus of this work is to study the feasibility, reliability and applicability of advanced dielectrics in both Metal Oxide Semiconductor Field Effect Transistor (MOSFET) gate oxide and device level packaging for Microelectromechanical Systems (MEMS). The scaling of silicon based MOSFET is approaching physical limits imposed by atomic structure. This continuous scaling trend of complementary MOSFET technologies introduces new challenges relating to power, heat and device behavior. To overcome the power dissipation and heating problems arising from gate leakage, high dielectric constant (high-k) materials are proposed. Hafnium

based high-k dielectric layers and metal gate electrodes have been extensively investigated as

alternative gate materials. Successful incorporation of these materials into the MOSFET gate

stack with minimum feature size of 45nm has recently been reported.

Here, the low frequency noise characteristics of MOSFETs with differently nitrided HfSiO gate dielectric materials are studied. To evaluate the high-k MOSFET performance using low frequency noise as a characterization tool, the devices were also subjected to different stress

iv

induced degradation. Device performance of differently nitrided samples is also compared with

the control, pure HfSiO MOSFET sample. This work reports, for the first time, the low frequency noise performance of 2nm high-k gate dielectric material for the sub 45nm technology node.

The advantages of the MEMS packaging approach described here compared to other MEMS packaging techniques are that it is a CMOS compatible low temperature method. Different MEMS devices can be used for vacuum encapsulation using this method. It does not require a high temperature deposition and etching of sacrificial materials and is stiction-free. Removal of the sacrificial layer is performed through openings, called trench cuts, and later the openings are sealed for encapsulation.

For the MEMS packaging application, Al<sub>2</sub>O<sub>3</sub> (alumina) is chosen as a resonator beam and sealing material. The primary reasons for choosing this material is due to the hard and stiff material property with high Young's modulus. Alumina can also be used in high temperature and under harsh environment. On top of that, packages with optical transparent window can be made with this material. For the first time this work was reported the use of alumina as a packaging material in MEMS.

Extensive RF and reliability measurements were performed on the packaged resonators including evaluation of the package permeability, stress and cavity pressure. Long term and accelerated life testing on the packaged resonators indicated the robustness of the package.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                      | iii     |

|-------------------------------------------------------|---------|

| ABSTRACT                                              | iv      |

| LIST OF ILLUSTRATIONS                                 | ix      |

| LIST OF TABLES                                        | xiv     |

| LIST OF SYMBOLS                                       | xv      |

| Chapter                                               | Page    |

| 1. INTRODUCTION                                       | 1       |

| 1.1 Introduction                                      | 1       |

| 1.2 Trends in Semiconductor and Device Scale          | 1       |

| 1.2.1 High-k Materials and Noise Modeling             | 2       |

| 1.3 Device Level Packaging in MEMS                    | 4       |

| 1.3.1 Cost Effective RF MEMS Packaging                | 5       |

| 1.4 Summary                                           | 7       |

| 2. NOISE AND CARRIER MOBILITY MEASUREMENTS            | 11      |

| 2.1 Introduction                                      | 11      |

| 2.2 Device Specification                              | 10      |

| 2.3 Measurement Setup                                 | 12      |

| 2.3.1 DC Characteristics Background and Measurements. | 12      |

| 2.3.2 Charge Density and Mobility Extraction          | 15      |

| 2.3.3 Low Frequency Noise Background and Measuremer   | nts20   |

| 2.3.4 Hot Carrier Stress Background and Measurements  | 25      |

| 2.3.5 Constant Voltage Stress Background and Measurem | nents26 |

|       | 2.4 Summary                                                                        | 28 |

|-------|------------------------------------------------------------------------------------|----|

| 3. NO | DISE RESULTS AND DISCUSSION                                                        | 29 |

|       | 3.1 Introduction                                                                   | 29 |

|       | 3.2 General MOSFET Noise Theory                                                    | 30 |

|       | 3.3 1/f Noise Model in MOSFET Device                                               | 37 |

|       | 3.3.1 1/f Noise in Conventional (SiO <sub>2</sub> ) Gate Oxide MOSFET              | 37 |

|       | 3.3.2 1/f Noise in High-k Gate Oxide MOSFET                                        | 45 |

|       | 3.4 Results and Discussion                                                         | 50 |

|       | 3.4.1 Effect of Nitridation on Low Frequency Noise                                 | 50 |

|       | 3.4.2 Effect of Nitridation on HCS and CVS Induced Low Frequency Noise Degradation | 57 |

|       | 3.5 Summary                                                                        | 68 |

| 4. D  | EVELOPMENT OF RF MEMS PACKAGING                                                    | 69 |

|       | 4.1 Introduction                                                                   | 69 |

|       | 4.2 Motivation and Approach                                                        | 70 |

|       | 4.2.1 MEMS Wafer Level Packaging Technology Review                                 | 70 |

|       | 4.3 Vacuum Cavity Package                                                          | 73 |

|       | 4.3.1 Design and Fabrication of Vacuum Package Only                                | 73 |

|       | 4.4 RF MEMS Resonator                                                              | 76 |

|       | 4.4.1 Design and Fabrication                                                       | 76 |

|       | 4.5 Integration of The Vacuum Package Cavity with MEMS Resonator                   | 78 |

|       | 4.6 Summary                                                                        | 85 |

| 5. RF | MEMS PACKAGE ASSESSMENT AND DISCUSSION                                             | 86 |

|       | 5.1 Introduction                                                                   | 86 |

|       | 5.2 Overmolding of Vacuum Cavity Package                                           | 87 |

|       | 5.3 DC and RF Characteristics of MEMS Resonators                                   | 89 |

|       | 5.3.1 DC and RF Characterization Measurement Setup                                 | 89 |

| 5.3.2 RF Characteristics of Packaged and Unpackaged Resonator | 90 |

|---------------------------------------------------------------|----|

| 5.3.3 Integrity of the Resonator inside the Package           | 93 |

| 5.4 Long Term and Accelerated Life Testing                    | 93 |

| 5.4.1 Effect of External Pressure on Packaged Resonator       | 94 |

| 5.4.2 Extended Hour RF Characterization                       | 94 |

| 5.4.3 High Temperature Operating Life (HTOL) Experiment       | 95 |

| 5.4.4 High Temperature Storage Life (HTSL) Experiment         | 99 |

| 5.4.5 Temperature Cycling1                                    | 00 |

| 5.4.6 Accelerated Humidity and Drop Test1                     | 01 |

| 5.5 Summary1                                                  | 04 |

| 6. SUMMARY AND CONCLUSION1                                    | 05 |

| APPENDIX                                                      |    |

| A. SELF PACKAGED MEMS RESONATOR FABRICATION PROCESS FLOW1     | 80 |

| REFERENCES1                                                   | 16 |

| BIOGRAPHICAL INFORMATION1                                     | 26 |

# LIST OF ILLUSTRATIONS

| Figure                                                                                                                                                   | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

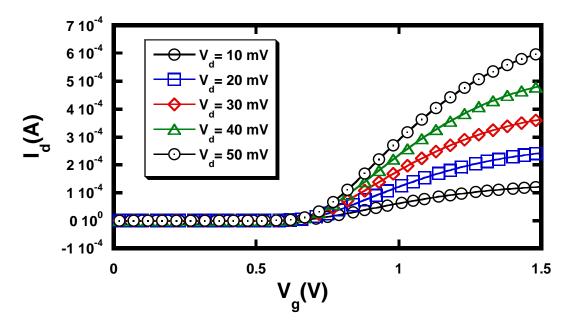

| 2.1 Measured drain current as a function of gate voltage at different drain voltages.                                                                    | 14   |

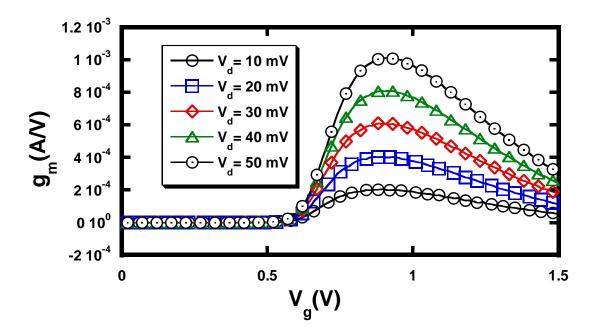

| 2.2 Measured transconductance as a function of gate voltage at different drain voltages.                                                                 | 14   |

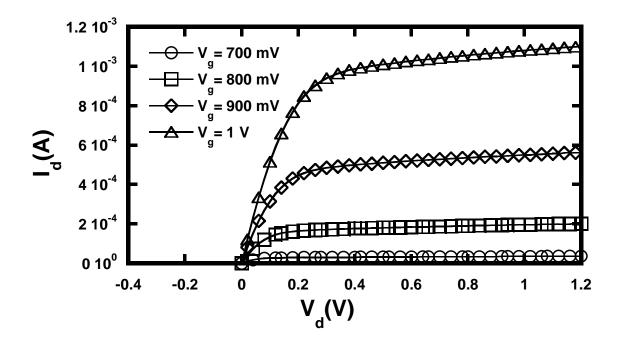

| 2.3 Drain current as a function of drain voltage at different gate voltages                                                                              | 15   |

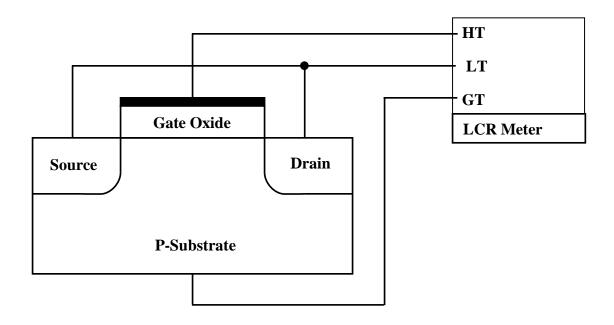

| 2.4 Split C-V measurement set up for MOSFET device. HT, LT and GT are high terminal, low terminal and ground terminal respectively [2]                   | 18   |

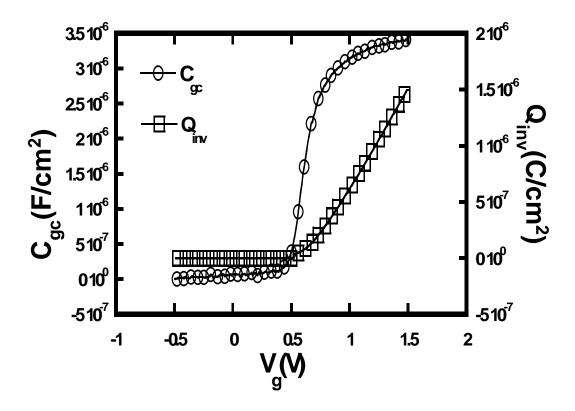

| 2.5 Corrected gate to channel capacitance of TiN/HfSiON nMOSFET from split C-V measurement and calculated channel inversion charge are shown here.       | 20   |

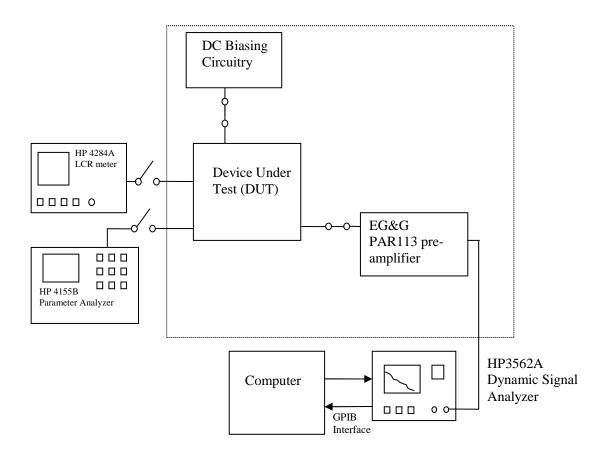

| 2.6 An overview of the low frequency noise measurement system                                                                                            | 24   |

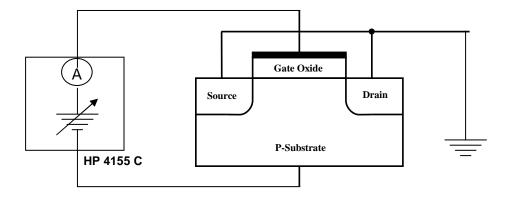

| 2.7 An overview of the constant voltage stress measurement setup                                                                                         | 27   |

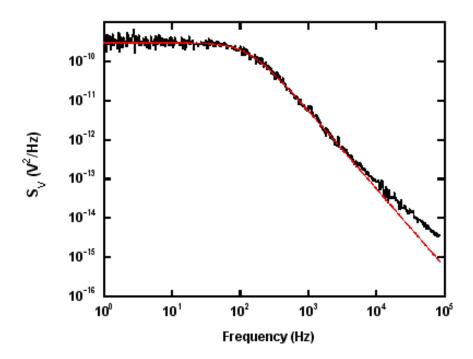

| 3.1 Typical MOSFET white noise at high frequencies. The device here is a TiN/HfSiO nMOSFET biased at Vg = 1.13 V and Vd = 0.05 V                         | 31   |

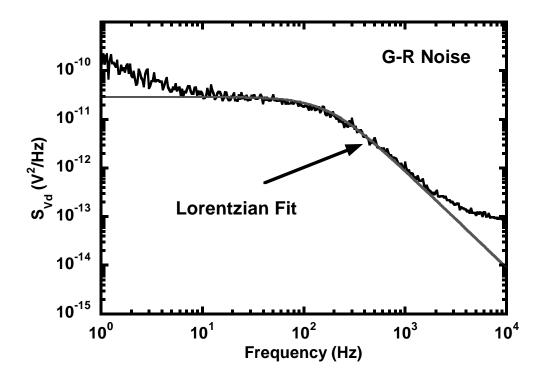

| 3.2 G-R noise in TaSiN/HfO2/SiO2 nMOSFET biased at Vg = 0.5 V and Vd = 0.05 V. The Lorentzian approximation is provided for reference [11]               | 33   |

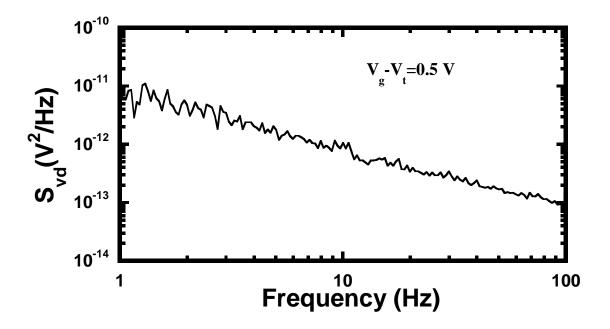

| 3.3 Voltage noise power spectrum of small area SiO <sub>2</sub> MOSFET biased at Vg = 1.3 V and Vd = 0.05 V along with a Lorentzian fitting [14]         | 35   |

| 3.4 1/f noise for $10x0.25\mu m^2$ TiN/HfSiON nMOSFET sample with device biased at Vd=50 mV and gate overdrive (V <sub>g</sub> -V <sub>t</sub> ) = 0.5 V | 36   |

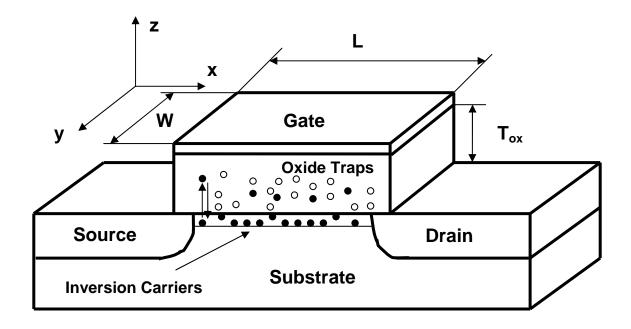

| 3.5 Cross section of a typical MOSFET showing trapping/de-trapping of inversion layer carriers by traps in the gate oxide [23]                           | 40   |

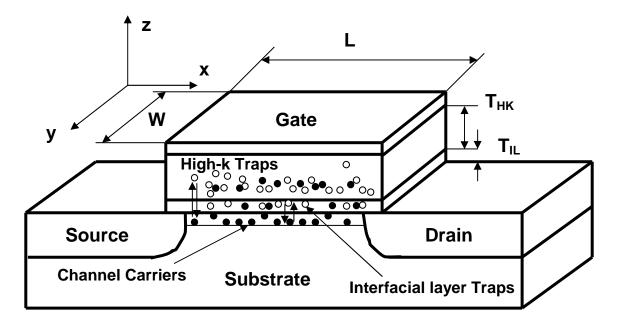

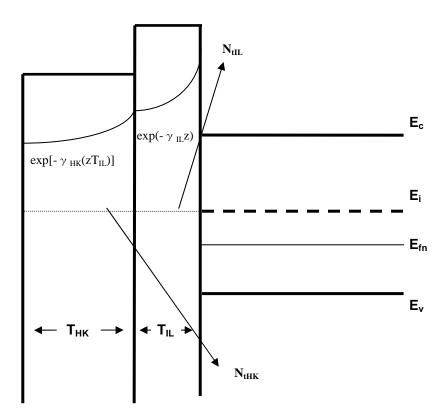

| 3.6 Typical structure of MOSFET with high-k/interfacial layer gate stack [23]                                                                            | 45   |

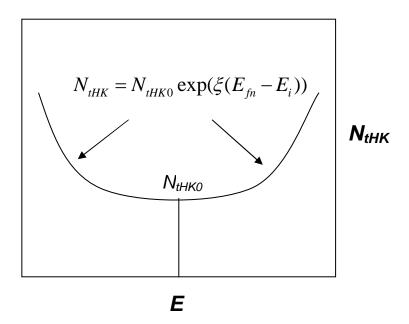

| 3.7 Variation of trap density profile with respect to energy in the high-k gate oxide region                                                             | 48   |

| 3.8 High-k MOSFET band diagram with high-k and interfacial layer [ 33]                                                                                   | 49   |

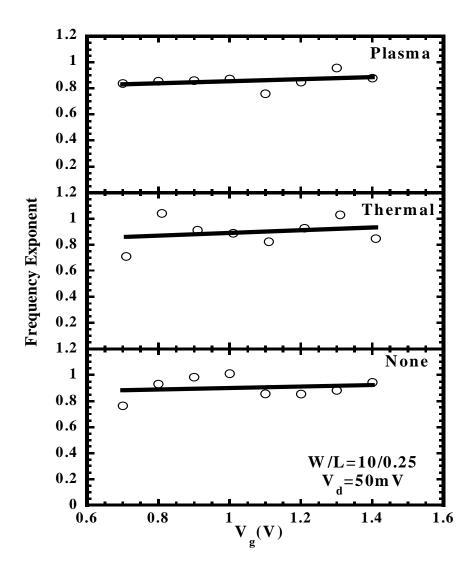

| 3.9  | Frequency exponent for 1-100 Hz range is plotted against                                                                                                                                                                                                                                              | E1 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | gate bias to extract the fitting parameters $ \xi_{{\scriptscriptstyle HK}} $ and $ \eta_{{\scriptscriptstyle HK}} $                                                                                                                                                                                  |    |

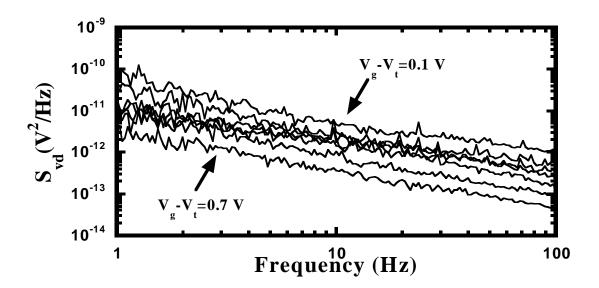

| 3.10 | O Typical drain voltage noise power spectra plot for 10x0.25µm² TiN/HfSiON nMOSFET for plasma nitrided sample with device biased at V <sub>d</sub> =50 mV and gate overdrive (V <sub>g</sub> -V <sub>t</sub> ) varying from 0.1 to 0.7 V                                                              | 52 |

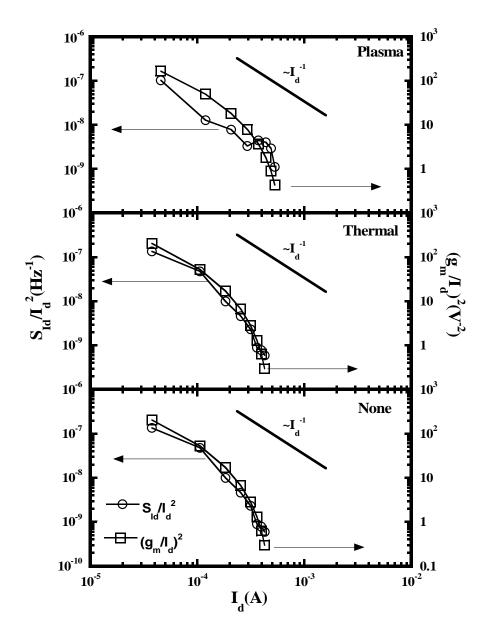

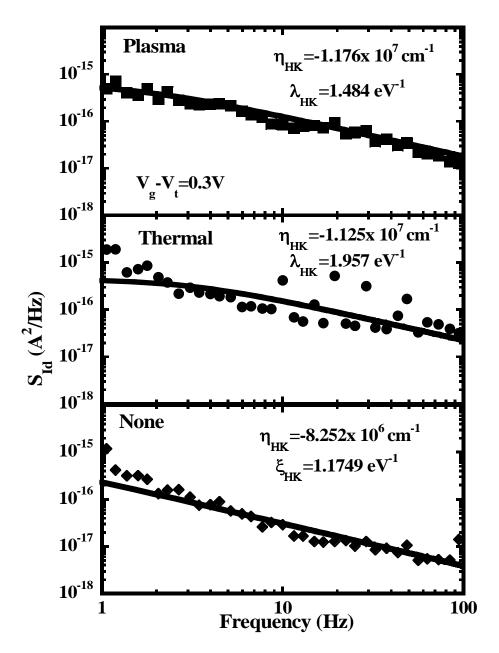

| 3.11 | $1  S_{ld} /  I_d^2$ and $(g_m / I_d)^2$ vs. $I_d$ to determine the physical mechanism responsible for $1/f$ noise ( $S_{ld}$ at 1 Hz). Since $S_{ld} /  I_d^2$ and $(g_m / I_d)^2$ follow the same trend, charge carrier number fluctuations are the dominant physical mechanism causing noise.      | 55 |

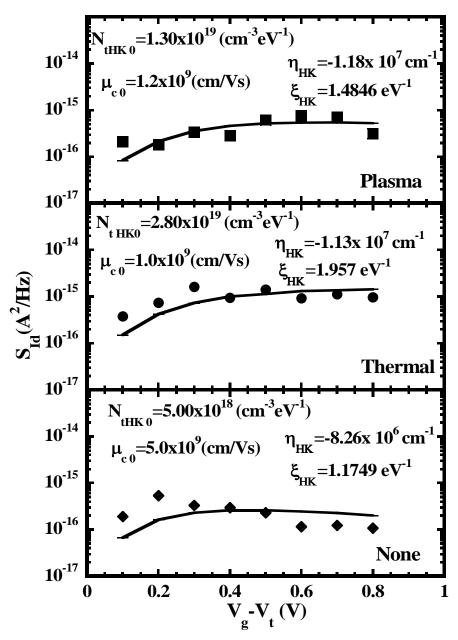

| 3.12 | 2 Measured noise spectra in the 1-100Hz frequency range for devices biased at $V_g$ - $V_t$ =0.3 V and $V_d$ =50mV along with the MSUN model fitted to the data with the four modeling parameters                                                                                                     | 56 |

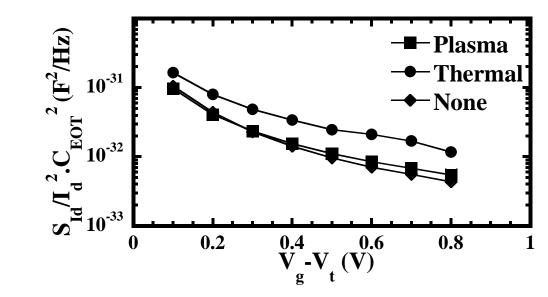

| 3.13 | 3 Typical fitting obtained between the measured current noise power spectral density at 1 Hz and the model predictions (solid line), using the MSUN model. Plasma and thermally nitrided HfSiON samples are compared to the pure HfSiO sample (none).                                                 | 59 |

| 3.14 | 4 Total 1/f noise for differently nitrided samples along with the pure HfSiO sample.                                                                                                                                                                                                                  | 60 |

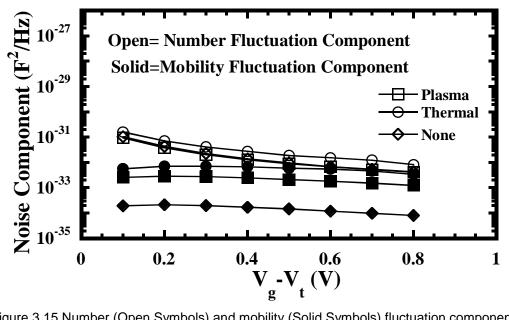

| 3.15 | 5 Number (Open Symbols) and mobility (Solid Symbols) fluctuation components of the drain current noise power spectral density measured at 1 Hz versus gate overdrive for three different process splits. Thermally nitrided samples show the highest 1/f noise                                        | 60 |

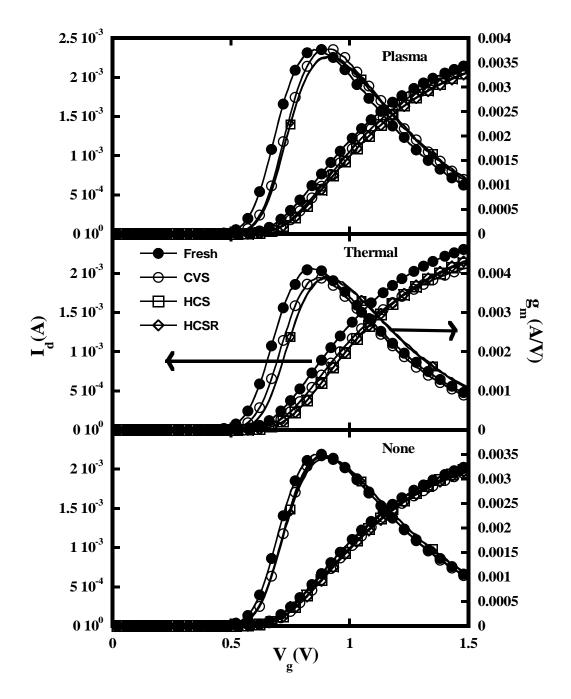

| 3.16 | 6 Drain current and transconductance characteristics of three different nMOSFETs after hot carrier and constant voltage stress, measured in forward and reverse modes.  Gate area is 10 x 0.1 μm². Plasma and thermally nitrided gate dielectrics to obtain HfSiON are compared to pure HfSiO (none). | 65 |

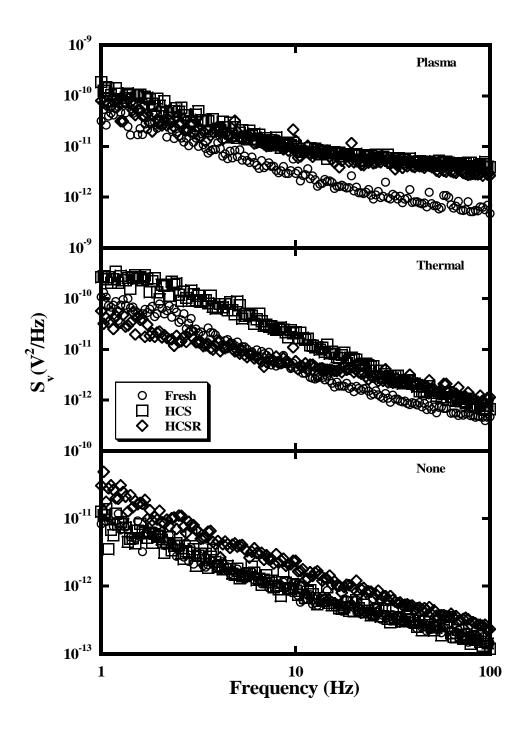

| 3.17 | 7 Drain voltage noise power spectral density at $V_{ds}$ =50 mV and $(V_g-V_t)$ =0.3 V after applying constant voltage stress at the gate for 1000s on 10 x 0.1 $\mu$ m <sup>2</sup> nMOSFET. HCS: Hot carrier stressing. HCSR: Hot carrier stressing, reverse mode measurement                       | 66 |

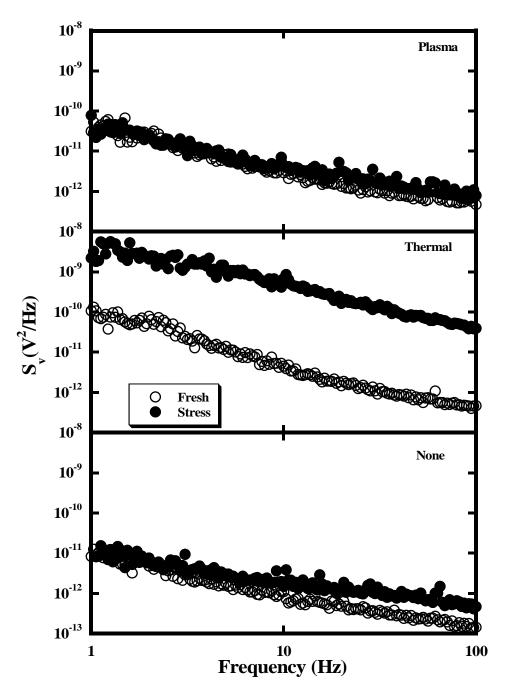

| 3.18 | 8 Noise characteristics of two differently nitrided HfSiON nMOSFETs along with HfSiO device. $V_{ds}$ =50mV and $(V_g$ - $V_t$ )=0.3 V. Gate area is 10 x 0.1 $\mu$ m <sup>2</sup> . Constant voltage stress of 10MV/cm is applied at the gate terminal for 1000s.                                    | 67 |

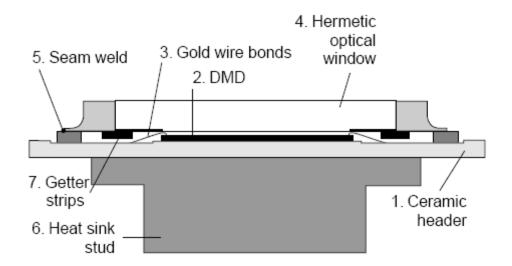

|      | Chip scale packaged digital micromirror (DMD <sup>TM</sup> ) from Texas Instruments. Reprinted after J. Faris, T. Kocian, "DMD <sup>TM</sup> packaging evolution and strategy," <i>Proc. IMAPS 98</i> , pp. 108-113, 1998 by permission of <i>IMAPS</i>                                               | 71 |

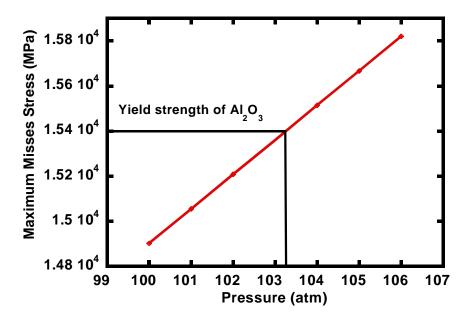

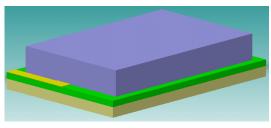

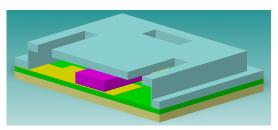

| 4.2 The mechanical strength of the designed packages<br>simulated using CoventorWare <sup>™</sup> . With pressure applied<br>on top of the package, the deflection and the maximum induced<br>Von Mises stress was computed. The structure was found to<br>withstand up to 103 Atm                                                                                                                                                                                                                                              | 74 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

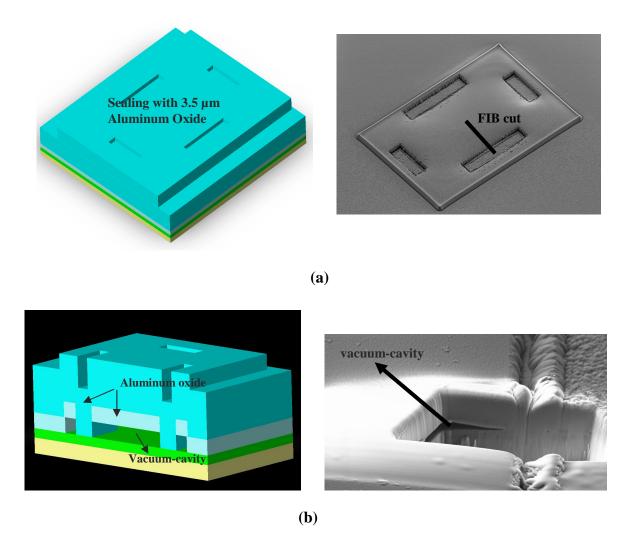

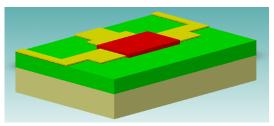

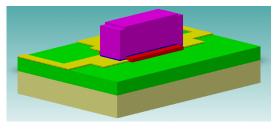

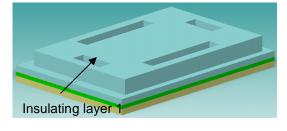

| 4.3 CoventorWare <sup>™</sup> model and SEM picture of (a) vacuum-cavity package without the resonator (b) focused ion beam (FIB) cut into the vacuum-package to show the presence of a vacuum-cavity                                                                                                                                                                                                                                                                                                                           | 75 |

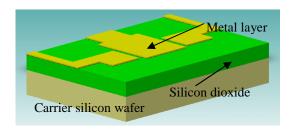

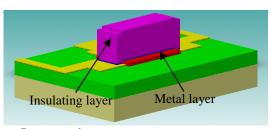

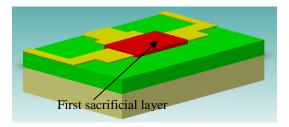

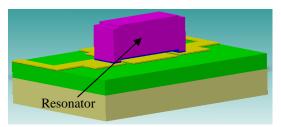

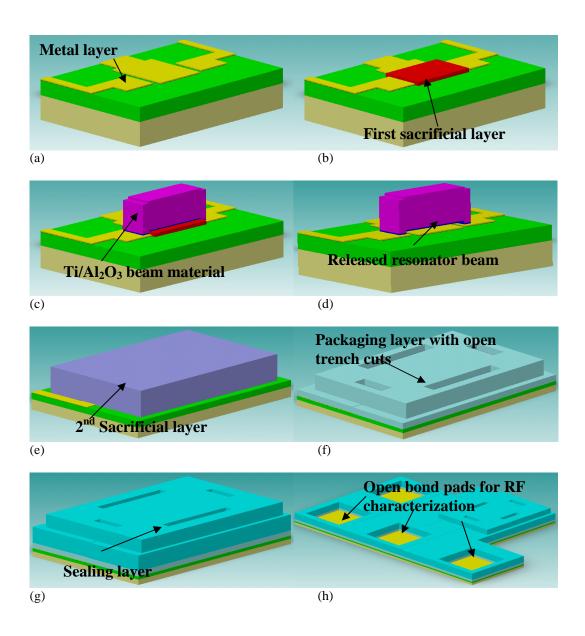

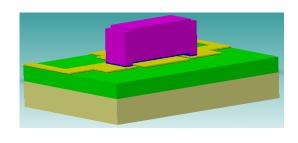

| <ul> <li>4.4 CoventorWare<sup>TM</sup> model of RF MEMS resonator fabrication.</li> <li>(a) Insulating layer deposition. (b) Deposition of first sacrificial layer. (c) Deposition of resonator beam. (d) Ashing of first sacrificial layer</li> </ul>                                                                                                                                                                                                                                                                          | 77 |

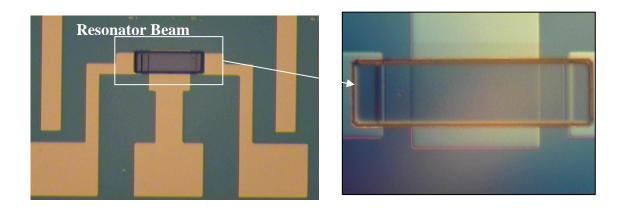

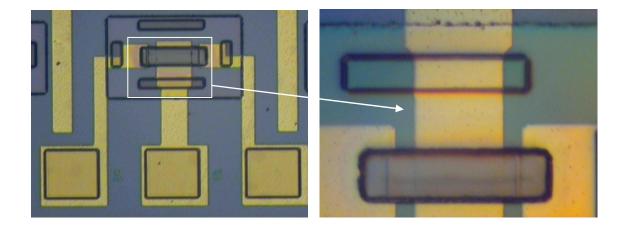

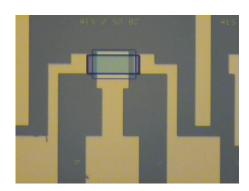

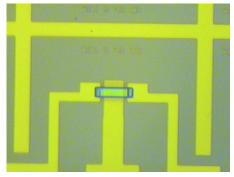

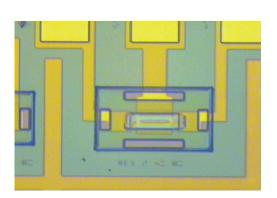

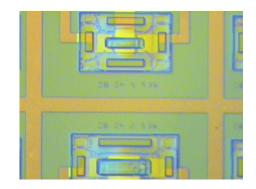

| 4.5 Optical picture of a 5 MHz resonator shows the magnified picture of the released resonator beam after ashing the first sacrificial layer                                                                                                                                                                                                                                                                                                                                                                                    | 78 |

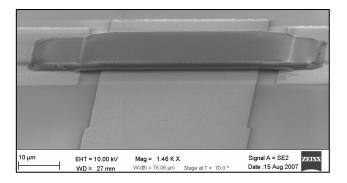

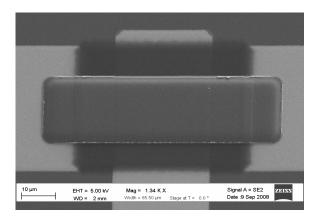

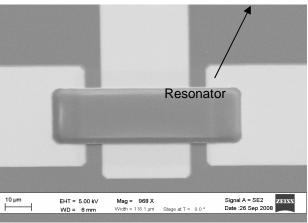

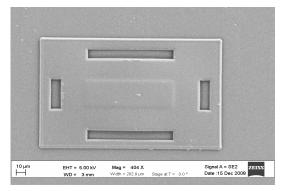

| 4.6 SEM image of a micromachined 3.6 MHz MEMS resonator. This image reveals that the resonator beam is completely released after ashing the first sacrificial layer                                                                                                                                                                                                                                                                                                                                                             | 79 |

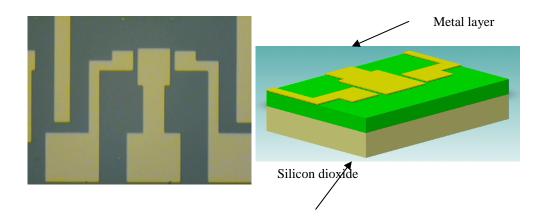

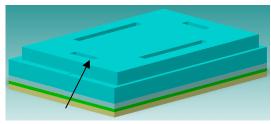

| <ul> <li>4.7 Fabrication steps: (a) SiO<sub>2</sub> insulating layer and metal layer.</li> <li>(b) Deposition of the first sacrificial layer. (c) Ti/Al<sub>2</sub>O<sub>3</sub> resonator beam deposition. (d) Ashing the first sacrificial layer. (e) Second sacrificial layer. (f) Depositing the packaging layer, forming trenches and ashing second sacrificial layer. (g) Sealing the cavity.</li> <li>(h) Opening bond pads for RF characterization. In (c) and (d), vertical axis is exaggerated by 3 times.</li> </ul> | 80 |

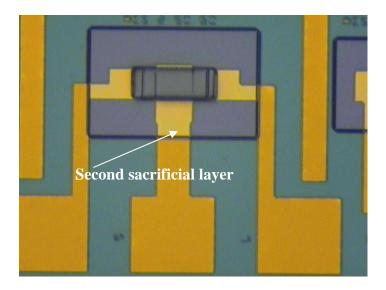

| 4.8 Optical image of a pre-released resonator with the second sacrificial layer. Second sacrificial layer determines the height between the beam and the packaging layer                                                                                                                                                                                                                                                                                                                                                        | 81 |

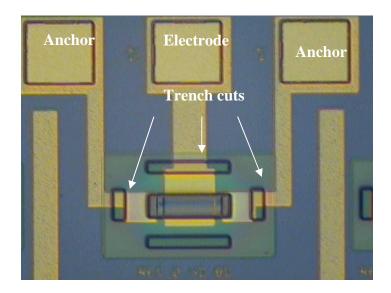

| 4.9 Trench cuts are made before deposition of the sealing layer.  The purpose of the trench cut is to ease the process of ashing                                                                                                                                                                                                                                                                                                                                                                                                | 81 |

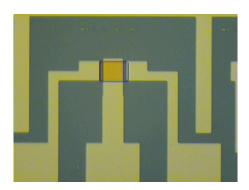

| 4.10 Magnified picture after ashing of first (determines<br>the resonator beam height) and second sacrificial layer<br>(determines the height between beam and packaging layer).<br>No trace of sacrificial layer is present.                                                                                                                                                                                                                                                                                                   | 82 |

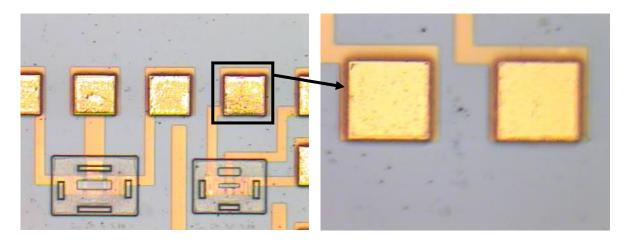

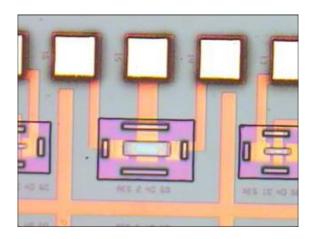

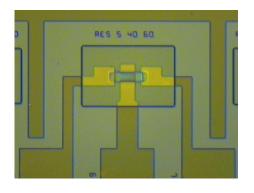

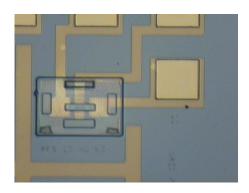

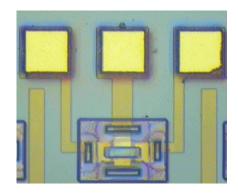

| 4.11 Optical image of the packaged resonators after sealing<br>of the ashed holes and opening of the bond pads. Magnified<br>picture of the bond pads shows that these are opened successfully                                                                                                                                                                                                                                                                                                                                  | 83 |

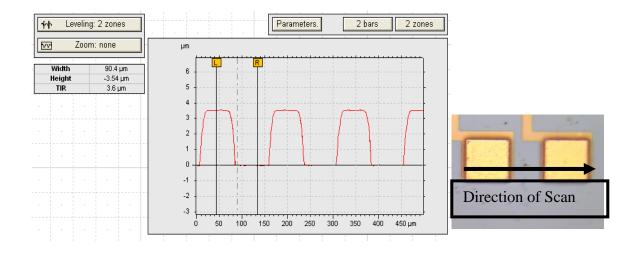

| 4.12 Profilometer data shows that the bond pads are opened uniformly                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 83 |

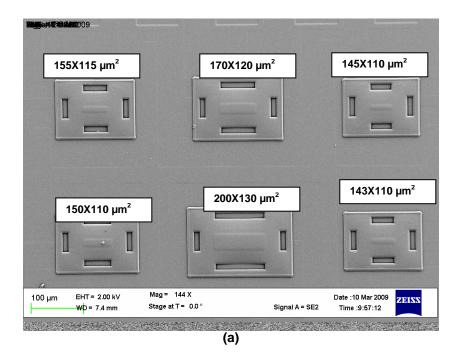

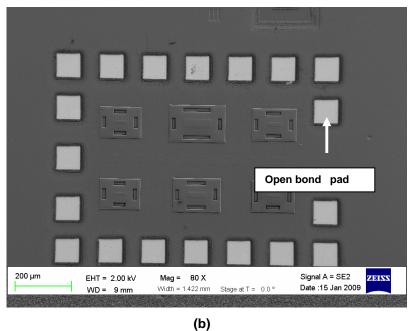

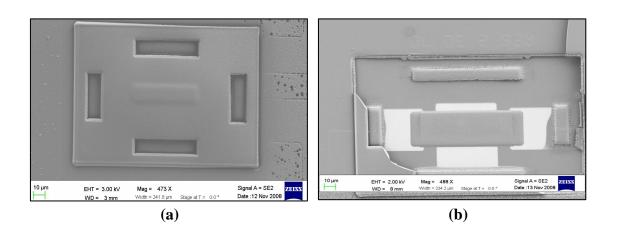

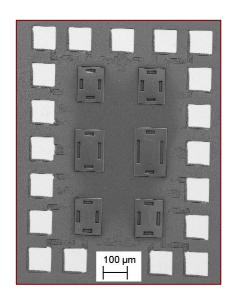

| 4.13 SEM image of completely sealed resonators (a) before and (b) after opening the bond pads. Packages are intact after opening the bond pads. The size of different packages is also given. Width of the trench cut is 15 µm and length is proportional with the package size                                                                                                                                                                                                                                                 | 84 |

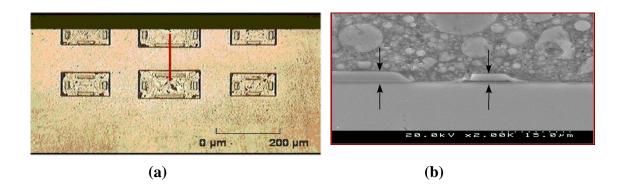

| 5.1 | <ul> <li>(a) Six different vacuum-cavity packages with the substrate removed after the over-molding process.</li> <li>The line depicts the cross-sectional cut made for the SEM.</li> <li>(b) Cross sectioned picture shows that the packages have survived after the over-molding process. The arrows point to the cross-sectioned package cavity. Between the two set of arrows lies the sealed trench-cut.</li> </ul> | 88 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.2 | Optical image of completely sealed resonator after opening bond pads                                                                                                                                                                                                                                                                                                                                                     | 38 |

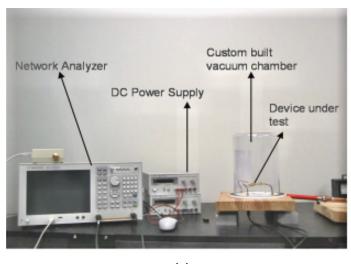

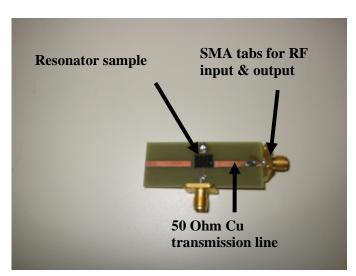

| 5.3 | (a) Experimental setup for unpackaged RF MEMS resonators. (b) DUT is glued to circuit board.                                                                                                                                                                                                                                                                                                                             | 91 |

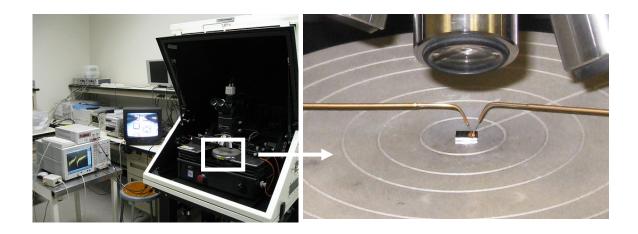

| 5.4 | Wafer level RF measurement setup at atmospheric pressure inside probe station. Setup includes a E 5071C network analyzer and an Agilent E 3620A power supply                                                                                                                                                                                                                                                             | 92 |

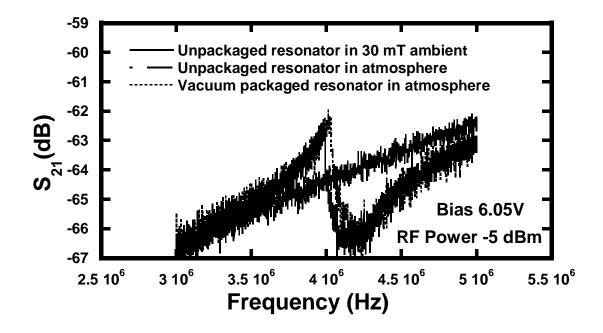

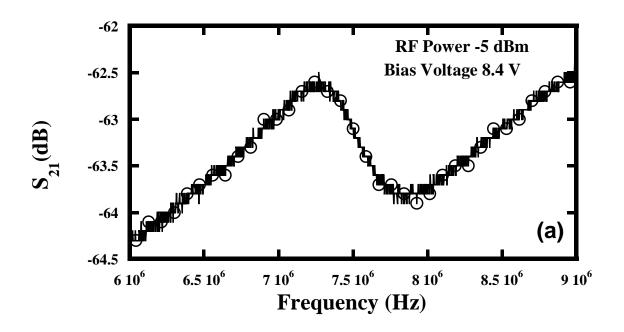

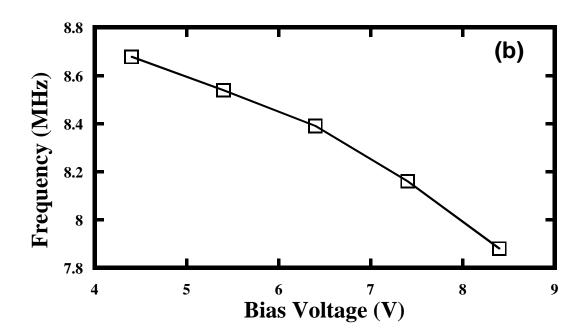

| 5.5 | Measured RF response of an unpackaged 3.6 MHz resonator showing resonance at 3.65 MHz in vacuum (25 mTorr) and no resonance at atmospheric pressure. Moreover, the vacuum packaged resonator shows resonance at 3.66 MHz inside the probe station at atmospheric pressure.                                                                                                                                               | 92 |

| 5.6 | (a) SEM image of a completely sealed. (b) SEM image of a vacuum-packaged 3.6 MHz resonator where the top layer is intentionally removed to inspect the resonator inside.                                                                                                                                                                                                                                                 | 93 |

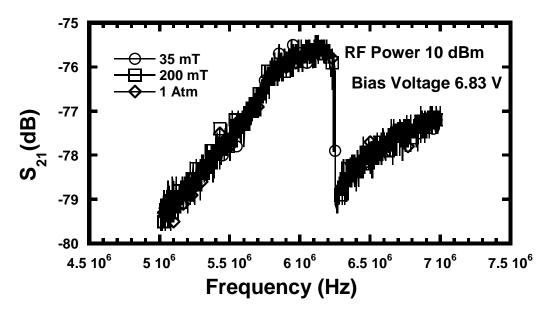

| 5.7 | Completely sealed RF MEMS resonators showing no change in resonance frequency with chamber pressure variation. Devices are slightly overdriven to get the sharp transition                                                                                                                                                                                                                                               | 97 |

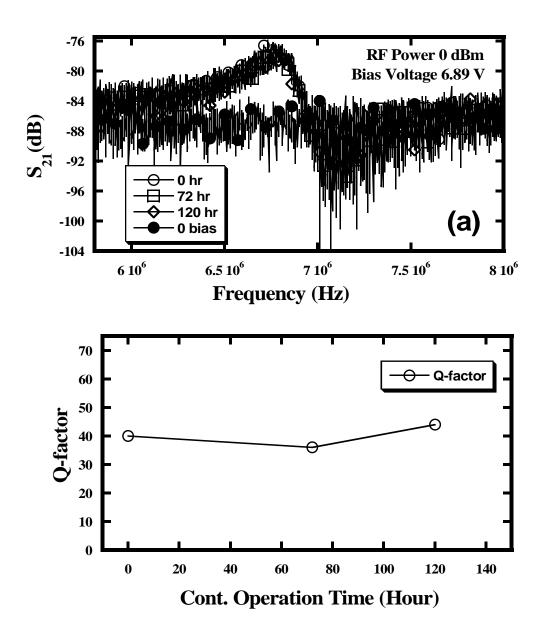

|     | Extended 120-hour RF characterization with the device held under constant bias during the duration of the experiment.  Both (a) resonance frequency and (b) Q factor show no change in their characteristics                                                                                                                                                                                                             | 97 |

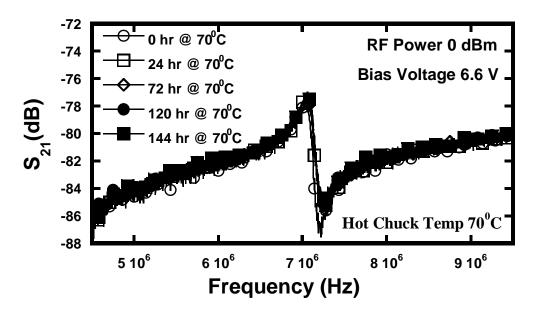

|     | High temperature operating life measurements on a completely packaged resonator for 150 hours at 70°C.  The resonators survived at elevated temperatures                                                                                                                                                                                                                                                                 | 98 |

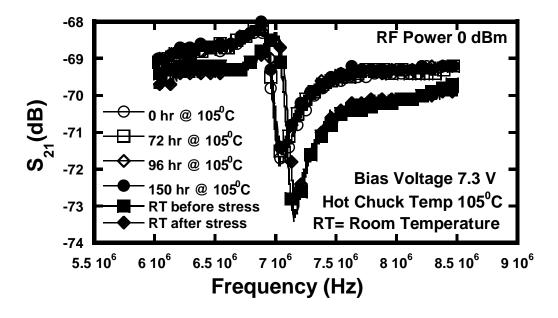

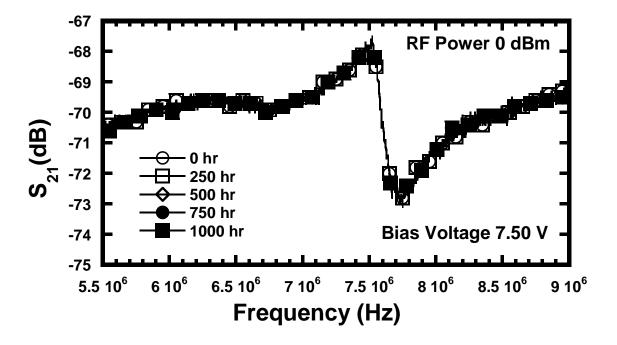

| 5.1 | 0 RF characteristics of a completely sealed 7 MHz resonator during high temperature operating life (HTOL) experiment performed at 105°C.                                                                                                                                                                                                                                                                                 | 98 |

| 5.1 | 1 RF characteristics of a completely sealed 7.5 MHz resonator during high temperature storage life (HTSL) experiment.                                                                                                                                                                                                                                                                                                    | 99 |

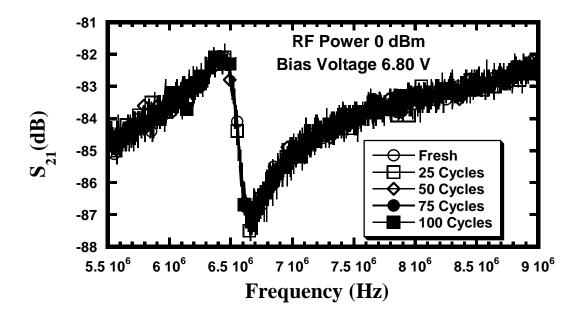

| 5.1 | 2 Temperature cycling (27°C to 120°C) effect on RF characteristics of a 6.5 MHz packaged resonator. Each cycle consists of 12 hours. Measurements were taken every 25 cycles for a total of 100 cycles                                                                                                                                                                                                                   | 20 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                          | ソ  |

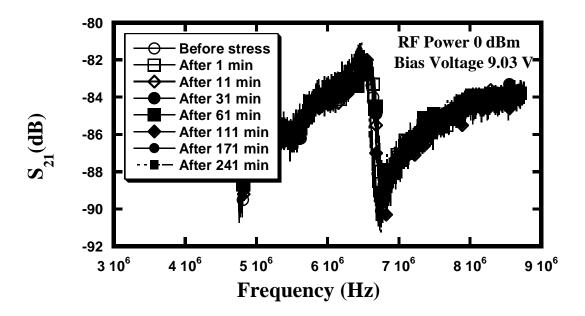

|      | packaged resonator is checked by dipping the sample in water at room temperature. No change in resonance frequency is observed                      | 101 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

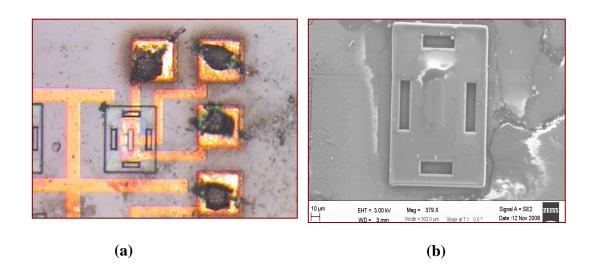

| 5.14 | The (a) optical and (b) SEM image of the dropped package resonator shows considerable visual damage on top of the wafer, but package remains intact | 102 |

|      | a) RF characteristics and (b) DC tenability of a packaged resonator after drop test. Here the sample fell up side down from three feet height.      | 103 |

# LIST OF TABLES

| Table |                                                                                                            | Page |

|-------|------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Device Specification                                                                                       | 12   |

| 3.1   | Extracted MSUN Model Parameters                                                                            | 57   |

| 3.2   | Stress Induced Degradation for Different of $g_{m,max}$ , $I_{d,sat}$ , and $V_{th}$ for Different Samples | 62   |

| 5.1   | DC Continuity Check of Released Resonators                                                                 | 90   |

# LIST OF SYMBOLS

$C_{EOT}$  equivalent oxide capacitance of MOSFET (Fcm<sup>-2</sup>)

$C_g$  total gate capacitance of MOSFET (Fcm<sup>-2</sup>)

$C_{gb}$  gate to bulk capacitance of MOSFET (Fcm<sup>-2</sup>)

$C_{gc}$  gate to channel capacitance of MOSFET (Fcm<sup>-2</sup>)

$C_{ox}$  gate oxide capacitance of MOSFET (Fcm<sup>-2</sup>)

$C_{overlap}$  overlap capacitance (Fcm<sup>-2</sup>)

$D_{it}$  interface trap density from sub-threshold measurements (eV<sup>-1</sup>cm<sup>-2</sup>)

E energy level (eV)

EOT equivalent oxide thickness (nm)

$E_{c}$  conduction band edge (eV)

$E_{\it fn}$  quasi Fermi level (eV)

$E_{\rm \it g} \qquad \qquad {\rm energy \ Gap \ (eV)}$

$E_i$  intrinsic Fermi level (eV)

$E_{\scriptscriptstyle v}$  valence band edge (eV)

$E_x$  field along the channel (Vcm<sup>-1</sup>)

f frequency (Hz)

| $f_t$            | trap occupancy function                                                            |

|------------------|------------------------------------------------------------------------------------|

| $\mathcal{G}_d$  | Conductance (A V <sup>-1</sup> )                                                   |

| $g_m$            | transconductance (A V <sup>-1</sup> )                                              |

| h                | Planck's constant (eV-s)                                                           |

| $I_d$            | drain current (A)                                                                  |

| $I_g$            | gate current (A)                                                                   |

| I <sub>sub</sub> | substrate current (A)                                                              |

| Is               | source current (A)                                                                 |

| k                | dielectric constant                                                                |

| k                | Boltzmann's constant (eV K <sup>-1</sup> )                                         |

| L                | MOSFET channel length (μm)                                                         |

| $\Delta L$       | length of pinch-off/velocity saturation region (µm)                                |

| m <sup>*</sup>   | electron effective mass (kg)                                                       |

| N                | inversion layer charge density (cm <sup>-2</sup> )                                 |

| $N_{o}$          | source end charge density (cm <sup>-2</sup> )                                      |

| $N_f$            | fixed charge density (cm <sup>-2</sup> )                                           |

| N(x)             | inversion layer charge density at distance $x$ from the source (cm <sup>-2</sup> ) |

| $N_t$            | oxide trap density (cm <sup>-3</sup> eV <sup>-1</sup> )                            |

| N <sub>ot</sub>  | occupied traps per unit area (cm <sup>-2</sup> )                                   |

$N_{tHKO}$  trap density at the intrinsic Fermi level, at the high-k dielectric - interfacial

layer interface (cm<sup>-3</sup> eV<sup>-1</sup>)

$N_{tHK}(E_{fn}, z)$  trap density distribution in the high-k layer at the quasi Fermi level (cm<sup>-3</sup> eV<sup>-1</sup>)

$N_{tlL}(E_{fn}, z)$  trap density distribution in the interfacial layer at the quasi Fermi level (cm<sup>-3</sup>

$eV^{-1}$ )

$\Delta N$  inversion charge in the  $W \Delta x$  area

$\Delta N_{ot}$  number of occupied traps in the gate oxide ( $W\Delta x$  area)

q electronic charge (C)

Q<sub>bulk</sub> bulk charge (Ccm<sup>-2</sup>)

Q<sub>D</sub> depletion charge (Ccm<sup>-2</sup>)

Q<sub>G</sub> gate charge (Ccm<sup>-2</sup>)

Q<sub>inv</sub> inversion layer charge (Ccm<sup>-2</sup>)

Q<sub>it</sub> interface trap charge (Ccm<sup>-2</sup>)

Q<sub>sc</sub> semiconductor charge (Ccm<sup>-2</sup>)

$Q_t$  oxide trap charge (Ccm<sup>-2</sup>)

R coupling coefficient between fluctuations in the channel charge and in the

gate oxide trapped charge

S subthreshold slope (V<sup>-1</sup>)

$S_l$  total current noise power spectral density (A<sup>2</sup> Hz<sup>-1</sup>)

$S_{ld}$  total drain current noise power spectral density (A<sup>2</sup> Hz<sup>-1</sup>)

$S_{\Delta Id}(x,f)$  power spectral density of the local current fluctuations (A<sup>2</sup> Hz<sup>-1</sup>)

$S_{\Delta Nt}(x, f)$  power spectral density of the mean square fluctuations in the trapped charge

carriers over the area  $W\Delta x$  (Hz<sup>-1</sup>)

$S_{V_{\perp}}$  drain voltage noise power spectral density (V<sup>2</sup> Hz<sup>-1</sup>)

T temperature (K)

$t_{\it CET}$  capacitance equivalent thickness (nm)

EOT equivalent oxide thickness (cm)

$T_{HK}$  high-k dielectric thickness (cm)

$T_{IL}$  thickness of interfacial layer (cm)

$T_{ox}$  thickness of gate oxide (cm)

$V_d$  drain to source voltage (V)

$V_{dsat}$  drain to source voltage at pinch-off/velocity saturation point (V)

$V_g$  gate to source voltage (V)

$V_{ox}$  potential across gate oxide (V)

$V_s$  source voltage (V)

$V_{sub}$  substrate voltage (V)

$V_t$  threshold voltage (V)

V(x) horizontal channel potential in the channel at a distance x from the source (V)

W MOSFET channel width of (μm)

x distance in the channel (cm)

y distance in the width dimension (cm)

z distance into the gate dielectric stack (cm)

xviii

| Δχ                | infinitesimal length in the gate dielectric (cm)                                       |

|-------------------|----------------------------------------------------------------------------------------|

| Δy                | infinitesimal width in the gate dielectric (cm)                                        |

| Δz                | infinitesimal thickness in the gate dielectric (cm)                                    |

| $lpha_{H}$        | Hooge's Coefficient                                                                    |

| $lpha_{	ext{sc}}$ | screened coulomb scattering coefficient (V s)                                          |

| γ                 | carrier tunneling coefficient in the gate dielectric (cm <sup>-1</sup> )               |

| $\gamma_{_{HK}}$  | carrier tunneling coefficient in the high-k gate dielectric (cm <sup>-1</sup> )        |

| ${\cal E}_0^{}$   | permittivity of free space (Fcm <sup>-1</sup> )                                        |

| $\eta_{_{HK}}$    | fitting parameter that determines the high-k dielectric trap density distribution      |

|                   | as a function of $z (cm^{-1})$                                                         |

| $\lambda_{_{HK}}$ | fitting parameter that defines the effect of dielectric band-bending on the trap       |

|                   | density that the tunneling electron encounters in the high-k dielectric layer          |

|                   | $(eV^{-1})$                                                                            |

| $\mu$             | surface potential based effective carrier mobility (cm²/Vs)                            |

| $\mu_{c0}$        | mobility fitting parameter (cm/Vs)                                                     |

| $\mu_{	ext{eff}}$ | effective carrier mobility (cm²/Vs)                                                    |

| $\mu_{	ext{imp}}$ | mobility due to impurity scattering (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) |

| μ <sub>latt</sub> | mobility due to lattice scattering (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> )  |

| $\mu_{others}$    | mobility due to other scattering phenomena (cm²/Vs)                                    |

| $\mu_{ox}$        | mobility due to oxide charge scattering (cm <sup>2</sup> /Vs)                          |

$\xi_{HK} \qquad \qquad \text{fitting parameter for energy dependence of high-k traps (eV}^{-1})$   $\tau \; (E, x, y, z) \qquad \text{trapping time constant in the gate dielectric (s)}$   $\tau \qquad \qquad \text{trapping time constant (s)}$   $\tau_o \qquad \qquad \text{trapping time constant at the Si/SiO}_2 \; \text{interface (s)}$   $\sigma \qquad \qquad \text{frequency exponent as in 1/f}^\sigma$   $\omega \qquad \qquad \text{angular frequency (radians/s)}$   $\psi_s \qquad \qquad \text{surface potential (V)}$

#### CHAPTER 1

# INTRODUCTION

# 1.1 Introduction

This dissertation is divided into two sections. In the first section, the low frequency noise performance of Hafnium (Hf) based high dielectric constant (high-k) gate dielectric metal-oxide-semiconductor field effect transistors (MOSFETs) is considered. The second section discusses CMOS process compatible, cost effective, wafer level vacuum packaging of radio frequency (RF) microelectromechanical systems (MEMS) devices.

# 1.2 Trends in semiconductor industry and device scale

For many decades, the performance of MOSFET has been the main driving force for the growth of the semiconductor industry. This growth is sustained by conventional device scaling. For this reason, the gate length has been reduced from hundreds of micrometers in the 1960s to a few tens of a nanometer today. During 1970s, it was discovered that devices with short gate lengths [1], 1 µm at that time, showed undesired behavior, due to a predicament called short channel effect. Scaling of the threshold voltage also causes an increase in the subthreshold current and leads to high power consumption even when the device is off. On the other hand, gate looses control over the channel as the gate length is scaled down. This leads to a reduced threshold voltage and an increased off-current for devices with a short channel length. However, other technologies to improve device performance were also explored at the same time as traditional downscaling faced difficulties. It was also found that continuous downscaling of device requires introduction of new dielectric materials for the gate oxide. All of these have resulted in the emergence and development of a broad range of alternative CMOS technologies with new materials and novel architectures.

Unfortunately, down-scaling has also resulted in the following undesirable effects [2,3,4]. The carrier mobility has degraded when the doping concentration is increased due to higher effective electric field as well as due to impurity scattering. Moreover, source and drain resistances had to be scaled down in proportion to the channel resistance which is increasingly difficult since the junction depth decreases simultaneously. Reliability and power dissipation became serious problems in the generalized scaling scheme. The tunneling current increased exponentially with the decreasing gate oxide thickness. In addition, the depletion of poly-si gate gave rise to a reduction in the effective oxide capacitance, since the depletion region appears as a capacitance acting in series with the gate oxide capacitance. All these effects together demonstrate the need to find alternative materials and device architectures to enhance the carrier mobility, control the short channel effects, and limit the gate leakage current.

# 1.2.1 High-k materials and noise modeling

# 1.2.1.1 Introduction of high-k materials

Improvements in integrated circuit (IC) speed and chip area have been achieved by scaling down the physical thickness of the conventional SiO<sub>2</sub> gate dielectrics and device dimension. Driving technology for modern integrated circuits greatly relies on aggressive down scaling of MOS transistors. Reducing the transistor size not only increases package density but also increases circuit speed and reduces power dissipation [5]. However, SiO<sub>2</sub> has reached its physical limitation due high leakage current and reliability concerns. Continuous scaling down of the MOSFET with the minimum feature size of 90 nm and below would require equivalent oxide thickness (EOT) of 1.5~2nm and below. A 1~1.5 nm of SiO<sub>2</sub> layer corresponds to only around 3~4 monolayers of SiO<sub>2</sub>. In this thinner EOT range, SiO<sub>2</sub> suffers from leakage current which is too high to be used for low-power applications. In addition, SiO<sub>2</sub> thickness control across a 12-inch wafer imposes even more serious difficulty in growth of such a thin film. Moreover, in that

thickness, direct tunneling current through the SiO<sub>2</sub> cannot be tolerated anymore. Therefore, it has become necessary to identify alternative high-k gate dielectrics in order to meet the stringent requirements in the leakage gate current and EOT. So far a number of high-k gate materials have been reported such as HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub> and their silicates [6,7,8,9]. Among these various high-k gate dielectric materials, Hf-based high-k gate materials and its silicates with moderate high-k value (dielectric constant between 21~25) have been found to be attractive because they have demonstrated enhanced device properties, especially low gate leakage current, improved reliability against induced electrical stress, and better compatibility with poly-silicon as well as metal gate processes [5].

# 1.2.1.2 Advantages and disadvantages of high-k materials

The scaling of the MOSFET follows the Moore's law, which predicts the increase in number of transistors in IC. However, scaling of conventional gate oxide, SiO<sub>2</sub>, beyond 1.5nm is problematic. The leakage current flowing through the gate oxide exceeds well above the specification. Therefore, high-k gate dielectrics have attracted a great deal of attention as the replacement of conventional SiO<sub>2</sub> gate dielectrics. The reason for using higher dielectric constant material is to provide a substantially thicker dielectric material to reduce gate leakage current and to improve the gate capacitance. So far, many materials have been evaluated as a suitable candidate for the gate oxide. Among these materials, Hf-based high-k gate dielectrics appear to be sone of the most promising materials. In fact, Hf-based gate dielectric materials could be scaled down to below EOT of around 1 nm with excellent electrical and physical characteristics. Although high-k gate dielectric materials are necessary to continue the current scaling trends, these materials also have been known to have higher trap density than conventional gate oxide materials [10]. A number of different processing techniques have been reported to improve the characteristics of high-k gate dielectrics [11,12,13,14]. The origin of traps in the high-k gate dielectric materials still remains a question. These pre-existing traps can

play an important role in the dielectric wear-out as well as device performance. In order to evaluate reliability, it is necessary to pin point the factors that influence the breakdown of the high-k gate dielectric materials.

## 1.2.1.3 Low Frequency Noise performance

This new high-k gate dielectric technology has several important implications on the MOSFET low frequency noise (LFN) performance. LFN is sensitive to the defects and imperfections in the proximity of the carrier current path. The device quality in terms of defect densities as well as the LFN properties may differ substantially for different materials, manufacturing technologies and device architecture. At the same time as the more complex technologies may lead to the increased LFN, the downsizing of the transistor dimensions certainly causes higher LFN.

# 1.3 Device level packaging in MEMS

Second part of this proposal discusses design, fabrication, and characterization of wafer level vacuum packaging of MEMS devices. For MEMS products, packaging is one of the stumbling blocks against successful commercialization of the product and is a major portion of the total production cost of virtually every MEMS device. This high cost has made packaging the key point of focus for the industry to reduce cost in order to enhance the competitiveness of the product in the market. Packaging technology vary widely depending between MEMS devices exposed to the environment (pressure sensor) and those isolated from it (RF MEMS and accelerometer). Many MEMS devices require expensive vacuum packaging. MEMS resonator is one example where the quality (Q) factor of the resonator depends on the pressure of the ambient. According to 2007 report on assembly and packaging of International Technology Roadmap for Semiconductors (ITRS) [15], much emphasis has been given to the wafer level vacuum packaging for RF MEMS devices due to its improved electrical performance, low cost,

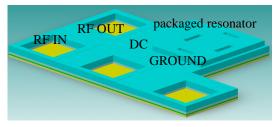

lower power requirements and smaller size. Providing a controlled micro-environment for isolating MEMS structures may represent an optimal approach for the cost effective production of suspended MEMS devices. By effectively sealing the MEMS at a wafer or die level, it is possible to subject the device to conventional high volume packaging approaches. This work details the design and fabrication of "canopy structure" vacuum packaging of RF MEMS device. The approach is to successfully encapsulate the RF MEMS resonators with the vacuum packages to form self packaged devices and to check the quality of vacuum in the package by measuring the resonator characteristics.

# 1.3.1 Cost effective RF MEMS packaging

# 1.3.1.1 Wafer level packaging

Wafer level encapsulation mitigates many of the challenges associated with MEMS packaging such as, dicing, handling, and encapsulation and it represents a challenging and costly task in the manufacturing of MEMS systems [16,17]. On an average, 70% of the cost of a MEMS device is in packaging. The package protects the MEMS device from the detrimental effects of the environment. A vacuum encapsulation is especially required for the operations of MEMS devices such as resonators, Pirani gauges and gyroscopes etc. The package can also provide design specific functions such as RF signal isolation as well as mechanical stability and radiation protection required for sensors.

The main advantage for moving from chip-scale to wafer level is the cost. Moreover, since the wafer level packaging is typically done in clean room environment, there is less chance of contaminating the MEMS device. As a device prototype we have chosen RF MEMS resonators, because the Q-factor and resonance frequency ( $f_r$ ) of the MEMS resonators are pressure dependent. Therefore, any change in pressure inside the cavity will result in corresponding

change in Q factor and  $f_r$ . In this way, we can monitor the vacuum quality inside the encapsulation layer.

# 1.3.1.2 Review of current MEMS packaging

To ensure the long term reliability, in some cases an open die MEMS device must be hermitically packaged. For MEMS packaging there are generally two approaches. One is chip scale packaging, where sealing is performed on the individual die after dicing; the other one is wafer-level packaging, where sealing is performed in parallel with device fabrication prior to dicing and assembly. Wafer level packaging provides many benefits- two most important being the lowest cost and smallest size.

The wafer level packaging can be classified into wafer bonding and sacrificial layer based encapsulation techniques. The wafer bonding is typically done by bonding a cap wafer on to the MEMS wafer. In the sacrificial layer based technique, the encapsulation can be done on top of a surface micromachined device by depositing a thin film overcoat. Later, the trench cuts are made on top of the packaging layer, followed by removing of the sacrificial layer and finally sealing of the trench cuts by films deposition.

Although wafer bonding results in good life expectancy, it has a number of disadvantages. First of all, the anchor region where the cap seals to the MEMS die must be large to ensure a safe and hermetic seal. This results in a significant increase in die size and consequently in the production cost. And more importantly for RF MEMS there is also an increase in electromagnetic loss. The bonded die is also thicker than the standard IC die. Wafer to wafer bonding requires alignment of the cap to the host MEMS wafer, which can complicate the packaging especially for small packages. On top of all these, the bonding requires very clean

surfaces. Therefore, packaging of MEMS with rough surfaces may be difficult and may result in a non hermetic seal and yield loss.

A possible solution for all of the above problems is the formation and sealing of surface micromachined layer over the MEMS. The main advantages of this integrated packaging technique would be the reduced thickness and chip area with resultant lower cost batch process. In this dissertation, we have introduced  $Al_2O_3$  (alumina) as a sealing and resonator beam material as part of a low cost, low temperature packaging technique.

# 1.4 Summary

The contribution of this dissertation is on the contemporary reliability issues arising directly from the semiconductor industry. The first part of this work deals with the low frequency noise characterization and reliability of Hf-based high-k gate dielectric materials. Recently, there have been reports on the LFN performance of various mixed signal circuits with MOSFETS using Hf-based high-k gate dielectric materials [18, 19, 20]. Since LFN is a growing concern for analog and mixed signal CMOS circuitry, it is important to characterize the LFN not only for fresh devices but also during the lifetime of the transistor. By and large, this has been neglected so far. In this work, we present a systematic study of 1/f noise exhibited by HfSiON gate-dielectric MOSFETs, and its dependence on the nitridation technique. In addition, Hot Carrier Stress (HCS) and Constant Voltage Stress (CVS) induced noise degradation in plasma and thermally nitrided HfSiON and HfSiO devices was investigated. It is shown, for the first time that the nitrogen distribution profile in the gate dielectric due to different nitridation techniques affects the HCS and CVS induced 1/f noise performance of ultra thin HfSiON nMOSFETs.

The second part of the dissertation addresses a very important issue in a fast growing MEMS industry, the packaging. Packaging plays a critical role for microelectromechanical systems. For specific RF applications, where the use of MEMS technology is highly attractive, cost of effective packaging is one of the primary barriers to commercialization. RF MEMS packaging is comparatively new with a variety of approaches being explored to balance the broad range of technological and cost constraints. Many RF MEMS devices require a hermetic or vacuum operation environment. This work presents a post-CMOS compatible method for vacuum packaging of RF MEMS devices by growing an encapsulation layer during the device fabrication. The packaging technique is scalable from device to die to wafer level. The resulting MEMS devices are surrounded by a vacuum or hermetic cavity and can then be placed in a conventional, low cost circuit package. This is a low temperature, area efficient, across wafer, device level encapsulation for MEMS. In this case, RF MEMS resonators in a fixed-fixed beam configuration were used as the test bed for the device level vacuum packaging technique since the quality factor of the resonators can be used as an indirect measure of the package quality and reliability. The encapsulation process started after fabricating the MEMS resonators and is based on a double sacrificial layer surface micromachining technique, used to create a cavity under and above the resonator. Polyimide was used as a sacrificial layer, followed by the deposition of a packaging layer with trench cuts, which facilitate the sacrificial layer removal. The trench cuts were then sealed at a low-pressure environment, thus forming a cavity around the device at the sealant layer deposition pressure. Extensive RF characterization and reliability tests were performed on the packaged resonators. No noticeable degradation in RF characteristics was observed with high temperature and thermal cycling stress, indicating the good reliability of the packages. In addition we report for the first time the use of alumina as resonator beam and packaging material.

A brief outline of the dissertation is presented below.

Chapter 1 presents background, goal and achievements of this work. This chapter also provides a general overview of importance of the work.

Chapter 2 gives information about background as well as various measurement techniques used to evaluate the low frequency noise performance of Hf-based high-k gate dielectric MOSFETs.

Chapter 3 introduces effects of various nitridation techniques on the low frequency noise performance followed by HCS and CVS induced low frequency noise degradation.

Chapter 4 introduces the motivation and approach for cost effective RF MEMS packaging. This chapter also presents the design and fabrication process for the vacuum cavity package and the RF MEMS resonator.

Chapter 5 presents the extensive RF characterization of packaged RF MEMS resonators. A thorough study of different long term and accelerated life testing is also performed.

Chapter 6 is the conclusion of the work done and it also suggests future directions for the present work.

#### CHAPTER 2

#### NOISE AND CARRIER MOBILITY MEASUREMENTS

# 2.1 Introduction

With the immense progress in silicon technology and miniaturization of electronic devices to nanometer sizes, the reliability of gate oxide and its interface has gained importance. Trapped charges, defects and traps both in the oxide and at the high-k/ Si interface play an important role in the gradual degradation of the oxide characteristics. To characterize the defects in the oxide and to predict device reliability due to oxide breakdown, flicker or 1/f noise has been shown to be a well established diagnostic tool. The measurement of noise is a complex task. The measurement setup must be designed carefully with appropriate shielding and batteries as the power source to avoid disturbances in the measurement setup. The noise measurement is typically performed in the frequency domain by measuring the power spectral density with a spectral analyzer.

This chapter presents the specifications for the MOSFETs used for the noise analysis, describes different measurement methods including DC characteristics, charge density and mobility extraction, low frequency noise as well as different stressing techniques.

# 2.2 Device specification

The devices used in this work were provided by SEMATECH International, fabricated using the 45 nm technology node [21]. Standard CMOS processing flow was used to fabricate the samples. On HF cleaned wafers, a SiON interface layer was thermally grown. 2nm HfSiO was deposited with an optimized atomic layer deposition (ALD) process using  $Hf[N(CH_3)C_2H_5]_4$  (TEMAHf) and  $Si[N(CH_3)C_2H_5]_4$  (TEMASi) precursors with ozone oxidant. For plasma

nitridation of ALD HfSiO sample, processing time was varied to control the nitrogen content in the film. Other plasma process conditions were kept constant. For thermal nitridation, a similar nitrogen concentration was incorporated in ALD HfSiO film in NH<sub>3</sub> ambient and N content was increased by increasing the temperature of NH<sub>3</sub> anneal. ALD TiN with polysilicon capping was used as the gate electrode. A conventional CMOS process flow that included 1000°C, five-second activation anneal was used after gate stack formation. Nitrogen content for both plasma and thermally nitrided samples was measured by X-ray photoelectron spectroscopy (XPS) to be 8%. Subsequently TiN was deposited as the gate electrode using ALD. The rest of the CMOS processing was standard. A lot-split containing HfSiO gate dielectric with no nitridation was also included in the investigation as a control sample. Thermally and plasma nitrided samples (HfSiON) and pure HfSiO with no added nitrogen displayed capacitances equivalent to 1.03, 1.06 and 1.17 nm EOT, respectively. The device specification is shown in the following table. The nitrogen method column indicates how nitrogen was incorporated in the gate dielectric and W/L (Width/Length) column indicates device dimensions.

Table 2.1 Device Specifications

| Dielectric(HfSiON)   | EOT (nm) | Nitridation Method | W/L(µm/µm) |

|----------------------|----------|--------------------|------------|

| 10% SiO <sub>2</sub> | 1.06     | Plasma             | 10/0.25    |

| 10% SiO <sub>2</sub> | 1.03     | Thermal            | 10/0.25    |

| 10% SiO <sub>2</sub> | 1.17     | None (HfSiO)       | 10/0.25    |

Semiconductor parameter analyzer Agilent 4155C was used for DC characterization before noise measurements to extract the threshold voltage ( $V_t$ ), transconductance ( $g_m$ ), conductance ( $g_d$ ) and subthreshold slope (S). Split C-V measurements were carried out on 10x10  $\mu$ m<sup>2</sup> devices to calculate carrier effective mobility and capacitance equivalent thickness ( $t_{CET}$ ). The reason for using large area MOS devices for C-V measurements is that large area

capacitors are easier to measure.  $10x0.25~\mu\text{m}^2$  devices were used for the low-frequency noise measurements. For hot carrier stress and constant voltage stressing conditions  $10x0.1~\mu\text{m}^2$  devices were used.

## 2.3 Measurement Setup

The frequency range for low-frequency noise measurements was typically from 1Hz to 100 KHz. The low-frequency noise measurement technique requires sensing very weak signals. Therefore, it is necessary to minimize the internal noise other than 1/f noise as well as to prevent external interference. By using a battery to bias the device and shielding the device during measurements, we can prevent interference from power lines and other equipment.

The following sets of measurements were performed:

- DC characteristics

- Charge density and mobility extraction

- Low frequency noise

- Stressing

# 2.3.1 DC characteristics background and measurements:

# 2.3.1.1 DC characteristics background

Various MOSFET device performance parameters are required for noise analysis. Thus, DC characterization was always done prior to the noise measurements. Additionally, the DC measurements were repeated after the noise measurements to check if there is any change in the device parameters. A typical set of DC curves are shown in Figure 2.1 obtained using HP-4155C semiconductor parameter analyzer on TiN/2nm HfSiON n-channel MOSFET. From

the  $I_d$ - $V_d$  and  $I_d$ - $V_g$  curves, parameters like ac conductance  $(g_d = \partial I_d / \partial V_d)$ , transconductance  $(g_m = \partial I_d / \partial V_g)$ , subthreshold slope  $(S = \partial log(I_d) / \partial V_g)$  and the threshold voltage  $(V_l)$  were obtained.

#### 2.3.1.2 DC characteristics measurement

The first step in device evaluation was to perform DC characterizations, and measure the terminal currents versus applied voltage. For sensitive and accurate parameter measurements, the Source-Measure Units (SMU) of HP 4155C parameter analyzer is connected to on a shielded 8060 series MicroManipulator probe station with triax cables. Proper grounding of the probe station is ensured before start of the measurments. Precautions were also taken every time to protect the devices from possible voltage spikes or electro-static discharge (ESD).

Basic device parameters such as different terminal currents, drain  $(I_d)$ , source  $(I_s)$ , gate  $(I_g)$  and substrate  $(I_{sub})$ , as well as the terminal voltages were recorded. User defined functions were used to obtain  $V_{th}$ ,  $g_m \big( A/V \big) = \frac{dI_d}{dV_g}$ ,  $g_d \big( A/V \big) = \frac{dI_d}{dV_d}$  and  $S \big( Dec/V \big)$  of the devices.

Different DC characteristic data from 10x0.25  $\mu m^2$  HfSiO nMOSFET device are presented in Figures 2.1-2.3

Figure 2.1 Measured drain current as a function of gate voltage at different drain voltages.

Figure 2.2 Measured transconductance as a function of gate voltage at different drain voltages.

Figure 2.3 Drain current as a function of drain voltage at different gate voltages.

# 2.3.2 Charge density and mobility extraction:

# 2.3.2.1 Charge density and mobility extraction background

The inversion layer charge density and mobility values are needed for the noise analysis at different gate bias voltages, as explained in detail in Chapter 3. Mobility can also be extracted from the  $g_m$ . However, in ultra thin gate dielectric MOSFET devices, gate leakage current is a prominent phenomenon which leads to errors in the extracted MOSFET device parameters. Therefore, it is important to consider the effect of leakage current. Otherwise the mobility will be underestimated. To accurately determine the MOSFET inversion layer charge density and channel carrier mobility, split C-V measurements were performed. This split C-V measurement technique was originally suggested by Koomen [22].

The applied voltage at the MOSFET gate terminal is considered as the summation of surface potential ( $\psi_{x}$ ) and the potential across the gate oxide ( $V_{ox}$ ) i.e.,

$$V_g = \psi_s + V_{ox}$$

or  $V_g = \psi_s + \frac{Q_{sc}}{C_{ox}}$

$$Q_{sc} = Q_{inv} + Q_{bulk}$$

(2.3.1)

The device channel charge  $Q_{sc}$ , consists of  $Q_{inv}$  the inversion layer charge and  $Q_{bulk}$  charges in the bulk.

To get the channel capacitance,

$$\frac{d\psi_{s}}{dV_{g}} = \frac{C_{ox}}{C_{ox} + \frac{dQ_{inv}}{d\psi_{s}} + \frac{dQ_{bulk}}{d\psi_{s}}}$$

(2.3.2)

Therefore, gate to channel capacitance is given by,

$$C_{gc} = \frac{dQ_{inv}}{dV_g} = \frac{dQ_{inv}}{d\psi_s} \frac{d\psi_s}{dV_g} = \frac{\frac{dQ_{inv}}{d\psi_s} C_{ox}}{C_{ox} + \frac{dQ_{inv}}{d\psi_s} + \frac{dQ_{bulk}}{d\psi_s}}$$

(2.3.3)

whereas, the gate to bulk capacitance is given by differentiating the charges in the bulk with respect to gate voltage,

$$C_{gb} = \frac{dQ_{bulk}}{dV_g} = \frac{dQ_{bulk}}{d\psi_s} \frac{d\psi_s}{dV_g} = \frac{\frac{dQ_{bulk}}{d\psi_s} C_{ox}}{C_{ox} + \frac{dQ_{inv}}{d\psi_s} + \frac{dQ_{bulk}}{d\psi_s}}$$

(2.3.4)

The final expressions for gate to channel capacitance and gate to bulk capacitance are given by,

$$C_{gc} = \frac{C_{inv} C_{ox}}{C_{ox} + C_{inv} + C_{bulk}} ; \qquad C_{gb} = \frac{C_{bulk} C_{ox}}{C_{ox} + C_{inv} + C_{bulk}}$$

and,

$$C_g = C_{gc} + C_{gb}$$

Now, the charge can be found by integrating the capacitance,

$$Q_{inv} = \int_{-\infty}^{V_g} C_{gc}(V_g) dV_g \qquad \text{and} \qquad Q_{bulk} = \int_{-V_g}^{\infty} C_{gb}(V_g) dV_g$$

The effective mobility can then be expressed in the following way,

$$\mu_{eff} = \frac{g_d}{(W/L) Q_{inv}}$$

(2.3.5)

For the mobility in the linear region of MOSFET operation,  $g_d$  is obtained by biasing the drain end at very low voltage, generally at 10-20 mV.

### 2.3.2.2 Charge density and mobility extraction measurements

After the completion of the DC parameter extraction, the split C-V measurements were done on  $10x10~\mu\text{m}^2$  devices using a HP 4284 LCR meter. First, the DUT (Device Under Test) was connected to the LCR meter. To minimize the contribution of the capacitance from interface traps, the operating frequency must be high enough. Parallel circuit mode (Cp-D) was selected from LCR meter because of the small channel capacitance. Before taking C-V measurements, both open and short corrections were performed. The high potential and high current ports as well as low potential and low current ports were shorted together. Furthermore, the length of the

shorting wires and the distance from the device leads were kept small to minimize the stray capacitance effects as much as possible. As shown in the Fig 2.4, the gate was connected to the high potential, the drain and source terminals were shorted and connected to the low potential ports. The contribution from the bulk charges was reduced by connecting the substrate to the ground terminal. The theory and details of the procedure and measurement setup can be found in a report by Siva Prasad Devireddy [23].

Since high-k gate dielectrics were used here, the gate leakage was at least an order of magnitude lower than the drain current even at the highest gate overdrive. If significant gate leakage currents are observed, appropriate corrections can be made as suggested in [24,25].

Figure 2.4 Split C-V measurement set up for MOSFET device. HT, LT and GT are high terminal, low terminal and ground terminal respectively [22].

The C-V measurement set up was controlled by a Lab-VIEW program through GPIB interface with the LCR meter. The gate voltage was varied from -1.5 V to 1.5 V, with 10 mV step increments. As mentioned earlier, higher frequency measurements will eliminate the capacitance contribution from the interface traps. Therefore, 1MHz frequency was chosen. The C-V parameters were extracted as following. From the experimental data,  $C_{gc}$  was measured. This was followed by measurement of stray capacitance,  $C_{overlap}$  from the sub-threshold region. Finally, the stray capacitance measured from sub-threshold region ( $C_{overlap}$ ) is subtracted from the measured capacitance to get the net channel capacitance  $C_{gc}$ . A typical channel capacitance vs. gate voltage curve is shown in Figure 2.5 for an nMOSFET. Later, the inversion charge is calculated by the equation given below,

$$Q_{inv} = \int_{0}^{V_g} C_{gc} dV_g$$

(2.3.6)

Now, using equation (2.3.5), the effective mobility can be written as,

$$\mu_{eff} = I_d L / W Q_{inv} V_d \tag{2.3.7}$$

The above equation can be used to extract the effective mobility in both linear and saturation regions. In addition,  $t_{CET}$  can be calculated using the following equation:

$$t_{CET} = (\varepsilon_0 * 3.9)/C_{gc} \tag{2.3.8}$$

Figure 2.5 Corrected gate to channel capacitance of TiN/HfSiON nMOSFET from split C-V measurement and calculated channel inversion charge are shown here.

# 2.3.3 Low frequency noise background and measurements:

# 2.3.3.1 Low frequency noise background

In low frequency noise measurements, the power spectral density is the quantity that is preferably measured instead of noise power, since the spectral shape also provides very important information. Internal noise as well as external interference is needed to be minimized to get the reliable low frequency noise results. Even if the interference can be reduced to an acceptable level, the measurement might not still be accurate. One important thing to remember

is the noise response from the other circuit elements (i.e. bias box, connecting wires, preamplifier etc.) in the noise set up must be much lower than the noise response from the DUT. It is, therefore, primarily important to minimize the noise of the other elements in the setup. Appropriate shielding should be used for the part of the setup where the desired signal is sensitive to interference. Rechargeable batteries should be utilized as a power source to avoid noise contribution from the biasing circuitry. A low noise amplifier is used to amplify the weak signal before being fed into the spectrum analyzer. However, the amplifier inevitably adds its own internal noise to the signal. Therefore, the internal noise of the amplifier sets the measurement limit of the system and must be minimized. A spectrum analyzer measures and analyzes the signal in the frequency domain. Modern spectrum analyzers utilize discrete Fast Fourier Transform (FFT) algorithms to convert the measured signal from the time domain to the frequency domain. Most spectral analyzers have several choices of window functions to make the signal periodic in the time record. The most common types of windows are Hanning, rectangular, Gaussian top and flattop windows. Each window has different advantages and disadvantages. The Hanning window provides a good frequency resolution; therefore, it is used for low frequency noise measurements in this work.

### 2.3.3.2 Low frequency noise measurement

Wafer level low frequency noise measurements were performed at room temperature using an enclosed low noise 8060 series MicroManipulator probe station with proper grounding. The noise measurement set-up includes a DC bias box, an EG&G PAR113 pre-amplifier and a HP 3562A dynamic signal analyzer. Rechargeable Ni-Cd battery was used for DC bias box. Several batteries are connected together to get required bias for drain and gate terminal for the MOSFET. The drain and gate voltage was controlled by a variable resistor. The pre-amplifier, to amplify the drain voltage fluctuation, was battery powered. The frequency range in the pre-

amplifier and voltage gain were set in 0.03 Hz-300 kHz and 1000 respectively with input terminal in AC coupled mode. The output from the pre-amplifier was feed into the HP 3562A dynamic signal analyzer. Averaging must be used for reliable noise measurements. In this work 30 averages were used with 90 % data overlapping. The analyzer was set to evaluate the power spectral density of the voltage noise in V<sup>2</sup>/Hz units in 1 Hz- 100 kHz frequency range. Fig. 2.6 shows the overall LFN measurement set up.

Contributions from stray noise sources are minimized by taking above precautions. For MOSFET noise measurements, the source and the substrate terminals are always shorted. Preamplifier's inherent noise and channel thermal noise are considered by taking background noise before each noise measurement at a particular gate overdrive. This is done by applying zero voltage at the drain end. Later, this background noise is subtracted from the noise measurement to the net 1/f noise.

Reliable noise measurements require some knowledge and expertise due to the difficulty in measuring weak noise signals. Therefore, the following steps are suggested for reliable low frequency noise measurements.

- Turn off unused equipment that might disturb the measurement.

- Use preamplifier with low internal noise

- Use metal film resistors and DC batteries in the bias circuitry for lowest noise.

- Sometimes bad contacts due to worn-out probes or too gentle probing force can introduce noise that exceeds noise from DUT.

- Wireless and mobile phones should not be used in the vicinity of the measurement setup.

Even switching of lights and equipment introduces disturbance in the low frequency range.

### 2.3.4 Hot carrier stress background and measurements:

#### 2.3.4.1 Hot carrier stress background

Hot carriers (electrons or holes) are of concern in integrated circuits, because electrons and/or holes that gain energy in an electric field can be injected into the oxide to become oxide trapped charge, they can drift through the oxide, causing gate current, they can create interface traps, and they can generate photons [26]. The carrier temperature T and energy E are related through the expression E = kT, here k is Boltzman constant. At room temperature,  $E \approx 25$  meV for T = 300 K. When carriers gain energy by being accelerated in an electric field, their energy E increases. For example,  $T = 1.2 \times 10^4$  K for E = 1 eV. Hence the name hot carriers means energetic carriers, not that the entire device is hot. Let us briefly discuss the effects of hot carriers. During hot carrier stressing, some of the electrons in the channel entering the drain space-charge region experience impact ionization. The resulting hot carriers can be injected into the oxide  $(N_{ot})$ , can flow through the oxide  $(I_G)$ , can generate interface traps  $(D_{it})$ , flow to the substrate contact as  $I_{sub}$ , and create photons [26]. The photons, in turn, can propagate into the device, be absorbed, and create electron-hole pairs.  $N_{ot}$  and  $D_{it}$  lead to threshold voltage changes and mobility degradation. The substrate current causes a voltage drop in the substrate, forward biasing the source-substrate junction, leading to further impact ionization and possibly snapback breakdown. The device can be viewed as a parasitic bipolar junction transistor (BJT) in parallel with the MOSFET. The BJT has an almost open base and open base BJTs often exhibit snapback breakdown with negative differential resistance. Almost open base means the

base potential is not well controlled and although the base contact is grounded, the interior base has an ill-defined potential.

Figure 2.6 An overview of the low frequency noise measurement system.

The popular method to determine hot carrier degradation in conventional  $SiO_2$  based n-channel devices is to bias the device at maximum substrate current. The substrate current depends on the channel lateral electric field. At low  $V_G$ , with the device in saturation, the lateral