# ROOM-TEMPERATURE SINGLE-ELECTRON DEVICES BASED ON CMOS FABRICATION TECHNOLOGY

by

# VISHVA RAY

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT ARLINGTON

December 2008

Copyright © by Vishva Ray 2008

All Rights Reserved

#### **ACKNOWLEDGEMENTS**

I thank my supervisor, mentor, and guide, Dr. Seong Jin Koh, for encouraging me to pursue a topic of my choice and helping me in every possible way. I owe my perseverance to Dr. Koh, who was extremely helpful in exposing me to new challenges all the way through. Without his active help and support this thesis could not have been written.

I also thank my group members – Ram, Jason, Charles, and Pradeep, who encouraged me all the way though, helping me actively in my projects, day in and day out. They were there to help me out whenever I needed them, even at the wee hours of the night. Their sacrifices and contribution are immeasurable.

I owe my spirit of hard work to my father and my ability to remain calm in spite of everything (failed experiments, upcoming deadlines, which are integral parts of graduate studies) to my mother. They both helped me in my research even if they were not present physically by my side. I thank Urmi, my little sister, who has taught me optimism and how to be humble even at times of massive accomplishments.

My special appreciation goes to Didi, who taught me the ways of survival and achievement in an alien world. She was a woman of high hopes, positive thinking and hard work – all of which have gone into the making of this thesis. Unfortunately, she is not there anymore to share my achievement with me today.

Last but not least, I thank Kamalika, my wife, for enduring my irregular working hours as a graduate student. Her emotional support was of immense help.

Finally I would like to thank Noir, the godsend gift that I received just a little over a month prior to my submission of this thesis, who made my last grueling days fun, enjoyable, and relaxing.

This study was supported by the Office of Naval Research under Grant No. N00014-05-1-0030, by the National Science Foundation under Grant No. ECS-0449958, and by the Texas Higher Education Coordinating Board under Grant No. 003656-0014-2006.

August 25, 2008

#### **ABSTRACT**

# ROOM-TEMPERATURE SINGLE-ELECTRON DEVICES BASED ON CMOS FABRICATION TECHNOLOGY

# Vishva Ray, PhD

## The University of Texas at Arlington

Supervising Professor: Seong Jin Koh

Single-electron devices, in which the transport and storage of individual electrons is precisely controlled, have many potential benefits in the field of electronics, optics, and sensors. Fabrication of these devices requires the arrangement of device components (Coulomb island, source, drain, and gate electrodes) with nanometer scale precision. Although several methods have successfully demonstrated single-electron behavior, large-scale fabrication of single-electron devices has not been possible.

This research aims to -

- Come up with a method which would allow the fabrication of single-electron devices on a large scale,

- Make the fabrication method compatible with current CMOS technology, and,

- Enable room-temperature operation of the single-electron devices.

A major achievement of this research has been the creation of a new single-electron device structure within the framework of current CMOS technology which has allowed for the fabrication of single-electron devices on a large scale and in parallel process. This was made possible by employing a vertical electrode configuration where the source and the drain electrodes were separated by a thin layer of dielectric medium (~10 nm). Next, Coulomb islands

V

were attached to the exposed sidewalls of the dielectric film using a combination of colloidal and surface chemistry. Individually addressable gate electrodes were then incorporated in devices, also in complete parallel processing.

Subsequent I-V measurements of these devices have yielded Coulomb blockade, Coulomb staircase, and Coulomb oscillations at room temperature and at low temperature. A systematic study of the single-electron charging/tunneling was carried out utilizing different sizes of Coulomb islands. The dependence of the nature of the Coulomb blockade and Coulomb staircase on nanoparticle size, temperature, and location of the Coulomb island were also investigated. Simulations based on the orthodox theory are in excellent agreement with the experimental results.

Another challenge toward the realization of nanoscale devices is to develop a technique which enables an accurate and reliable positioning of nanostructures onto the targeted locations. Combining wet chemistry and CMOS fabrication technology, a method was developed which enables precise positioning of nanoparticles in the gap between two electrodes. Such precise positioning of nanoparticles could be utilized to improve the yield of single-electron devices.

# TABLE OF CONTENTS

| ACKNOWLEDO    | GEMENTS                                                                          | iii  |

|---------------|----------------------------------------------------------------------------------|------|

| ABSTRACT      |                                                                                  | V    |

| LIST OF ILLUS | TRATIONS                                                                         | xi   |

| LIST OF TABLE | ES                                                                               | xxi  |

| Chapter       |                                                                                  | Page |

| 1.            | INTRODUCTION                                                                     | 1    |

|               | 1.1 Overview                                                                     | 1    |

|               | 1.2 Single-electron devices                                                      | .2   |

|               | 1.3 Organization of this thesis                                                  | 4    |

| 2.            | THEORY OF SINGLE-ELECTRON TUNNELING                                              | 6    |

|               | 2.1 Introduction                                                                 | 6    |

|               | 2.2 Tunnel junction                                                              | 7    |

|               | 2.3 Double junction single-electron device                                       | .8   |

|               | 2.3.1 Coulomb blockade in a double junction single-electron device               | .22  |

|               | 2.3.2 Coulomb staircase in a double junction single-electron device              | .35  |

|               | 2.4 Charging energy of a double junction single-electron device                  | 68   |

|               | 2.5 Electron transport in single-electron transistors                            | .71  |

|               | 2.5.1 Stability diagram of a single-electron transistor                          | 89   |

|               | 2.5.2 Charging energy of a single-electron transistor                            | 96   |

|               | 2.5.3 Coulomb oscillations in a single-electron transistor                       | 97   |

|               | 2.5.4 Interval between Coulomb oscillation peaks in a single-electron transistor | 103  |

|    | 2.6 Orthodox theory of single-electron tunneling             | 04 |

|----|--------------------------------------------------------------|----|

|    | 2.6.1 Electron tunneling rate through tunnel junctions10     | 05 |

| 3. | NEW SINGLE-ELECTRON DEVICE STRUCTURE10                       | 80 |

|    | 3.1 Introduction                                             | 80 |

|    | 3.2 History of single-electron devices10                     | 80 |

|    | 3.2.1 Recent advancements in the field of single electronics | 11 |

|    | 3.3 New single-electron device structure1                    | 14 |

| 4. | FABRICATION OF SINGLE-ELECTRON DEVICES                       | 18 |

|    | 4.1 Introduction                                             | 18 |

|    | 4.2 Thermal oxidation                                        | 18 |

|    | 4.3 Deposition of the source electrodes                      | 19 |

|    | 4.4 Deposition of the silicon dioxide dielectric film        | 21 |

|    | 4.5 Deposition of the drain electrodes                       | 21 |

|    | 4.5.1 Etching of the PECVD SiO <sub>2</sub> film             | 22 |

|    | 4.6 Attachment of Au nanoparticles                           | 24 |

|    | 4.7 Deposition of gate electrodes                            | 26 |

|    | 4.8 Deposition of bond pads for single-electron devices      | 28 |

|    | 4.8.1 Formation of vias12                                    | 28 |

|    | 4.8.2 Deposition of the bond pads12                          | 29 |

|    | 4.9 Mounting individual dies on a chip carrier13             | 31 |

|    | 4.10 Device wire bonding                                     | 33 |

| 5. | ELECTRICAL CHARACTERIZATION OF SINGLE-ELECTRON DEVICES       | 37 |

|    | 5.1 Introduction                                             | 37 |

|    | 5.1.1 Room temperature measurement set-up14                  | 40 |

|    | 5.1.2 Low temperature measurement set-up                                                                          | 142 |

|----|-------------------------------------------------------------------------------------------------------------------|-----|

|    | 5.2 Coulomb staircase in a double junction single-electron device using 10 nm Au nanoparticles                    | 155 |

|    | 5.3 Coulomb staircase in a double junction single-electron device using 20 nm Au nanoparticles                    | 159 |

|    | 5.4 Coulomb blockade in a double junction single-electron device using 10 nm Au nanoparticles                     | 164 |

|    | 5.5 Coulomb blockade/staircase statistics for double junction single-electron devices with 10 nm Au nanoparticles | 167 |

|    | 5.6 Single-electron transistors using 10 nm Au nanoparticles                                                      | 169 |

|    | 5.7 Statistics of Coulomb oscillations in single-electron transistors                                             | 177 |

| 6. | ELECTROSTATIC FUNNELING FOR PRECISE NANOPARTICLE PLACEMENT                                                        | 179 |

|    | 6.1 Introduction                                                                                                  | 179 |

|    | 6.2 Concept of Electrostatic Funneling                                                                            | 183 |

|    | 6.3 Experimental procedures for electrostatic funneling                                                           | 186 |

|    | 6.4 Effectiveness of electrostatic funneling                                                                      | 188 |

|    | 6.5 Interaction between charged surfaces and nanoparticles in an aqueous medium                                   | 193 |

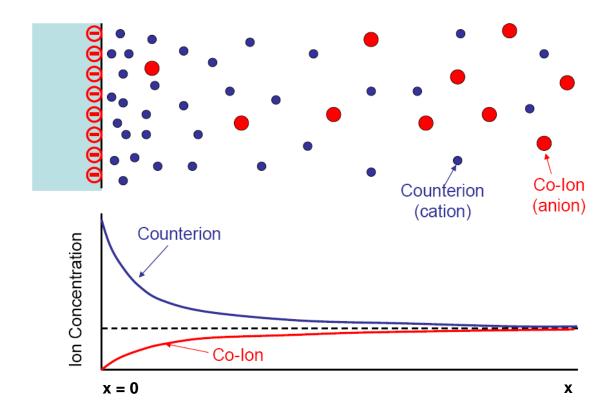

|    | 6.5.1 The electric double layer                                                                                   | 193 |

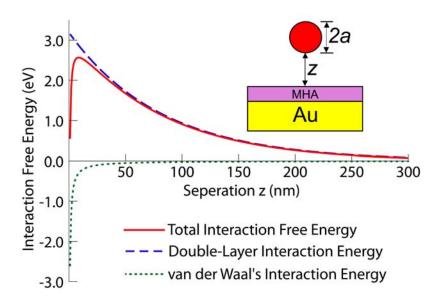

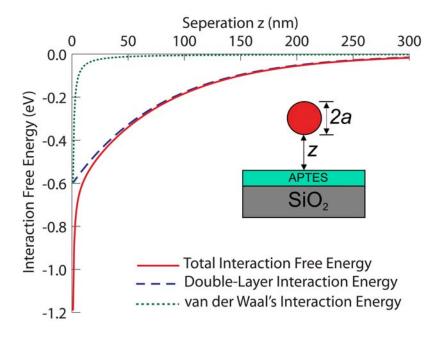

|    | 6.5.2 Calculation of double layer interaction energies                                                            | 196 |

|    | 6.5.3 Calculation of effective reduced surface potentials                                                         | 197 |

|    | 6.5.4 Calculation of effective reduced surface potentials for planar geometry                                     | 198 |

|    | 6.5.5 Calculation of effective reduced surface potentials for spherical geometry                                  | 200 |

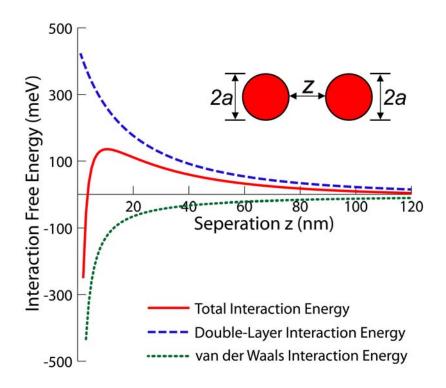

|    | 6.5.6 Calculation of total interaction energies                                                                   | 203 |

|       |         | 6.6 Interaction between two identical nanoparticles in an aqueous medium                 | . 206 |

|-------|---------|------------------------------------------------------------------------------------------|-------|

|       |         | 6.7 Application of electrostatic funneling in the fabrication of single-electron devices | 208   |

|       | 7.      | CONCLUSION                                                                               | 212   |

| Appen | dix     |                                                                                          |       |

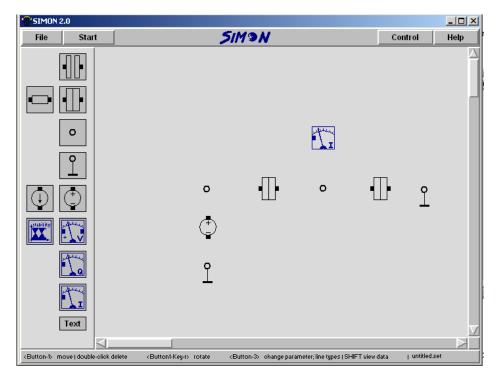

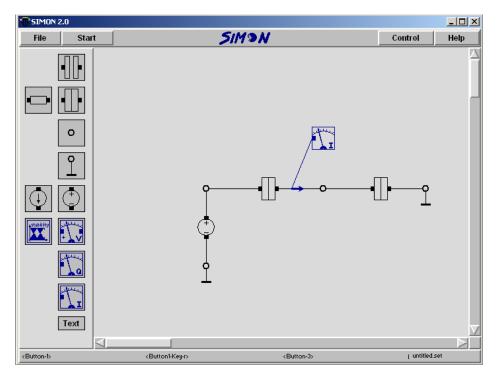

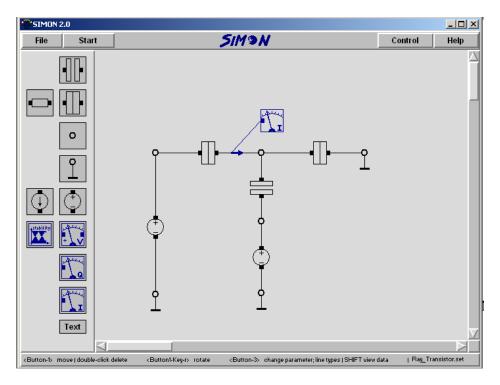

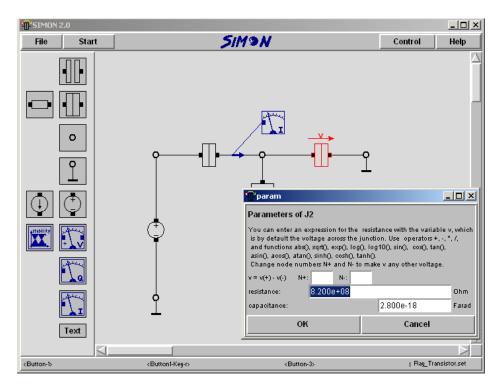

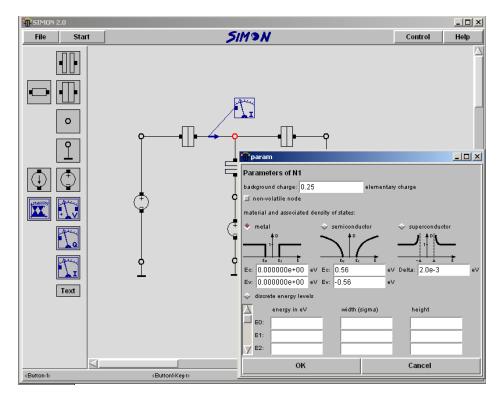

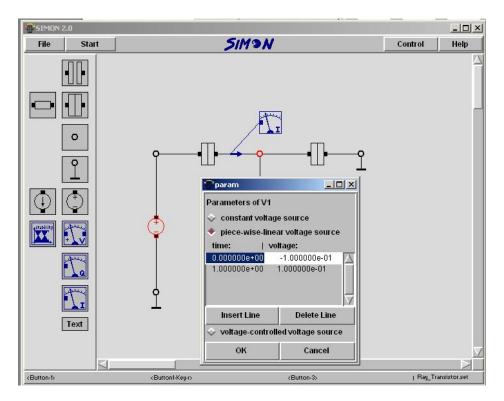

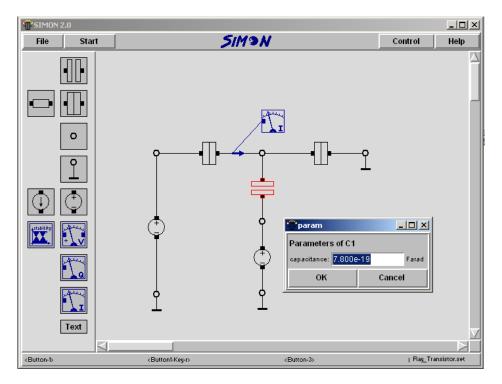

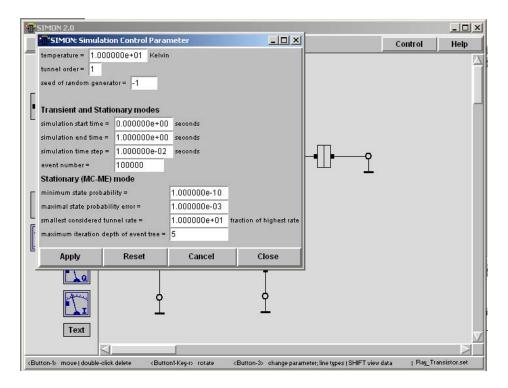

|       | A. SIM  | ULATION OF SINGLE-ELECTRON DEVICES USING SIMON                                           | 214   |

| REFE  | RENCES  | S                                                                                        | . 227 |

| BIOGE | RAPHICA | AL INFORMATION                                                                           | 234   |

# LIST OF ILLUSTRATIONS

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

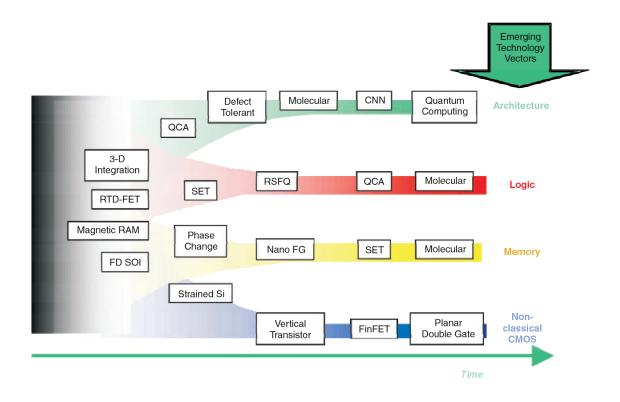

| 1.1    | Emerging technology sequence of the Engineering, Research and Developement section of the International Technology Roadmap for Semiconductors                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3    |

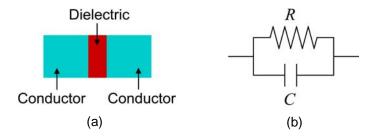

| 2.1    | (a) Schematic of a tunnel junction (b) Equivalent circuit of a tunnel junction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .7   |

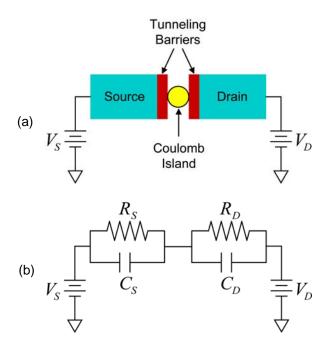

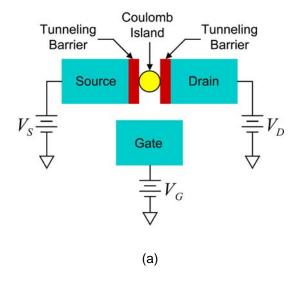

| 2.2    | Schematic of a double junction single-electron device. (a) Schematic arrangement of single-electron device components (i.e., source electrode, drain electrode, and Coulomb island). The Coulomb island is separated from the electrodes by tunnel barriers. (b) The equivalent circuit of a double junction single-electron device which can be represented as two tunnel junctions connected in series. $R_S$ , $C_S$ , and $R_D$ , $C_D$ denote the resistances and capacitances of the tunnel junctions between the source electrode and the island, and between the drain electrode and the island, respectively | .9   |

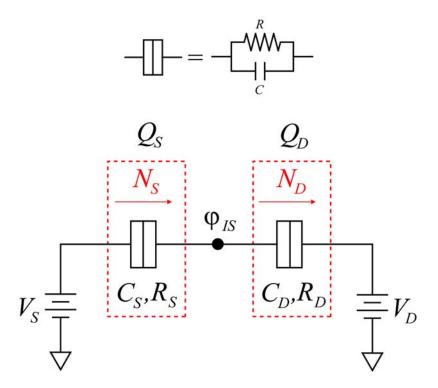

| 2.3    | Equivalent circuit diagram of a double junction single-electron device. The two tunnel junctions are shown in the dashed red boxes. $Q_{S}$ and $Q_{D}$ are the capacitor charges, $V_{S}$ and $V_{D}$ are the voltage sources connected to the source electrode and drain electrode, respectively, and $N_{S}$ and $N_{D}$ are the integer number of electrons which have tunneled across the junction between the source and the island, and the island and the drain, respectively. $\varphi_{IS}$ is the electrostatic potential of the Coulomb island                                                            | .13  |

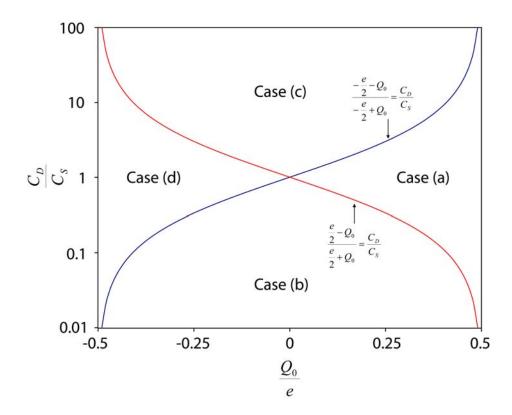

| 2.4    | Numerically plotted $\frac{C_D}{C_S}$ vs $\frac{Q_0}{e}$ curves for Cases (a) – (d) described by equations (2.40) (a) – (d) in Section 2.3.1. These curves are obtained by solving the inequalities derived in equations (2.41) (a) – (h)                                                                                                                                                                                                                                                                                                                                                                             | .29  |

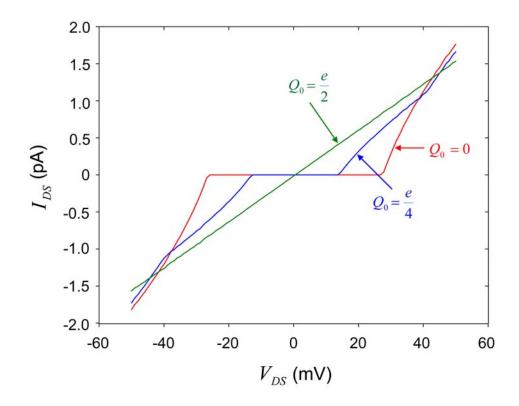

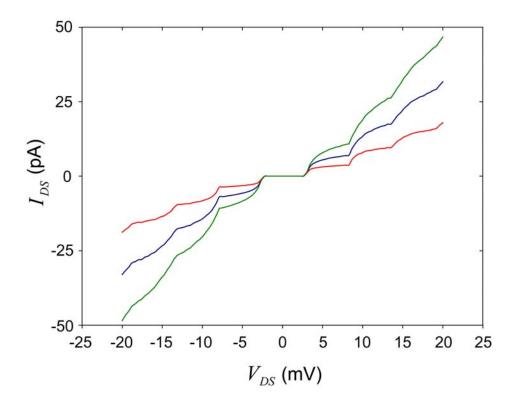

| 2.5    | Simulated I-V characteristics of a double-junction single-electron device showing the effect of $Q_0$ on the width of the Coulomb blockade. Red: Simulated I-V characteristics of a double-junction single-electron device using $C_S=C_D=3aF$ , $R_S=R_D=8G\Omega$ , $Q_0=0$ , and $T=0K$ . Blue: Simulated I-V characteristics of a double-junction single-electron device using $C_S=C_D=3aF$ ,                                                                                                                                                                                                                    |      |

|     | $R_{\scriptscriptstyle S}=R_{\scriptscriptstyle D}=8G\Omega$ , $Q_{\scriptscriptstyle 0}=rac{e}{\varLambda}$ , and $T=0K$ . Green: Simulated I-V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | characteristics of a double-junction single-electron device using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | $C_S=C_D=3aF$ , $R_S=R_D=8G\Omega$ , $Q_0=\frac{e}{2}$ , and $T=0K$ 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

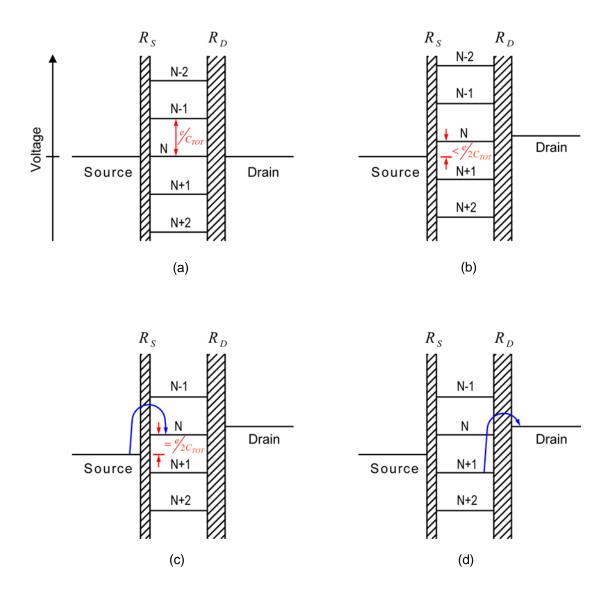

| 2.6 | Schematic of the mechanism of current flow in an asymmetric ( $C_D > C_S$ and $R_D >> R_S$ ; $C_D R_D >> C_S R_S$ ) double junction single-electron device. (a) When no source-drain bias is applied. (b) When a small source-drain bias is applied such that it is not enough to add an electron to the island. The device is under the Coulomb blockade regime. (c) Application of a suitable source-drain bias causes an electron to tunnel into the island from the source electrode. (d) The asymmetry causes the island to retain the extra electron till it can go back to the ground state when the electron tunnels out of the island into the drain electrode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

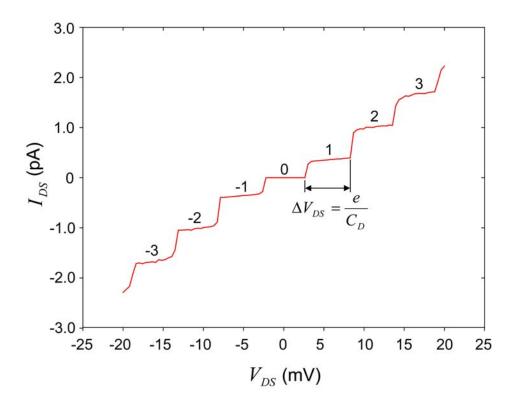

| 2.7 | Simulated I-V characteristics of an asymmetric double junction single-electron device showing the existence of the Coulomb staircase. The simulation parameters are $C_S=3aF$ , $C_D=30aF$ , $R_S=80M\Omega$ , $R_D=8G\Omega$ and $Q_0=0$ . The simulation was done at $T=0K$ . Since $C_D>C_S$ , the width of the Coulomb staircase $\Delta V_{DS}=\frac{e}{C_D}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.8 | Simulated I-V characteristics of an asymmetric double junction single-electron device showing the presence of a Coulomb staircase. The asymmetry is formed by keeping $C_S=C_D=C$ and $R_D>>R_S$ such that $R_DC_D>>R_SC_S$ . The simulation parameters are: Red: $C_S=C_D=3aF$ , $R_S=80M\Omega$ , $R_D=240M\Omega$ , $Q_0=0$ , and $T=0K$ . Blue: $C_S=C_D=3aF$ , $R_S=80M\Omega$ , $R_D=400M\Omega$ , $Q_0=0$ , and $Q_0$ |

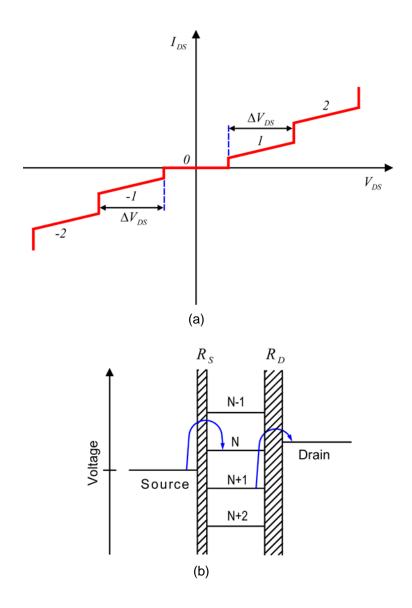

| 2.9 | Schematic of Coulomb staircase in an asymmetric double junction single-electron device with $C_D > C_S$ and $R_D >> R_S$ such that $C_D R_D >> C_S R_S$ . (a) Schematic of the $I_{DS}$ - $V_{DS}$ characteristics showing electron occupancy in the Coulomb island as a function of the applied source-drain bias $V_{DS}$ . (b) The voltage diagram of this device depicting the sequence of electron tunneling into and out of the island for a positive applied $V_{DS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

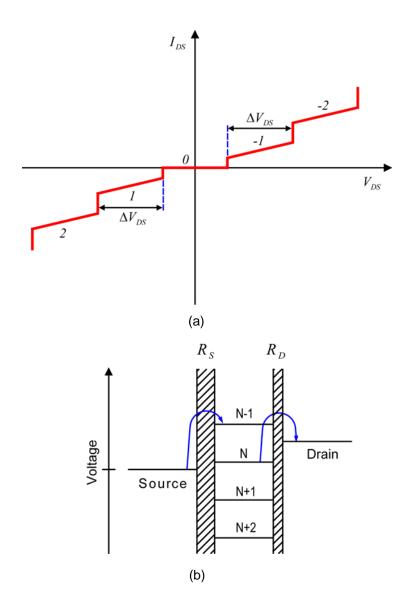

| 2.10 | Schematic of Coulomb staircase in an asymmetric double junction single-electron device with $C_S > C_D$ and $R_S >> R_D$ such that                                                                                                                                                                                                                      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | $C_S R_S >> C_D R_D$ . (a) Schematic of the $I_{DS}$ - $V_{DS}$ characteristics                                                                                                                                                                                                                                                                         |

|      | showing electron occupancy in the Coulomb island as a function of                                                                                                                                                                                                                                                                                       |

|      | the applied source-drain bias $V_{\scriptscriptstyle DS}$ . (b) The voltage diagram of this                                                                                                                                                                                                                                                             |

|      | device depicting the sequence of electron tunneling out of and into                                                                                                                                                                                                                                                                                     |

|      | the island for a positive applied $V_{\it DS}$                                                                                                                                                                                                                                                                                                          |

| 2.11 | Simulated I-V characteristics of an asymmetric double junction single-electron device corresponding to Case (c) in Table 2.1 showing the existence of the Coulomb staircase. The simulation parameters are $C_{\scriptscriptstyle S}=3aF$ , $C_{\scriptscriptstyle D}=9aF$ , $R_{\scriptscriptstyle S}=80M\Omega$ , $R_{\scriptscriptstyle D}=4G\Omega$ |

|      | and $Q_0=0$ . The simulation was done at $T=0K$ . The width of the                                                                                                                                                                                                                                                                                      |

|      |                                                                                                                                                                                                                                                                                                                                                         |

|      | Coulomb blockade is $\frac{e}{C_D}$ = $17.8 mV$ . Also, the width of the Coulomb                                                                                                                                                                                                                                                                        |

|      | staircase is equal to $\frac{e}{C_D} = 17.8 mV$                                                                                                                                                                                                                                                                                                         |

| 2.12 | Schematic of a single-electron transistor. (a) Schematic arrangement of single-electron transistor components (i.e., source electrode, drain electrode, gate electrode, and Coulomb island).                                                                                                                                                            |

|      | (b) The equivalent circuit of a single-electron transistor. $R_{\scriptscriptstyle S}$ , $C_{\scriptscriptstyle S}$ ,                                                                                                                                                                                                                                   |

|      | and $R_{\scriptscriptstyle D}$ , $C_{\scriptscriptstyle D}$ denote the resistances and capacitances of the tunnel                                                                                                                                                                                                                                       |

|      | junctions between the source electrode and the Coulomb island, and between the Coulomb island and the drain electrode, respectively, while <i>C</i> denotes the capacitance of the gate which is coupled to the                                                                                                                                         |

|      | while $C_G$ denotes the capacitance of the gate which is coupled to the                                                                                                                                                                                                                                                                                 |

|      | Coulomb island. The gate is connected to a separate voltage source $V_{\scriptscriptstyle G}$ 72                                                                                                                                                                                                                                                        |

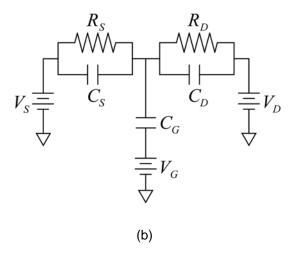

| 2.13 | Schematic of a stability diagram of a single-electron transistor.                                                                                                                                                                                                                                                                                       |

|      | The shaded areas of the trapezoids correspond to the regions                                                                                                                                                                                                                                                                                            |

|      | where no tunneling through either junction may occur, thus putting the device in the Coulomb blockade regime. The red lines forming                                                                                                                                                                                                                     |

|      | the boundaries of the trapezoids represent the onset of                                                                                                                                                                                                                                                                                                 |

|      | tunneling in the device                                                                                                                                                                                                                                                                                                                                 |

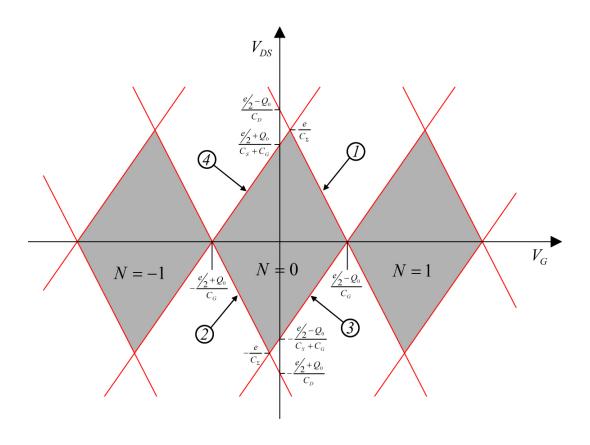

| 2.14 | Electrostatic potential diagrams of a single-electron transistor. (a) Single-electron transistor under Coulomb blockade regime under the application of a small source-drain bias and zero gate bias. (b) The application of a suitable positive gate voltage $V_{\it G}$ increases                                                                     |

|      | the potential of the Coulomb island causing a single electron to tunnel                                                                                                                                                                                                                                                                                 |

|      | into the island from the source electrode. (c) The extra electron tunnels out of the Coulomb island into the drain electrode and brings the island back to its original charge state. (d) Conductance versus gate voltage                                                                                                                               |

|      | characteristics of a single-electron transistor. Arrow 1 denotes                                                                                                                                                                                                                                                                                        |

|      | peak where the electron occupancy in the island changes by one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 99  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

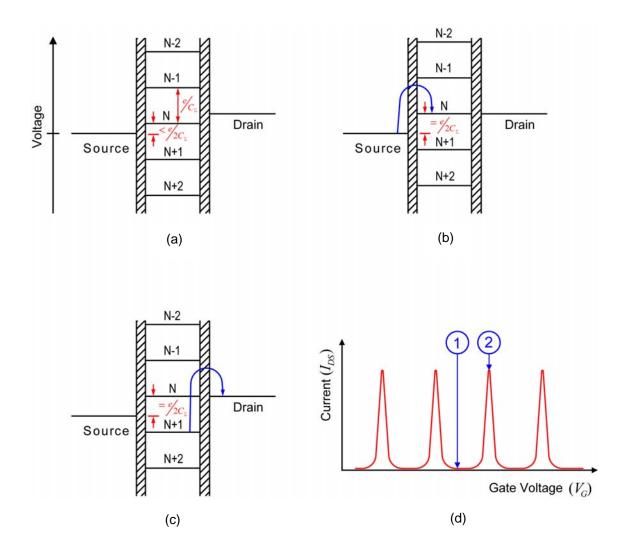

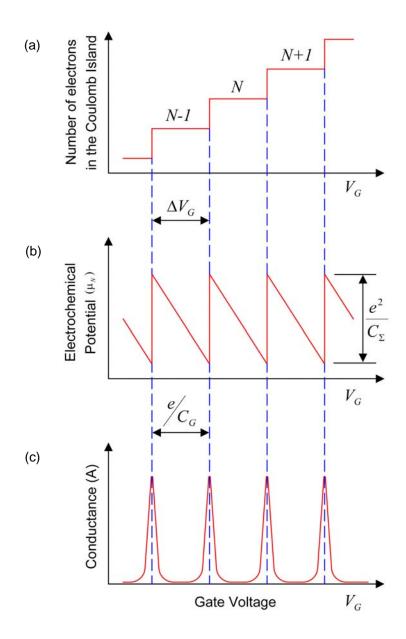

| 2.15 | (a) Electron occupation in the Coulomb island as a function of the applied gate voltage $(V_G)$ . The actual charge state of the Coulomb island is quantized and increases in a step-wise manner with $V_G$ . (b) Electrochemical potential $(\mu_N)$ of the island as a function                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|      | of $V_{\scriptscriptstyle G}$ . (c) Conductance of the single electron transistor as a function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|      | of ${\cal V}_{\cal G}$ . The peaks (non-zero current) in the plot are Coulomb oscillations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|      | which are observed only when the electron occupancy in the island changes by one electron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 102 |

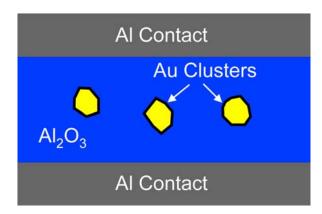

| 3.1  | A cross section of embedded metal clusters such as Au in a dielectric medium. The ends of the dielectric film are connected to conducting electrodes for applying a bias from an external source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 110 |

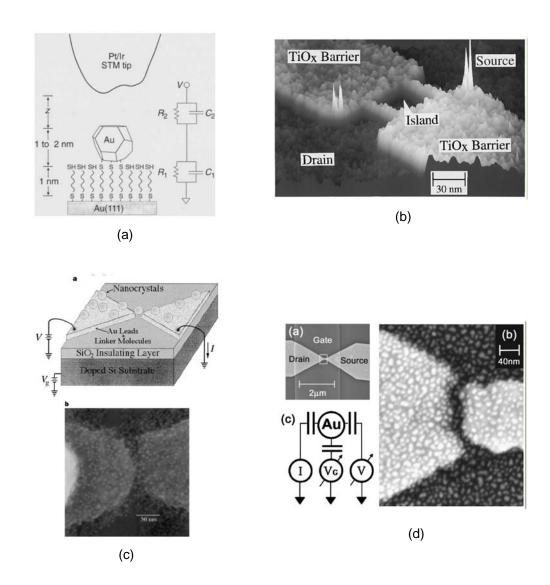

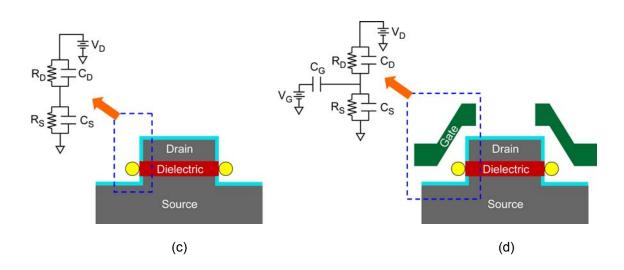

| 3.2  | Approaches adapted for the fabrication of single-electron devices.  (a) The use of a scanning tunneling microscope (STM) to study single-electron transport phenomena [3.11]. (b) The use of a STM for nano-oxidation of metallic Ti films to fabricate single-electron transistors [3.12]. (c) The use of a combination of e-beam lithography and shadow mask evaporation to fabricate single-electron transistor using CdSe nanoparticles [3.13]. (d) Fabrication of single-electron transistors by using electromigration to create nanometer scale source-drain electrode gap [3.14]                                                                                                                                                                  | 113 |

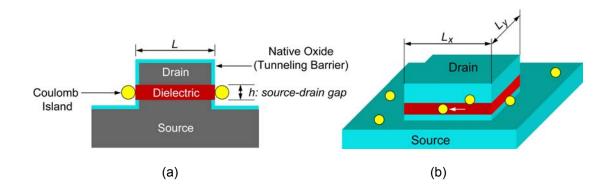

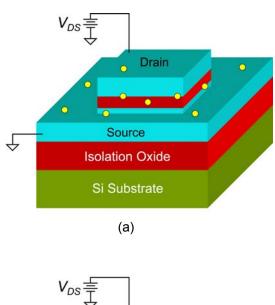

| 3.3  | Schematic of the new single-electron device structure (a) Vertical arrangement of the source and the drain electrodes. The thickness of the intervening dielectric film ( $h$ ) defines the source-drain electrode gap. (b) Isometric view of the single-electron device structure. The source and the drain electrodes are self-aligned so that the gap between the source and the drain is uniform along the periphery of the device. The lateral dimensions ( $L_x$ and $L_y$ ) can be of any dimension since the electron transport takes places only through an island positioned on the side-wall of the exposed dielectric layer (c) Schematic of a double junction single-electron tunneling device and its equivalent circuit (d) Schematic of a |     |

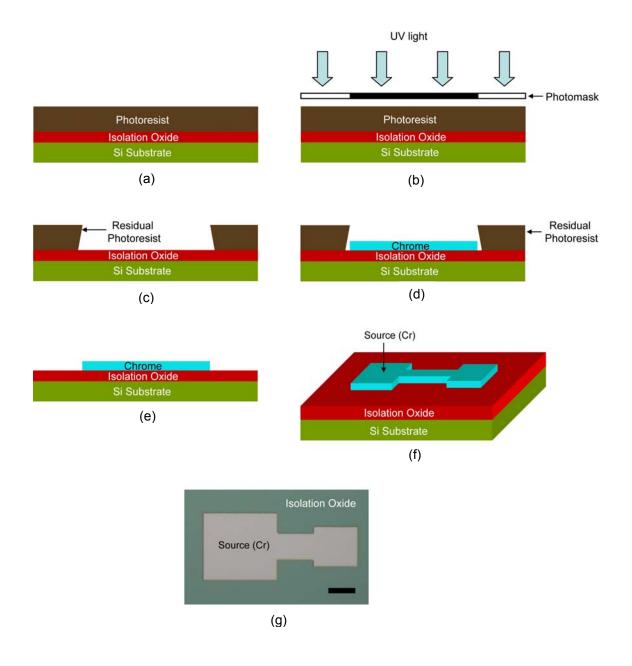

| 4.1  | Deposition of the source electrodes. (a) Negative photoresist is spun onto the substrate and baked. (b) The wafers are exposed to UV light through photomask followed by a post-exposure bake. (c) Unexposed resist is removed by the developer. (d) Chrome is evaporated onto the samples. (e) Lift-off is done in acetone. (f) 3-dimensional schematic showing the profile of the source electrode. (g) Top view of a source electrode taken with an optical microscope. Scale bar = 100 μm.                                                                                                                                                                                                                                                            |     |

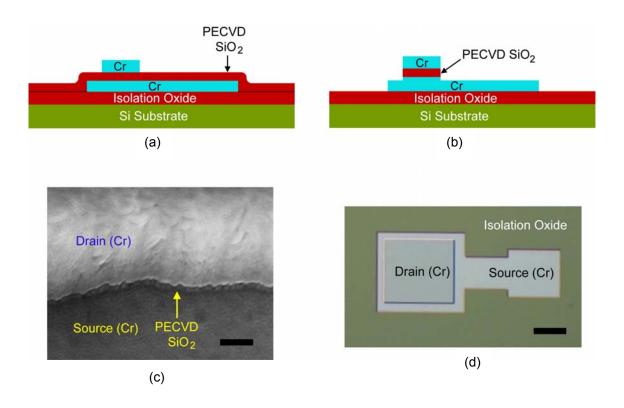

| 4.2 | Deposition of the drain electrodes. (a) Schematic arrangement of the drain on top of the source electrode. The source and the drain electrodes are separated by the dielectric film of $SiO_2$ deposited by PECVD process. (b) The intervening layer of $SiO_2$ film between the electrodes is etched away using the drain electrode as the hard mask. The $SiO_2$ film that remains underneath the drain electrodes defines the gap between the source and the drain electrodes in the single-electron device structure. (c) SEM image of the device side-wall after the $SiO_2$ film has been etched. The yellow arrow indicates the remaining portion of the $SiO_2$ film which creates a uniform and nanometer scale gap between the source and the drain electrodes. Scalebar = 100 nm. (d) Optical microscope image (top view) of the single-electron device structure showing the arrangement of the drain electrode on top of the source electrode. Scalebar = 100 $\mu$ m |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

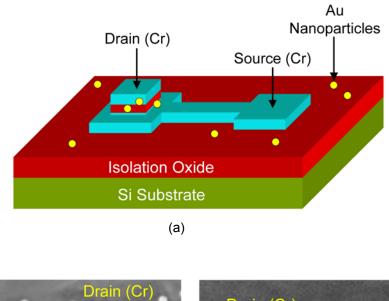

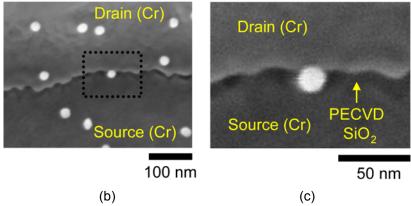

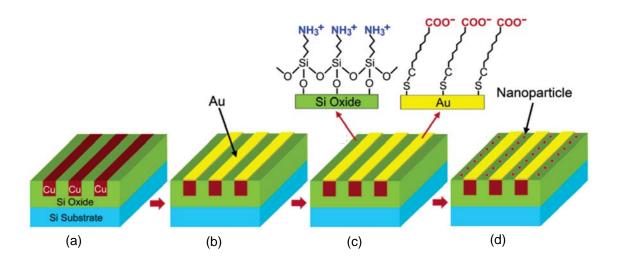

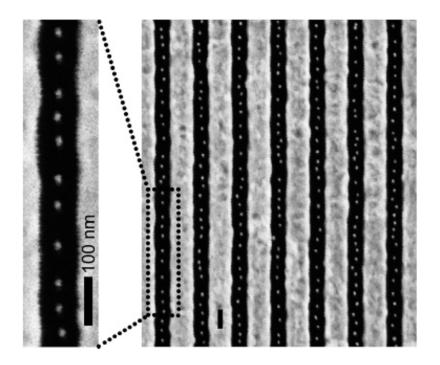

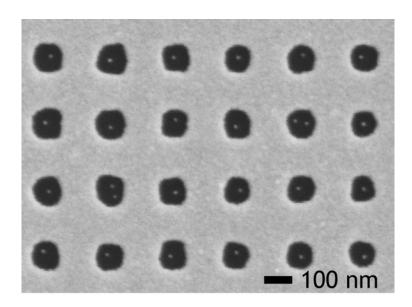

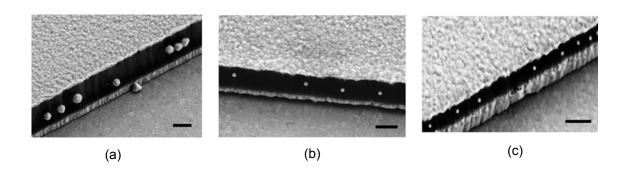

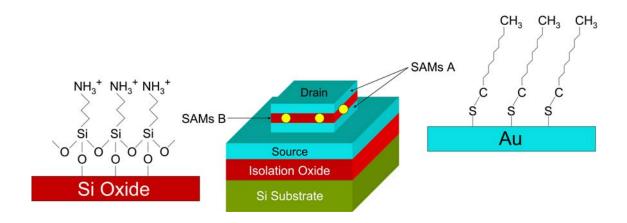

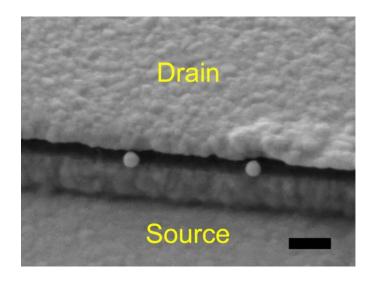

| 4.3 | Attachment of Coulomb islands on the single-electron device.  (a) Schematic of a single-electron device after the attachment of Coulomb islands (Au nanoparticles). The attachment of the Au nanoparticles on the device is random. (b) SEM image of a single-electron device side-wall after the attachment of 20 nm Au nanoparticles (bright dots). The exposed side-wall of the PECVD oxide is the dark line separating the source and the drain electrodes. The dotted box shows a ~ 20 nm Au nanoparticle which is good candidate for single-electron transport. (c) A magnified view of the dotted box in (b). The sample stage is tilted at an angle of 30° from the vertical during imaging. So the thickness of the PECVD SiO <sub>2</sub> appears two times (1/sin30°) smaller than actual                                                                                                                                                                               |

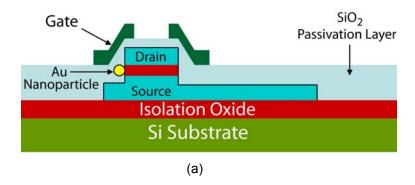

| 4.4 | Deposition of the gate electrodes for a single-electron transistor (a) Schematic illustration of the position of the gate electrode with respect to the source electrode, the drain electrode and the Coulomb island (Au nanoaprticle) in a single-electron transistor.  Schematic not to scale. (b) Top view of device structure after the definition of the gate electrode. Scale bar = 100 µm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

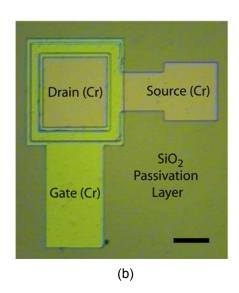

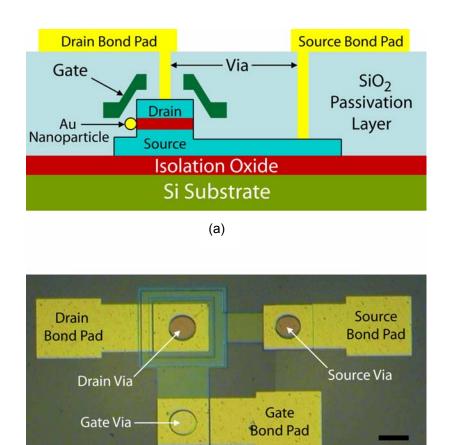

| 4.5 | Etching of vias and deposition of bond pads of a single-electron transistor. (a) Schematic illustration of vias and bond pads in a single-electron transistor. (b) Optical microscope image showing the top view of a completed single-electron transistor.  Scale bar = 100 µm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

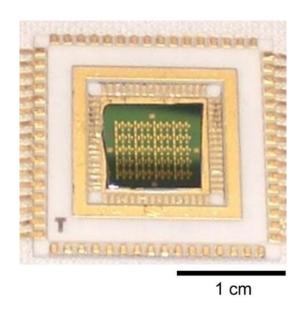

| 4.6 | An individual die containing an array of 60 single-electron transistors that has been mounted on a chip carrier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

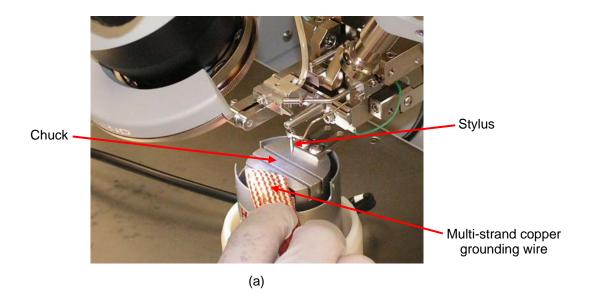

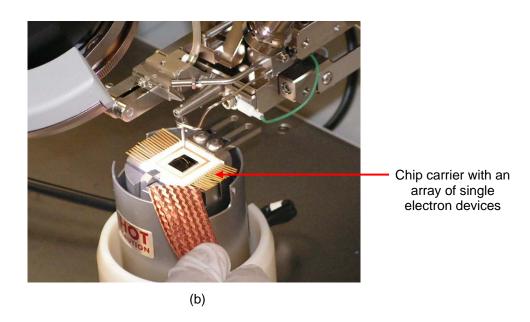

| 4.7 | Removal of static charge before wire bonding. (a) Static charge built up is removed from the wire-bonder body by connecting its electrically conducting surfaces to an earth ground. (b) Static charge is removed from the chip carrier (with a die mounted on it) by touching the legs of the carrier to an earth ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

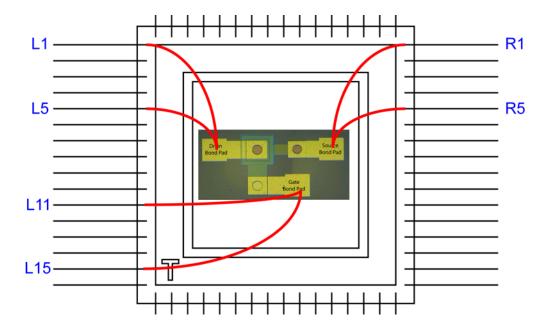

| 4.8  | Schematic layout of a chip carrier with a single-electron transistor wire bonded to predesignated legs of the chip carrier.  Only one completed single-electron transistor is shown in the carrier cavity for clarity. The source bond pads are bonded to legs R1 and R5, the drain bond pads to L1 and L5 and the gate bond pads to L11 and L15, respectively                            | 136 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

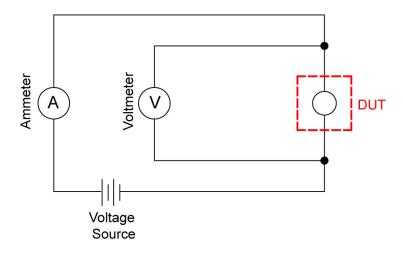

| 5.1  | Schematic of Kelvin (4-wire) resistance measurement used for the electrical characterization of single-electron devices                                                                                                                                                                                                                                                                   | 138 |

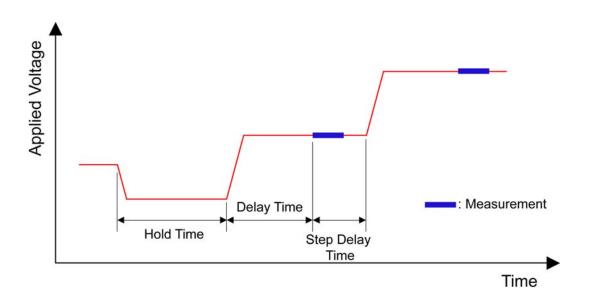

| 5.2  | Schematic of the sweep measurement mode used for the electrical characterization of single-electron devices                                                                                                                                                                                                                                                                               | 139 |

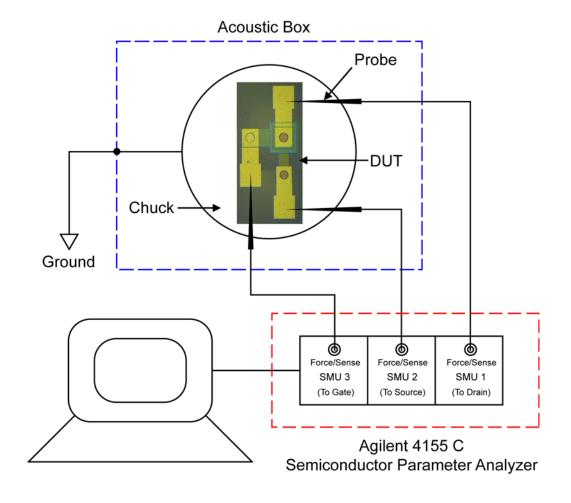

| 5.3  | Schematic diagram of the room-temperature measurement set-up of single-electron devices                                                                                                                                                                                                                                                                                                   | 141 |

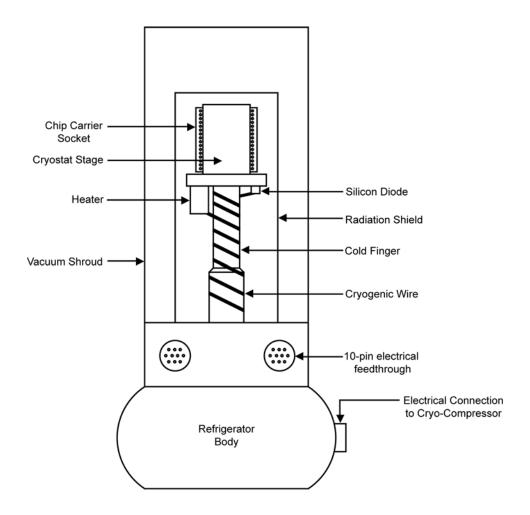

| 5.4  | Schematic front view of the cryostat used for the electrical characterization of single-electron devices at low temperatures                                                                                                                                                                                                                                                              | 143 |

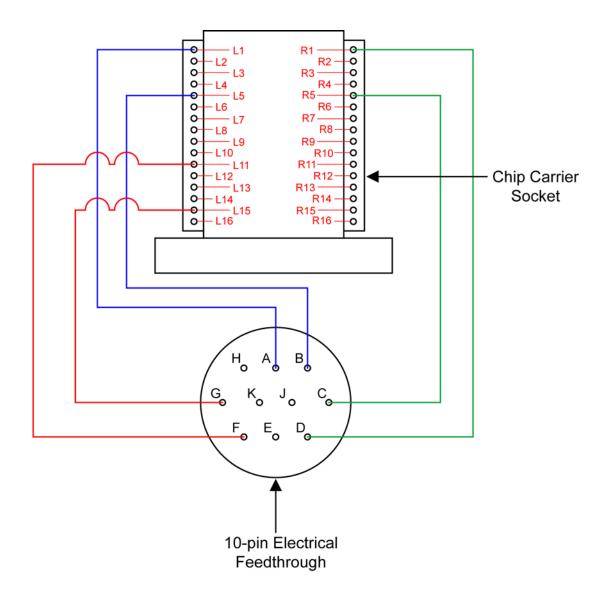

| 5.5  | Schematic of the connections between the legs of the multi-pin chip carrier socket of the cryostat and a 10-pin electrical feedthrough attached to the cryostat body                                                                                                                                                                                                                      | 144 |

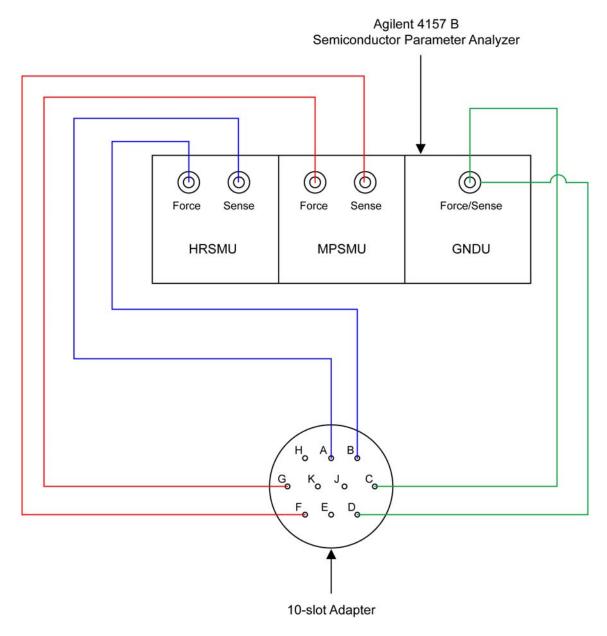

| 5.6  | Wiring diagram between the 4157 B semiconductor parameter analyzer and the 10-slot adapter                                                                                                                                                                                                                                                                                                | 146 |

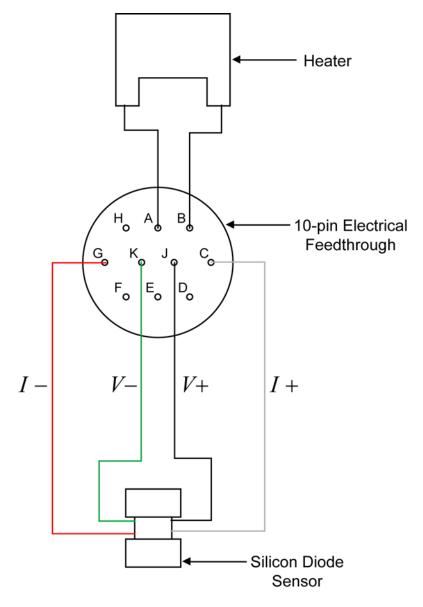

| 5.7  | Wiring diagram from the heater and the silicon diode sensor to the 10-pin electrical feedthrough on the cryostat body                                                                                                                                                                                                                                                                     | 148 |

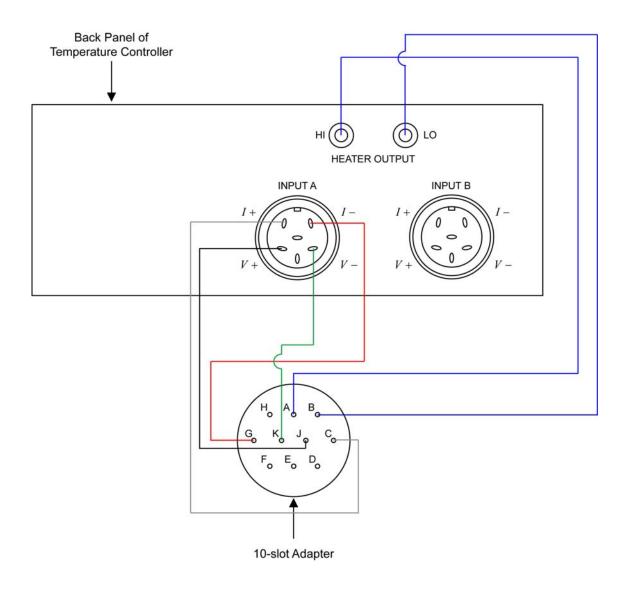

| 5.8  | Wiring diagram between the temperature controller and the 10-slot adapter                                                                                                                                                                                                                                                                                                                 | 150 |

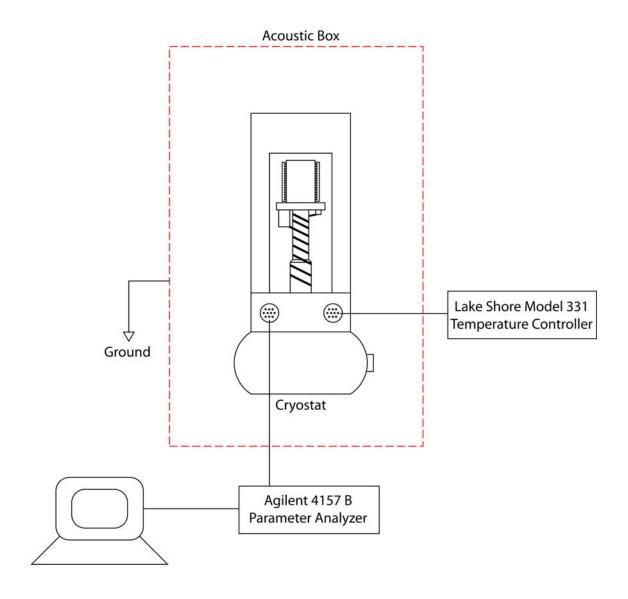

| 5.9  | Schematic diagram of the overall set-up for the electrical characterization of single-electron devices at low temperatures                                                                                                                                                                                                                                                                | 152 |

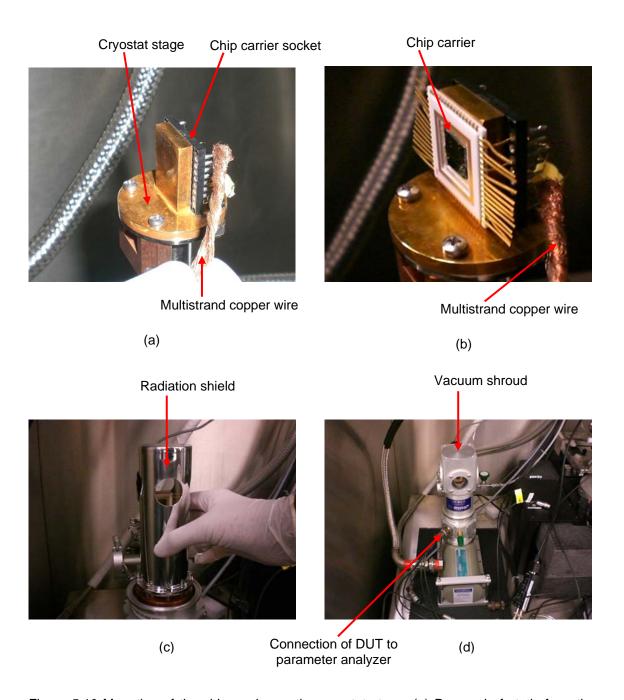

| 5.10 | Mounting of the chip carrier on the cryostat stage.  (a) Removal of static from the chip carrier socket which is attached to the cryostat stage. (b) Mounting of the chip carrier into the multi-pin chip carrier socket.  (c) Lowering of the radiation shield into position.  (d) Placing the vacuum shroud in position.                                                                | 154 |

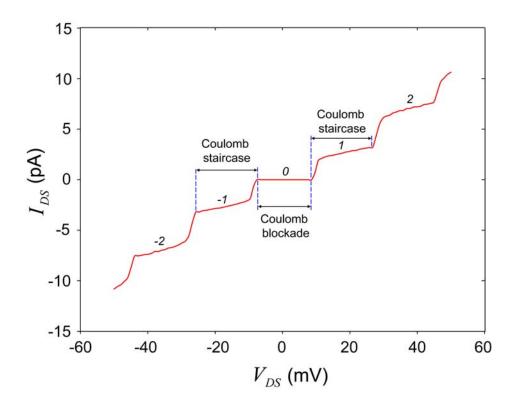

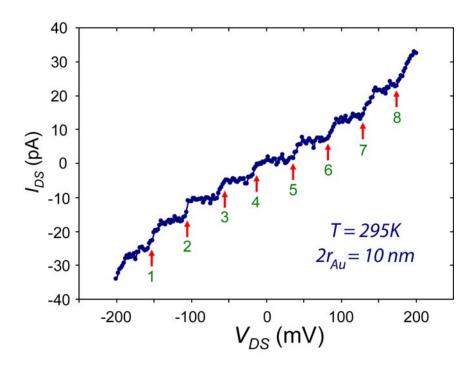

| 5.11 | Plot of the I-V characteristics of a double junction single-electron device using 10 nm diameter Au nanoparticles as the Coulomb islands. The current-voltage characteristics of the device show a clear Coulomb blockade and Coulomb staircase at room-temperature. Each arrow in the plot indicates source-drain voltage at which there is a sharp change in the current of the device. | 156 |

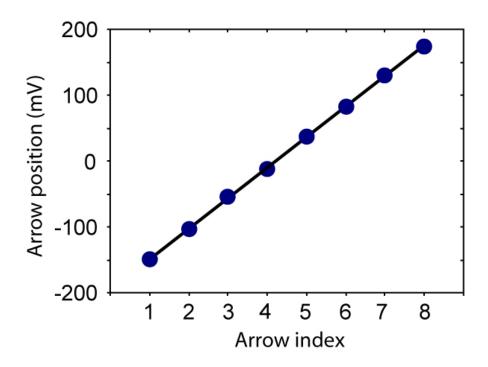

| 5.12 | Plot of the voltage data points corresponding to the arrow positions at which a sharp change in current is observed for the single-electron device with 10 nm diameter Au nanoparticles as Coulomb islands. The values for the voltages are obtained from the I-V plot of the device shown in Figure 5.11 and tabulated in Table 5.1. The average step width $\Delta V_{DS}$ (the average distance                                                                                                                                                                                                                                                                        |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | between adjacent arrow positions) is 46 ± 3 mV. This highly periodic step size confirms that the single-electron tunneling is taking place only through a single nanoparticle that is positioned in the right tunneling range from the source and the drain electrodes                                                                                                                                                                                                                                                                                                                                                                                                    |

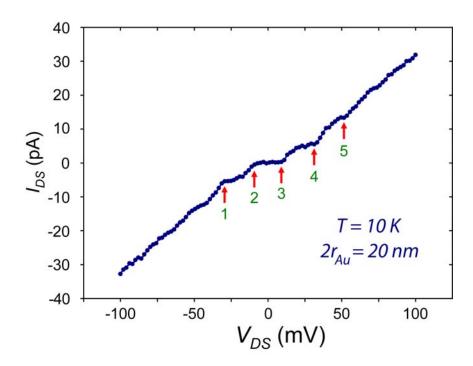

| 5.13 | Plot of the I-V characteristics of a double junction single-electron device using 20 nm diameter Au nanoparticles as the Coulomb islands. The current-voltage characteristics of the device show a clear Coulomb blockade and Coulomb staircase at a temperature of 10 K.  Each arrow marker in the plot indicates the source-drain voltage at which there is a sharp change in the current of the device                                                                                                                                                                                                                                                                 |

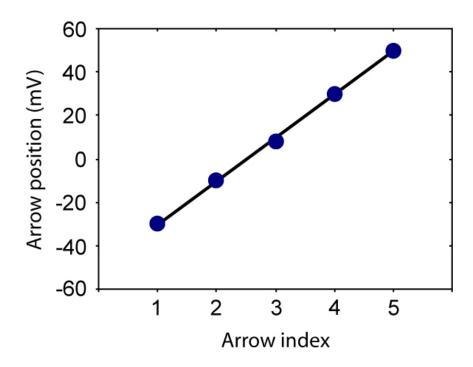

| 5.14 | Plot of the voltage data points corresponding to the arrow positions at which a sharp change in current is observed for the single-electron device with 20 nm diameter Au nanoparticles as Coulomb islands. The values for the voltages are obtained from the I-V plot of the device shown in Figure 5.13 and tabulated in Table 5.2. The average step width $\Delta V_{DS}$ (the average distance between adjacent arrow positions) is 20 ± 2 mV. This highly periodic step size confirms that the single-electron tunneling is taking place only through a single nanoparticle that is positioned in the right tunneling range from the source and the drain electrodes |

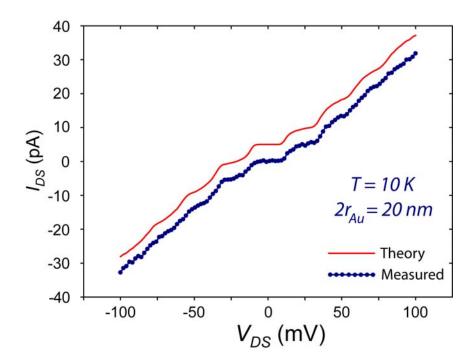

| 5.15 | Comparison between the measured I-V characteristics (blue dots) and simulated I-V characteristics based on the orthodox theory (red line) of the double junction single-electron device using 20 nm diameter Au nanoparticles as Coulomb islands. The simulation parameters were $C_D$ = 7.30 aF, $C_S$ = 0.88 aF, $R_D$ = 2.05 G $\Omega$ , and $R_S$ = 0.40 G $\Omega$ , and background charge of $Q_0$ = 0.05e. The simulated I-V data is offset vertically by 5 pA for clarity                                                                                                                                                                                        |

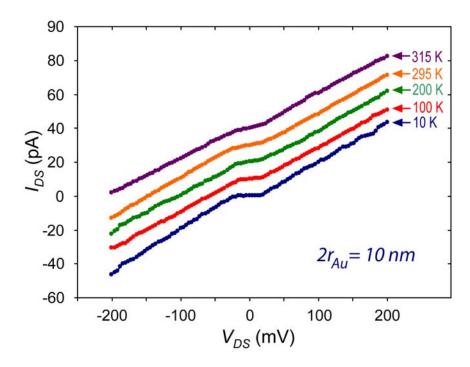

| 5.16 | Plot of I-V characteristics of a double junction single-electron device using 10 nm diameter Au nanoparticles as Coulomb islands that has symmetrical tunneling junctions, measured at five different temperatures. Since the tunnel junctions are symmetrical, only a clear Coulomb blockade without the evidence of Coulomb staircase is observed. With increasing temperature, the blockade region gradually smears out due to thermally activated tunneling of electrons.  Some remnant blockade can still be observed at 315 K                                                                                                                                       |

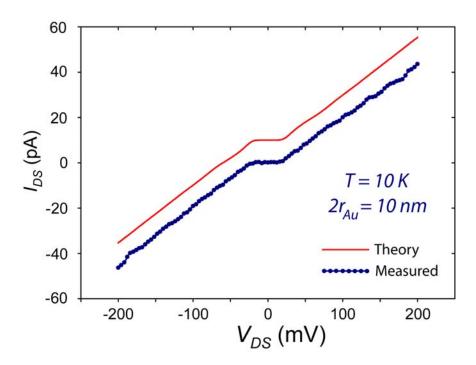

| 5.17 | Comparison between the measured I-V characteristics (blue dots) and simulated I-V characteristics based on the orthodox theory (red line) of the double junction single-electron device using 10 nm diameter Au nanoparticles as Coulomb islands. The simulation parameters were                                                                                                                                                                                                                                                                                                                                                                                          |

|      | $C_D$ = 3.5 aF, $C_S$ = 3.4 aF, $R_D$ = 1.8 G $\Omega$ , and $R_S$ = 2.1 G $\Omega$ ,                                                                                                                                                                                                                                                                              |       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      | and background charge of $\mathcal{Q}_{\scriptscriptstyle 0}$ = 0.07e. The simulated I-V data is                                                                                                                                                                                                                                                                   |       |

|      | offset vertically by 10 pA for clarity                                                                                                                                                                                                                                                                                                                             | 166   |

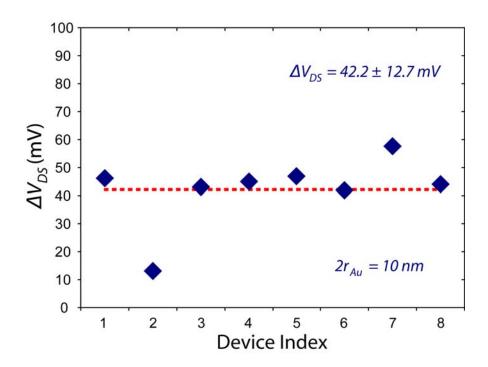

| 5.18 | The step widths $\Delta V_{\rm DS}$ of Coulomb blockade/staircase for                                                                                                                                                                                                                                                                                              |       |

|      | eight different double junction single-electron devices. Each of<br>the eight devices had 10 nm diameter Au nanoparticles as<br>Coulomb islands. Overall, the eight devices had an average                                                                                                                                                                         |       |

|      | $\Delta V_{DS}$ of 42.2 ± 12.7 mV. With the exception of device 2,                                                                                                                                                                                                                                                                                                 |       |

|      | all other devices had $\Delta V_{DS} \sim$ 50 mV                                                                                                                                                                                                                                                                                                                   | 168   |

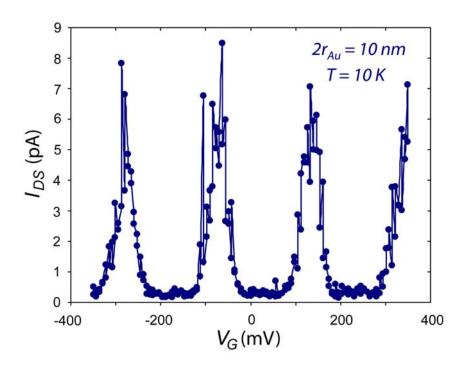

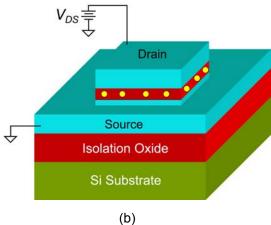

| 5.19 | Demonstration of Coulomb oscillations in a single-electron transistor using 10 nm diameter Au nanoparticles as Coulomb islands at a temperature of 10 K. The source-drain bias was kept constant at 10 mV and the gate bias was swept from -350 mV to 350 mV. The average gap between two successive Coulomb oscillation peaks $\Delta V_G$ was $\approx$ 205 mV.  | . 170 |

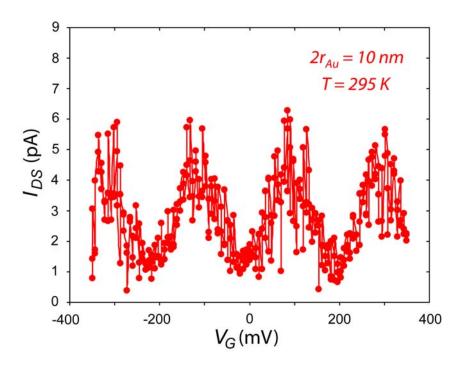

| 5.20 | Demonstration of Coulomb oscillations in a single-electron transistor using 10 nm diameter Au nanoparticles as Coulomb islands at a temperature of 295 K. The source-drain bias was kept constant at 10 mV and the gate bias was swept from -350 mV to 350 mV. The average gap between two successive Coulomb oscillation peaks $\Delta V_G$ was $\approx$ 205 mV. |       |

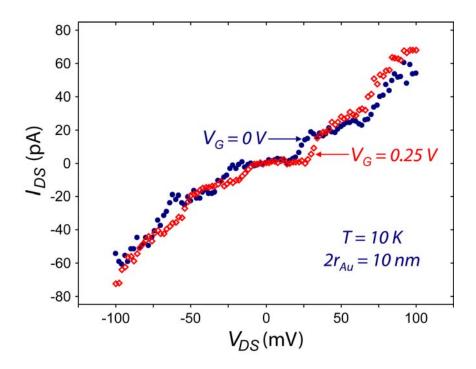

| 5.21 | Coulomb blockade and Coulomb staircase characteristics of a single-electron transistor when the applied gate bias, $V_{\rm G}$ = 0 V                                                                                                                                                                                                                               |       |

|      | (blue dots) and when $V_{\scriptscriptstyle G}$ = 250 mV (red diamonds). The Coulomb                                                                                                                                                                                                                                                                               |       |

|      | island size for this device was 10 nm and the electrical characterization was done at 10 K. A shift in the Coulomb blockade/staircase of the device is clearly observed demonstrating the effect of gate biasing                                                                                                                                                   | 474   |

|      | on single-electron transistors.                                                                                                                                                                                                                                                                                                                                    | . 174 |

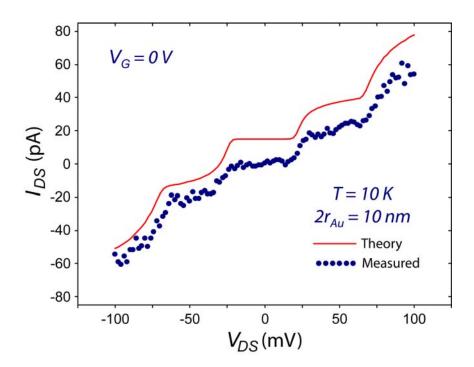

| 5.22 | Comparison between the measured I-V with $V_G$ = 0 V in Figure 5.21 (blue dots) with the simulated I-V using the orthodox theory (red line). The simulation parameters are $C_D$ = 3.4 aF, $C_S$ = 0.24 aF, $C_G$ = 0.78 aF,                                                                                                                                       |       |

|      | $R_D$ = 0.79 G $\Omega$ , $R_S$ = 0.19 G $\Omega$ , and $Q_0$ = 0.05 $\epsilon$ . The simulated curve                                                                                                                                                                                                                                                              |       |

|      | is shifted by 15 pA vertically for clarity                                                                                                                                                                                                                                                                                                                         | . 175 |

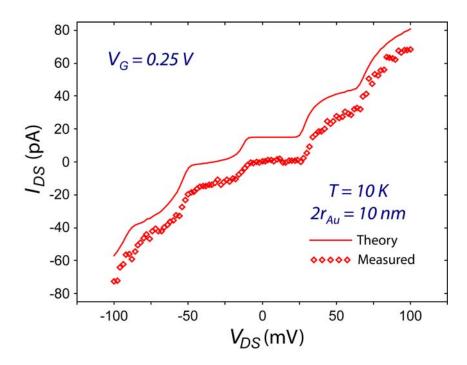

| 5.23 | Comparison between the measured I-V with $V_G$ = 250 mV in Figure 5.21 (red diamonds) with the simulated I-V using the orthodox theory (red line). The simulation parameters are $C_D$ = 3.4 aF, $C_S$ = 0.24 aF, $C_G$ = 0.78 aF,                                                                                                                                 |       |

|      | $R_D$ = 0.79 G $\Omega$ , $R_S$ = 0.19 G $\Omega$ , and $Q_0$ = 0.05 $e$ . The simulated curve is shifted by 15 pA vertically for clarity                                                                                                                                                                                                                          | .176  |

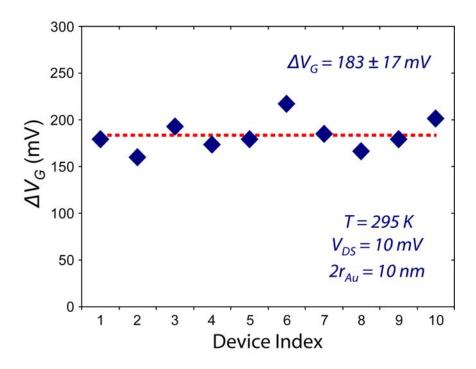

| 5.24 | Average interval of Coulomb oscillation peaks $\Delta V_{\scriptscriptstyle G}$ for 10 different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      | single-electron transistors measured at room temperature. All the 10 devices used 10 nm diameter Au nanoparticles as Coulomb islands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

|      | The red broken line is the average $\Delta V_{\scriptscriptstyle G}$ of 183 mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .178  |

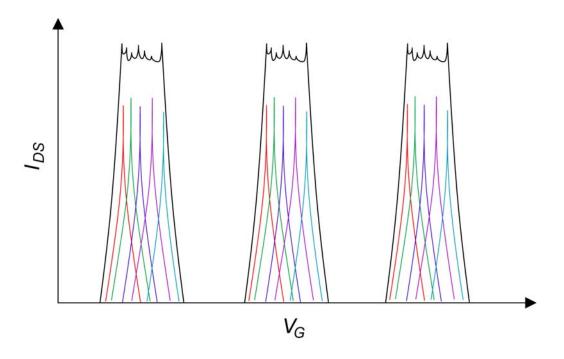

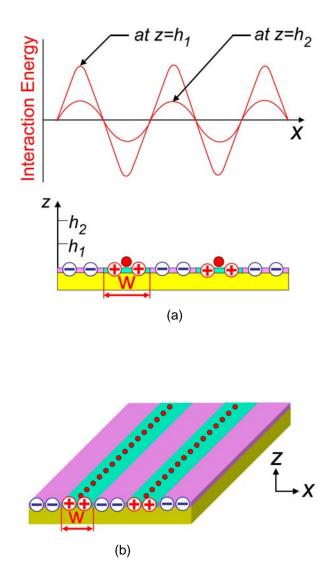

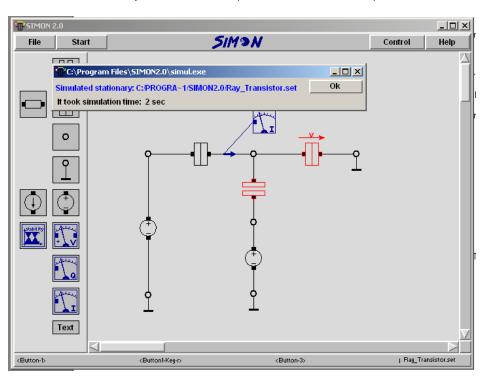

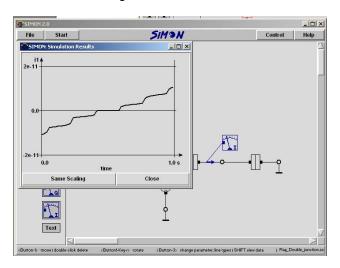

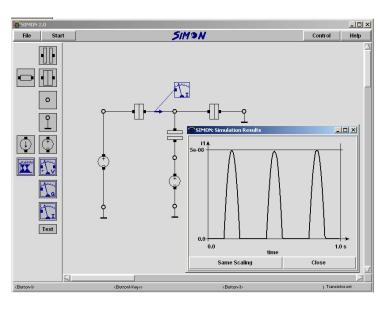

| 6.1  | Schematic illustration of random and selective attachment of nanoparticles on a single-electron device. (a) The random attachment of nanoparticles on the exposed side-wall of the PECVD oxide of a single-electron device. The random attachment leads to low device yield. (b) Controlled positioning of nanoparticles on a single-electron device. This could be a method of achieving higher yields for single-electron devices with the new device structure.                                                                                                                                                                                                                                                                                         | . 180 |