# THERMO-MECHANICAL SOLUTIONS IN ELECTRONIC PACKAGING: COMPONENT TO SYSTEM LEVEL

by

# AALOK TRIVEDI

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

# MASTER OF SCIENCE IN MECHANICAL ENGINEERING

THE UNIVERSITY OF TEXAS AT ARLINGTON

August 2008

Copyright © by Aalok Trivedi 2008

All Rights Reserved

This thesis is dedicated to my parents

for their support and blessings

#### ACKNOWLEDGEMENTS

I express my sincere gratitude and appreciation to my graduate advisor Prof. Dereje Agonafer for his constant guidance, support and encouragement. I would like to acknowledge my industrial advisor, Dr. Gamal Refai-Ahmed, AMD Inc., for his expert guidance in addressing current industry issues. I also would like to thank Dr. Haji-Sheikh and Dr. Seiichi Nomura, for their time to be on my supervising committee.

I am grateful to Henry Wong, for giving me an opportunity to work at Motorola Inc., Tempe, AZ, during Summer 2007, allowing me real time industry exposure. I extend thanks to my colleagues at Motorola, He Junru and late David Chau for their constant input during my stay there.

Also off late, I had got into a close working relationship with CommScope Inc., Richardson, TX, and would like to thank Mark Hendrix for providing me with the opportunity and support. I also would like to thank Deepak Sivanandan, Nick Shliker and all my colleagues at CommScope for believing in me and helping me out in my day to day activities.

I would like to thank my EMNSPC team mates who always have been supporting and helpful. My sincere thanks to Dr. Abhijit Kaisare and Nikhil Lakhkar for getting me grounded and going. Thanks to Ms. Sally Thompson for arranging things, may it be last minute arrangements. My roommates and friends, past and present have always been a great pleasure, non-ending support and fun to be with.

July 10, 2008

iv

#### ABSTRACT

# THERMO-MECHANICAL SOLUTIONS IN ELECTRONIC PACKAGING: FIRST TO SYSTEM LEVEL

Aalok Trivedi, M.S.

The University of Texas at Arlington, 2008

Supervising Professor: Dereje Agonafer

Since the advent of the transistor and integrated circuit, the performance of electronic equipment has increased significantly while footprint of systems at all levels continues to decrease. Recently, the number of transistors on a high end microprocessor has exceeded a billion. All of the above has necessitated considerable improvement in cooling technology and associated reliability. In this era of high heat fluxes, air cooling still remains the primary cooling solution mainly due to its cost and ease of installation and operation. The primary goal of a good thermal design is to ensure that the chip can function at its rated frequency or speed while maintaining the junction temperature within the specified limit. With the focus on good thermal design, mechanical reliability related issues due to the weight of the heat sink on stresses induced on different components of the package also needs to be considered. With all this thermo-mechanical design going into at the first and the second level of the electronics design, leads to a system level problem. Owing to time-to-market requirements, CFD analysis allows to complete thermal optimization long before the product test can be made available bringing

about financial benefits and timely engineering support during product development. In this study, the development of a heat sink tester, analysis of effect of weight of heat sink assembly on mechanical reliability of WB-PBGA package, followed by a system level thermal solution for a telecommunication cabinet is presented.

Part-1 of the thesis focuses on a component level problem, "Experimental and Computational Characterization of a Heat Sink Tester". Use of heat sinks as a thermal solution is well documented in the literature. Previous work exists where uncertainty in heat transfer coefficient for the heat sink tester is calculated by detailed uncertainty analysis based on Monte-Carlo simulations [7]. In this study, the objective is to characterize a heat sink tester experimentally and computationally to see how these results correlate. Experimental characterization for commercially available heat sinks is done according to JEDEC JESD 16.1 [23] standards and is compared against the vendor specifications and computational results. To obtain computational results, a CFD tool Icepak<sup>™</sup> is used to carry out the thermal analysis. The results thus obtained from experimental characterization, computational analysis and vendor specifications are used for benchmarking the heat sink tester.

Part-2 of the thesis addresses a package level mechanical reliability issue, "Effect of Weight of Heat Sink Assembly on Mechanical Reliability of a WB-PBGA package". In this study, a stress analysis of described package is carried out to study the effect of weight of heat sink assembly on the mechanical reliability of the package. A three dimensional finite element model of WB-PBGA package and Printed Wiring Board (PWB) is solved numerically to predict the stresses induced and assess their impact on the mechanical integrity on different components of the package, which is accomplished by using a commercial analysis tool ANSYS<sup>™</sup>. Die and C4 interconnect stresses are examined to evaluate package reliability. Stresses induced within the die and C4 interconnect are examined for different heat sink materials and variation of force developed by different heat sink attachments such as clip-on and screw-on types. Finally

vi

recommendations are made regarding choice of heat sink material and clip force for overall heat sink assembly design.

Finally, part-3 of this study presents thermal solution to a system level problem, "Compact Modeling of a Telecommunication Cabinet". The objective of this study is to present an overview of techniques to minimize the computational time for complex designs such as heat exchangers used in telecommunication cabinets. The discussion herein presents the concepts which lead to developing a compact model of the heat exchanger, reducing the mesh count and thereby the computation time, without compromising the acceptability of the results. Compact modeling, selective meshing, and replacing sub-components with simplified equivalent models all help reduce the overall model size. The model thus developed is compared to a benchmark case without the compact model. Given that the validity of compact models is not generalized, it is expected that this methodology can address this particular class of problems in telecommunications systems. The CFD code FLOTHERM<sup>™</sup> by Flomerics is used to carry out the analysis.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                         | iv   |

|--------------------------------------------------------------------------|------|

| ABSTRACT                                                                 | v    |

| TABLE OF CONTENTS                                                        | viii |

| LIST OF ILLUSTRATIONS                                                    | xii  |

| LIST OF TABLES                                                           | xv   |

| NOMENCLATURE                                                             | xvi  |

| Chapter                                                                  | Page |

| 1. INTRODUCTION                                                          | 1    |

| 1.1 What is Electronic Packaging?                                        | 1    |

| 1.2 Why Electronic Packaging?                                            | 1    |

| 1.3 Packaging Levels                                                     | 3    |

| 1.4 Power Trends in Electronics                                          | 4    |

| 1.5 Thermal Management                                                   | 6    |

| 1.5.1 First Level Package Cooling                                        | 7    |

| 1.5.2 Second Level Package Cooling                                       | 7    |

| 1.5.3 Third or System Level Package Cooling                              | 7    |

| 1.6 Mechanical Integrity of the Package                                  | 8    |

| 1.7 Computational Fluid Dynamics in Electronic Packaging                 | 8    |

| PART-1 EXPERIMENTAL AND COMPUTATIONAL CHARACTERIZATION OF A HEAT STESTER | SINK |

| 2. | INTRODUCTION | 11 |  |

|----|--------------|----|--|

|    |              |    |  |

| 2.1 Background 11 |

|-------------------|

|-------------------|

|      | 2.2 Thermal Management                                | 12 |

|------|-------------------------------------------------------|----|

|      | 2.3 Research Overview                                 | 12 |

| 3. C | OMPUTATIONAL MODEL                                    | 15 |

|      | 3.1 Computational Model Description                   | 15 |

|      | 3.2 Icepak Modeling                                   | 16 |

|      | 3.3 Meshing                                           | 17 |

| 4. E | EXPERIMENTAL VALIDATION                               | 19 |

|      | 4.1 Airflow Chamber Configuration                     | 19 |

|      | 4.2 Test Setup                                        | 20 |

|      | 4.3 Experimental Test Procedure                       | 20 |

|      | 4.4 Commercial Heat Sinks Tested                      | 21 |

|      | 4.5 Calculations                                      | 22 |

| 5. R | ESULTS AND DISCUSSIONS                                | 23 |

|      | 5.1 Area Effect on Heat Transfer                      | 23 |

|      | 5.2 Experimental Results                              | 24 |

|      | 5.3 Computational and Experimental Results Validation | 26 |

|      | 5.4 Inferences                                        | 27 |

| 6. C | ONCLUSION                                             | 29 |

# PART-2 EFFECT OF WEIGHT OF HEATSINK ASSEMBLY ON MECHANICAL RELIABILITY OF A WIRE BONDED PLASTIC BALL GRID ARRAY PACAKGE

| 7. | INTRODUCTION             | 31 |

|----|--------------------------|----|

|    | 7.1 Background           | 31 |

|    | 7.2 Research Overview    | 32 |

|    | 7.3 Package Description  | 33 |

| 8. | COMPUTATIONAL MODEL      | 35 |

|    | 8.1 Modeling Methodology | 35 |

| 8.2 Heat Sink Assembly              | 38  |

|-------------------------------------|-----|

| 8.2.1 Heat Sink Weight              | 38  |

| 8.2.2 Heat Sink Mounting Techniques | 39  |

| 8.2.2.1 Clip-on Type                | 39  |

| 8.2.2.2 Screw-on Type               | .40 |

| 8.3 Meshing                         | 41  |

| 9. RESULTS AND DISCUSSIONS          | 42  |

| 10. SUMMARY AND CONCLUSION          | 49  |

# PART-3 COMPACT MODELING OF A TELECOMMUNICATION CABINET

| 11. INTRODUCTION                  | 52   |

|-----------------------------------|------|

| 11.1 Introduction                 | 52   |

| 11.2 Research Overview            | 52   |

| 11.3 Cabinet Description          | 53   |

| 12. COMPUTATIONAL MODELING        | 55   |

| 12.1 Modeling Methodology         | 55   |

| 12.1.1 Computational Analysis     | . 55 |

| 12.1.2 Experimental Analysis      | .56  |

| 12.2 Heat Exchanger Modeling      | . 56 |

| 12.3 Customer Shelf Assembly      | 58   |

| 12.4 Air Movers                   | 58   |

| 12.5 Other Modules                | 59   |

| 12.6 System Level Enclosure Model | 59   |

| 12.7 Meshing                      | 61   |

| 13. BOUNDARY CONDITIONS           | 62   |

| 13.1 Thermal Boundary Condition       | 62 |

|---------------------------------------|----|

| 13.1.1 Surface Exchange Factor Method | 62 |

| 13.1.2 Volume Resistance Method       | 63 |

| 13.2 Fluid Flow Boundary Condition    | 64 |

| 13.3 Thermal Load                     | 65 |

| 14. RESULTS AND DISCUSSIONS           | 66 |

| 15. CONCLUSION                        | 70 |

| 16. BEST KNOWN PRACTICES FOR MODELING | 71 |

| APPENDIX                              |    |

| A. ACRONYMS                           | 72 |

| REFERENCES                            | 74 |

| BIOGRAPHICAL INFORMATION              | 77 |

# LIST OF ILLUSTRATIONS

| Figure |                                                                               | Page |

|--------|-------------------------------------------------------------------------------|------|

| 1.1    | Electronic packaging market                                                   | 2    |

| 1.2    | Packaging hierarchy                                                           | 3    |

| 1.3    | Moore's law                                                                   | 4    |

| 1.4    | Power density chart                                                           | 5    |

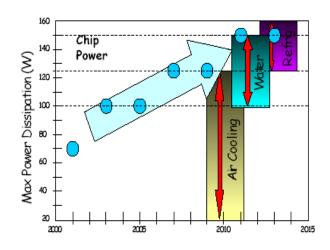

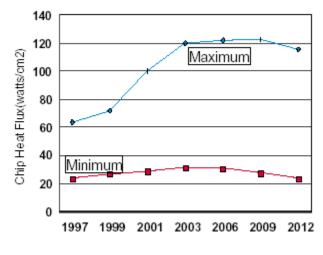

| 1.5    | Chip power dissipation chart                                                  | 6    |

| 1.6    | Chip heat flux chart                                                          | 6    |

| 2.1    | Chip cooling with a heat sink                                                 | 12   |

| 3.1    | Heat sink tester arrangement                                                  | 15   |

| 3.2    | Icepak model of the heat sink tester apparatus                                | 16   |

| 3.3    | Computational model for the heat sink tester setup                            | 16   |

| 3.4    | Temperature contours taken at the center of Z-plane                           | 17   |

| 3.5    | Model mesh                                                                    | 18   |

| 3.6    | Grid sensitivity analysis                                                     | 18   |

| 4.1    | Schematic of an air flow bench                                                | 19   |

| 4.2    | Experimental setup                                                            | 20   |

| 4.3    | Heat sinks tested                                                             | 22   |

| 5.1    | Area effect on heat distribution                                              | 23   |

| 5.2    | 400 mm <sup>2</sup> heater coupon heat flux distribution at different heights | 24   |

| 5.3    | Thermal resistance curve for P52120SB-45B heat sink                           | 25   |

| 5.4    | Thermal resistance curve for PAL 6030 heat sink                               | 25   |

| 5.5    | Thermal resistance comparison for PAL 6030 heat sink                          | 26   |

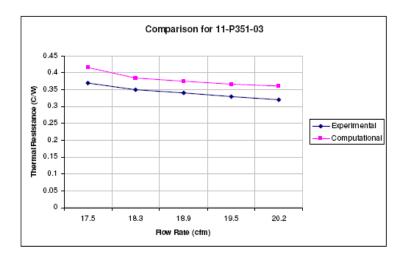

| 5.6    | Thermal resistance comparison for 11-P351-03 heat sink                        | 26   |

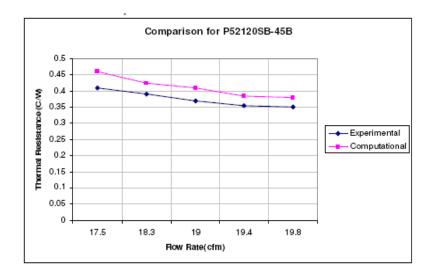

| 5.7  | Thermal resistance comparison for P52120SB-45B heat sink                                                  | 27 |

|------|-----------------------------------------------------------------------------------------------------------|----|

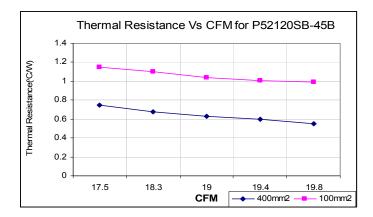

| 5.8  | Thermal resistance comparison for different heater coupon areas                                           | 27 |

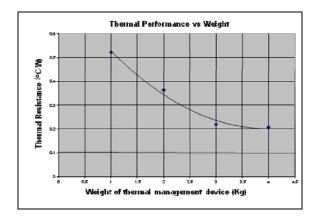

| 7.1  | Thermal resistance vs. weight of thermal management device                                                | 33 |

| 7.2  | Package schematic                                                                                         | 33 |

| 7.3  | Layers of substrate                                                                                       | 34 |

| 7.4  | Layers of printed wiring board                                                                            | 34 |

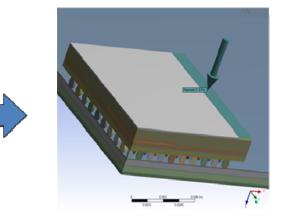

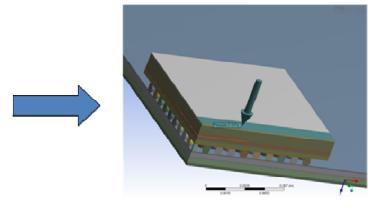

| 8.1  | Quarter model of the package                                                                              | 35 |

| 8.2  | Quarter model with symmetry planes                                                                        | 35 |

| 8.3  | Pressure applied due to heat sink weight                                                                  | 38 |

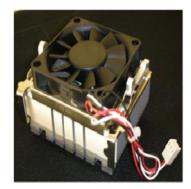

| 8.4  | Clip-on type heat sink                                                                                    | 39 |

| 8.5  | Screw-on type heat sink                                                                                   | 40 |

| 8.6  | FEM of the given package                                                                                  | 41 |

| 9.1  | Equivalent stress for the given package                                                                   | 42 |

| 9.2  | Die stress for Cu heat sink due to clip-on type attachment                                                | 43 |

| 9.3  | Die stress for Cu heat sink due to screw-on type attachment                                               | 44 |

| 9.4  | C4 interconnect stresses for Cu heat sink                                                                 | 45 |

| 9.5  | Effect of weight of heat sink on package stresses for clip type attachment                                | 45 |

| 9.6  | Effect of weight of heat sink on package stresses for screw-on type attachment                            | 46 |

| 9.7  | Effect of clip force (lb <sub>f</sub> ) on package stresses                                               | 46 |

| 9.8  | Effect of screw force corresponding to clip deflection (mm) on package stresses                           | 47 |

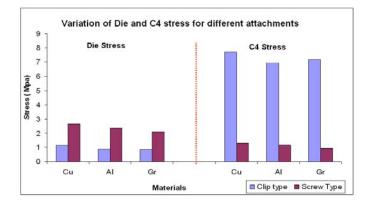

| 9.9  | Effect of heat sink mounting attachment on Die and C4 Interconnect stresses induced for a given heat sink | 47 |

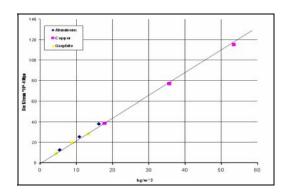

| 9.10 | Die stress vs. weight applied by the heat sink                                                            | 48 |

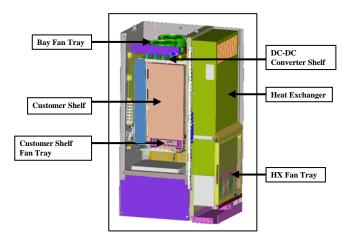

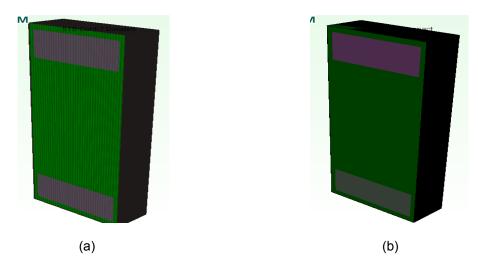

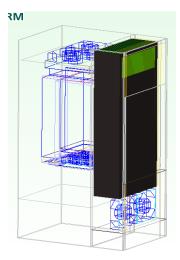

| 11.1 | CAD model of the CommScope cabinet                                                                        | 54 |

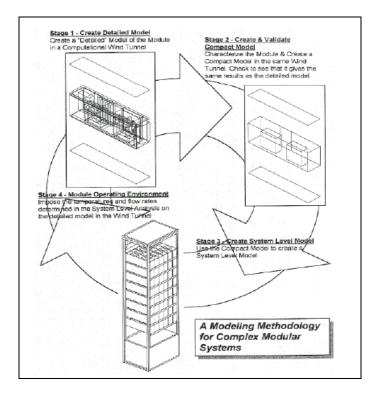

| 12.1 | Modeling methodology                                                                                      | 56 |

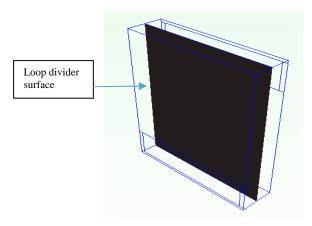

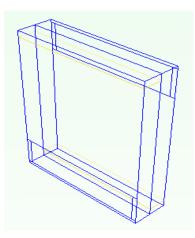

| 12.2 | Isometric view of HX towards the inner loop side                                                  | 57 |

|------|---------------------------------------------------------------------------------------------------|----|

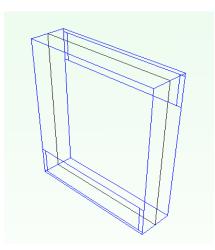

| 12.3 | Wire frame view of the counter flow HX                                                            | 58 |

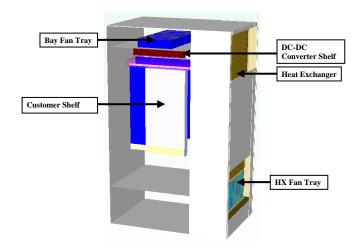

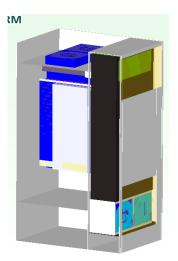

| 12.4 | FLOTHERM model of the CommScope cabinet                                                           | 60 |

| 12.5 | Isometric view of the cabinet, solid and wireframe                                                | 60 |

| 13.1 | Isometric view of HX compact model used in Surface Exchange<br>Factor Method with divider surface | 63 |

| 13.2 | Isometric view of HX compact model used in Volume<br>Resistance Method                            | 64 |

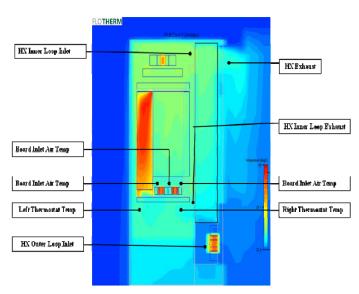

| 14.1 | Monitor point locations inside the cabinet                                                        | 66 |

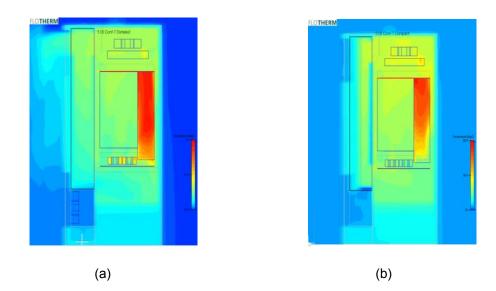

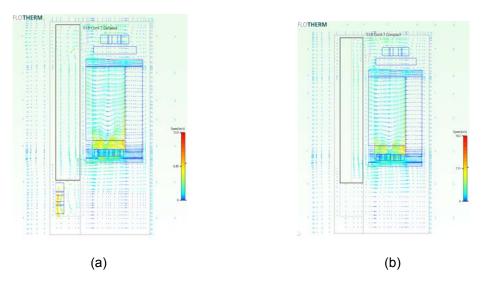

| 14.2 | Temperature contour plots at midpoint of the customer shelf width                                 | 67 |

| 14.3 | Vector plots at midpoint of customer shelf width                                                  | 67 |

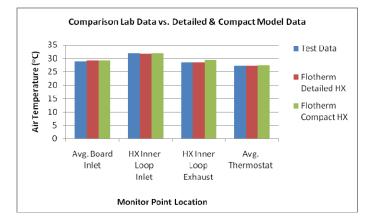

| 14.4 | Results comparison for computational, detailed and compact models to lab results                  | 68 |

# LIST OF TABLES

| Table |                                                                          | Page |

|-------|--------------------------------------------------------------------------|------|

| 8.1   | Heat sink material densities                                             | 36   |

| 8.2   | Package dimensions                                                       | 36   |

| 8.3   | Material properties                                                      | 37   |

| 13.1  | Electronic equipment power values                                        | 65   |

| 14.1  | Computational, detailed and compact model results comparison to lab data | 68   |

| 14.2  | Mesh count and computation time comparison                               | 69   |

# NOMENCLATURE

- R<sub>Th</sub> Thermal resistance (°C/W)

- T<sub>j</sub> Junction temperature (°C)

- T<sub>a</sub> Ambient temperature (°C)

- P Power (W)

- R<sub>jp</sub> Thermal resistance between junction to package (°C/W)

- R<sub>pc</sub> Thermal resistance between package and sink (°C/W)

- R<sub>sa</sub> Thermal resistance between sink and ambient (°C/W)

- T<sub>p</sub> Temperature at the top of heater coupon (°C)

- T<sub>s</sub> Temperature at the top of thermal interface (°C)

- T<sub>x</sub> Temperature recorded at different vertical locations on the heater coupon (°C)

- K Thermal Conductivity (W/mK)

- H Convective heat transfer coefficient (W/m<sup>2</sup> °K)

- T<sub>b</sub> Temperature at the base of the heat sink (°C)

- P<sub>n</sub> Differential pressure

- V Voltage (V)

- I Current (A)

- Q Flow rate (cfm)

- A Area (mm<sup>2</sup>)

- v Velocity (m/s)

- g Acceleration due to gravity  $(m/s^2)$

- r Radius of the nozzle (mm)

- E Young's Modulus (GPa)

- α Poisson's ratio

| δ Deflection | (mm) |

|--------------|------|

|--------------|------|

- P<sub>f</sub> Force (lb<sub>f</sub>)

- L Length (mm)

- I Moment of Inertia (mm<sup>4</sup>)

- m Mass (kg)

٠

- v Volume (m<sup>3</sup>)

- p Pressure (in of H<sub>2</sub>O)

- q Heat Absorbed/Rejected (W)

- *m* Mass Flow Rate (kg/s)

- $C_p$  Specific Heat of Air (J/kg  $^{\circ}K$ )

- $\Delta T$  Temperature Difference (<sup>o</sup>K)

- ζ Loss coefficient (m<sup>-1</sup>)

- ρ Density (kg/m<sup>3</sup>)

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 What is Electronic Packaging?

Electronic packaging is a link that interconnects the IC's and other electronic components into a system, providing a structurally and environmentally protected enclosure for electronic circuits enabling the transfer of signals and the diffusion of heat. In other words, it performs three basic functions:

- 1. Provide electrical connection

- 2. Thermal management and

- 3. Form a structural and environmental protective enclosure for semiconductor devices and electronic components

It encompasses the semiconductor devices, interconnects, cooling and mounting mechanisms, along with facilitating production and assembly processes needed to create electronic products. Often times, it is the packaging and assembly strategy that decides the weight, size, durability, performance, and cost of the product. Increasing the electronic packaging technology determines the productivity and competitiveness of the electronics industry. Electronic components can be roughly characterized into active and passive components. Active components consume power in delivering functionality within a system, while passive provide connection, mechanical support, filtering, noise reduction, and other functions which are critical to the performance of active devices.

#### 1.2 Why Electronic Packaging?

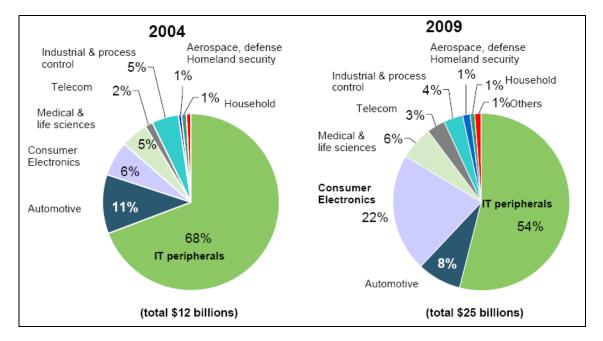

Electronic products are now integral parts of our personal and professional lives. They enable us in communication, access of information, management of offices and homes, transportation, manufacturability and entertainment. The technologies, referred to in the context of electronic products, are microelectronics for processing information, optical and magnetic storage for storing information, photonic and wireless communications for transferring information, micro-machined micro-sized motors to serve in medical electronics, batteries for supplying the power, device and integrated systems packaging to end up with integrated and highly functional products [1]. In other words, the electronic or microsystems packaging has a big chunk of share in the markets as depicted in figure 1.1, representing the current and future trend for electronic packaging:

- Computer and Business equipment

- Military and Aerospace

- Automotive industry

- Communications

- Industrial and Medical

- Consumer

Figure 1.1 Electronic packaging market [4]

## 1.3 Packaging Levels

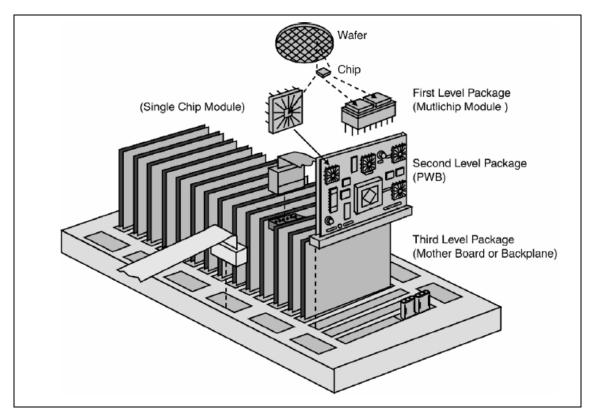

To develop a thermo-mechanical design for a specified electronic product, it is important to know the different packaging levels. The packaging hierarchy is divided into three structural levels:

- First level package: Chips into single-chip modules (SCM) or multichip modules (MCM)

- Second level package: Components (SCMs, MCMs, connectors, etc.) on a printed circuit board (PCB)

- Third level package: PCB assemblies, cables, power supplies, cooling systems, and peripherals into a frame or a box

Figure 1.2 Packaging hierarchy [1]

The chip or integrated circuit (IC) device is separated from its wafer and packaged on a carrier as a single-chip package (SCP) or a multichip package or module (MCP or MCM). The package is then assembled onto a larger PCB usually referred to as a card or a board. The card

assembly is mounted on a back plane which may carry many adapter cards that provide different functions and may act as interfaces to the world outside the computer box. So with these discrete structural levels in electronic packaging, it is very important to focus on the level of the package which is worked on. Moreover, based on the level of the package to be addressed, there are varied thermo-mechanical solution techniques that could be implemented for the optimal and reliable working of the electronic product [2]. Different structural hierarchical levels in electronic packaging are shown in figure 1.2.

#### <u>1.4 Power Trends in Electronics</u>

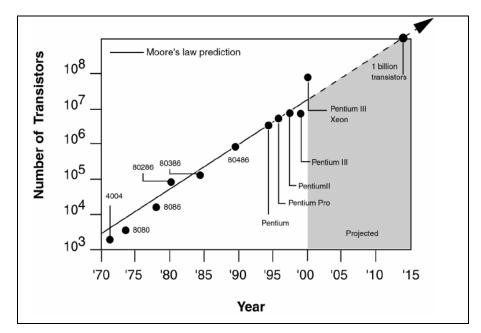

In 1965, Gordon Moore published a prophetic article stating, the number of transistors that can be inexpensively placed on an integrated circuit is increasing exponentially, doubling approximately every 18 months, figure 1.3. The trend has continued for more than half a century and is not expected to stop for another decade at least and perhaps much longer [38].

Figure 1.3 Moore's law [1]

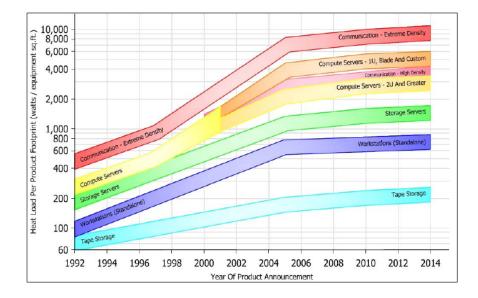

Hence, since the advent of the transistor and integrated circuit, the performance of electronic equipment has increased significantly while footprints of systems at all levels continue to decrease. Moreover, NEMI 2000 reports say that the chip power is going to be 300 Watts by year 2012. Figure 1.4 depicts the power per product footprint for all levels of packaging covering most of the applications of electronic packages. Owing to the increasing high power trend, it is becoming a challenge to manage the thermal loading without compromising the efficiency and power capabilities of the electronic packages.

Figure 1.4 Power density chart [3]

Presented in figure 1.5 and 1.6 are, the power trends for the chip power and chip heat flux respectively. The chip power and heat flux have increased and are going to increase for days to come. With continuous trend towards increase in power, efficient thermal management with mechanical reliability are the challenges limiting the technological development in electronic packaging industry.

Figure 1.5 Chip power dissipation chart [6]

Figure 1.6 Chip heat flux chart [6]

#### 1.5 Thermal Management

Decreasing the temperature of a component increases its performance as well as reliability. In addition to lowering the junction temperatures within a component, it is sometimes also important to reduce the temperature variation between components that are electronically connected in order to obtain optimum performance. Thermal considerations become an important part of electronic equipment because of increased heat flux. Thermal management of electronic components may employ different heat transfer modes simultaneously and acting at different levels:

#### 1.5.1 First Level Package Cooling

The chip package, which houses and protects the chip, forms the bottom of the packaging hierarchy or first level. Thermal packaging at this level is primarily concerned with conducting heat from the chip to the package surface and then into the printed wiring board. At this packaging level, reduction of the thermal resistance between the silicon die and the outer surface of the package is the most effective way to lower the chip temperature. The reduction of thermal resistance can be brought about by using die-attach adhesives with diamond, silver, or another high conductivity filler material, thermal greases, and so-called phase change materials, which soften at the operating temperature to better conform to the surface of the chip or different available forms of heat spreaders. The cooling can be brought about by active cooling techniques like air jet impingement and dielectric liquid, heat sinks and immersion in a dielectric liquid are the respective examples of the cooling techniques [1].

#### 1.5.2 Second Level Package Cooling

The printed wiring board (PWB), which provides the means for chip-to-chip communication, constitutes the second level. Heat removal at this level occurs both by conduction in the printed wiring board and by convection to the ambient air. Use of thick, high conductivity printed wiring boards with heat sinks or heat pipes on the back side could be ways to take away heat from the board. Most of the times in network equipments, heat is taken away from the printed wiring board by having internal air flow loops created by fans or blowers [1].

#### 1.5.3 Third or System Level Package Cooling

The back-plane or motherboard, which interconnects the printed wiring boards, is termed as the third or system level. Thermal management at this level generally involves the use of active thermal control measures, such as air handling systems, refrigeration systems, heat pipes, heat exchangers and pumps. Depending on the application to be served, it might be possible to cool the module and/or rack by relying on the natural circulation of the heated air [1].

7

#### 1.6 Mechanical Integrity of the Package

Recent leaps in the electronic packaging has necessitated considerable improvement in cooling technology and associated reliability. Heat sinks play an important role in cooling technology by providing an increased surface area to dissipate heat. Increasing the surface area implies added weight exerted on the package which is a function of density of material used, with the options of Copper, Aluminum and Graphite considered in this study. Stresses induced in the package for all these combinations needs to be investigated. The package should be designed in such a way that the stress in any component should not exceed the permissible limits of that material and moreover, the thermo-mechanical and cyclic loading reliability should also be acceptable. All these factors are to be considered while selecting the cooling mechanism and finalizing the design for the package.

#### 1.7 Computational Fluid Dynamics in Electronic Packaging

CFD tools like FLOTHERM<sup>™</sup> and Icepak<sup>™</sup> allows engineers to model electronic system designs and perform heat transfer and fluid flow simulations that can increase a product's quality and significantly reduce its time-to-market. These tools provide complete thermal management system that can be used to solve component-level, board-level, or system-level problems. It provides design engineers with the ability to test conceptual designs under operating conditions that might be impractical to duplicate with a physical model, and obtain data at locations that might otherwise be inaccessible for monitoring [26].

On similar lines, when it comes to structural and reliability related issues, ANSYS Workbench platform provides an environment that offers an efficient and intuitive interface to simulate the physical problem and perform the required analysis. It is a tool having thermal, mechanical and fatigue problem solving capabilities amongst others, hence can provide thermomechanical solutions in electronic packaging. Optimization is another feature which allows a

8

control on a variable by systematically choosing the values for other variables from within an allowed set [27].

PART-1

EXPERIMENTAL AND COMPUTATIONAL CHARACTERIZATION OF A HEAT SINK TESTER

#### CHAPTER 2

## INTRODUCTION

#### 2.1 Background

Developments in the semiconductor industry, along with consumer demand for cheaper, lighter, high-density information processing tools, have in effect revolutionized the entire electronic packaging infrastructure. The result of this demand has been the rapid development of high-density, high-function, semiconductor devices with ever increasing functionality packaged into smaller and smaller devices. The increased power dissipation of today's integrated circuits has made the knowledge of junction to ambient thermal resistance, more important to those who manufacture and use these devices than ever before. The junction to ambient thermal resistance, R<sub>th</sub>, is a measure of the temperature rise of the die's active surface (junction) above the temperature of the ambient coolant fluid, per unit power dissipations, and is given by,

$$R_{th} = \frac{\left(T_j - T_a\right)}{P} \tag{2.1}$$

where,  $T_j$ ,  $T_a$ , and P, are the chip junction temperature, the ambient coolant fluid temperature, and the chip power dissipation, respectively.

This junction to ambient thermal resistance,  $R_{ja}$ , is composed of three primary thermal resistances in series, and can be expressed as,

$$R_{ja} = R_{jp} + R_{ps} + R_{sa}$$

(2.2)

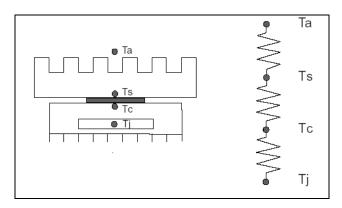

where  $R_{jp}$ ,  $R_{ps}$ ,  $R_{sa}$  are the thermal resistances between the junction to package, package to sink, and sink to ambient, respectively. Figure 2.1 shows schematic of a

microprocessor chip that is cooled with a heat sink, which is attached to the chip via a thermal interface. In such a configuration, the junction to package thermal resistance,  $R_{jp}$ , represents the chip conduction resistance, and one dimensional spreading due to the non-uniform heat flux, respectively. The package to sink thermal resistance,  $R_{ps}$ , takes into account the impedance to heat flow due to presence of the thermal interface material that resides between the top of the chip package and the bottom of the heat sink. The sink to ambient thermal resistance,  $R_{sa}$ , includes the conduction from the heat sink base and fins, the convective heat transfer between the finned surface and the coolant flowing through the passages, as well as the sensible temperature rise in the coolant fluid as it carries the heat away. Thus, the challenge is to accurately measure the performance of a high performance cold plate or a heat sink, when its performance is comparable (or better) in magnitude to that of the thermal interface that is used to attach it to a heater surface. This study is experimental validation of heat sink tester, designed previously in [7, 8].

Figure 2.1 Chip cooling with a heat sink

#### 2.2 Thermal Management

Heat sinks have been an integral part of electronic systems for almost 40 years now. Several modifications in base geometry, fin geometry and materials have been made during the course of years to achieve lower thermal resistance and higher heat transfer coefficient. Initially, the focus was on enhancing the heat transfer area by increasing the number of fins, thereby increasing the size of the heat sink. This approach can have two drawbacks:

- 1. Pressure drop and hence pumping power increase across the heat sink

- 2. Weight of the heat sink increases

Due to the low thermal conductivity and low specific heat of air, several investigators came to conclusion that air cooling is not good enough for high power chips [5].

However, placing a fan directly above heat sink enhances the heat transfer coefficient significantly [14]. On the same lines, heat sinks are extensively used in desktop and laptop cooling applications. Despite drawbacks in deploying air cooling techniques, this technology is here to stay at least for low powered devices. Khan et. al [16] has analyzed the role of fin geometry in heat sink performance. They concluded that the square pin fin heat sink was worst as far as heat transfer and drag force, and in terms of total entropy generation rate. Rectangular and elliptical pin fin outperformed all other fin geometries in terms of total entropy generation rates. Bar-Cohen and Iyengar [17, 18] established geometric constraints that are encountered in today's heat sinks, optimized the fin geometry to increase the heat transfer coefficient by minimizing weight and pressure drop based on a least energy and least-material methodology. Moreover on printed wiring boards, in order to cool the critical components, heat sinks of various kinds are by far the most common heat management option deployed. So still there is a lot of research going on optimizing the heat sink design to fulfill the purpose of thermal management keeping in mind the other constraints.

#### 2.3 Research Overview

Summarizing the air cooling technology, alongside having constraints of low heat transfer coefficients compared to liquid and direct cooling technologies, increased size and weight constraints, this technology has an edge and is here to stay owing to its low cost, simplicity, and ease in installation and maintenance. There is a need to develop a reference

methodology to characterize the heat sinks, so that consistency is maintained between vendor specifications and customer requirements. An effort has been made in that regards, to benchmark a heat sink tester which could be used to characterize various heat sinks with acceptable dimensional and material properties compatible to the tester.

Heat sinks tested here are provided by Alpha Novatech Inc. and Aavid Thermalloy Inc. [34, 35]. In many instances, it is directly assumed that the base temperature of heat sink is constant. In reality however, temperature and hence heat flux distribution across the base is not uniform. According to the computational and uncertainty analysis done in [7, 8] a huge amount of error is introduced in measuring heat flux and heat transfer coefficient due to the errors in temperature measurement. To an extension of the previous work, several commercially available heat sinks are characterized and validated against vendor specifications and computational results.

## CHAPTER 3

## COMPUTATIONAL MODEL

#### 3.1 Computational Model Description

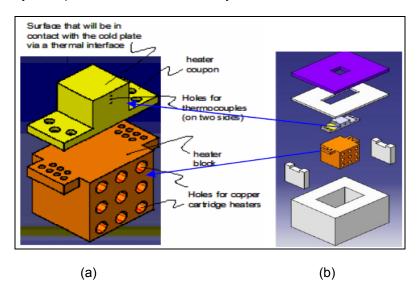

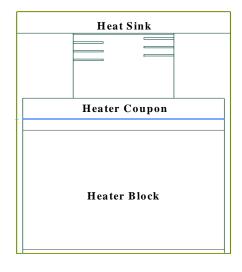

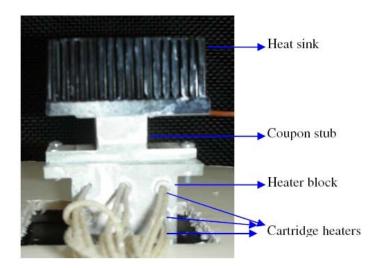

The heat source used in this study is a custom made heat sink tester that was designed to have a uniform heat flux distribution at the base of the heat sink. A unique approach of heater block and heater coupon was used. The advantage of this type of arrangement is that with the heater block remaining the same, coupons of different materials and different cross-sections can be used. 10 x 10 mm (100 mm<sup>2</sup>) and 20 x 20 mm (400 mm<sup>2</sup>) are the different sizes and corresponding cross-section of heater coupons used for characterization. Thus, various different heat sinks or cold plates can be tested. The computational modeling was strongly validated by an uncertainty analysis using Monte Carlo simulations and it was found that error involved in heat transfer coefficient was within 10% of the simulation result, with assumed errors in concerned parameters [7]. Figure 3.1 depicts the solid model of heater coupon and heater block followed by an exploded view of the assembly.

Figure 3.1 Heat sink tester arrangement (a) Heat sink tester layout (b) Exploded view of the assembly

# 3.2 Icepak Modeling

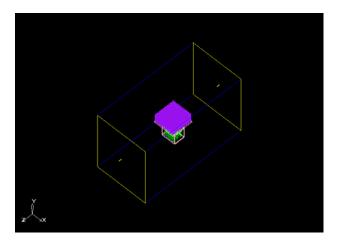

Icepak<sup>™</sup> a commercial code is used to compare and validate the experimental studies. Figure 3.2 shows the Icepak model for the heat sink tester apparatus. A macro in Icepak (JEDEC enclosure) is used to simulate a numerical wind tunnel to replicate actual testing conditions as shown in figure 3.3. The cold plate tester is positioned in center of the enclosure. Heat transfer coefficient of 1 W/m<sup>2</sup>K is applied on the heat sink tester to take into consideration the losses. Same cfm of 18 to 24 range is used in computational experiments, as it was done while experimental characterization.

Figure 3.2 Icepak model of the heat sink tester apparatus

Figure 3.3 Computational model for the heat sink tester setup

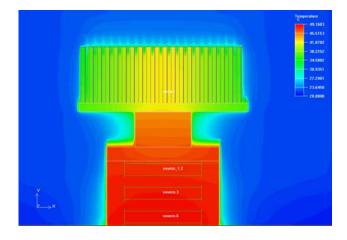

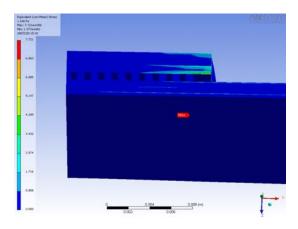

Three heat sinks that were tested on an air flow bench were also studied computationally. A heat transfer coefficient of 1  $W/m^2K$  is applied on the blocks for modeling of losses. The temperature difference between base of heat sink and ambient temperature divided by the power applied is taken as the thermal resistance of heat sink. Figure 3.4 shows the temperature contour across the heat sink. The contours are taken at mid-plane in the z direction.

Figure 3.4 Temperature contours taken at the center of Z-plane

# 3.3 Meshing

Figure 3.5 shows hexahedral meshing used to mesh the model. The model is meshed heavily in solder and thermocouple areas and a relatively coarse mesh is used in the cabinet and other areas.

| orden er den her en ser sen handen er<br>orden er den her er ser sen handen er<br>orden |

|-----------------------------------------------------------------------------------------|

|                                                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

| perso (Tw.)<br>averaginum (Li                                                           |

| <br>                                                                                    |

|                                                                                         |

| fautr X                                                                                 |

Figure 3.5 Model mesh (Hexahedral mesh)

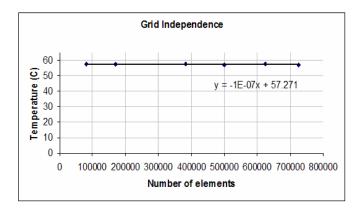

Figure 3.6 shows the grid independence. The temperature of one of the heaters is monitored; the number of elements is changed from 70,000 to 750,000. The percentage variation in temperature is observed to be within 1%, hence the model can be considered to be grid independent.

Figure 3.6 Grid sensitivity analysis

## CHAPTER 4

## EXPERIMENTAL VALIDATION

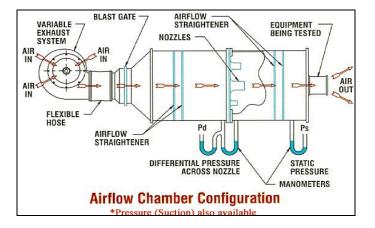

#### 4.1 Airflow Chamber Configuration

The air flow chamber used for the experimental testing comprised of different

components and sections as shown in figure 4.1. The air flow chamber facilitates computing:

- System resistance

- Fan performance curves

- Thermal resistance

Figure 4.1 Schematic of an air flow bench [37]

Air flow bench comprised of a blower with capability of producing flows in both the directions at ~10-4000 cfm. It has three tubes connected to pressure transducers for static and differential pressure measurement. The pressure transducers are connected to a Data Acquisition Centre (DAC) and ultimately to LabVIEW for data analysis and measurement [29]. The pressure transducer situated on the side of the airflow plenum allowed measurement of the static pressure drop across the test section while the second pressure transducer measured pressure drop across the nozzle section and gave airflow in cubic feet per minute (cfm). By

selecting an appropriate nozzle or combination of nozzles in the nozzle section, desired flow rate can be generated as per requirement. Air flow rate can be adjusted by changing the rotational speed of the counter blower.

## 4.2 Test Setup

The heat sink tester assembly comprised of the heater block where nine cartridge heaters were used, and a heater coupon that uniformly spreads heat at the base of the heat sink. The coupon has flux meter arrangement as shown in figure 4.2. Holes are drilled at a fixed distance of 1 mm starting from top of the coupon stub. Thermocouples are inserted in these holes to obtain the temperature. Six temperature values obtained are plotted against position of thermocouples starting from the base of heat sink. The Y intercept of curve drawn through these points gives the temperature of the base of heat sink. Various heat sinks were tested to confirm reliability of the heat sink tester and ensure repeatability.

Figure 4.2 Experimental setup

## 4.3 Experimental Test Procedure

With the setup discussed, following is the procedure that was followed to carry out the experiment:

- Total power across all the nine heaters was 28 W.

- Heat sink tester assembly other than the heat sink area was insulated in order to minimize the heat transfer losses.

- At all the interfaces; heaters and heater block, heater block and heater coupon, heater coupon and thermocouple and heater coupon and heat sink, a thermal interface material (Silicone compound K = 3.7 W/m °K) was applied to minimize the interface thermal resistance.

- The system was pressurized, or in other words made leak proof to avoid any air leakage during the test to minimize losses.

- Nozzle section was setup up with nozzles that could provide the required flow rate.

- After powering up the cartridge heaters and turning on the counter blower at the required flow rate, sufficient time was given to the system so that the steady state was achieved.

- At this point, the pressure and temperature readings were taken, and temperature readings were extrapolated to obtain the temperature at the base of the heat sink.

This experimental procedure was repeated throughout the experimental investigation to ensure both accurate and reliable data. This data was then compared to the data obtained from the vendor data and CFD analysis.

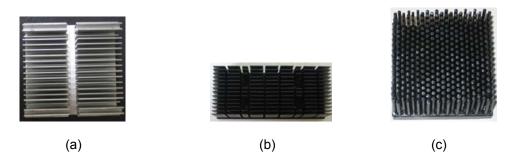

## 4.4 Commercial Heat Sinks Tested

Three heat sinks were tested on the air flow bench. The results were compared with the uncertainty analysis and computational results, thus validating the accuracy of the heat sink tester. The heat sinks tested in this study are shown in figure 4.3.

Figure 4.3 Heat sinks tested [34, 35], (a) 11-P351-03, (b) P52120SB-45B and (c) PAL 6030

#### 4.5 Calculations

The data that was collected during the experiment using LabVIEW, was for the differential pressure ( $P_n$ ), static pressure, and temperature at the base of the heat sink ( $T_b$ ). The ambient air temperature ( $T_a$ ) reading was obtained from a gauge connected to the air flow bench. The values for current and voltage were obtained from the variable voltmeter.

The calculation of thermal resistance of the heat sink was computed from the formulation:

$$T_b = T_a + (P \times R_{th}) \tag{4.1}$$

Where power generated by the cartridge heater is given by

$$P = V \times I \tag{4.2}$$

The airflow rate generated by the airflow bench is given by,

$$Q = (A \times V) \times 60 \tag{4.3}$$

where

$$V = \sqrt[2]{\frac{2gP_n}{r}}$$

(4.4)

## **RESULTS AND DISCUSSIONS**

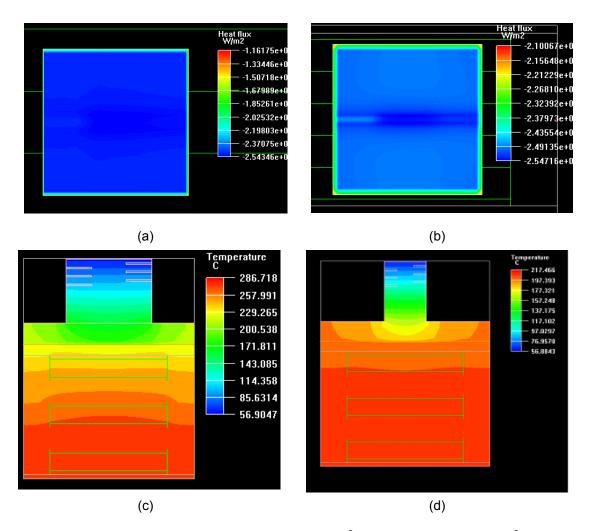

## 5.1 Area Effect on Heat Transfer

To understand the effect of area on the heat distribution pattern, heater coupons with 100 mm<sup>2</sup> and 400 mm<sup>2</sup> area were characterized using CFD tool Icepak.

Figure 5.1 Area effect on heat distribution (a) 400 mm<sup>2</sup> heater coupon (b) 100 mm<sup>2</sup> heater coupon (c) 400 mm<sup>2</sup> heater coupon temp contours (d) 100 mm<sup>2</sup> heater coupon temp contours

As can be seen from temperature contours shown in figure 5.1, 400 mm<sup>2</sup> area heater coupon has got more uniform heat distribution with lower maximum temperature value, attributed to higher heat transfer area. Heater coupon with 100 mm<sup>2</sup> area has a disadvantage of higher heat loss for the same heater coupon height at the cost of heat distribution. Hence, this data should be used to bring about the right trade-off while selecting the heat sink tester so an optimum design is obtained with maximum possible accuracy.

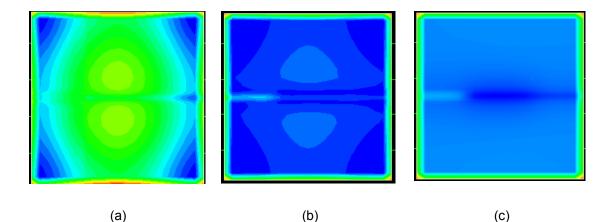

Figure 5.2 depicts the temperature contours for 100 mm<sup>2</sup> area heater coupon looking from the top at various heights from the top. Greater the height of the coupon from the bottom, it allows more time for uniform heat distribution and better accuracy. But the height of the coupon comes at the cost of heat loss, so again an optimized height should be designed to bring about the right balance between the heat loss and accuracy due to better heat distribution.

#### 5.2 Experimental Results

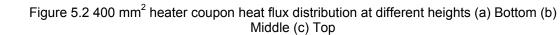

A series of heat sinks were tested on an air flow bench. The heat sinks were tested with different flow bypass areas and varied range of cfm to have a good idea about the thermal resistance. Initially readings were taken in conditions that were described by the vendor and with an off the shelf heat source mainly for benchmarking purposes. It is observed that the thermal resistance curve suggested by vendor and the curve obtained are in good agreement (within 10 %).

Figure 5.3 Thermal resistance curve for P2120SB-45B heat sink

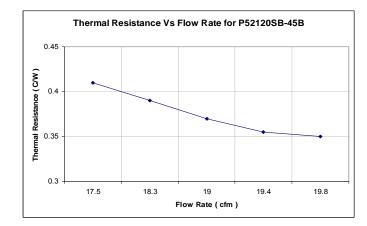

Figure 5.4 Thermal resistance curve for PAL 6030 heat sink

Figure 5.3 and 5.4 shows the thermal resistance vs. flow rate curve for P52120SB-45B and PAL 6030 heat sinks respectively. These were tested under the conditions that were described by the vendor. It is verified that the arrangement gives results under acceptable limits. The same heat sinks were tested with the designed heat sink tester. It is observed from comparisons that the thermal resistance curve presented the exact same trend but the values were significantly different. Difference in magnitude was expected as we were using a source of different cross-sectional area. Moreover, the temperature readings were flickering. This was

mainly due to the limitation on the accuracy with which the thermocouple can measure the temperature. The thermal interface material was applied to the spherical tip of T-type thermocouple and was tested again, and it was found that the readings became less flickering and ultimately brought the error down. Once it was assured that the methodology used was correct, other heat sinks were tested using the 400 mm<sup>2</sup> heater coupon.

5.3 Computational & Experimental Results Validation

Figure 5.5 Thermal resistance comparison for PAL 6030 heat sink

Figure 5.6 Thermal resistance comparison for 11-P351-03 heat sink

Figure 5.7 Thermal resistance comparison for P52120SB-45B heat sink

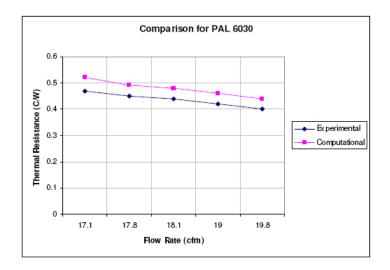

Figures 5.5, 5.6 and 5.7 show the thermal resistance plots of PAL 6030, 11-3P51-03 and P52120SB-45B heat sinks taken at same CFM range. Heat sink P52120SB-45B was also tested using  $100 \text{mm}^2$  heater coupon to check the effect of area on the thermal resistance. The results obtained verified the importance of spreading resistance as the thermal resistance value jumped significantly from 0.75 to 1.1 (°C/W), as shown in figure 5.8.

Figure 5.8 Thermal resistance comparison for different heater coupon areas

## 5.4 Inferences

The difference in thermal resistance can be considered associated with the spreading resistance across the heater coupon and heat sink. The cartridge heaters were applied a layer

of Silicone paste to avoid heat loss. The thermocouples were inserted fully into the flux meter type arrangement still there was a possibility that there can be some heat loss there too. The temperature obtained after extrapolation was compared with the readings taken by placing thermocouples directly on the top. They were in agreement and hence one dimensional heat flow was confirmed.

Comparing the computational (0.93°C/W) and experimental (0.84°C/W) thermal resistances for PAL 6030 heat sink, it was observed that there was a 10% difference. This difference in thermal resistance can be attributed to the heat losses.

#### CONCLUSION

An attempt has been made to study thermal resistance of heat sinks using a custom designed heat sink tester. The heat sink tester was designed to provide uniform heat flux at the base of the heat sink. The computational design was done in  $Icepak^{TM}$ . The uncertainty analysis was done by incorporating box-muller equation in Monte-Carlo simulations [7]. The experimental study validated this uncertainty analysis and computational model.

The difference in thermal resistance depends a lot on size of heat source and heat flux distribution at the base of the heat sink. The thermal resistance value of PAL 6030 heat sink was found to be 0.84 °C/W by experimental study and 0.93 °C/W by computational study which corresponds to 9.6% error using a 400 mm<sup>2</sup> heater coupon. The difference in computational and experimental thermal resistances was because of the difference in assumed thermal resistance of interface material (in computational model) was different than the actual one. This could be because of non-uniform thickness of interface and non-uniform thermal conductivity. Also there can be some loss of heat due to conduction and natural convection through insulation. So summarizing, the heat sink tester developed provides a good reference for validating various commercially available heat sinks depending on geometric compatibilities.

Future work needs to be done to develop and establish an experimental setup and procedure, to characterize heat management devices for manufacturing flaws like porosities, impurities, fan failures and likes. This procedure needs to be quick in order that the characterization can be done in very short times for permissible number of tests.

29

PART-2

# EFFECT OF WEIGHT OF HEATSINK ASSEMBLY ON MECHANICAL RELIABILITY OF A WIRE BONDED PLASTIC BALL GRID ARRAY PACKAGE

## INTRODUCTION

#### 7.1 Background

Plastic Ball Grid Arrays (PBGA) is one of the most popular packaging alternatives for high I/O devices in the industry and has more or less replaced traditional plastic quad flat packs (PQFPs). With no leads to bend, PBGA has greatly reduced co-planarity problems and thus has minimized handling issues. Also during reflow the C4 interconnect are self-centering, reducing placement problems during surface mounts. The larger ball pitch (1.25 mm) gives the package good strength and improves the yield. From the thermal and electrical performance perspective, PBGA has got an edge over QFPs and PQFPs. Owing to all the advantages, they find a wide range of applications in computers, automotive electronic systems, wireless infrastructure, etc.

Drastic downsizing and increased performance of packages imposes higher heat dissipation problems and asks for more efficient heat sinks. Depending on the thermal load applied by the package and the cooling requirement, there are different types of heat sinks available with various materials, design and accessories. Primary objective of the heat sink is to absorb heat from the processor and dissipate it to the atmosphere by conduction, convection and radiation. Clip-on type, screw-on type and adhesive bonding [10] are means by which heat sink can be mounted on to the package. The material of the heat sink, its size, accessories, and the mounting mechanisms corresponds to the load applied by the heat sink on to the package. Also, with increased performance of the package, the weight of the heat sink also increases.

In this study a stress analysis of WB-PBGA was carried out to study the effect of weight of heat sink assembly on the mechanical reliability of the package. While doing so, a three dimensional finite element model (FEM) of WB-PBGA and printed wiring board (PWB) was solved numerically to predict the stresses induced and assess their impact on the mechanical integrity of the die and package as a whole, due to the weight of the heat sink assembly.

Die and C4 interconnect stresses have also been examined to evaluate package reliability. Stresses induced within the die and C4 interconnect are examined for different heat sink materials. In addition, the variation of force developed by heat sink clip and screw (screw-on type mounting) has been examined. The modeling utilizes a solid model for geometry creation and a finite element commercial program for simulation.

#### 7.2 Research Overview

Previous work has been done to study the effect of adhesively bonded heat sink and the effect of the weight of the heat sink on the mechanical reliability of a two-layer wire bonded plastic ball grid array (WB-PBGA) package [10, 11]. Heat sink with its weight and mounting mechanism apply pressure and thereby stresses on the package. There are two types of heat sink mounting techniques discussed here and their respective stress fields. Clip-on and screwon type are the two methods by which heat sink can be mounted on to the package. In clip-on type, a clip is placed on two of the sides of the heat sink. The clip, with its two ends fixed along with the help of hooks from the package, applies a load to the center of the device. For the screw-on type there is only one clip which is fixed in the center with the help of screws on two ends. So basically owing to the difference in the arrangement, stresses induced by the two techniques are different and were analyzed. Figure 7.1 shows the trend of the thermal resistance vs. the heat sink weight.

Figure 7.1 Thermal resistance vs. weight of thermal management device

## 7.3 Package Description

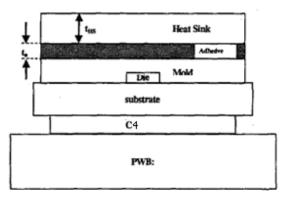

A schematic diagram of WB-PBGA model whereby stress analysis was carried out is shown in figure 7.2. Dimensions of different components of the package are tabulated in table 2. A silicon die is placed over a substrate with the help of a die attach material. The die is further encapsulated by an Epoxy Molding Compound (EMC). EMC absorbs stresses acting on the die and also insulates the die from atmospheric effects forming a protective covering around the die. C4 interconnect provides connection between the bottom surface of the substrate and the Printed Wiring Board (PWB).

Figure 7.2: Package schematic [9]

C4 interconnect forms a full array with a pitch of 1.25 mm totaling 391. To maintain a junction temperature of a package below a specified limit, a heat sink is mounted on top of the EMC with the help of one of the heat sink mounting techniques discussed. Substrate considered for the package is as shown in figure 7.3, is made up of five layers which include two layers of solder mask, two layers of substrate copper layer and one BT composite layer. PWB used in this analysis is modeled according to the Joint Electron Device Engineering Council (JEDEC) standards [23]. It is made up of one signal layer, three power layers (IS2P) with upper and lower trace layers, thick internal power planes and thick core layers as shown in the figure 7.4. The thickness of different layers of substrate and PWB is shown in figure 7.3 and figure 7.4, respectively.

| Solder Mask          |  |

|----------------------|--|

| Cu Layer (0.36mm)    |  |

| BT Resin (0.15mm)    |  |

| Cu Layer (0.36mm)    |  |

| Solder Mask (0.07mm) |  |

Figure 7.3 Layers of substrate [9]

| Solder Mask (0.043mm)     |

|---------------------------|

| Cupowerplane (0.036mm)    |

| FR-4 Dielectric (0.55mm)  |

| Cupowerplane (0.036mm)    |

| FR-4 Dielectric (0. 55mm) |

| Cupowerplane (0.036mm)    |

| FR-4 Dielectric (0.257mm) |

| Solder Mask (0.043mm)     |

Figure 7.4 Layers of printed wiring board [9]

## COMPUTATIONAL MODEL

## 8.1 Modeling Methodology

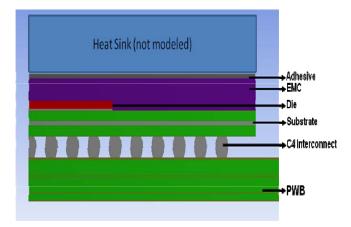

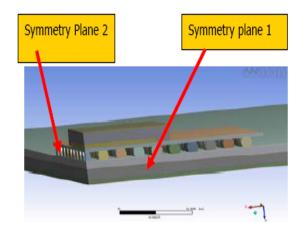

Geometry of the package is created as different parts and assembled using Pro/Engineer wildfire 3.0. This Pro/E assembly file is imported into ANSYS Workbench <sup>™</sup> 10.0 to carry out further stress analysis [27, 28]. Figure 8.1 shows a quarter model of the package, heat sink not modeled.

Figure 8.1 Quarter model of the package

Figure 8.2 Quarter model with symmetry planes

Densities for different materials of the heat sink are as tabulated in table 1. Dimensions and material properties of the package components in terms of Young's Modulus and Poisson's ratio are tabulated in table 2 and table 3 respectively.

| Material of heat sink | Density (kg/m³)       |

|-----------------------|-----------------------|

| Copper (Cu)           | 8.2 x 10 <sup>3</sup> |

| Aluminum (Al)         | 2.7 x 10 <sup>3</sup> |

| Graphite (Gr)         | 2.1 x 10 <sup>3</sup> |

Table 8.1: Heat sink material densities [31]

| Component           | Dimensions (mm)           |  |  |

|---------------------|---------------------------|--|--|

| Die                 | 10 X 10 X 0.3             |  |  |

| Die Attach Material | 10 X 10 X 0.05            |  |  |

| Mold compound       | 25 X 25 X 1.15            |  |  |

| Substrate overall   | 25 X 25 X Total           |  |  |

|                     | Thickness                 |  |  |

| C4 interconnect     | Pitch = 1.25 (Full array) |  |  |

|                     | C4 Diameter, D= 0.76      |  |  |

|                     | height= 0.28              |  |  |

| PWB overall         | 100 X 100 X 1.57          |  |  |

| Adhesive material   | 25 X 25 X 0.15            |  |  |

| Heat sink           | 70 X 90 X 35              |  |  |

| Component           | Young's | Poisson's |

|---------------------|---------|-----------|

|                     | Modulus | Ratio     |

|                     | (GPa)   |           |

| Die                 | 162.7   | 0.278     |

| Die Attach Material | 5       | 0.3       |

| Molding Compound    | 15.78   | 0.25      |

| Substrate           | 113.7   | 0.33      |

| PWB                 | 13.37   | 0.11      |

| Solder Mask         | 4.13    | 0.2       |

| C4 Interconnects    | 19.71   | 0.35      |

| Adhesive            | 25      | 0.33      |

| PWB Solder mask     | 4.13    | 0.2       |

| T1/B1 BT composite  | 24      | 0.39      |

| PWB copper layer    | 113.7   | 0.33      |

Table 8.3: Material properties [9, 31]

Figure 8.2 shows the quarter model of the package with the applied symmetry planes. Displacement on the symmetry side has been fixed in all directions i.e. x, y, z = 0 along entire symmetry planes. Material properties as given in table 3 have been assigned to the respective components. Young's Modulus and Poisson's ratio are the only material properties considered while doing this analysis. Heat sink material density is used to calculate pressure exerted by the heat sink on to the package using following expressions:

Mass of heat sink,

$$m = \rho \times V$$

(8.1)

Corresponding force,

$$F = m \times a$$

(8.2)

Equivalent pressure,

$$P = \frac{F}{A}$$

(8.3)

#### 8.2 Heat Sink Assembly

When analyzing the reliability of the package, we need to consider all forces acting on it. This study specifically concentrates on two forces, first the force due to the weight of the heat sink and secondly, force due to the heat sink mounting technique used. The weight of the heat sink will vary with the type of heat sink material used which would ultimately be a function of the density of the heat sink material. Copper, Aluminum and Graphite are the heat sink materials considered here. The heat sink mounting techniques are:

- 1. clip-on type and

- 2. screw-on type

Both these mechanisms apply force on the heat sink in a different manner which is explained in the following sections.

## 8.2.1 Heat Sink Weight

Heat sink weight is one of the important factors which lead to stresses in the package. Further, weight applied by the heat sink is a direct function of the density of the heat sink material. Here Cu, Al and Gr are the materials used for the heat sink. All of these materials have their own merits and demerits based on their thermal capabilities and weight factor. Depending on the application, thermal performance, and stress limitations one needs to select the optimum configuration.

Figure 8.3 Pressure applied due to heat sink weight

For calculating the force applied by the heat sink, the density of the heat sink material for a given heat sink volume was considered. The pressure was found out using the adhesive top area as shown in figure 8.3.

#### 8.2.2 Heat Sink Mounting Techniques

## 8.2.2.1 Clip-on Type

One of the methods used to mount a heat sink on top of the package is with the help of clip attachments. There are two clips total, one on each side of the heat sink as shown in figure 8.4. The two ends of the clip have hooks, which apply pressure on the sides of the heat sink with the help of a cam like central attachment. It has been found that the clip force applied is of the order of 2-5 lb<sub>f</sub> [33]. Clips retain the heat sink assembly in the socket by exerting a force on the heat sink and the socket.

Figure 8.4 Clip-on type heat sink [9]

The clip force, in turn, aids in forcing the grease to fill the many microscopic peaks and valleys on the heat sink and package surface, thereby reducing the interface thermal resistance. However, it has been determined that increasing the clip force beyond 5 lb<sub>f</sub> does not significantly increase the thermal performance of varied interfaces in the package. So in this analysis, a clip force of 2 to 5 lb<sub>f</sub> is considered, and the effects are analyzed on different components of a package. During analysis in ANSYS and while applying the boundary

conditions, an area equivalent to clip dimensions was considered on the sides of the heat sink. The corresponding pressure values as given by equation 9 were used as shown in figure 8.4.

8.2.2.2 Screw-on Type

For this case, only one clip [32] is used as compared to two clips in the clip on type arrangement. Moreover, here the clip is placed right in the center of the package with the help of screws on the ends of the clips. A cam like attachment in the center of the clip applies force on the heat sink, which is then transferred to the package. To calculate the force applied by the clip in this case, cantilever theory is used. Considering one screw to be tightened completely on one end and the central cam like attachment just touching the heat sink surface, there would be some deflection towards the second screw side.

## Figure 8.5 Screw-on type heat sink [9]

To overcome this deflection, force needs to be applied to offset. In the process of making the deflection zero, there would be some reaction force acting at the center, which would be the force applied by the arrangement. The deflection-force relationship used to determine reaction is:

$$\delta = \frac{PL^3}{EI} \tag{8.4}$$

The area where the force would be applicable is again considered equal to clip dimensions. The point to be noted here is, the clip in this type of arrangement is in the center of

the package as shown in figure 8.5. So, from the available force and area a corresponding pressure is calculated, which is then used for the analysis.

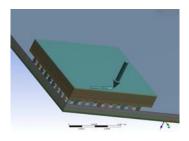

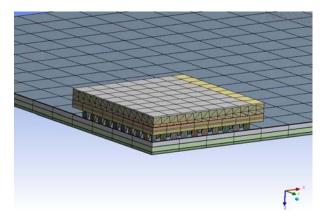

## 8.3 Meshing

When the FEM is created it generated 284,966 nodes and 51,125 elements. With this large number of elements and nodes the analysis would take a lot of CPU time (60 min), so a quarter model has been created by imposing symmetry conditions decreasing the number of nodes and elements to 91,418 and 17,141, respectively reducing the CPU time to 15 minutes. Contact / target elements between components are created automatically within the ANSYS Workbench using bonded contact type as a default option. Quarter model of the package with the mesh is as shown in figure 8.6.

Figure 8.6 FEM of the given package (Quarter model)

## **RESULTS AND DISCUSSIONS**

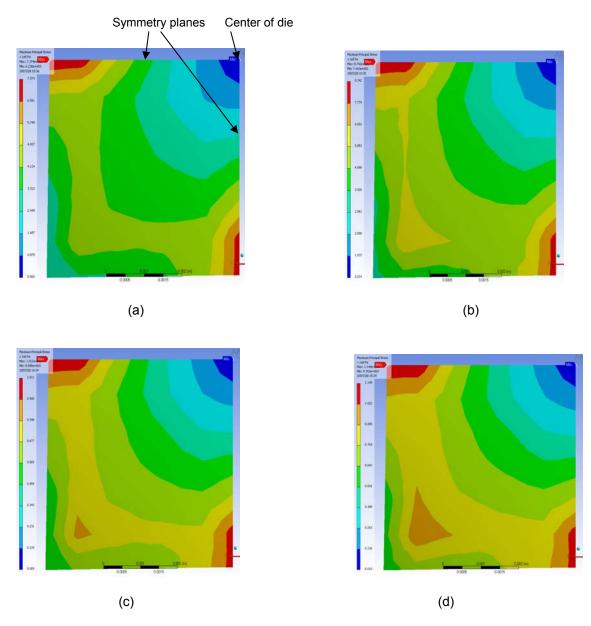

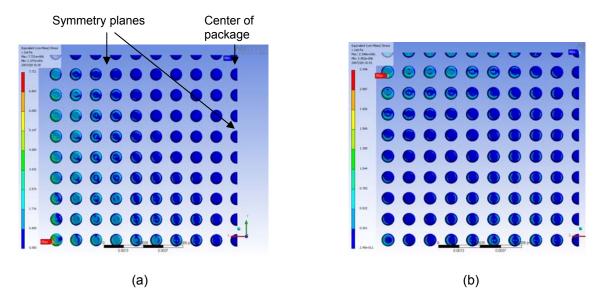

The stresses with different heat sink materials and the two mounting techniques were examined, and are discussed in the following sections. Figure 9.1 shows the equivalent stress distribution for the given package. As discussed earlier, a quarter model has been used owing to the advantage a symmetric model had to offer and figure 9.2 (a) shows the symmetry planes and the location of center of the die. The same convention is used in all the analysis plots.

Figure 9.1 Equivalent stress for the given package

Figure 9.2 shows the effect of different clip forces on stresses induced in the die. The heat sink used is Cu with clip force varying from 2 to 5  $lb_r$ . It can be seen that stresses are maximum at the edges of the die corresponding to where the pressure is applied on the sides of heat sink by the clip attachment. Moreover, by increasing the clip force, the stress distribution is moving towards the center of the package.

Figure 9.2 Die stress for Cu heat sink due to clip-on type attachment (a) 2 lb<sub>f</sub> clip force, (b) 3 lb<sub>f</sub> clip force, (c) 4 lb<sub>f</sub> clip force, (d) 5 lb<sub>f</sub> clip force

Figure 9.3 shows the effect of screw force corresponding to clip deflection for Cu heat sink. As can be seen, the stresses are concentrated more towards the central part of the package. Moreover with increase in screw force, the stress distribution is moving towards the central part of the package.

Figure 9.3 Die stress for Cu heat sink due to screw-on type attachment, corresponding to clip deflection of (a) 5mm, (b) 4 mm, (c) 3 mm, (d) 2 mm

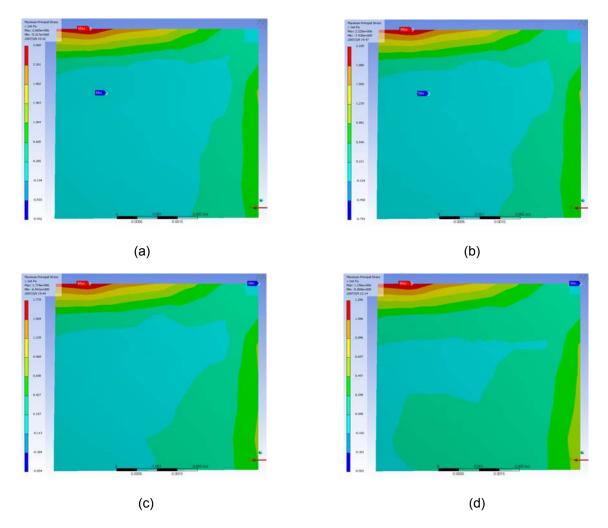

The magnitude of stress induced in die due to screw-on type arrangement is quite high as compared to that induced by clip-on type arrangement. Figure 9.4 shows the maximum stress on C4 interconnect with clip-on and screw-on type arrangements. Again owing to the arrangement, C4 interconnect stresses in clip-on type are more concentrated towards the periphery and towards the central part for screw-on type. Also the magnitude of stress in clip-on type is quite high as compared to screw-on type. So based on the limiting stresses for die or C4 interconnect, choice of mounting technique can be made.

Figure 9.4 C4 interconnect stresses for Cu heat sink (a) 5 lb<sub>f</sub> clip force (b) Screw force corresponding to 5mm clip deflection

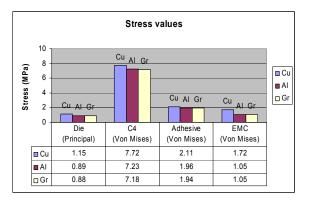

Figure 9.5 Effect of weight of heat sink on package stresses for clip type attachment

Figure 9.5 shows the stresses induced in different components of the package with different heat sink materials at a given pressure system for clip-on type arrangement. As can be seen, the weight of the heat sink is an important factor which leads to stresses in the package. Cu with the maximum density induces maximum stress values whereas AI and Gr being less dense induce lower stresses. C4 interconnect is the package component where maximum stresses are produced for clip-on type arrangement.

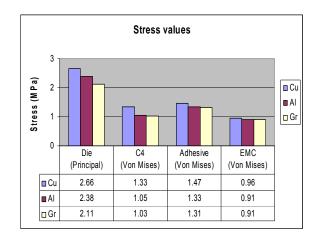

Figure 9.6 Effect of weight of heat sink on package stresses for screw-on type arrangement

Figure 9.6 shows the stresses induced in different components of the package with different heat sink materials at a given pressure system for screw-on type arrangement. Here again the weight of the heat sink plays a major role in determining the stress on the package assembly. However, for this case, the die is the package component where the maximum stresses are induced.

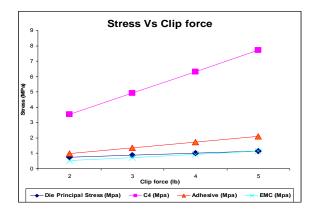

Figure 9.7 Effect of clip force (lb<sub>f</sub>) on package stresses

Figure 9.7 shows effect of clip force on stresses induced in different components of the package. Obviously with an increase in clip force the stresses induced increases but as discussed, an increase in clip force beyond a certain value does not add much

to the performance of the package. Also, there is a limit to the stress each package component can withstand depending on its material properties. Based on the analysis done, clip force to be applied can be determined with respect to the limiting stresses on the package.

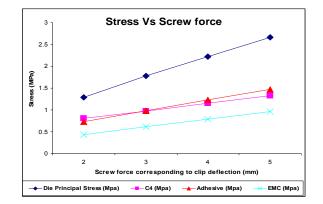

Figure 9.8 Effect of screw force corresponding to clip deflection (mm) on package stresses

Figure 9.8 shows effect of screw force on stresses induced on components of the package. Here with an increase in screw force, stresses induced in the package components also increases. A compromise between screw force and stresses allowable needs to be determined. Also, it can be seen that absolute magnitude of stresses induced in this type of arrangement are a lot less than the clip-on type arrangement.

Figure 9.9 Effect of heat sink mounting attachment on Die and C4 interconnect stresses induced for a given heat sink

Figure 9.9 essentially implies that clip-on type arrangement leads to high stresses on C4 interconnect, whereas screw-on type has high stress fields on the die. Moreover, the overall magnitude of stress is high in clip-on type arrangement as compared to screw-on type arrangement. So based on the application, choice can be made for the most effective heat sink mounting mechanism. Figure 9.9 shows the relationship between the applied weight from the heat sink on the surface area of the die vs. the associated stress on the die's balls. Figure 9.10 reveals that for equivalent weight of different materials, the associated stress on the die is identical.

Figure 9.10 Die stress vs. weight applied by the heat sink

#### SUMMARY AND CONCLUSION

A 3D finite element stress analysis of WB-PBGA package is carried out to study the effect of the weight of a heat sink and heat sink mounting techniques on mechanical reliability of the package. Here emphasis was given to stresses induced with different heat sink mounting techniques. The result showed high stresses in C4 interconnect for clip-on type arrangement and high die stresses for screw-on type arrangement with the absolute values of induced stresses being maximum for clip-on cases. Based on this results a decision can be made on the type of heat sink mounting technique to be used for a given package. Also, the analysis reflected that stresses induced in die and C4 interconnect are towards the periphery of the package for clip-on type arrangement and are towards the central part of the package for screw-on type arrangement and are towards the concentration on the periphery for clip-on type and in the central part for screw-on type. Moreover the stress contours showed that stresses are more spread out for clip-on type as compared to screw-on type arrangement.

The effect of the weight of different materials of heat sink was also analyzed. As was expected Cu being fairly heavier compared to Al and Gr induced more stresses on the package. But again Cu with high thermal conductivity gives better thermal performance as compared to Al and Gr. So keeping in mind weight of heat sink and the thermal performance required, an optimum choice has to be made. This again can be combined with type of heat mounting technique to be used depending on the package.

Further investigation needs to be carried out taking into consideration the heat sink assembly, limiting permissible stresses for package components, and thermal performance

49

required from the package. Also, this all can be combined with thermal cyclic loading on the package and thereby study their reliability issues. Moreover, the objective of this study was to investigate the effect of weight of heat sink and heat sink mounting mechanism on mechanical reliability of considered package. However, some arbitrary heat sink and thereby heat sink weight was considered, instead the analysis needs to be investigated to an industry problem with realistic weight and force values.

PART-3

## COMPACT MODELING OF A TELECOMMUNICATION CABINET

## INTRODUCTION

#### 11.1 Introduction

CommScope integrated cabinets provide environmentally secure enclosures for all types of electronic equipment. The cabinets optimize equipment density, heat transfer and dissipation, power reserve, environmental protection and ease of installation [30]. These types of enclosures, with their multiple equipment configurations, demand thermal performance tests and analysis.

CFD allows quick and robust analysis for multiple test configurations and design of experiments. Without a computational approach, time-consuming prototype testing must be performed. Moreover, the permutations of equipment configurations can quickly grow, leading to an extended cycle of prototype builds, testing, and test configuring. With the ever increasing time-to-market requirements, testing a large enclosure with multiple configurations can be accelerated through simulation. Such simulations are very effective for studying design alternatives and exploring viable what-if scenarios. To ensure reliability and accuracy of the simulation model, high levels of detail are necessary in the regions of critical components. At the same time, non-critical areas can have reduced detail and lower mesh counts, if modeled properly.

#### 11.2 Research Overview

Computational Fluid Dynamics (CFD) is widely used in the telecommunication industry to validate experimental data and obtain both qualitative and quantitative results during the

52

upstream and downstream of the product development. The objective of this research is to present an overview of techniques to minimize the computational time for complex designs such as a heat exchanger used in telecommunication cabinets. The discussion herein presents the concepts which lead to developing a compact model of the heat exchanger, reducing the mesh count and thereby the computation time, without compromising the acceptability of the results. The model can be further simplified by identifying the components significantly affecting the physics of the problem and eliminating components that will not adversely affect either the fluid mechanics or heat transfer, further reducing the mesh density. Compact modeling, selective meshing, and replacing sub-components with simplified equivalent models all help reduce the overall model size. The model thus developed is compared to a benchmark case without the compact model. Given that the validity of compact models is not generalized, it is expected that this methodology can address this particular class of problems in telecommunications systems. The CFD code FLOTHERM<sup>TM</sup> by Flomerics is used to carry out the analysis.

#### 11.3 Cabinet Description