# COMPLEXITY REDUCTION IN H.264 ENCODER USING

# OPEN MULTIPROCESSING

by

# **TEJAS PRAVIN SATHE**

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

# MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

THE UNIVERSITY OF TEXAS AT ARLINGTON May 2012 Copyright © by Tejas Sathe 2012

All Rights Reserved

#### ACKNOWLEDGEMENTS

It would not have been possible to complete this thesis without the guidance and the help of several individuals who in one way or another contributed and extended their valuable assistance

First and foremost, my utmost gratitude to my thesis advisor, Dr. K. R. Rao, whose sincerity and encouragement I will never forget. I really appreciate his helpful nature and care he takes for the students. I feel really proud to be Dr. Rao's student and a member of Multimedia Processing Lab.

I would like to thank Dr. Saibun Tjuatja and Dr. Ioannis D. Schizas for their valuable time and taking interest to review my thesis work. I am also very grateful to Dr. Dongil Han for his technical guidance and financial support.

I want to thank Dr. Roger Walker for offering the course 'Real Time Data Acquisition and Control', in which he taught parallel programming using OpenMP, which this thesis is based on.

This thesis would never have been completed without the encouragement and devotion of my family and friends. I express my sincere gratitude towards them.

April 20, 2012

#### ABSTRACT

# COMPLEXITY REDUCTION IN H.264 ENCODER USING OPEN MULTIPROCESSING

Tejas Sathe, (M.S.)

The University of Texas at Arlington, 2012

Supervising Professor: K. R. Rao

H.264 video standard developed by Joint Video Team has proven dramatic improvements in bit-rate efficiency, compression ratio, video quality and error resilience. But, all this is achieved at the expense of more than four times of the computational complexity due to various new features including quarter-pixel motion estimation with variable block sizes and multiple reference frames, adaptive directional intra-prediction, integer transformation based on discrete cosine transform, alternative entropy coding mode, Context-based Adaptive Variable Length Coding (CAVLC) or Context-Based Adaptive Binary Arithmetic Coding (CABAC), in loop de-blocking filter etc.

This thesis aims at reducing the encoding time for the video sequences while maintaining the same quality and compression efficiency using parallel processing approach. Entire video sequence is divided into four groups having one I frame each. In this thesis, the original JM software code, written in serial manner is enhanced in such a way that the encoding of all individual parts of the original video is implemented in parallel using the threads that are managed by Open Multiprocessing runtime system which shows more than 60% encoding time reduction.

JM 18.0 reference software is used in this thesis for implementing H.264 video encoder. The reference software along with manual is available at http://iphome.hhi.de/suehring/tml. The software manual includes information about the H.264 encoder and decoder input parameters, syntax, compilation issues, and additional information with regards to the best usage and configuration of the software.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTSiii                                                      |

|--------------------------------------------------------------------------|

| ABSTRACT iv                                                              |

| LIST OF ILLUSTRATIONS xi                                                 |

| LIST OF TABLES                                                           |

| LIST OF ACRONYMSxiv                                                      |

| Chapter Page                                                             |

| 1. INTRODUCTION1                                                         |

| 1.1 Introduction to video coding standards1                              |

| 1.2 The role and standardization procedure of video<br>coding standards2 |

| 1.3 Importance of H.264 Advanced Video Coding4                           |

| 1.4 H.264 CODEC standard4                                                |

| 1.5 Key features of H.264 video codec5                                   |

| 1.6 H.264 Profiles6                                                      |

| 1.6.1 Baseline Profile6                                                  |

| 1.6.2 Main Profile6                                                      |

| 1.6.3 Extended Profile6                                                  |

| 1.6.4 High Profiles7                                                     |

| 1.6.5 Applications of H.264 profiles8                                    |

| 1.7 Summary8                                                             |

| 2. NEED FOR TIME COMPLEXITY REDUCTION IN H.2649                          |

| 2.1 Key concepts involved in a video codec9                              |

| 2.1.1 CODEC and types of compression9                                    |

| 2.1.2 Working of H.264 video codec11                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1.3 Encoder11                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.1.4 Decoder14                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.1.5 Intra Prediction15                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1.6 Inter Prediction17                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1.7 Rate Distortion Optimization22                                                                                                                                                                                                                                                                                                                                                                   |

| 2.1.8 Transform, Scaling, and Quantization22                                                                                                                                                                                                                                                                                                                                                           |

| 2.1.9 In loop deblocking filter23                                                                                                                                                                                                                                                                                                                                                                      |

| 2.1.10 Entropy Coding24                                                                                                                                                                                                                                                                                                                                                                                |

| 2.2 Need for time complexity reduction25                                                                                                                                                                                                                                                                                                                                                               |

| 2.3 Summary27                                                                                                                                                                                                                                                                                                                                                                                          |

| 3. PARALLEL PROGRAMMING BASICS28                                                                                                                                                                                                                                                                                                                                                                       |

| 3.1 Introduction to parallel programming28                                                                                                                                                                                                                                                                                                                                                             |

| 3.2 Multicore                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.3 Parallel Computing in Microprocessors                                                                                                                                                                                                                                                                                                                                                              |

| 3.3 Parallel Computing in Microprocessors                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.4 Multi-threading on Single-Core versus Multi-Core Platforms                                                                                                                                                                                                                                                                                                                                         |

| 3.4 Multi-threading on Single-Core versus Multi-Core Platforms                                                                                                                                                                                                                                                                                                                                         |

| 3.4 Multi-threading on Single-Core versus Multi-Core Platforms    31      3.5 Concurrency    33      3.6 Thread level Parallelism    34                                                                                                                                                                                                                                                                |

| 3.4 Multi-threading on Single-Core versus Multi-Core Platforms    31      3.5 Concurrency    32      3.6 Thread level Parallelism    32      3.7 Basic concepts in parallel programming    32                                                                                                                                                                                                          |

| 3.4 Multi-threading on Single-Core versus Multi-Core Platforms    31      3.5 Concurrency    33      3.6 Thread level Parallelism    34      3.7 Basic concepts in parallel programming    34      3.8 Methods to do parallel processing    35                                                                                                                                                         |

| 3.4 Multi-threading on Single-Core versus Multi-Core Platforms    31      3.5 Concurrency    33      3.6 Thread level Parallelism    32      3.7 Basic concepts in parallel programming    32      3.8 Methods to do parallel processing    35      3.9 Requirements of a parallel programming language    36                                                                                          |

| 3.4 Multi-threading on Single-Core versus Multi-Core Platforms    31      3.5 Concurrency    32      3.6 Thread level Parallelism    32      3.7 Basic concepts in parallel programming    32      3.8 Methods to do parallel processing    35      3.9 Requirements of a parallel programming language    36      3.10 Summary    37                                                                  |

| 3.4 Multi-threading on Single-Core versus Multi-Core Platforms    31      3.5 Concurrency    32      3.6 Thread level Parallelism    32      3.7 Basic concepts in parallel programming    32      3.8 Methods to do parallel processing    35      3.9 Requirements of a parallel programming language    36      3.10 Summary    37      4. OPENMP: API SPECIFICATION FOR PARALLEL PROGRAMMING    36 |

| 4.4 Rea | asons behind the popular usage of OpenMP        | 42   |

|---------|-------------------------------------------------|------|

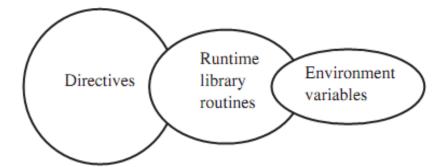

| 4.5 Op  | enMP Directives                                 | 44   |

|         | 4.5.1 parallel Construct                        | 44   |

|         | 4.5.2 loop Construct                            | 45   |

|         | 4.5.3 sections Construct                        | 46   |

|         | 4.5.4 single Construct                          | . 47 |

|         | 4.5.5 parallel loop Construct                   | . 47 |

|         | 4.5.6 parallel Sections Construct               | . 47 |

|         | 4.5.7 task Construct                            | . 48 |

|         | 4.5.8 critical Construct                        | 49   |

|         | 4.5.9 master Construct                          | 49   |

|         | 4.5.10 master Construct                         | 49   |

|         | 4.5.11 taskwait Construct                       | 49   |

|         | 4.5.12 atomic Construct                         | 49   |

| 4.6 Rui | ntime Library Routines                          | . 50 |

|         | 4.6.1 void omp_set_num_threads(int num_threads) | . 50 |

|         | 4.6.2 int omp_get_num_threads(void)             | . 50 |

|         | 4.6.3 int omp_get_max_threads(void)             | . 50 |

|         | 4.6.4 int omp_get_thread_num(void)              | . 50 |

|         | 4.6.5 int omp_get_num_procs(void)               | . 50 |

|         | 4.6.6 int omp_in_parallel(void)                 | . 50 |

|         | 4.6.7 int omp_get_team_size(int level)          | . 50 |

|         | 4.6.8 void omp_init_lock(omp_lock_t *lock)      | . 50 |

|         | 4.6.9 void omp_destroy_lock(omp_lock_t *lock)   | . 51 |

|         | 4.6.10 void omp_set_lock(omp_lock_t *lock)      | . 51 |

|         | 4.6.11 void omp_unset_lock(omp_lock_t *lock)    | 51   |

| 4.6.12 int omp_test_lock(omp_lock_t *lock)                         | 51 |

|--------------------------------------------------------------------|----|

| 4.7 Clauses                                                        | 51 |

| 4.7.1 default(shared   none)                                       | 51 |

| 4.7.2 shared(list)                                                 | 51 |

| 4.7.3 private(list)                                                | 52 |

| 4.7.4 firstprivate(list)                                           | 52 |

| 4.7.5 lastprivate(list)                                            | 52 |

| 4.8 Environment Variables                                          | 52 |

| 4.8.1 OMP_SCHEDULE type [, chunk]                                  | 52 |

| 4.8.2 OMP_NUM_THREADS list                                         | 52 |

| 4.8.3 OMP_DYNAMIC dynamic                                          | 52 |

| 4.8.4 OMP_NESTED nested                                            | 52 |

| 4.8.5 OMP_THREAD_LIMIT limit                                       | 53 |

| 4.9 Race Conditions                                                | 53 |

| 4.10 Summary                                                       | 55 |

| 5. RESULTS OF COMPLEXITY REDUCTION<br>USING TASK BASED PARALLELISM | 56 |

| 5.1 Prediction structures                                          | 56 |

| 5.2 Task Based Parallelism using OpenMP                            | 57 |

| 5.3 Experimental Results                                           | 59 |

| 5.3.1 QCIF and CIF sequences                                       | 59 |

| 5.3.2 Preview of test sequences [26] used                          | 61 |

| 5.3.3 Performance metrics                                          | 62 |

| 5.3.4 Encoding specifications                                      | 62 |

| 5.3.5 Results obtained with QCIF sequences                         | 63 |

| 5.3.6 Results obtained with CIF sequences                          | 64 |

| 5.3.7 Graphs of average encoding time for all ix                   |    |

| QCIF sequences65                                                 |

|------------------------------------------------------------------|

| 5.3.8 Graphs of average encoding time for all<br>CIF sequences65 |

| 5.3.9 Rate-Distortion graphs for QCIF sequences                  |

| 5.3.10 Rate-Distortion graphs for CIF sequences70                |

| 5.4 Analysis of task based parallelism used in this thesis74     |

| 5.4.1 Comparison of task based with data level parallelism74     |

| 5.4.2 Limitations of task based parallelism method74             |

| 5.5 Summary75                                                    |

| 6. CONCLUSIONS AND FUTURE WORK76                                 |

| 6.1 Conclusions76                                                |

| 6.2 Future work76                                                |

| REFERENCES                                                       |

| BIOGRAPHICAL INFORMATION                                         |

# LIST OF ILLUSTRATIONS

| Figure                                                                         | Page |

|--------------------------------------------------------------------------------|------|

| 1.1 Steps in international standardization                                     | 3    |

| 1.2 H.264 Profiles                                                             | 7    |

| 2.1 Spatial and temporal correlation in a video                                | 10   |

| 2.2 Block diagram of H.264 encoder                                             | 12   |

| 2.3 Difference between adjacent frames                                         | 14   |

| 2.4 Decoder block diagram of H.264                                             | 15   |

| 2.5 Intra 4x4 prediction modes and prediction directions                       | 16   |

| 2.6 H.264 Intra 16x16 prediction modes<br>(all predicted from pixels H and V). | 17   |

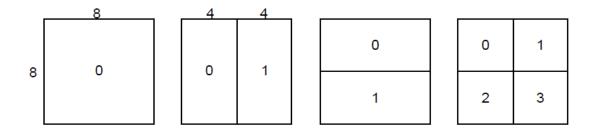

| 2.7 Macroblock partitions: 16x16, 8x16, 16x8, 8x8                              | 18   |

| 2.8 Macroblock sub partitions: 8x8, 4x8, 8x4, 4x4.                             | 18   |

| 2.9 Optimum choice of partitions for residual without motion compensation      | 19   |

| 2.10 4:2:0, 4:2:2 and 4:4:4 sampling patterns (progressive).                   | 20   |

| 2.11 Integer, half-pixel and quarter-pixel motion estimation.                  | 21   |

| 2.12 Zigzag scan orders for 4 × 4 and8 × 8 blocks                              | 23   |

| 2.13 CABAC coding process                                                      | 25   |

| 3.1 Simple comparison of single core, multiprocessor and multi core            | 31   |

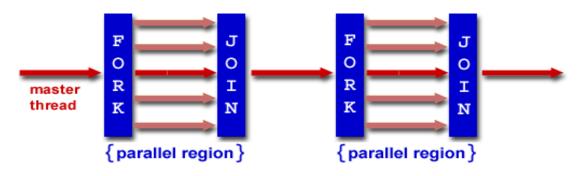

| 4.1 Fork/join model in OpenMP                                                  | 40   |

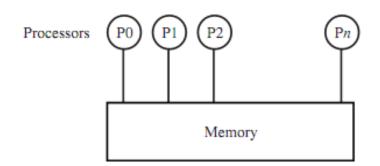

| 4.2 A canonical shared memory architecture                                     | 41   |

| 4.3 Parallel regions                                                           | 41   |

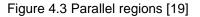

| 4.4 Components of OpenMP                                                       | 42   |

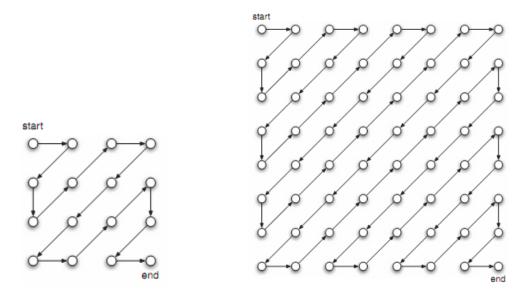

| 5.1 Low delay prediction structure.                                                        | 56 |

|--------------------------------------------------------------------------------------------|----|

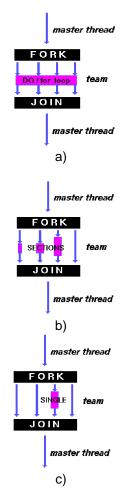

| 5.2 Different types of parallelisms using OpenMP.                                          | 58 |

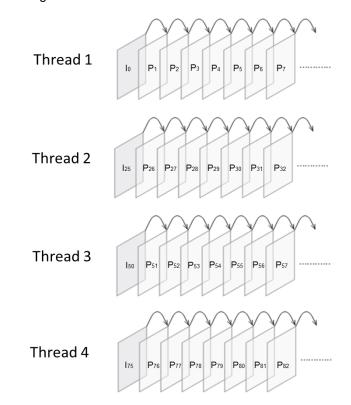

| 5.3 Parallel encoding of 100 frames<br>using 4 threads, with each thread encoding 25 frame | 59 |

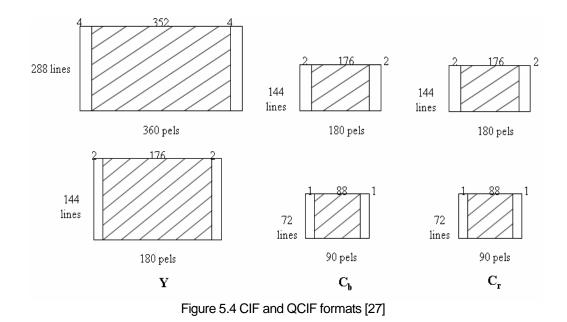

| 5.4 CIF and QCIF formats                                                                   | 60 |

| 5.5 Preview of various test sequences used for testing                                     | 61 |

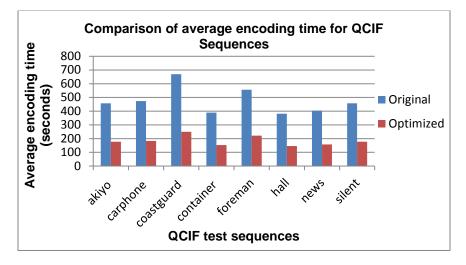

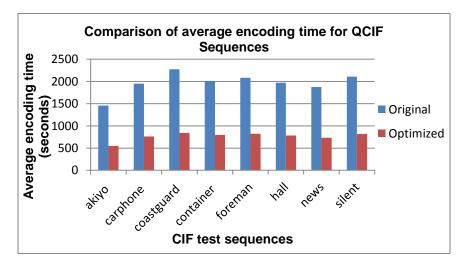

| 5.6 Comparison of average encoding time for all QCIF sequences.                            | 65 |

| 5.7 Comparison of average encoding time for all<br>CIF sequences.                          | 65 |

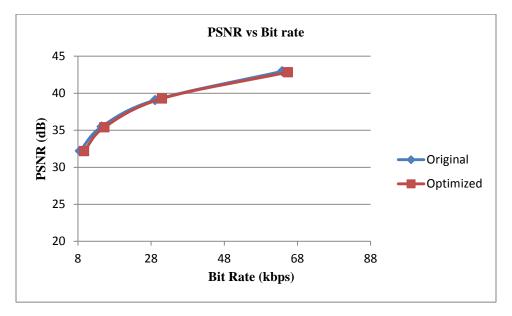

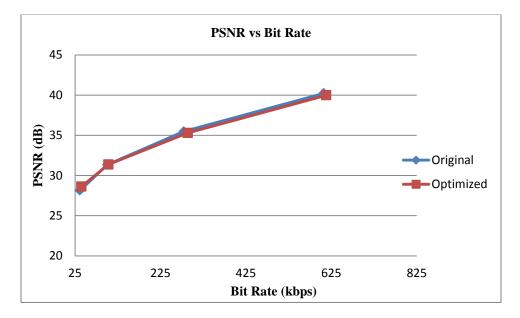

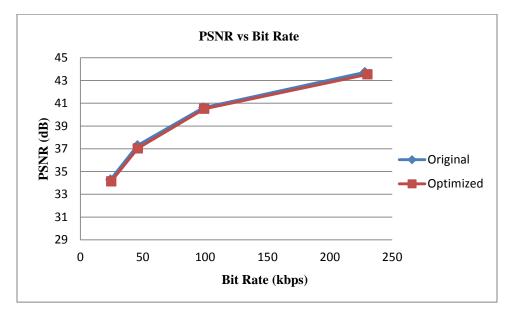

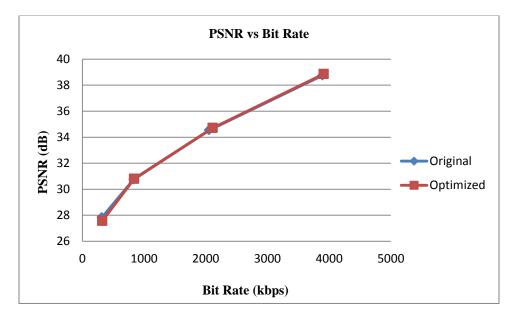

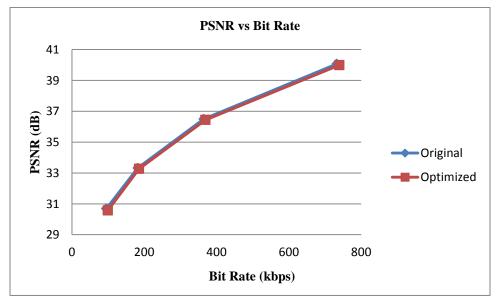

| 5.8 Rate-Distortion graph for Akiyo_qcif.yuv                                               | 66 |

| 5.9 Rate-Distortion graph for Carphone_qcif.yuv                                            | 66 |

| 5.10 Rate-Distortion graph for Coastguard_qcif.yuv                                         | 67 |

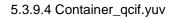

| 5.11 Rate-Distortion graph for Container_qcif.yuv                                          | 67 |

| 5.12 Rate-Distortion graph for Foreman_qcif.yuv.                                           | 68 |

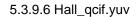

| 5.13 Rate-Distortion graph for Hall_qcif.yuv.                                              | 68 |

| 5.14 Rate-Distortion graph for News_qcif.yuv.                                              | 69 |

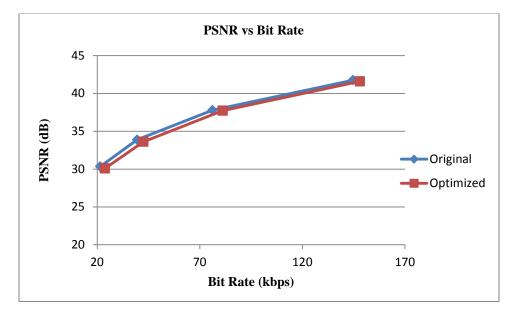

| 5.15 Rate-Distortion graph for Silent_qcif.yuv.                                            | 69 |

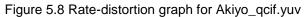

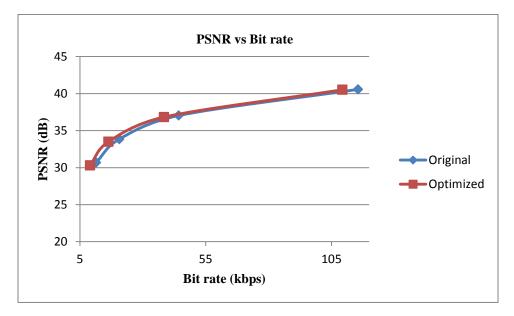

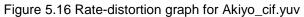

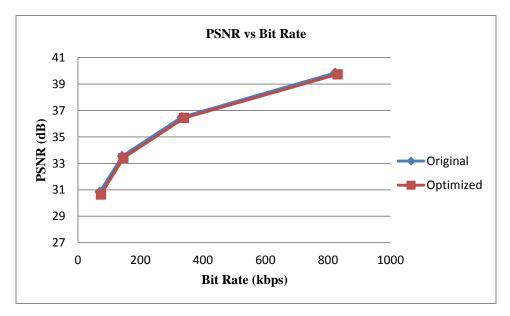

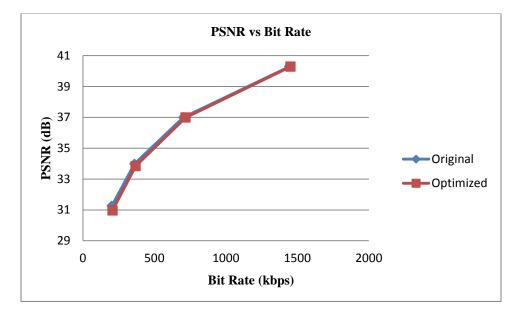

| 5.16 Rate-Distortion graph for Akiyo_cif.yuv                                               | 70 |

| 5.17 Rate-Distortion graph for Carphone_cif.yuv                                            | 70 |

| 5.18 Rate-Distortion graph for Coastguard_cif.yuv                                          | 71 |

| 5.19 Rate-Distortion graph for Container_cif.yuv.                                          | 71 |

| 5.20 Rate-Distortion graph for Foreman_cif.yuv.                                            | 72 |

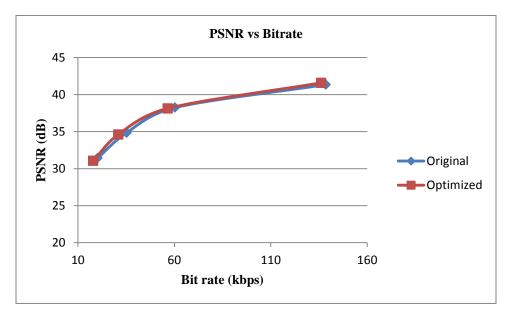

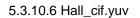

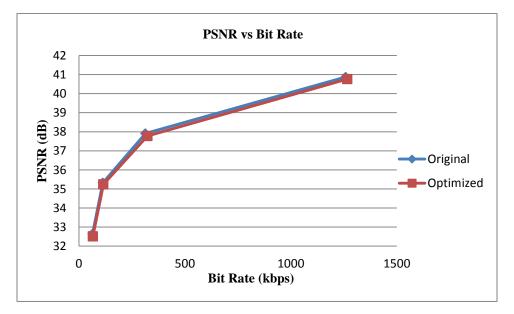

| 5.21 Rate-Distortion graph for Hall_cif.yuv.                                               | 72 |

| 5.22 Rate-Distortion graph for News_cif.yuv                                                | 73 |

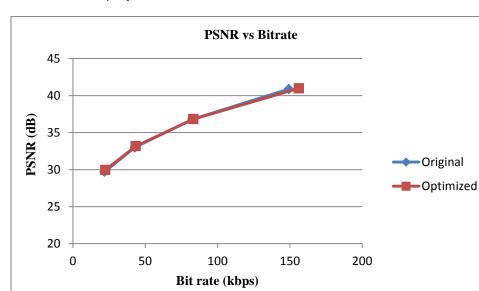

| 5.23 Rate-Distortion graph for Silent_cif.yuv.                                             | 73 |

# LIST OF TABLES

| Table                                                          | Page |

|----------------------------------------------------------------|------|

| 1.1 H.264 Profiles and Applications                            | 8    |

| 5.1 Simulation results for QCIF video sequences at QP = 22, 27 | 63   |

| 5.2 Simulation results for QCIF video sequences at QP = 32, 37 | 63   |

| 5.3 Simulation results for CIF video sequences at QP = 22, 27  | 64   |

| 5.4 Simulation results for CIF video sequences at QP = 32, 37  | 64   |

## LIST OF ACRONYMS

- AVC Advanced Video Coding

- B slice Bi-directionally predictive slice

- CABAC Context-Based Adaptive Binary Arithmetic Coding

- CAVLC Context Adaptive Variable Length Coding

- CD-ROM Compact Disc- Read Only Memory

- CIF Common Intermediate Format

- CMP Chip Multi Processing

- CPU Central Processing Unit

- CUDA Compute Unified Device Architecture

- DCT Discrete Cosine Transform

- DVD Digital Video Disk

- FIR Finite Impulse Response

- FMO Flexible Macroblock Order

- **GPU** Graphical Processing Unit

- GPGPU General Purpose Computation on Graphical Processing Unit

- HD High Definition

- I slice Intra slice

- ISO International Organization for standardization

- ITU-T International Telecommunication Union- Transmission standardization sector

- JVT Joint Video Team

- JM Joint Model

- MPEG Moving Picture Experts Group

- MV Motion Vector

- NAL Network Abstraction Layer

- NTSC National Television System Committee

- P slice Predictive slice

- PSNR Peak Signal to Noise Ratio

- PCM Pulse Code Modulation

- QCIF Quarter Common Intermediate Format

- QP Quantization Parameter

- RAM Random Access Memory

- RDO Rate Distortion Optimization

- RISC Reduced Instruction Set Computing

- **RS** Redundant Slices

- SAD Sum of Absolute Differences

- SATD Sum of Absolute Transformed Differences

- SSIM Structural Similarity Index Metric

- TV Television

- URQ Uniform Reconstruction Quantizers

- VCEG Video Coding Experts Group

- VCL Video Coding Layer

- VCE Video Codec Engine

- VLE Variable Length Encoding

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Introduction to video coding standards

Over past forty years, efficient digital representation of image and video signals has been the subject of considerable research. The rapid growth of digital video coding technology has resulted in increased commercial interest in video communications. This arose a need for international image and video coding standards, which is the basis of large markets for video communication equipment, digital video broadcasting.

Research in signal processing and image compression, VLSI technology, visual communications, digital video coding technology and growing availability of digital transmission links, is dramatically becoming more feasible. Interoperability of implementations from different vendors enables the consumer to access video from a wider range of services and VLSI implementations of coding algorithms conforming to international standards can be manufactured at considerably reduced costs. Modern data compression techniques today offer the possibility to store or transmit the vast amount of data necessary to represent digital images and video in an efficient and robust way. Digital video technology is enabling and generating ever new applications with a broadening range of requirements regarding basic video characteristics such as spatiotemporal resolution, chroma format, and sample accuracy. Various application areas, now a days, range from videoconferencing over mobile TV and broadcasting of standard and high-definition TV content up to very high quality applications such as professional digital video recording or digital cinema/large-screen digital imagery.

Prior video coding standards such as MPEG2/H.262 [1], H.263 [2], and MPEG4 Part 2 [3] are already established in parts of those application domains. But with the proliferation of digital video into new application areas such as mobile TV or high-definition TV broadcasting, the requirements for efficient representation of video have increased up to operation points where previously standardized video coding technology can hardly keep pace. Furthermore, more cost-efficient solutions in terms of bit rate vs. end-to-end reproduction quality are increasingly sought in traditional application areas of digital video as well. If your work contains more than four chapters, add additional template chapters to your template now before continuing. To add additional chapters to those that come with your template you will need to use the text selection and copy operations.

A diversity of products has been developed targeted for a wide range of emerging applications, such as video on demand, digital TV/HDTV broadcasting, and multimedia image/video database services.

#### 1.2 The role and standardization procedure of video coding standards [11], [24]

Over last two decades, various video coding techniques have been proposed. Although there have been a wide range of innovations in the domain of video encoding, commercial video coding applications tend to use a limited number of standardized techniques for video compression. In fact, standardized video coding formats always have upper hand, as far as potential benefits are concerned, compared with non-standard, proprietary formats.

Standards attempt to simplify the inter-operability between encoders and decoders from different manufacturers. In addition, standards make it possible to build platforms that incorporate video, in which many different applications such as video codecs, audio codecs, transport protocols, security and rights management, interact in well-defined and consistent ways.

Almost every video coding technique used commercially is patented. This fact always poses a risk in which some other video codec implementation may infringe patent(s). The

techniques and algorithms required to implement a standard are well-defined and the cost of licensing patents that cover these techniques, i.e. licensing the right to use the technology exemplified in the patents, can be clearly defined.

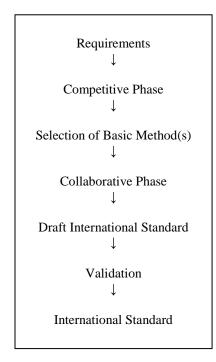

The main steps towards the finalization of a standard can roughly be described as shown in Figure 1.1, although there are slight differences in standardization procedures among the different standardization bodies.

Figure 1.1 Steps in international standardization

Starting with the requirements phase, the requirements for a particular application or for a field of applications are identified. Different algorithms are developed next by various laboratories and then compared. A single basic technique, as a result of this comparison, is identified which is then sophisticated in a joint effort during the next phase, called collaborative phase. At the end of this phase a draft standard is issued, which has to be validated by compliance testing based on computer simulations or hardware testing. Once successful validation and eventual refinements are done the final standard is issued.

#### 1.3 Importance of H.264 Advanced Video Coding [11]

The H.264 video coding standard was jointly published by the International Telecommunication Union (ITU) and the International Standards Organization (ISO). The standard is known by several other names like 'MPEG-4 Part 10' and 'Advanced Video Coding'. Over 550 pages long and filled with highly technical definitions and descriptions, the standard's document was developed by a team consisting of hundreds of video compression experts from the Joint Video Team (JVT). JVT is a collaboration of the Moving Picture Experts Group (MPEG) and the Video Coding Experts Group (VCEG).

H.264/AVC standard has enormous significance in the broadcast, internet, consumer electronics, mobile and security industries, amongst others. It describes and defines a method of coding video that can give better performance than any of the preceding standards.

The H.264 video codec attempts to compress the video so that, the compressed video clip takes up less bandwidth as far as transmission is concerned and takes up less memory space compared to older codecs, as far as storage on secondary memory is concerned.

A combination of market expansion, technology advances and increased user expectation is driving demand for better, higher quality digital video. Various examples in daily life include High Definition (HD) content delivery, uploading and downloading videos using websites such as YouTube, recording and sharing videos using mobile handsets, internet video calls and so on. In each of these examples, the most important expectation from a codec is better video compression for delivering more, higher-quality video in a frugal way. It is the H.264 standard that makes it possible to transmit HD content over a broadcast channel having limitedcapacity, to record hours of video on a Flash memory card and to deliver massive numbers of video streams over an already busy internet.

#### 1.4 H.264 CODEC standard [1, 2]

The aim of H.264 is high-quality coding of video contents at low bit-rates, having significant improvements in coding efficiency and error robustness in comparison with previous

video coding standards [1]. There are a number of new features and capabilities that have been added in H.264 to improve its coding performance. As a result, the H.264 encoding process is more computationally intensive than existing standards.

Some important applications of H.264 codec include:

- 1. Broadcast over cable, satellite, cable modem, DSL, terrestrial, etc.

- 2. Interactive or serial storage on optical and magnetic devices, DVD, etc.

- Conversational services over ISDN, Ethernet, LAN, DSL, wireless and mobile networks, modems, etc. or mixtures of these.

- Video-on-demand or multimedia streaming services over ISDN, cable modem, DSL, LAN, wireless networks, etc.

- Multimedia messaging services (MMS) over ISDN, DSL, Ethernet, LAN, wireless and mobile networks, etc.

## 1.5 Key features of H.264 video codec

Following are some highlighted features of H.264 video codec:

- 1. Variable block-size motion compensation with small block sizes

- 2. Quarter-sample-accurate motion compensation

- 3. Multiple reference picture motion compensation

- 4. Weighted prediction

- 5. Improved "skipped" and "direct" motion inference

- 6. Directional spatial prediction for intra coding

- 7. In-the-loop deblocking filtering

- 8. Context-adaptive entropy coding

- 9. Flexible slice size

- 10. Flexible macroblock ordering (FMO)

#### 1.6 H.264 Profiles [2]

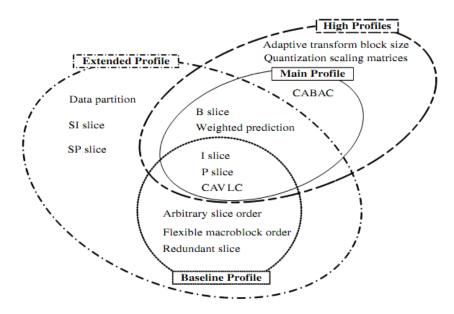

The JVT involved in defining H.264 focused on creating a simple and clean solution, limiting options and features to a minimum. An important aspect of the standard, as with other video standards, is providing the capabilities in profiles (sets of algorithmic features) and levels (performance classes) that optimally support popular productions and common formats. Following sets of capabilities, known as profiles, as shown in Figure1.2, are defined in H.264/AVC standard. These profiles target specific classes of applications.

#### 1.6.1 Baseline Profile

- Flexible macroblock order: macroblocks may not necessarily be in the raster scan order. The map assigns macroblocks to a slice group.

- Arbitrary slice order: the macroblock address of the first macroblock of a slice of a picture may be smaller than the macroblock address of the first macroblock of some other preceding slice of the same coded picture.

- Redundant slice: this slice belongs to the redundant coded data obtained by same or different coding rate, in comparison with previous coded data of same slice.

## 1.6.2 Main Profile

- B slice (Bi-directionally predictive-coded slice): the coded slice by using inter-prediction from previously decoded reference pictures, using at most two motion vectors and reference indices to predict the sample values of each block.

- Weighted prediction: scaling operation by applying a weighting factor to the samples of motion-compensated prediction data in P or B slice.

- 3. CABAC (Context-based Adaptive Binary Arithmetic Coding) for entropy coding.

#### 1.6.3 Extended Profile

- Includes all parts of Baseline Profile: flexible macroblock order, arbitrary slice order and redundant slice

- 2. SP slice: the specially coded slice for efficient switching between video streams, similar to

coding of a P slice.

- 3. SI slice: the switched slice, similar to coding of an I slice.

- 4. Data partition: the coded data is placed in separate data partitions, each partition can be placed in different layer unit.

- 5. B slice

- 6. Weighted prediction

- 1.6.4 High Profiles

- 1. Includes all parts of Main Profile: B slice, weighted prediction and CABAC

- 2. Adaptive transform block size: 4x4 or 8x8 integer transform for luma samples

- 3. Quantization scaling matrices: different scaling according to specific frequency associated with the transform coefficients in the quantization process to optimize the subjective quality

This thesis implements the video algorithm using baseline profile.

Figure 1.2 H.264 Profiles [1]

# 1.6.5 Applications of H.264 profiles [1]

| Application                   | Requirements                                                                                               | H.264<br>Profiles         |

|-------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------|

| Broadcast television          | Coding efficiency, reliability (over a controlled distribution channel), interlace, low-complexity decoder | Main                      |

| Streaming video               | Coding efficiency, reliability (over a uncontrolled packet-<br>based network channel), scalability         | Extended                  |

| Video storage and<br>Playback | Coding efficiency, interlace, low-complexity encoder and decoder                                           | Main                      |

| Videoconferencing             | Coding efficiency, reliability, low latency, low-complexity encoder and decoder                            | Baseline                  |

| Mobile video                  | Coding efficiency, reliability, low latency, low-complexity encoder and decoder, low power consumption     | Baseline                  |

| Studio distribution           | Lossless or near-lossless, interlace, efficient transcoding                                                | Main and<br>High Profiles |

# Table 1.1 H.264 Profiles and Applications

# 1.7 Summary

This chapter explains video coding standardization, especially, the H.264/AVC standard along with key features in it.

Next chapter illustrates working of the H.264 codec, which gives a gist of additional complexity involved in the standard. The chapter finally concludes with need for time complexity reduction in H.264.

#### CHAPTER 2

## NEED FOR TIME COMPLEXITY REDUCTION IN H.264

#### 2.1 Key concepts involved in a video codec [11]

Basically, video coding is the process of compressing and decompressing a digital video signal. Digital video is nothing but, a representation of a natural or real-world visual scene, sampled spatially and temporally. A frame is produced by sampling a scene temporally at a point in time. The frame represents the complete visual scene at that point in time, or a field, which typically consists of odd- or even-numbered lines of spatial samples. Sampling is repeated at certain intervals such as 1/25 or 1/30 second to finally produce a moving video signal. Three components or sets of samples are typically required to represent a scene in color. In order to determine the performance of a visual communication system, which is a difficult and inexact process, the accuracy of a reproduction of a visual scene has to be measured.

#### 2.1.1 CODEC and types of compression [11]

Any compression of audio, video and data involves a complementary pair of systems, an encoder, which acts as a compressor and a decoder which acts as a decompressor. The role of compression is to compact the data into a smaller number of bits. The encoder converts the source data into a compressed form occupying a reduced number of bits, prior to transmission or storage. On the other hand, the decoder converts the compressed form back into a representation of the original video data. The encoder/decoder pair is nothing but a CODEC (enCOder/ DECoder).

There are, typically two kinds of compression types defined, lossless and lossy compression. In case of lossless compression, the reconstructed data at the output of the decoder is a perfect copy of the original data. But, lossless compression of image and video information gives only a moderate amount of compression.

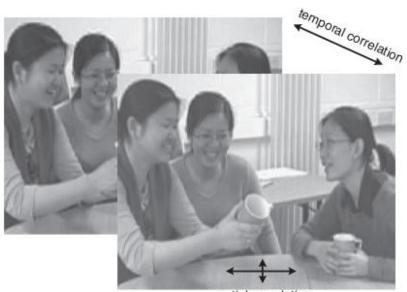

Lossy compression, on the other hand, is necessary to achieve higher compression. Lossy compression helps achieve much higher compression ratios, but, at the expense of a loss of visual quality. Most of the video coding methods exploit both temporal and spatial redundancies to achieve compression as shown in Figure 2.1.

In the spatial domain, there exists high correlation between pixels (samples) that are close to each other, i.e. the values of neighboring samples are often very similar.

spatial correlation

Figure 2.1 Spatial and temporal correlation in a video [11]

There is a high correlation or similarity, as shown in Figure 2.1, between temporally adjacent frames, i.e. successive frames in time order, especially, if the temporal sampling rate or frame rate is high.

## 2.1.2 Working of H.264 video codec [1], [11]

The codec, consisting of an encoder and a decoder is depicted in Figures 2.2 and 2.4. The encoder may select between intra and inter coding for block-shaped regions of each picture to exploit either spatial or temporal redundancy. Intra-coding uses various spatial prediction modes to reduce spatial redundancy in the source signal for a single picture. Inter - coding, which could be predictive or bi-predictive is more efficient using inter-prediction of each block of sample values from some previously decoded pictures. In order to reduce temporal redundancy among different pictures, inter-coding uses motion vectors for block-based inter-prediction. Prediction is obtained from deblocking filtered signal of previous reconstructed pictures.

The deblocking filter is to reduce the blocking artifacts at the block boundaries. Motion vectors and intra-prediction modes may be specified for a variety of block sizes in the picture. The prediction residual is then further compressed using a transform to remove spatial correlation in the block before it is quantized.

Finally, the motion vectors or intra-prediction modes are combined with the quantized transform coefficient information and dencoded using entropy code such as context-adaptive variable length codes (CAVLC) or context adaptive binary arithmetic coding (CABAC).

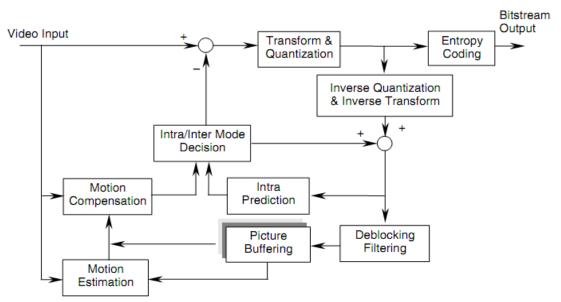

2.1.3 Encoder [2], [7], [11]

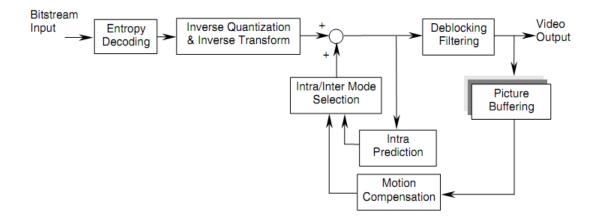

The H.264 video encoder block diagram is shown in Figure 2.2. The working of the encoder can be roughly divided into two parts: forward and reverse paths.

Figure 2.2 Block diagram of H.264 encoder [1]

## 2.1.3.1 Encoder (Forward Path)

An H.264 video encoder carries out prediction, transform and encoding process to produce a compressed H.264 bit stream. A frame to be encoded is processed by an H.264 compatible video encoder. In addition to coding and sending the frame as a part of the coded bit stream, the encoder reconstructs the frame i.e. imitates the decoder and the reconstructed frame is stored in a coded picture buffer, and used during the encoding of further frames.

An input frame is presented for encoding as shown in Figure 2.2. The frame is processed in units of a macroblock corresponding to 16x16 pixels in the original image. Each macroblock is encoded in intra or inter mode. Based on a reconstructed frame, a predicted macroblock is formed. In intra mode, predicted macroblock is formed from samples in the current frame that have been previously encoded, decoded and reconstructed. The unfiltered samples are used to form P. In inter mode, P is formed by inter or motion-compensated prediction from one or more reference frame(s). The prediction for each macroblock may be formed from one or more past or future frames (in

time order) that have already been encoded and reconstructed.

In the encoder, the prediction macroblock P is subtracted from the current macroblock. This produces a residual macroblock, also known as difference macroblock. Figure 2.3 shows how a difference frame looks like. Using a block transform, the difference macroblock is transformed and quantized to give a set of quantized transform coefficients. These coefficients are rearranged and encoded using entropy encoder. The entropy encoded coefficients, and the other information such as the macroblock prediction mode, quantizer step size, motion vector information etc. required to decode the macroblock form the compressed bitstream. This is passed to network abstraction layer (NAL) for transmission or storage.

Figure 2.3 Difference between adjacent frames. a) Frame 1, b) Frame 2, c) Difference frame

#### 2.1.3.2 Encoder (Reconstruction path)

In the reconstruction path, quantized macroblock coefficients are dequantized and are re-scaled and inverse transformed to produce a difference macroblock. This is not identical to the original difference macroblock, since quantization is a lossy process. The predicted macroblock P is added to the difference macroblock to create a reconstructed macroblock a distorted version of the original macroblock. To reduce the effects of blocking distortion, a de-blocking filter is applied and from a series of macroblocks, reconstructed reference frame is created.

## 2.1.4 Decoder [1], [2], [11]

The decoder block diagram of H.264 is shown in Figure 2.4. The decoder carries out the complementary process of decoding, inverse transform and reconstruction to produce a decoded video sequence.

The decoder receives a compressed bitstream from the NAL. The data elements are entropy decoded and rearranged to produce a set of quantized coefficients. These are rescaled and inverse transformed to give a difference macroblock. Using the other information such as the macroblock prediction mode, quantizer step size, motion vector information etc. decoded from the bit stream, the decoder creates a prediction macroblock P, identical to the original prediction P formed in the encoder. P is added to the difference macroblock and this result is given to the deblocking filter to create the decoded macroblock.

Figure 2.4 Decoder block diagram of H.264 [1].

The reconstruction path in the encoder ensures that both encoder and decoder use identical reference frames to create the prediction P. If this is not the case, then the predictions P in encoder and decoder will not be identical, leading to an increasing error or drift between the encoder and decoder.

# 2.1.5 Intra Prediction [2], [10], [11]

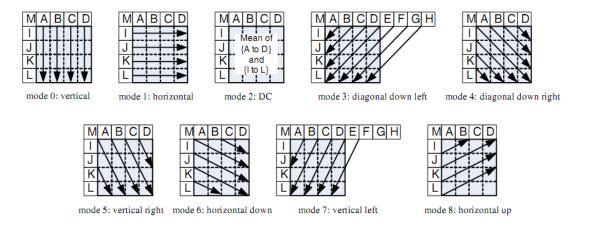

Adaptive intra directional prediction modes for (4x4) and (16x16) blocks are shown in Figures. 2.5 and 2.6.

In order to exploit the spatial redundancy between adjacent macroblocks within a frame, technique used in H.264 encoder is intra-prediction. From adjacent edges of neighboring macroblocks that are decoded before the current macroblock, it predicts the pixel values as linear interpolation of pixels. Directional in nature, these interpolations are with multiple modes. Each mode implies a spatial direction of prediction. There are 9 prediction modes defined for a 4x4 block and 4 prediction modes defined for a 16x16 block.

2.1.5.1 4x4 luma prediction modes [4], [14]

Figure 2.5 shows a luminance macroblock and a 4x4 luma block that is required to be predicted and various modes of prediction are shown. The samples above and to the left have previously been encoded and reconstructed and are available both in the encoder and decoder

to form a prediction reference. The prediction block is calculated based on the samples labeled A-M in Figure 2.5. However, in some cases, not all of the samples A-M are available within the current slice: in order to preserve independent decoding of slices, only samples within the current slice are available for prediction. DC prediction (mode 0) is modified depending on which samples out of A-M are available; the other modes (1-8) may only be used if all of the required prediction samples are available (except that, if E, F, G and H are not available, their value is copied from sample D).

Direction of prediction in each mode is indicated by the arrows in Figure 2.5. For modes 3-8, the predicted samples are formed from a weighted average of the prediction samples A-M. The encoder may select the prediction mode for each block that minimizes the residual between P and the block to be encoded.

Figure 2.5 Intra 4x4 prediction modes and prediction directions [11]

The 9 prediction modes (0-8) are calculated for the 4x4 block shown in Figure 2.5. The prediction block is then created by each of the predictions. The Sum of Absolute Errors (SAE) for each prediction is calculated for each mode, which indicates the magnitude of the prediction error. The mode that finally gives the smallest SAE is finally selected for encoding.

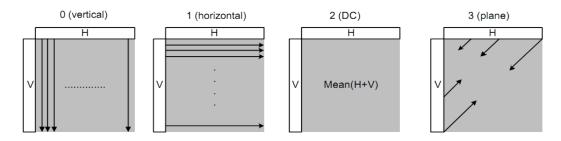

## 2.1.5.2 16x16 luma prediction modes [14]

The entire 16x16 luma component of a macroblock can be predicted, as an alternative to the nine 4x4 luma modes. For 16x16 macroblock, four modes are available, shown in Figure 2.6:

- 1. Mode 0 (vertical): extrapolation from upper samples (H).

- 2. Mode 1 (horizontal): extrapolation from left samples (V).

- 3. Mode 2 (DC): mean of upper and left-hand samples (H+V).

- Mode 4 (Plane): a linear "plane" function is fitted to the upper and left-hand samples H and V. This works well in areas of smoothly-varying luminance.

Figure 2.6 H.264 Intra 16x16 prediction modes [11] (all predicted from pixels H and V)

# 2.1.6 Inter Prediction [1], [11], [14]

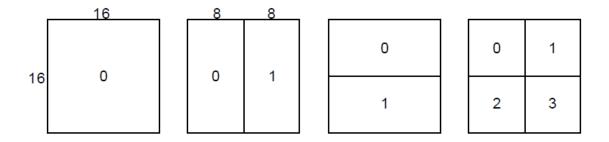

To exploit temporal redundancy between the frames, inter prediction is performed in H.264 encoder. In this process, a block of luma and chroma samples is predicted from a picture that has previously been coded and transmitted, a reference picture. Selecting a prediction region, generating a prediction block and subtracting this from the original block of samples to form a residual are various steps involved. The residual is then transformed, coded and transmitted. The block size can range from 16x16 to 4x4 luma and corresponding chroma samples.

The luminance component of each macroblock (16x16 samples) maybe split up in 4 ways, 16x16, 16x8, 8x16 or 8x8 as shown in Figure 2.7. Each of the sub-divided regions is a macroblock partition. If the 8x8 mode is chosen, each of the four 8x8 macroblock partitions

within the macroblock may be split in a further 4 ways, 8x8, 8x4, 4x8 or 4x4 (known as macroblock sub-partitions) as shown in Figure 2.8. These partitions and sub-partitions give rise to a large number of possible combinations within each macroblock. In general, a large partition size is appropriate for homogeneous areas of the frame and a small partition size may be beneficial for detailed areas.

Figure 2.7 Macroblock partitions: 16x16, 8x16, 16x8, 8x8 [14]

Figure 2.8 Macroblock sub partitions: 8x8, 4x8, 8x4, 4x4 [14]

Each macroblock partition or sub-partition requires a separate motion vector. Each motion vector must be coded and transmitted; in addition, the choice of partition(s) must be encoded in the compressed bitstream. If a large partition size (e.g. 16x16, 16x8, 8x16) is chosen, less number of bits are required to indicate the choice of motion vector(s) and the type of partition. The motion compensated residual may contain a significant amount of energy in frame areas with high detail. Choosing a small partition size (e.g. 8x4, 4x4, etc.) may give a lower-energy residual after motion compensation but requires a larger number of bits to signal

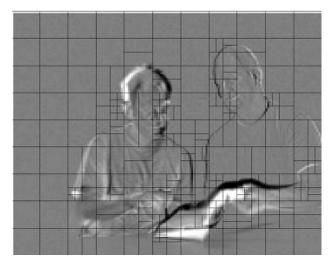

the motion vectors and choice of partition(s). The choice of partition size therefore has a significant impact on compression performance. In general, a large partition size is appropriate for homogeneous areas of the frame and a small partition size may be beneficial for detailed areas. Figure 2.9 shows a residual frame (without motion compensation). The H.264 encoder chooses the best partition size for each part of the frame in such a way that the partition size minimizes the coded residual and motion vectors. If there is little difference between the frames (residual appears grey), a 16x16 partition is chosen; whereas in areas of detailed motion (residual appears black or white), smaller partitions are more efficient.

Figure 2.9 Optimum choice of partitions for residual without motion compensation [11]

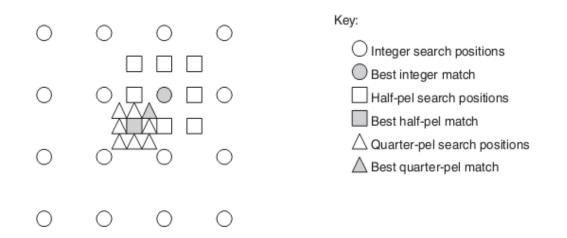

AVC also defines sub-pel motion compensation, which can provide significantly better compression performance than integer-pel compensation, at the expense of increased complexity. The codec defines quarter- pel accuracy which, definitely, performs better than halfpel accuracy.

Three sampling patterns [11] for Y, Cr and Cb supported by H.264/AVC are shown in Figure 2.10. 4:4:4 sampling means that the three components (Y:Cr:Cb) have the same resolution and hence a sample of each component exists at every pixel position. 4:2:2 sampling, sometimes referred to as YUY2, consists of chrominance components having the same vertical

resolution as the luma but half the horizontal resolution. In the popular 4:2:0 sampling format ('YV12'), Cr and Cb each have half the horizontal and vertical resolution of Y. 4:2:0 sampling is widely used for consumer applications such as video conferencing, digital television and digital versatile disk (DVD) storage.

Figure 2.10 4:2:0, 4:2:2 and 4:4:4 sampling patterns (progressive) [11]

One of the most important factors behind the increased coding efficiency at high bitrates and high video resolutions is sub-pel accuracy. In the luma component, the sub-pel samples at half-pel positions are generated first and are interpolated from neighboring integer-pel samples using a 6-tap FIR filter with weights (1, -5, 20, 20, -5, 1) / 32. Once all the half-pel samples are available, each quarter-pel sample is produced using bilinear interpolation between neighboring half- or integer-pel samples, as shown in Figure 2.11. For 4:2:0 video source

sampling, 1/8 pel samples are required in the chroma components (corresponding to 1/4 pel samples in the luma). These samples are interpolated (linear interpolation) between integer-pel chroma samples. Sub-pel motion vectors are encoded differentially with respect to predicted values formed from nearby encoded motion vectors.

Figure 2.11 Integer, half-pixel and quarter-pixel motion estimation [11]

Reference pictures that are used for inter-prediction of a sample block are stored in the picture buffer. With respect to the current picture, the pictures before and after the current picture, in the display order are stored into the picture buffer.

#### 2.1.7 Rate Distortion Optimization [13]

The H.264/AVC intra-prediction is conducted for all types of blocks such as 4x4 luma blocks, 16x16 luma blocks, and 8x8 chroma blocks. The residual between the current block and its prediction is then transformed, quantized, and entropy coded.

To obtain the best mode among these modes, the H.264/AVC encoder performs the rate-distortion optimization (RDO) technique for each macro block.

- 1. Set macro block parameters : QP (quantization parameter) and Lagrangian multiplier  $\lambda$

- 2. Calculate :  $\lambda MODE = 0.85 \cdot 2(QP-12)/3$

# Then calculate cost, which determines the best mode Cost = D + λMODE. R D – Distortion R - Bit rate with given QP Distortion (D) is obtained by SSD (sum of squared differences) between the original macro block and its reconstructed block.

Bit rate(R) includes the number of bits for the mode information and transforms coefficients for macro block. Considering the RDO procedure for intra mode selection in H.264/AVC, the number of mode combinations in one macro block is N8x (16xN4 + N16)

N8 – number of modes of an 8x8 chroma block, N4 – number of modes of an 4x4 luma block N16 – number of modes of a 16x16 luma block

2.1.8 Transform, Scaling, and Quantization [3]

H.264/MPEG4-AVC also uses transform coding of the prediction residual. H.264/MPEG4-AVC specifies a set of integer transforms of different block sizes. An additional  $M \times N$  transform stage is further applied to all resulting DC coefficients in the case of the luma component of a macroblock that is coded using the 16  $\times$  16 intra-coding type (with N = M =4) as well as in the case of both chroma components. For these additional transform stages, separable combinations of the four-tap Hadamard transform and two-tap Haar/Hadamard

transform are applied.

Besides the important property of low computational complexity, the use of these small block-size transforms in H.264/MPEG4-AVC has the advantage of significantly reducing ringing artifacts. For high-fidelity video, however, the preservation of smoothness and texture generally benefits from a representation with longer basis functions. A better trade-off between these conflicting objectives can be achieved by making use of the 8×8 integer.

For the quantization of transform coefficients, H.264/MPEG4-AVC uses uniform reconstruction quantizers (URQs). One of 52 quantizer step size scaling factors is selected for each macroblock by a quantization parameter (QP). The scaling operations are arranged so that there is a doubling in quantization step size for each increment of six in the value of QP.

The quantized transform coefficients of a block are usually scanned in a zig-zag fashion as shown in Figure 2.12 and further processed using the entropy coding.

Figure 2.12 Zigzag scan orders for 4 × 4 and8 × 8 blocks [11]

#### 2.1.9 In loop deblocking filter [1], [3], [11]

Since AVC uses coarse quantization, at low bit rates, the block-based coding typically shows clearly visually noticeable artifacts or discontinuities along the block boundaries. If no

further provision is made to deal with this, these artificial discontinuities may also diffuse into the interior of blocks by means of the motion-compensated prediction process. The removal of such blocking artifacts can provide a substantial improvement in perceptual quality.

For that purpose, H.264/MPEG4-AVC defines a deblocking filter that operates within the predictive coding loop, and thus constitutes a required component of the decoding process. The filtering process exhibits a high degree of content adaptivity on different levels, from the slice level along the edge level down to the level of individual samples. As a result, the blockiness is reduced without much affecting the sharpness of the content. Consequently, the subjective quality is significantly improved. At the same time, the filter reduces bit rate by typically 5–10 percent while producing the same objective quality as the non-filtered video.

2.1.10 Entropy Coding [3]

In H.264/MPEG4-AVC, many syntax elements are coded using the same highlystructured infinite-extent variable-length code (VLC), called a zero-order exponential-Golomb code. A few syntax elements are also coded using simple fixed-length code representations. For the remaining syntax elements, two types of entropy coding are supported.

When using the first entropy-coding configuration, which is intended for lowercomplexity (esp. software-based) implementations, the exponential-Golomb code is used for nearly all syntax elements except those of quantized transform coefficients, for which a more sophisticated method called context-adaptive variable length coding (CAVLC) is employed. When using CAVLC, the encoder switches between different VLC tables for various syntax elements, depending on the values of the previously transmitted syntax elements in the same slice. Since the VLC tables are designed to match the conditional probabilities of the context, the entropy coding performance is improved from that of schemes that do not use contextbased adaptivity.

The entropy coding performance is further improved if the second configuration is used, which is referred to as context-based adaptive binary arithmetic coding (CABAC).

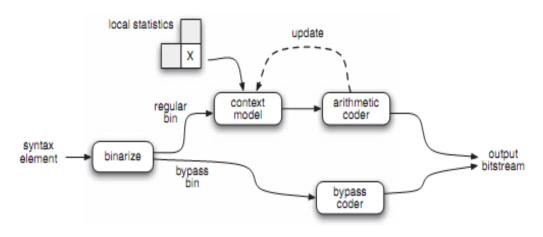

CABAC design is based on three components: binarization, context modeling, and binary arithmetic coding as shown in Figure 2.13. Binarization enables efficient binary arithmetic coding by mapping nonbinary syntax elements to sequences of bits referred to as bin strings. The bins of a bin string can each be processed in either an arithmetic coding mode or a bypass mode. The latter is a simplified coding mode that is chosen for selected bins such as sign information or lesser significance bins in order to speed up the overall decoding (and encoding) processes. Compared to CAVLC, CABAC can typically provide reductions in bit rate of 10–20 percent for the same objective video quality when coding DTV/HDTV signals.

Figure 2.13 CABAC coding process [11]

# 2.2 Need for time complexity reduction [2], [8], [11]

The new standard is aimed at high-quality coding of video contents at very low bit-rates. H.264 uses the same hybrid block-based motion compensation and transform coding model. Furthermore, a number of new features and capabilities has been introduced in H.264 to efficiently improve the coding performance.

Finally, with all the enhancements available in H.264/AVC compared to previous standards, the codec outperforms in terms of compression efficiency and video quality. But, again, the price to pay for all of these advantages is the complexity involved in the standard, thereby making it challenging to the engineer or designer who has to develop, program or

interface with an H.264 codec. As the standard becomes more complex, the encoding and decoding processes require much more computation power than most existing standards.

H.264 has various choices and parameters than any previous standard codec. Of course, getting the perfect controls and parameters for a particular application is not an easy task. If done correctly, H.264 delivers high compression performance; on the contrary, the result is poor-quality pictures and/or poor bandwidth efficiency.

Computationally expensive, an H.264 coder can lead to slow coding and decoding times or rapid battery drain on handheld devices. Thus, in order to make the codec usable on a handheld device and to be able to encode a video real time, there has to be some ways to reduce the time complexity involved in the video encoding.

Some of the different ways adopted to tackle this problem are: Changing the motion estimation algorithm and making intra/inter mode selection more time efficient, using Single Instruction Multiple Data (SIMD) execution model, optimizing the codec to make it run on DSP or dedicated hardware, parallel programming etc.

The complexity of emerging multimedia applications imposes new demands on processor performance. Most modern microprocessors, now a days have multimedia instructions and multithreading capabilities to facilitate multimedia applications. For example, the single-instruction-multiple-data (SIMD) execution model was introduced in Intel architectures. Intel also introduced hyper-threading technology [8], which enables a processor to execute multiple threads simultaneously. These advances in personal computers in addition to higher clock frequency have provided the necessary computational power for many multimedia applications.

To implement multimedia applications on personal computers requires some hardwarespecific algorithm modifications. This thesis uses the parallel programming approach to reduce the overall encoding time by up to 60% by making use of four threads and making them work in parallel.

# 2.3 Summary

This chapter describes the working of H.264 codec. It then illustrates various blocks of the encoder such as transform and quantization, inter/intra prediction, motion estimation/motion compensation etc. The explanation gives overview of complexity involved in the codec. Finally it depicts the need for complexity reduction in the codec.

This thesis is aimed at complexity reduction in the H.264 codec using parallel programming technique. Next chapter mainly describes various basic concepts involved in parallel programming.

#### CHAPTER 3

# PARALLEL PROGRAMMING BASICS

#### 3.1 Introduction to parallel programming

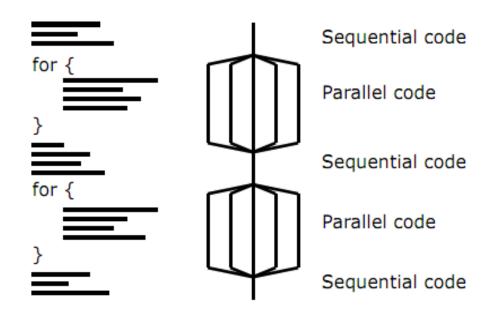

Parallel programming and design of efficient parallel programs have been well established in high performance, scientific computing for many years. In parallel computing, calculations are carried out simultaneously, operating on the principle that large problems can often be divided into smaller ones, which are solved in parallel. Parallel computer programs are difficult to write as compared to sequential ones because, various potential software bugs are to be avoided e.g. data dependencies, race conditions etc. Communication and synchronization between the different subtasks are typically most challenging parts, in order to achieve good parallel program performance. There are several different forms of parallel computing: bit-level, instruction level, data, thread level, task parallelism.

#### 3.2 Multicore [6], [8]

A multicore is an architecture design that places multiple processors on a single die (computer chip). Each processor is called a core. As chip capacity increased, placing multiple processors on a single chip became practical. These designs are known as Chip Multiprocessors (CMPs) because they allow for single chip multiprocessing. Multicore is simply a popular name for CMP or single chip multiprocessors. The concept of single chip multiprocessing is not new, and chip manufacturers have been exploring the idea of multiple cores on a uniprocessor since the early 1990s. These days CMP [6] has become the preferred method of improving overall system performance. This is a departure from the approach of increasing the clock frequency or processor speed to achieve gains in overall system performance. Increasing the clock frequency has started to hit its limits in terms of cost - effectiveness. Higher frequency requires more power, making it harder and more expensive to cool the system. This also affects sizing and packaging considerations. So, instead of trying to make the processor faster to gain performance, the response is now just to add more processors. The simple realization that this approach is better has prompted the multicore revolution. Multicore architectures are now center stage in terms of improving overall system performance. The approaches to designing and implementing application software that will take advantage of the multicore processors are radically different from techniques used in single core development. Thus, the focus of software design and development should change from sequential programming techniques to parallel and multithreaded programming techniques.

In single core configurations there is one general purpose processor, although it is important to note that many of today's single core configurations contain special graphic processing units, multimedia processing units, and sometimes special math coprocessors. But even with single core or single processor computers multithreading, parallel programming, pipelining, and multiprogramming are all possible.

#### 3.3 Parallel Computing in Microprocessors [7], [8]

Parallel programming is the art and science of implementing an algorithm, a computer program, or a computer application, using sets of instructions or tasks designed to be executed concurrently.

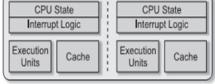

With the advancements in software, applications have become increasingly capable of running multiple tasks simultaneously. There are several approaches, both in software and hardware, in order to support thread-level parallelism. One approach to address the increasingly concurrent nature of modern software involves using a preemptive, or time-sliced, multitasking

operating system. Time-slice multi-threading allows developers to hide latencies associated with I/O by interleaving the execution of multiple threads. This model does not allow for parallel execution. Only one instruction stream can run on a processor at a single point in time. Another approach is to increase the number of physical processors in the computer. Multiprocessor systems allow true parallel execution; multiple threads or processes run simultaneously on multiple processors, but this comes with drawback of increased overall system cost.

A thread, which is a basic unit of CPU utilization, contains a program counter that points to the current instruction in the stream. It also contains CPU state information for the current thread. It also contains other resources such as a stack.

A logical processor can thus be created by duplicating this architecture space in a physical processor. The execution resources can be shared among the different logical processors. This technique is known as simultaneous multi-threading or hyper threading technology [15], in terms of Intel's implementation. It makes a single processor appear, from software's perspective, as multiple logical processors. Like CMP, a hyperthreaded processor allows two or more threads to execute on a single chip. However, in a hyperthreaded package the multiple processors are logical instead of physical. There is some duplication of hardware but not enough to qualify a separate physical processor. So hyperthreading allows the processor to present itself to the operating system as complete multiple processors when in fact there is a single processor running multiple threads.

The next logical step is the multi-core processor. Multi-core processors use chip multiprocessing (CMP). Processor manufacturers take advantage of improvements in manufacturing technology to implement two or more "execution cores" within a single processor. These cores are nothing but two individual processors on a single die. Execution cores have their own set of execution and architectural resources. These processors may or may not share a large on-chip cache, depending on design. These individual cores, in turn, may be combined

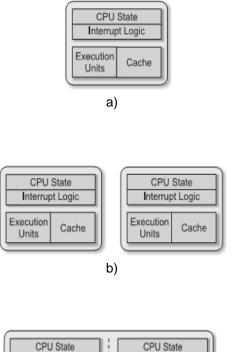

with SMT; effectively increasing the number of logical processors by twice the number of execution cores. The different processor architectures are highlighted in figure 3.1

c)

Figure 3.1 Simple comparison of single core, multiprocessor and multi core a) Single core, b) Multiprocessor c) Multicore [7]

# 3.4 Multi-threading on Single-Core versus Multi-Core Platforms [7]

These days, most modern applications use threads in one fashion or another. Hence, many developers are already familiar with the concept of threading, and have probably worked on applications that have multiple threads. However, there are certain important considerations developers should be aware of when writing applications targeting multi-core processors:

In order to achieve optimal application performance on multi-core architectures one must effectively use threads to partition software workloads.

Thread is used for improvement of user responsiveness on single-core platforms by many applications. Rather than blocking the user interface (UI) on a time consuming database query or disk access, an application will spawn a thread to process the user's request. This allows the scheduler to individually schedule the main control loop task that receives UI events as well as the data processing task that is running the database query. In this model, developers rely on straight-line instruction throughput improvements to improve application performance. This is the significant limitation of multi-threading on single-core processors. Since single-core processors are really only able to interleave instruction streams, but not execute them simultaneously, the overall performance gains of a multi-threaded application on singlecore architectures are limited. On these platforms, threads are generally seen as a useful programming abstraction for hiding latency. This performance restriction is removed on multicore architectures. On multi-core platforms, threads do not have to wait for any one resource. Instead, threads run independently on separate cores. For example, consider two threads that both wanted to execute a shift operation. If a core only had one "shifter unit" they could not run in parallel. On two cores, there would be two "shifter units," and each thread could run without contending for the same resource. Multi-core platforms, thus, allow developers to optimize applications by intelligently partitioning different workloads on different processor cores. Application code can be optimized to use multiple processor resources, resulting in faster application performance.

Multi-threaded applications running on multi-core platforms have different design considerations than do multi-threaded applications running on single-core platforms.

Considering the case of memory caching, each processor core may have its own cache. At any point in time, the cache on one processor core may be out of sync with the cache on the other processor core.

Suppose there are two threads running on a dual-core processor. Thread 1 runs on core 1 and thread 2 runs on core 2. The threads are reading and writing to neighboring memory locations. Since cache memory works on the principle of locality, the data values, while independent, may be stored in the same cache line. As a result, the memory system may mark the cache line as invalid, even though the data that the thread is interested in hasn't changed. This problem is known as false sharing. On the other hand, considering a single-core platform, there is only one cache shared between threads; therefore, cache synchronization is not an issue. Thread priorities can also result in different behavior on single-core versus multi-core platforms. For example, consider an application that has two threads of differing priorities. In an attempt to improve performance, the developer assumes that the higher priority thread will always run without interference from the lower priority thread. On a single-core platform, this may be valid, as the operating system's scheduler will not yield the CPU to the lower priority thread. However, on multi-core platforms, the scheduler may schedule both threads on separate cores. Therefore, both threads may run simultaneously. If the developer had optimized the code to assume that the higher priority thread would always run without interference from the lower priority thread, the code would be unstable on multicore and multi-processor systems.

#### 3.5 Concurrency [15]

Two events are said to be concurrent if they occur within the same time interval. Two or more tasks executing over the same time interval are said to execute concurrently. Concurrent does not necessarily mean at the same exact instant. For example two tasks may execute concurrently within the same second but with each task executing within different fractions of the second. The first task may execute for the first tenth of the second and pause. The second task may execute for the next tenth of the second and pause. The first task may start again executing in the third tenth of a second and so on. Each task may alternate executing. However, the length of a second is so short that it appears that both tasks are executing simultaneously.

Concurrent tasks can execute in a single or multiprocessing environment. In a single processing environment, concurrent tasks exist at the same time and execute within the same time period by context switching. In a multiprocessor environment, if enough processors are free, concurrent tasks may execute at the same instant over the same time period. The determining factor for what makes an acceptable time period for concurrency is relative to the application.

#### 3.6 Thread level Parallelism [6]

When implemented properly, threading can enhance performance by making better use of hardware resources.

A thread can be defined from both, hardware and software point of view. A thread is a discrete sequence of related instructions that is executed independently of other instruction sequences. In a program there is at least one thread called main thread, which, furthermore, can create other threads. On the other hand, at hardware level, thread is an execution path that remains independent of other hardware execution paths.