# ERROR CORRECTION METHODS FOR LATENCY-CONSTRAINED FLASH MEMORY SYSTEMS

by

# PRIYANKA ANKOLEKAR

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

THE UNIVERSITY OF TEXAS AT ARLINGTON

August 2008

Copyright © by Priyanka Ankolekar 2008

All Rights Reserved

#### **ACKNOWLEDGEMENTS**

Foremost, I would like to thank my mentors and supervisors, Stephan Rosner at Spansion Inc. and Dr. Jonathan Bredow at UT-Arlington, without whom I would not have done a thesis. Dr. Bredow not only supervised my thesis, he agreed to do so from Texas while I was in California for the entire duration of my work. I would like to thank him for being patient, having faith in me and providing me with vital guidance all the time. Stephan Rosner shared a lot of his expertise and insight with me refusing to accept anything less than the best I could do. His enthusiasm and inspiration was always there when I needed it.

I wish to thank Roger Isaac and Qamrul Hasan of Spansion for patiently answering all my questions and for the endless discussions which helped me out of many a tight-spot I encountered while working on this thesis. There are many others at Spansion whose assistance I deeply value – George Minassian, Venkat Natarajan, Mark Randolph and Darlene Hamilton. I would like to specially thank Filomena Mendonsa for brightening up the atmosphere at work.

I would like to express my appreciation to Dr. A. Davis and Dr. S. Gibbs for helping me to take this thesis to consummation by being a part of my thesis committee.

I am tempted to individually thank all of my friends, but the list will be too long and from fear of leaving someone out, I will simply say thank you all very much. However, Hari deserves a special thank you for helping me in every way and making my stay in California so easy.

I cannot finish without saying how grateful I am to Vinayak for making me laugh when I was stressed out and for the incredible amount of patience he has had with me. Lastly and most importantly, I would like to thank my parents whose faith in me sometimes borders on craziness and without which I would not be studying for a Master's degree. To them I dedicate this thesis.

July 11, 2008.

#### ABSTRACT

# ERROR CORRECTION METHODS FOR LATENCY-CONSTRAINED FLASH MEMORY SYSTEMS

Priyanka Ankolekar, M.S.

The University of Texas at Arlington, 2008

Supervising Professor: Jonathan Bredow

Maintaining the reliability of data stored in Flash devices and reading it correctly has become a challenge as the demand for higher density is forcing aggressive shrinking of Flash architectures. For all Flash systems, especially latency-constrained NOR Flash, an on-chip error correction code (ECC) is the only viable and robust solution to this problem.

This thesis investigates and optimizes low-latency error correction schemes for on-chip implementation in NOR systems using existing error correction methods as a starting point. As the first step towards doing this, a mathematical relation has been derived to compute the bit error rate (BER) of a memory array using technology-specific voltage distribution curves. The required error correction capacity is calculated using the BER of the memory array. Current onchip error correction (ECC) schemes in NOR Flash consist of a single error correcting Hamming code. However, for emerging Flash devices single bit error correction does not suffice to maintain data reliability. This problem has been addressed by analyzing and optimizing existing ECC schemes for low latency and minimal hardware and parity overhead while achieving at

iv

least 2-bit error correction. One of the proposed algorithms is a dual bit Hamming code which uses the Hamming code for 2-bit error detection and correction. Another optimized scheme, called Hierarchical BCH, makes effective use of the fast and simple Hamming code to correct frequently occurring single bit errors and the multi error correction BCH code to correct higher order errors in the rare case when the Hamming code detects a 2-bit error. This scheme gives an average latency of around 4ns while improving the array BER from 10<sup>-7</sup> to 10<sup>-15</sup>. Thus all these methods have been quantitatively proven to be applicable in latency-constrained eXecute-in-Place (XiP) NOR Flash systems.

# TABLE OF CONTENTS

| ACKNOWLED     | GEMENTS                                         | iii  |

|---------------|-------------------------------------------------|------|

| ABSTRACT      |                                                 | iv   |

| LIST OF ILLUS | STRATIONS                                       | ix   |

| LIST OF TABL  | .ES                                             | Xi   |

| Chapter       |                                                 | Page |

| 1. INTRODU    | JCTION                                          | 1    |

| 1.1.          | Data Reliability in Flash Memory                | 1    |

| 2. FLASH M    | MEMORY AND FAILURE MECHANISMS                   | 4    |

| 2.1. F        | Flash Memory Architectures                      | 4    |

| 2.1.1.        | Conventional Flash Technology                   | 4    |

| 2.1.2.        | Flash Architectures                             | 4    |

| 2.1.3.        | Spansion MirrorBit® Flash Technology            | 5    |

| 2.1.4.        | Types of Flash Memory: NAND and NOR             | 6    |

| 2.1.5.        | NOR XiP Execution Model                         | 7    |

| 2.2. F        | Flash Memory Failure Mechanisms                 | 8    |

| 2.2.1.        | Narrowing of the Threshold Voltage Window       | 8    |

| 2.2.2.        | Widening of Charge Distributions                | 8    |

| 2.2.3.        | Single Bit Charge Loss/Gain                     | 9    |

| 2.3.          | Standard Approaches against Flash Failures      | 10   |

| 2.3.1.        | Dynamic Reference Tracking                      | 10   |

| 2.3.2.        | Compensating Technology Errors in Design Cycles | 11   |

|       | 2.3.3  | 3. Using Error Correction Codes (ECCs)                     | 11  |

|-------|--------|------------------------------------------------------------|-----|

| 2     | .4.    | Defining Bit Error Rate as a Measure for Failures          | 12  |

|       | 2.4.1  | 1. Case 1 – The General Case                               | 13  |

|       | 2.4.2  | Case 2 – Voltage Distributions at Start of Life            | 14  |

|       | 2.4.3  | 3. Case 3 – Non-overlapping distributions: '1' read as '0' | 15  |

|       | 2.4.4  | 1. Case 4 - Non-overlapping distributions: '0' read as '1' | 16  |

|       | 2.4.5  | 5. Case 5 – Overlapping distributions: '1' read as '0'     | 16  |

|       | 2.4.6  | S. Case 6 – Overlapping distributions: '0' read as '1'     | 17  |

| 3. Al | NALYS  | SIS OF ERROR CORRECTION CODES                              | 20  |

| 3     | .1.    | HAMMING CODES                                              | 20  |

|       | 3.1.1. | . The Mechanics                                            | 21  |

|       | 3.1.2  | Encoding                                                   | .23 |

|       | 3.1.3  | Decoding                                                   | .24 |

|       |        | 3.1.3.1. Standard Array Method                             | .25 |

|       | 3.1.4  | Error Detecting and Correcting Capabilities                | .27 |

|       | 3.1.5  | Cyclic Hamming Codes                                       | 28  |

| 3     | .2.    | Multi Bit Error Correction BCH Codes                       | 28  |

|       | 3.2.1  | 1. The Mechanics                                           | 30  |

|       | 3.2.2  | 2. Encoding                                                | 31  |

|       | 3.2.3  | 3. Decoding                                                | 35  |

|       |        | 3.2.3.1. Standard Algebraic Decoding Method                | 35  |

|       |        | 3.2.3.2. Massey's Step-by-Step Decoding Algorithm          | 38  |

| 3     | .3.    | Computing Required Error Correction Capacity               | 40  |

| 4. IN | /IPLEM | MENTATION AND RESULTS                                      | 43  |

| 4     | .1.    | Error Correction Architectures for NOR Flash               | 43  |

|       | 4.1.1  | Single Bit Hamming Code                                    | 43  |

| 4.1.2.      | Dual Bit Hamming Code                   | 46 |

|-------------|-----------------------------------------|----|

| 4.1.3.      | BCH Code                                | 49 |

| 4.1.4.      | Hierarchical BCH                        | 52 |

| 4.2. A      | analyzing and Comparing Implementations | 54 |

| 4.2.1.      | Software Implementation                 | 55 |

| 4.2.2.      | Hardware Implementation                 | 56 |

| 4.2.3.      | Mixed Implementation                    | 60 |

| 5. SUMMAR   | RY AND CONCLUSIONS                      | 61 |

| APPENDIX    |                                         |    |

| A. HO\      | W TO COMPUTE MINIMAL POLYNOMIALS        | 63 |

| REFERENCES  | S                                       | 66 |

| BIOGRAPHICA | AL INFORMATION                          | 70 |

# LIST OF ILLUSTRATIONS

| Figure                                                                                              | Page |

|-----------------------------------------------------------------------------------------------------|------|

| 2.1. The Conventional Memory Cell – A Floating Gate Transistor [12]                                 | 4    |

| 2.2. Transistor threshold voltage distributions of cells in (a) an SLC array (b) a 2 bits/cel array |      |

| 2.3. A MirrorBit cell                                                                               | 6    |

| 2.4. NOR XiP Execution model                                                                        | 7    |

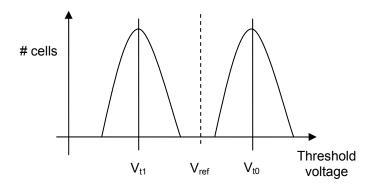

| 2.5. V <sub>t</sub> /Complementary Bit Disturb window – ideal V <sub>t</sub> distributions          | 8    |

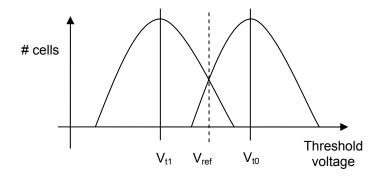

| 2.6. Actual V <sub>t</sub> distributions of cells storing a '1' and a '0' respectively              | 9    |

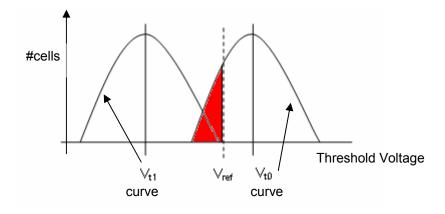

| 2.7. Overlap of V <sub>t</sub> distributions of cells containing '1' and '0'                        | 9    |

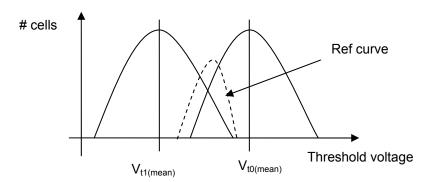

| 2.8. Dynamic reference curve                                                                        | 11   |

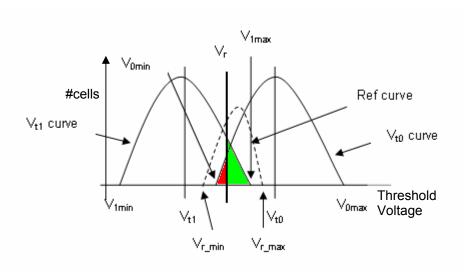

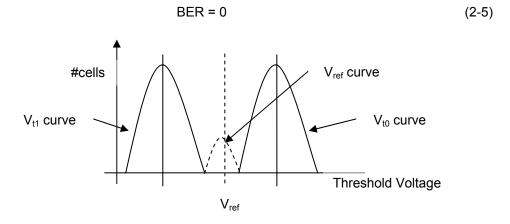

| 2.9. General case for calculation of current BER using a dynamic reference voltage                  | 13   |

| 2.10. Threshold voltage distributions across the memory array at the start of life                  | 14   |

| 2.11. Read error in non overlapping distributions ('1' read as a '0')                               | 15   |

| 2.12. Read error in non overlapping distributions ('0' read as a '1')                               | 16   |

| 2.13. Read error in overlapping V <sub>t</sub> distributions ('1' read as a '0')                    | 17   |

| 2.14. Read error in overlapping distributions ('0' read as a '1')                                   | 17   |

| 3.1. The mechanics of encoding of a (7, 4) Hamming code                                             | 21   |

| 3.2. Single bit error detection and correction using Hamming codes                                  | 22   |

| 3.3. Standard array for an (n, k) linear code                                                       | 26   |

| 3.4. 2D representation of redundancy around each code vector and the concept of $d_{min}$ .         | 27   |

| 3.5. (a) Modulo-2 addition (b) Modulo-2 multiplication                                              | 29   |

| 3.6. | Graphical representation of u = (1 1 1)                        | . 30 |

|------|----------------------------------------------------------------|------|

| 3.7. | Oversampling polynomial u(X)                                   | .30  |

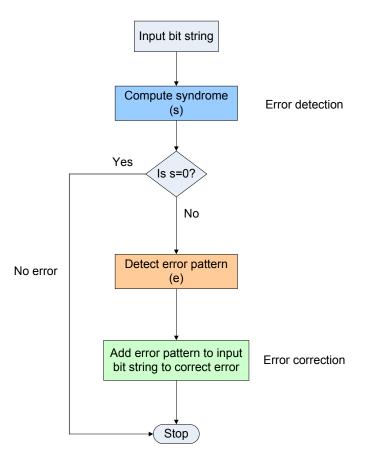

| 4.1. | Single bit Hamming decoding algorithm                          | 45   |

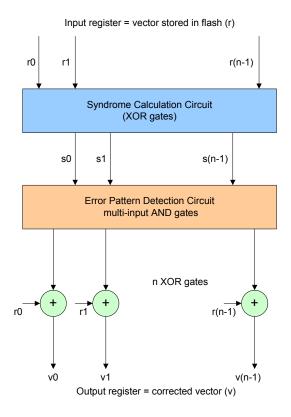

| 4.2. | Hamming decoder block diagram                                  | 46   |

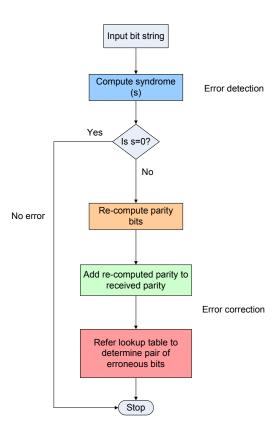

| 4.3. | Dual Bit Hamming Code Flow Diagram                             | .47  |

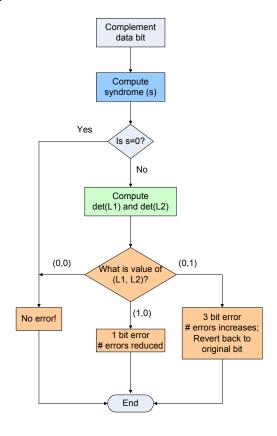

| 4.4. | Step-by-step BCH decoding algorithm for 2-bit error correction | 50   |

| 4.5. | Block Diagram of Massey's step-by-step BCH Decoding Algorithm  | .51  |

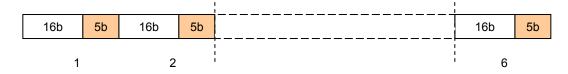

| 4.6. | Example of Hierarchical BCH code                               | . 52 |

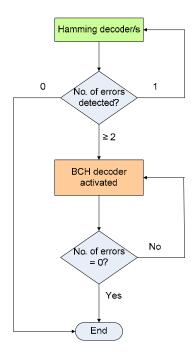

| 4.7. | Flow Diagram for the Hierarchical BCH Decoding Scheme          | .53  |

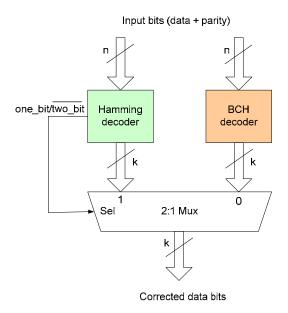

| 4.8. | Block Diagram of the Hierarchical BCH Decoding Scheme          | 54   |

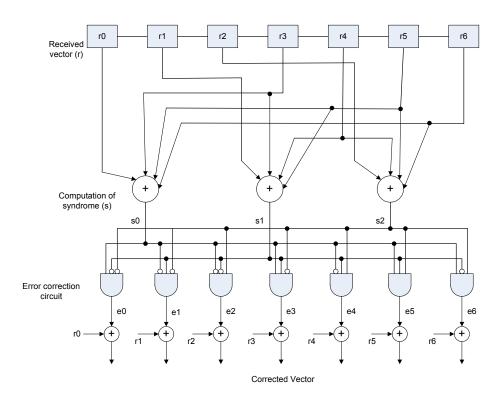

| 4.9. | Gate Level Circuit for a (7, 4) Hamming Code                   | .58  |

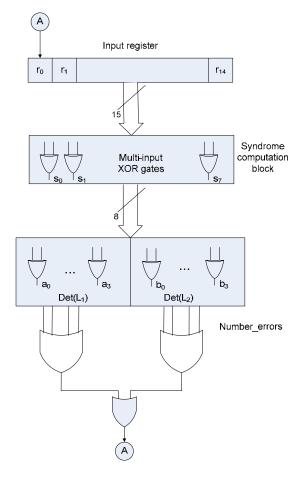

| 4.10 | . Gate Level Circuit for a (15, 7) BCH Code                    | . 59 |

# LIST OF TABLES

| Tabl | e                                                                                                 | Page |

|------|---------------------------------------------------------------------------------------------------|------|

| 2.1. | Comparing NAND and NOR Flash memory                                                               | 7    |

| 3.1. | Reconstructing the oversampled polynomial u(X)                                                    | 31   |

| 4.1. | Summary of optimized architectures for latency-constrained Flash systems                          | 44   |

| 4.2. | Lookup table for erroneous data bit pairs and corresponding 3-bit pattern for (7, 4) Hamming code |      |

| 4.3. | Possible Implementation Choices for ECC Architectures                                             | 55   |

| 4.4. | Latencies for Software Implementation of ECC Architectures                                        | 56   |

| 4.5. | Estimated Latency and Gate Count for Hardware Implementation                                      | 57   |

| 4.6. | Estimated Latency and Gate Count for Generic 256b Codes                                           | 57   |

| 4.7. | Latency and Gate Count for Synthesized Hardware Designs                                           | 59   |

## CHAPTER 1

#### INTRODUCTION

#### 1.1. Data Reliability in Flash Memory

Flash technology is the fastest growing semiconductor business because the embedded devices market and especially mobile devices require a substantial amount of fast, non-volatile, solid-state storage having high densities. Flash memory is indispensable in battery-powered applications like cell phones, cars, printers, networking equipment, set-top boxes, high-definition TVs, games and other consumer electronics. The increasing complexity of and demand for these products along with an enormous price pressure forces aggressive shrinking of device geometries as well as increasing storage capacities per area by storing multiple bits in each memory cell through multi-level cell (MLC) architectures for Flash memories.

These advances in increasing stored information per unit area by storing multiple bits as different charge levels in a memory cell result in a significant technical challenge in storing and detecting bits. Increased density leads to an increase in the Bit Error Rate (BER) of memory devices. This BER is affected by common disturb mechanisms such as silicon defects, cross-coupling, charge loss (or gain) over time. Bit disturb mechanisms increasingly affect data reliability and need to be compensated for with new methods as currently used solutions are not adequate anymore. For system stability it is mandatory to maintain some maximum BER.

There are two main approaches to achieve a suitable BER in a Flash memory array. One approach is making designs adaptable to technology errors. However, an extensive debug phase extends the overall design cycle of the product affecting the cost adversely and resulting in a loss in market opportunity. This method requires research on a per product basis and therefore is impractical for cost reasons.

The second approach is to correct bit errors in real-time using error correction codes (ECCs). Error correction methods reconstruct lost information by adding redundancy to the stored information. They can be implemented in a controller outside the memory device or on-chip with the memory array itself. The controller external to the memory chip can allow an area-efficient implementation of the algorithm. But controllers designed for NOR Flash memory devices do not have the infrastructure for supporting an ECC implementation making this a non-viable option.

This makes on-chip ECC the only solution. Only simple ECC algorithms can be implemented in the memory device because typical memory technologies do not easily support the efficient integration of large scale digital circuits. Ideally less complex ECC algorithms provide low latency access to the memory array and thus do not interfere with the software model of the memory system. The advantage of applying ECC on the memory device is that, differently from controller-based ECC, ECC-requirements of the memory, like low latency and low hardware and parity overhead, can be matched with the complexity of the applied ECC algorithm. The disadvantage is the limitation to low-complexity (and typically low-latency) ECC algorithms.

Advancements in Flash technology demand an improvement in and optimization of the methods used to protect and correct stored bits. This thesis addresses this problem in low latency NOR Flash memories in the following manner:

The causes for failures in Flash memory have been studied and related technology data has been used to extract error probabilities for a given memory array. These probabilities help determine the bit error rate for the memory array. The computed bit error rate (BER) has been used to quantify the exact requirements for an on-chip ECC implementation in NOR Flash. These requirements are low latency, required error correction capacity, a low gate count (in case of a hardware implementation) and a parity overhead that matches the 'spare' area available in the array (Spare area in a given memory array is a fixed area consisting of a certain

fixed number of bits that are not available for use by the consumer. This area can be used to store ECC redundancy computed internally in the memory device. As long as the ECC redundancy is less than or equal to the number of bits in the spare area, it does not add any additional bit overhead). These requirements are used as the basis for comparison of relevant published error detection/ correction (EDC/ECC) algorithms. This study helps to identify shortcomings in existing algorithms with regards an on-chip implementation in low-latency Flash systems. Existing algorithms are optimized in the light of these shortcomings to adhere to NOR Flash requirements and constraints. It is found that there is a trade-off between the error correction capacity of the algorithm, hardware complexity, latency and data overhead.

Giving primary consideration to low latency and high error correction capacity followed by a low hardware complexity and data overhead, a system-level implementation is proposed for each recommended solution. Every implementation is evaluated in terms of latency, bandwidth impact, die size and scalability across generations. This helps to arrive at optimum solutions for ECC algorithms that can be applied to improve data reliability in low-latency NOR Flash memories as device geometries become smaller.

#### CHAPTER 2

## FLASH MEMORY AND FAILURE MECHANISMS

## 2.1. Flash Memory Architectures

Flash memory is nonvolatile (NVM) memory that can be electrically erased and programmed.

## 2.1.1 Conventional Flash Technology

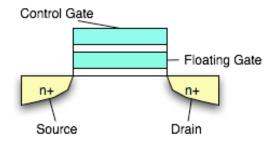

Information is stored in a Flash memory in an array of memory cells consisting of floating gate transistors. A floating gate transistor is a MOSFET having two gates – a control gate (CG) and a floating gate (FG). The floating gate is completely surrounded by the dielectric layer. Hence charge trapped on it remains unchanged for extended periods of time. This charge alters the threshold voltage (V<sub>t</sub>) [5] of the transistor. To read data, a voltage is applied to the control gate. The presence (logical '0') or absence (logical '1') of current through the channel helps detect the stored bit. Figure 2.1 shows a floating gate transistor.

Figure 2.1 The Conventional Memory Cell – A Floating Gate Transistor [12]

#### 2.1.2 Flash Architectures

A single memory cell can store one or more bits of data. A cell which stores a single data bit is called a *single level cell (SLC)* while one which stores more than one bit is a *multilevel cell (MLC)*. MLCs store multiple bits per cell by storing varying amounts of charge for each bit pattern. Therefore, in MLCs, the amount of current flow is sensed, rather than the mere

presence or absence of it as in SLCs, in order to determine the level of stored charged. Figure 2.2 shows the threshold voltage distributions in (a) single level cells and (b) multilevel cells.

Figure 2.2 Transistor threshold voltage distributions of cells in

(a) an SLC array (b) a 2 bits/cell MLC array

#### 2.1.3 Spansion MirrorBit® Flash Technology

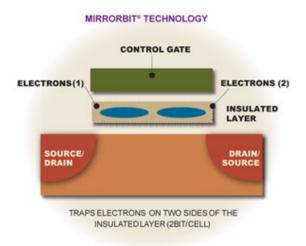

Spansion's MirrorBit® Flash technology physically stores two independent bits on a single cell. This makes it an SLC technology that can store multiple bits per cell. In a MirrorBit cell (Figure 2.3) data is stored as charge trapped in a thin insulating oxide-nitride-oxide (ONO) layer over the junction edges of MOSFET transistors (Note – In a floating gate transistor charge is trapped on a conducting gate terminal). The cell is programmed by injecting channel hot electrons (CHE) into the ONO layer and is erased by band-to-band-generated tunnel-assisted hot hole injection (HHI). The stored charge is sensed by reversing the role of the source and the

drain relative to programming conditions and reading the cell current [2]. Since charge can be stored on both sides of the transistor two-bit operation per cell is attained [3, 4].

Figure 2.3 A MirrorBit cell

MirrorBit architecture involves storing two bits (MirrorBit) or four bits (MirrorBit Quad) per cell. Thus a single MirrorBit cell can store at least 4 (2 bits/cell) up to 16 (4 bits/cell) levels of charge. This significantly improves the storage density. At smaller geometries, for example, 45nm or 32nm, the ONO layer can store a mere few hundred electrons making it difficult to read the amount of stored charge. Therefore read errors are inherent to Flash technology.

## 2.1.4 Types of Flash memory: NAND and NOR

Flash memories are classified as – NAND and NOR Flash. These two types differ in the manner in which individual memory cells are connected [13]. Table 2.1 compares NAND and NOR Flash operation.

Table 2.1 Comparing NAND and NOR Flash memory

| Parameter           | NOR           | NAND                            |

|---------------------|---------------|---------------------------------|

| Density             | 1Mbit – 1Gbit | 64Mbit – 16 Gbit (or<br>higher) |

| Read initial access | 80ns          | 20,000ns                        |

| Program             | 2 Mbytes/s    | 10 Mbytes/s                     |

| Erase               | 2 Mbytes/s    | Very high                       |

| Access method       | Random        | Sequential                      |

## 2.1.5 NOR XiP Execution Model

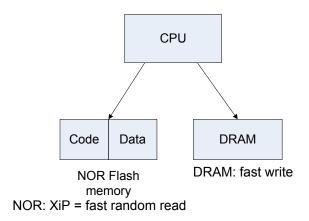

Random read accesses in NOR result in a very low initial read access time (~80ns) in comparison with sequential access NAND (~20,000ns). Therefore NOR is used for code storage and execution while NAND is used for data storage purposes. NOR is used in eXecute-in-Place (XiP) execution models (Figure 2.4) for code storage and execution. In such a model, the processor executes code directly from memory without copying it into RAM and then executing it. This makes for faster execution of codes while minimizing the RAM requirement of the system resulting in an overall reduction in cost. The XiP Execution Model combines high performance read with relatively inexpensive storage.

Figure 2.4 NOR XiP Execution model

## 2.2 Flash Memory Failure Mechanisms

# 2.2.1 Narrowing of the threshold voltage window

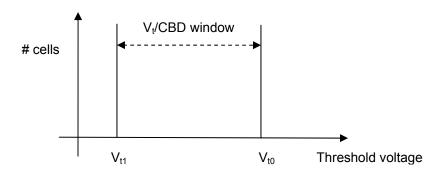

The gate dielectric layer has point defects in which charges get trapped. These trapped charges may migrate and redistribute between traps due to thermal activation. This redistribution may change the threshold voltage ( $V_t$ ) of the cell ultimately leading to a read error [1]. During an erase cycle, holes are injected into the ONO layer. In the subsequent programming step some holes stay and accumulate from cycle to cycle [1]. This degrades the  $V_t$  of the cell. The difference between the threshold voltages of a stored 0 and a 1 is called the  $V_t$ -window. It is also known as the Complementary Bit Disturb (CBD) window because if this window reduces so that the threshold voltages of 1 and 0 overlap, a 1 may be read as a 0 and vice versa.

Figure 2.5 V<sub>t</sub>/Complementary Bit Disturb window – ideal V<sub>t</sub> distributions

# 2.2.2 Widening of charge distributions

Figure 2.5 illustrates the ideal distributions of the  $V_t$  of the cells having a 1 and a 0 respectively. In reality, all the cells storing a 1 (or a 0) do not have the same  $V_t$ , their  $V_t$  values deviate from the ideal (Figure 2.2). This results in a  $V_t$  distribution as shown in Figure 2.6.

Figure 2.6 Actual V<sub>t</sub> distributions of cells storing a '1' and a '0' respectively

As the number of programming cycles increases, trapped charges alter the  $V_t$  – distributions shown in Figure 2.6. The distributions widen. This widening of distributions along with the narrowing of the  $V_t$  window results in an overlap of the '1' and '0' voltage distribution curves (Figure 2.7). If a programmed or erased bit lies in the overlap region, there is a read error.

Figure 2.7 Overlap of V<sub>t</sub> distributions of cells containing '1' and '0'

## 2.2.3 Single bit charge loss/gain

Single bit charge gain (SBCG) typically occurs after some program-erase cycling. It results in a very small number of cells having a large threshold voltage shift from the normal distribution. It has been attributed to localized defects in the tunnel oxide [6-8]. Such bits are called 'tail' bits because they lie at the ends of the voltage distribution curves. This effect is

commonly associated with the transient charging and discharging of cycling induced traps in the tunnel oxide [9], [10].

There are primarily three failure mechanisms in MLC Flash memory devices causing random bit errors which affect the reliability of stored data particularly as device geometries become smaller (for example, 45nm or 32nm).

#### 2.3 Standard Approaches against Flash Failures

Data reliability issues in Flash memory are currently being addressed in three ways: by using dynamic reference voltage tracking, compensating technology errors in design cycles and using error correction codes.

## 2.3.1 Dynamic Reference Voltage Tracking

Bit failures caused by narrowing and shifting of the CBD window can be mitigated to a certain extent by using a *dynamic reference tracking* scheme. In this method, the reference  $(V_{ref})$  of the voltage distributions is made dynamic so that it varies in accordance with the shift in the distribution curves. The dynamic reference is computed by taking an average of three voltages –  $V_t$  of a cell containing a '1', a '0' and a *read reference* cell. The *read reference cell* is set to a predetermined  $V_t$  value at wafer sort that distinguishes erased bits from programmed bits. The result is a *reference curve* over a period of time instead of a fixed reference line or point. So Figure 2.7 is redrawn as Figure 2.8.

Figure 2.8 Dynamic reference curve

# 2.3.2 Compensating Technology Errors in Design Cycles

This method involves in-depth, hence prolonged, research on a per product basis to compensate for failure mechanisms for individual designs. Each design is analyzed for possible failure mechanisms and solutions are proposed to eliminate or minimize their effect. This results in increased design cycles which has an unfavorable impact on the cost of and the time taken to market the product.

## 2.3.3 Using Error Correction Codes (ECCs)

An ECC algorithm can be applied on the controller of the Flash system or on the Flash memory chip itself.

An error correction algorithm can be implemented on a controller which is part of the system architecture but external to the memory chip. The ECC algorithm reconstructs lost information by adding redundancy to the stored data.

This technique allows large scale integration which supports an area effective implementation of ECC algorithms. It is easy to implement robust and more sophisticated ECC algorithms, but at the cost of a significant increase in read latencies. Therefore, it works well for storage-optimized devices where longer read latencies are acceptable. There are techniques to

reduce the read latencies for a controller-based ECC, but for XiP or code-optimized Flash memories the infrastructure for implementing an ECC algorithm on the controller does not exist.

This makes an on-chip ECC the only choice. The major advantage of an on-chip ECC is the algorithm hardware can be scaled down along with the device. On the flip side, complex ECC algorithms cannot be implemented easily as they require large digital circuits. Besides, since the algorithm is on-chip, read latencies have to be kept very small. Therefore the algorithms should be simple. Thus the ECC requirements of the memory can be matched with the complexity of the applied ECC algorithm. Therefore, on-chip ECC is the preferred implementation for latency constrained XiP NOR Flash. Software algorithms can also be implemented on-chip due to the presence of an on-chip 8051-like microcontroller.

On-chip ECC in NOR Flash memory should be constrained to achieve a low latency – typically 10ns, a low implementation complexity which translates to a low gate count (< 5000 NAND gates) in case of hardware and minimal RAM footprint in case of software and most importantly, a target bit error rate ~10<sup>-15</sup> for the memory array.

# 2.4 <u>Defining Bit Error Rate as a Measure for Failures</u>

The raw BER of the array should be known accurately in order to decide the error correction capacity of a given ECC algorithm needed to achieve the required target BER ( $\sim$ 10<sup>-15</sup>). The BER prior to using ECC can be computed using the technology data which is plotted as voltage distribution curves for the memory array (Section 2.1). The aggregate error distribution function is defined using the '1' and '0' threshold voltage distribution as a function of the number of programming cycles. The reference voltage varies dynamically as the voltage distribution for the array changes. Based on this distribution and the consequent variation of the reference ( $V_{ref}$ ), a formula is derived to compute the BER for a given Flash device. Six cases have been considered.

## 2.4.1 Case 1 - The General Case

In general the 1 and 0 distribution curves overlap. The reference voltage is in the middle of the overlap region (Figure 2.9).

Figure 2.9 General case for calculation of raw array BER using a dynamic reference voltage

The region in green consists of all the erased (1) bits which are read as a 0 while the region in red represents the programmed (0) bits which are read as a 1. At any given time, a read error occurs in a cell if and only if:

- i. (program a '0') AND (programmed cell lies in the red region) or

- ii. (erase/write a '1') AND (erased cell lies in the green region)

Consider (i):

P('0' read as a '1')

- = P(program '0',  $V_{t0} < V_{ref}$ )

- = {Area (red region)} / {Area (V<sub>t0</sub> curve) distribution}

$$= \left\{ \int_{V_{0 \, min}}^{V_{r}} P(V_{t0}) dV_{t0} \right\} / \left\{ \int_{V_{0 \, min}}^{V_{0 \, max}} P(V_{t0}) dV_{t0} \right\}$$

(2-1)

Taking into account statistical variability in the decision threshold (reference) voltage  $V_{ref}$ , this becomes,

$$P('0' \text{ read as a '1'}) = \{ \int_{V_{r min}}^{V_{r max}} P(program'0' | V_{t0} < V_{ref}) P(V_{ref}) dV_{ref} \}$$

(2-2)

Similarly, for (ii)

P('1' read as a '0')

- = P(erase/write '1',  $V_{t1} > V_{ref}$ )

- = {Area (green region)}/{Area (Vt1 curve)}

$$= \left\{ \int_{V_{r}}^{V_{1} \text{max}} P(V_{t1}) dV_{t1} \right\} / \left\{ \int_{V_{1} \text{min}}^{V_{1} \text{max}} P(V_{t1}) dV_{t1} \right\}$$

(2-3)

Taking into account statistical variability in the decision (reference) threshold voltage (V<sub>ref</sub>), this becomes,

$$P('1' \text{ read as a '0'}) = \{ \int_{V_{r min}}^{V_{r max}} P(program'1' | V_{t1} > V_{ref}) P(V_{ref}) dV_{ref} \}$$

(2-4)

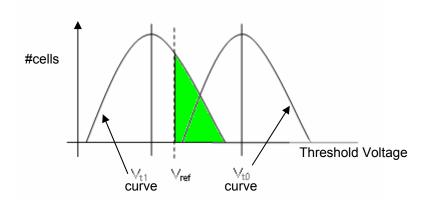

#### 2.4.2 Case 2 - Voltage Distributions at Start of Life

Figure 2.10 is a representation of the distribution at the start of life of the device. The 1 and 0 threshold voltage distributions are very tight and do not overlap each other. The resulting reference voltage ( $V_{ref}$ ) also lies approximately at the center of the CBD window. Therefore there are no read errors possible in this case.

Figure 2.10. Threshold voltage distributions across the memory array at the start of life

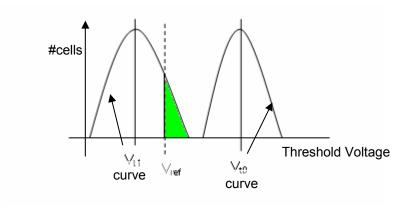

# 2.4.3 Case 3 - Non-overlapping distributions: '1' read as '0'

Figure 2.11. Read error in non overlapping distributions ('1' read as a '0')

This (Figure 2.11) is a special case of Case 1. Although the threshold voltage distributions for '0' and '1' do not overlap each other, the computed  $V_{ref}$  lies within the '1'-distribution. The cells that lie towards the right of  $V_{ref}$  in the shaded region are incorrectly read as a 0. The probability of a cell containing '1' being read as a '0' is:

P('1' read as '0')

- = P(erase/write '1', V<sub>t1</sub> > V<sub>ref</sub>)

- = {Area (green region)}/{Area (Vt1 curve)}

$$= \{ \int_{V_{t}}^{V_{1} \max} P(V_{t1}) dV_{t1} \} / \{ \int_{V_{1} \min}^{V_{1} \max} P(V_{t1}) dV_{t1} / \}$$

(2-6)

Accounting for the statistical variability in the decision threshold voltage (V<sub>ref</sub>),

$$P('1' \text{ read as a '0'}) = \{ \int_{V_{r min}}^{V_{r max}} P(\text{program'1'} | V_{t1} > V_{ref}) P(V_{ref}) dV_{ref} \}$$

(2-7)

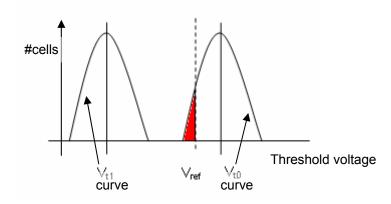

# 2.4.4 Case 4 - Non-overlapping distributions: '0' read as '1'

Figure 2.12. Read error in non overlapping distributions ('0' read as a '1')

This is similar to Case 3. Here the reference lies within the  $V_{t0}$  distribution. All the cells lying to the left of  $V_{ref}$  in the red region are read as '1' instead of a '0'. The probability of this read error is

P('0' read as '1')

- = P(program '0' ,  $V_{t0} < V_{ref}$ )

- = {Area (red region)} / {Area (V<sub>t0</sub> curve)}

$$= \left\{ \int_{V_{0 \, \text{min}}}^{V_{r}} P(V_{t0}) dV_{t0} \right\} / \left\{ \int_{V_{0 \, \text{min}}}^{V_{0 \, \text{max}}} P(V_{t0}) dV_{t0} / \right\}$$

(2-8)

However, since the decision threshold voltage (V<sub>ref</sub>) varies over the lifetime of the device,

$$P('0' \text{ read as '1'}) = \{ \int_{V_{r min}}^{V_{r max}} P(program'0' | V_{t0} < V_{ref}) P(V_{ref}) dV_{ref} \}$$

(2-9)

## 2.4.5 Case 5 – Overlapping distributions: '1' read as '0'

This is similar to Case 3. The difference is the overlap between the threshold voltage distributions for cells containing '1's and '0's respectively. A read error occurs if a stored '1' is read as a '0', i.e. the memory cell lies in the green region of the distribution.

Figure 2.13. Read error in overlapping V<sub>t</sub> distributions ('1' read as a '0')

The probability of error is given by:

P('1' read as a '0') = P(erase/write '1' ,  $V_{t1} > V_{ref}$ )

= {Area (green region)}/{Area (V<sub>t1</sub> curve)}

$$= \left\{ \int_{V_{t}}^{V_{1} \max} P(V_{t1}) dV_{t1} \right\} / \left\{ \int_{V_{1} \min}^{V_{1} \max} P(V_{t1}) dV_{t1} / \right\}$$

(2-10)

Considering the statistical variability of  $V_{\text{ref}}$ ,

$$P('1' \text{ read as a '0'}) = \int_{V_{r \, min}}^{V_{r \, max}} P(program'1' | V_{t1} > V_{ref}) P(V_{ref}) dV_{ref} \}$$

(2-11)

# 2.4.6 Case 6 – Overlapping distributions: '0' read as '1'

Figure 2.14. Read error in overlapping distributions ('0' read as a '1')

This case is similar to Case 4. The probability of a '0' read as a '1' is:

P('0' read as a '1')

- = P(program '0',  $V_{t0} < V_{ref}$ )

- = {Area (red region)} / {Area (V<sub>t0</sub> curve)}

$$= \{ \int_{V_{0 \min}}^{V_r} P(V_{t0}) dV_{t0} \} / \{ \int_{V_{0 \min}}^{V_{0 \max}} P(V_{t0}) dV_{t0} / \}$$

(2-12)

Accounting for a variable decision threshold voltage, V<sub>ref</sub>,

$$P('0' \text{ read as a '1'}) = \int_{V_{r \text{ min}}}^{V_{r \text{ max}}} P(\text{program'0'}| V_{t0} < V_{ref}) P(V_{ref}) dV_{ref}$$

(2-13)

Thus a mathematical relation has been developed to compute the current bit error rate using threshold voltage distributions in an array for all possible read error conditions that can occur in Flash memory.

XiP type NOR uses MLC architectures at smaller geometries. These are highly prone to bit disturbs. The bit error rate for a given memory array can be computed mathematically using technology data. Error correction codes are one of the important methods used to maintain data reliability by keeping the BER below 10<sup>-15</sup>. The low latency requirements of XiP NOR make a low-complexity on-chip ECC the preferred choice. Hamming codes and binary BCH codes are well suited for implementing as on-chip ECC for NOR Flash memory.

Hamming codes are the simplest error correcting block codes. They provide single bit error ECC and 2-bit error detection (EDC) (Section 3.1). These codes and their implementation as an on-chip ECC in Flash has been discussed in [31, 32]. [31] shows a Hamming decoder using asynchronous techniques. Asynchronous pulse generators are used to design a controllable clock for the decoder which is independent of the system clock. The transistors in the pulse generator have to be properly tuned. This may be an unnecessary effort for small

power savings. An area efficient implementation has been proposed in [32] for an on-chip Hamming decoder in NAND Flash. A few hundred gates are required to implement a Hamming decoder as will be proved in a later section. Therefore an area overhead is not a severe problem.

Hamming codes are suitable for a lower order BER (~10<sup>-12</sup>). They fail to ensure data reliability as BER increases to around 10<sup>-7</sup> for multi level cell architectures at smaller geometries. This necessitates the use of multi bit error correction. Convolutional codes effectively correct multiple bit errors. However a hardware implementation of a Viterbi encoder/decoder requires 20-30K gates which is very high for NOR Flash. [33] discusses a possible implementation of convolutional codes as on-chip ECC in MLC NOR. It is shown that the BER can be taken from 10<sup>-2</sup> to 10<sup>-11</sup> which is not the target bit error rate that is expected to maintain reliability of the Flash array. The performance of this code can be said to be comparable to a BCH algorithm discussed in detail later. Binary BCH codes can be designed to detect and correct multi bit errors. However there is a tradeoff between implementation complexity, latency and error correction capability of the code. The previous chapter discusses two BCH decoding algorithms of which Massey's step-by-step decoding algorithm [20] is expected to be effective in NOR Flash. The possibility of using BCH codes for error control in Flash memories has been mentioned in [36]. However it does not elaborate the possible implementation methods that may be used.

#### CHAPTER 3

## ANALYSIS OF ERROR CORRECTION CODES

On-chip error correction codes effectively compensate for deteriorating bit error rates which are generally of the order of 10<sup>-7</sup> to 10<sup>-11</sup> in Flash memory. Error correction codes improve the reliability of data by adding carefully designed redundant data over time (convolutional codes) or space (block codes). Convolutional codes operate on data streams where each bit is processed together with its succeeding and preceding bits. The results improve for higher encoder rates. The encoders and decoders used for convolutional codes (e.g. the Viterbi decoder and the Trellis encoder) are hardware-intensive circuits easily consisting of 20k-50k gates. This makes convolutional codes a good candidate only when hardware overhead is not a stringent constraint. On the other hand, block code algorithms can be designed to work within the latency and hardware constraints of NOR devices making them the codes of choice for on-chip ECC in Flash memory.

#### 3.1. <u>Hamming Codes</u>

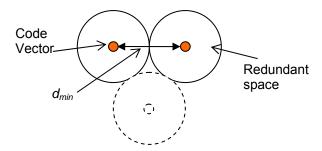

Block codes transform large blocks of data into code words. They only use current input data to compute redundancy for given data block as opposed to their convolutional counterparts which use past and future data too. The computed redundancy creates an extended decision 'space' around each information/data block. If the data word that is read out from memory lies in the decision space that 'belongs' to a certain information block, it is decoded as that information block.

Hamming codes illustrate the creation of redundant space around data blocks to detect and/or correct errors by simple mapping. Simple mechanics and the ease of implementation make these codes a popular choice for communication and data storage systems. However, they are ineffective if the number of random errors is large or if the errors are bursty.

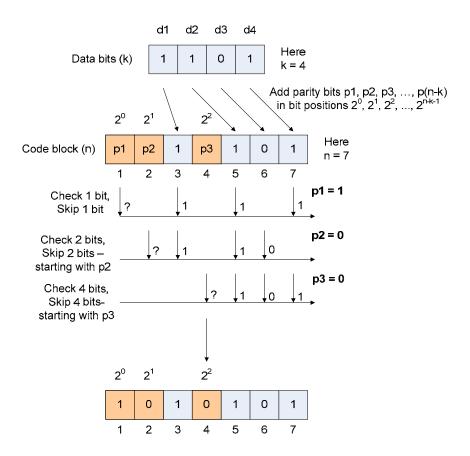

#### 3.1.1. The Mechanics

The (7, 4) (= (n, k)) Hamming code is the simplest single-error detection and correction, double-error detection code. Here 4 is the information block length (k) and 7 is the length of the output code word (n). The 3 additional bits (n-k) in the output code word are the redundant *parity* bits. In the example (Figure 3.1),  $d_1$ ,  $d_2$ ,  $d_3$  and  $d_4$  are the data bits to be encoded.  $p_1$ ,  $p_2$  and  $p_3$  are the parity bits.

Figure 3.1. The mechanics of encoding of a (7, 4) Hamming code

Suppose  $[d_1 \ d_2 \ d_3 \ d_4] = [1 \ 1 \ 0 \ 1]$ . The parity bits  $(p_1, p_2, p_3, ..., p_{n-k})$  are inserted in positions which are powers of 2  $(2^0, 2^1, 2^2, ..., 2^{n-k-1})$  because each parity bit represents an even parity check on information bits which are in bit positions whose binary representations have a '1' in the same place as the bit position (binary representation of a power of 2) of the parity. This

has the advantage of making the check positions independent of each other. For this example, the parity bits are computed in the following manner:

For  $p_1$ : Check alternate bits to see if even parity condition is satisfied.

$$p_1 = d_1 \bigoplus d_2 \bigoplus d_4 = 1 \tag{3-1}$$

For  $p_2$ : Check alternate sets of 2 bits each for even parity, starting with  $p_2$

$$p_2 = d_1 \oplus d_2 \oplus d_3 = 0 \tag{3-2}$$

For  $p_3$ : Check alternate sets of 4 bits each (starting with  $p_3$ ) for even parity,

$$p_3 = d_2 \oplus d_3 \oplus d_4 = 0 \tag{3-3}$$

In general, for  $p_{n-k}$  alternate sets of  $2^{n-k-1}$  bits each are checked to satisfy even parity. In this example, 1101 is encoded and stored as  $\underline{100}1101$  where the underlined bits are parity.

The relation between parity bits and the data bits is represented in matrix form as,

$$\begin{bmatrix} p_1 & p_2 & p_3 \end{bmatrix} = \begin{bmatrix} 1 & 1 & 0 & 1 \\ 1 & 0 & 1 & 1 \\ 0 & 1 & 1 & 1 \end{bmatrix} \begin{bmatrix} d_1 \\ d_2 \\ d_3 \\ d_4 \end{bmatrix}$$

(3-4)

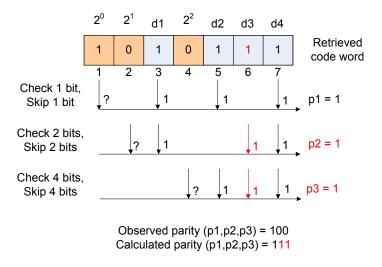

To detect and correct a single bit error: Suppose the retrieved code word is 1001111.

Figure 3.2. Single bit error detection and correction using Hamming codes

Assuming that at most a single bit may be disturbed, the erroneous bit is identified in the following manner (Figure 3.2):

If the observed parity  $(p_1, p_2, p_3) = 100$  and the calculated parity = 111, then the parity bits in conflict are  $p_2$ ,  $p_3$ . The bit that is exclusive to  $p_2$  and  $p_3$  is  $d_3$ . Hence  $d_3$  is the disturbed bit.

Now suppose the retrieved code word is  $\underline{110}0101$  (2-bit error). In this case, the observed parity  $(p_1, p_2, p_3) = 110$  and the calculated parity = 011 showing that  $(p_1, p_3)$  are in conflict. Hence  $d_2$  is incorrectly predicted to be in error.

In Hamming codes with distance 3 a double bit error is indistinguishable from a single bit error in a different code. In order to detect two bit errors and detect and correct a single bit error simultaneously, an additional parity bit is included in the code word. This increases the distance of the code to 4. This additional parity bit is calculated by adding (modulo-2) all the other bits in the code vector. Thus the presence of two bit errors can be detected but it cannot be corrected while a single bit error is detected and corrected.

#### 3.1.2. Encoding

As *k* increases (e.g. a (31, 26) code), it is impractical to use the above method.

The "generation" of a code word is achieved by a *generator matrix*,  $\mathbf{G}$ . The rows of a generator matrix generate all the code words for a particular code.  $\mathbf{G}$  is a  $(k \times n)$  matrix for a (n, k) code where n is the length of the code word and k is the data block length. In the k-dimensional vector space of all the binary n-tuples, it is possible to find k linearly independent code words such that every code word  $\mathbf{v}$  is a linear combination of these k code words. If  $\mathbf{u}$  is the information vector then,

$$\mathbf{v} = \mathbf{u}.\mathbf{G} \tag{3-5}$$

The generator matrix for the (7, 4) code is

$$\mathbf{G} = \begin{bmatrix} 1 & 1 & 0 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 & 0 \\ 1 & 1 & 1 & 0 & 0 & 1 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 1 \end{bmatrix}$$

(3-6)

Equation (3-6) shows the generator matrix in *systematic form*. The code word obtained after multiplying data with this matrix will have message bits easily distinguishable from the parity bits. Such a form of the encoded code work is called the *systematic form*. The generator matrix in systematic form is

$$G = [P I_k] \tag{3-7}$$

Where

$P = k \times (n-k)$  matrix which generates the parity bits.

$\mathbf{l_k} = k \times k$  identity matrix, i.e. a matrix having elements,  $\mathbf{b_{ij}} = 1$  for all  $\mathbf{i} = \mathbf{j}$  else  $\mathbf{b_{ij}} = 0$ .

Another useful matrix is called the *parity check matrix* (**H**). **H** is a (n-k) x n matrix such that  $\mathbf{G}.\mathbf{H}^\mathsf{T} = \mathbf{0}$  i.e. **G** and **H** are orthogonal. Alternately, an n-tuple  $\mathbf{v}$  is a code word in the code generated by **G** if and only if  $\mathbf{v}.\mathbf{H}^\mathsf{T} = \mathbf{0}$ . For **G** as written in Equation (3-7), the parity check matrix **H** is

$$\mathbf{H} = [\mathbf{I}_{\mathbf{n}-\mathbf{k}} \ \mathbf{P}^{\mathsf{T}}] \tag{3-8}$$

Where

$\mathbf{P}^{\mathsf{T}}$  = transpose of matrix  $\mathbf{P}$  in Equation (3-7)

$I_{n-k} = (n-k) \times (n-k)$  identity matrix.

**H** is called the *parity check matrix* because each row of **H** represents an even parity group with '1's in the positions of the bits that comprise the group.

# 3.1.3. Decoding

For a (n, k) linear code, if  $\mathbf{v} = (v_0, v_1, v_2, ..., v_{n-1})$  is the stored vector and  $\mathbf{r} = (r_0, r_1, r_2, ..., r_{n-1})$  is the vector read out from memory (received vector), then  $\mathbf{r}$  may differ from  $\mathbf{v}$  due to noise.

$$\mathbf{r} = \mathbf{v} + \mathbf{e} \tag{3-9}$$

Where **e** is an *n*-tuple called the *error vector* or *error pattern*.

When  $\mathbf{r}$  is read out, the host system should first determine if  $\mathbf{r}$  contains any errors. If so, an error correction algorithm must be executed. Errors are detected by computing the syndrome,  $\mathbf{s}$ , which is the vector product of the output vector and the transpose of the parity-check matrix.

$$\mathbf{s} = \mathbf{r}.\mathbf{H}^{\mathsf{T}}$$

$$= (\mathbf{v} + \mathbf{e}).\mathbf{H}^{\mathsf{T}}$$

$$= \mathbf{e}.\mathbf{H}^{\mathsf{T}}$$

(3-10)

If there are no errors or undetectable errors,  $\mathbf{s} = \mathbf{0}$ , else  $\mathbf{s} \neq \mathbf{0}$ . Undetectable error patterns are those which transform  $\mathbf{v}$  into another valid code. Since there are  $2^k - 1$  nonzero code words, there are  $2^k - 1$  undetectable error patterns.

If **H** is expressed in the systematic form, then Equation (3-10) yields a linear relationship between the syndrome and the error digits.

$$s_{0} = e_{0} + e_{n-k}p_{00} + e_{n-k+1}p_{10} + \dots + e_{n-1}p_{k-1,0}$$

$$s_{1} = e_{1} + e_{n-k}p_{01} + e_{n-k+1}p_{11} + \dots + e_{n-1}p_{k-1,1}$$

$$\dots$$

$$s_{n-k-1} = e_{n-k-1} + e_{n-k}p_{0,n-k-1} + e_{n-k+1}p_{1,n-k-1} + \dots + e_{n-1}p_{k-1,n-k-1}$$

$$(3-11)$$

Any error correction scheme is a method to solve the (n-k) linear equations of Equation (3-11) for the error digits. Once **e** is found, the vector  $\mathbf{r} + \mathbf{e}$  is taken as the actual stored code word [15]. Solving these equations is not easy since they have  $2^k$  solutions. One of the most popular decoding schemes for linear block codes like Hamming codes, is the *Standard Array Method* which is also known as the *syndrome decoding* or *table lookup decoding method*.

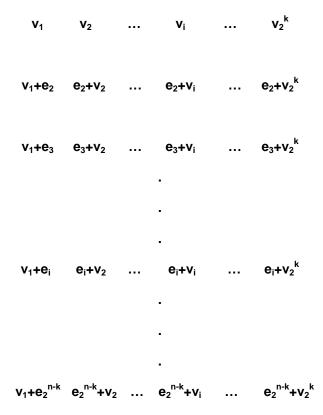

#### 3.1.3.1. Standard Array Method

For an (n, k) linear block code, there are  $2^k$  valid code vectors,  $\mathbf{v_1}, \mathbf{v_2}, ..., \mathbf{v_2}^k$ . The received vector  $\mathbf{r}$  may be any one of  $2^n$  possible n-tuples. Any decoding scheme is a rule to partition the  $2^n$  possible received vectors into  $2^k$  disjoint subsets  $D_1, D_2, ..., D_2^k$  such that the

code vector  $\mathbf{v_i}$  is contained in the subset  $D_i$  for  $1 \le i \le 2^k$  [15]. Thus a data 'space' is generated around each valid code word. If  $\mathbf{r}$  is located in the subset  $D_i$ , then  $\mathbf{r}$  is decoded into  $\mathbf{v_i}$ . This decoding is correct only if the actual stored vector was indeed  $\mathbf{v_i}$ .

Figure 3.3. Standard array for an (n, k) linear code

$\mathbf{v_1}$ ,  $\mathbf{v_2}$ , ...,  $\mathbf{v_2}^k$  are the  $2^k$  valid code vectors of the (n, k) linear block code. Generally,  $\mathbf{v_1} = \mathbf{0}$ .  $\mathbf{e_2}$ ,  $\mathbf{e_3}$ , ...,  $\mathbf{e_2}^{n-k}$  are distinct n-tuples from the remaining  $2^n - 2^k$  n-tuples. Thus, all the n-tuples are used in the array. Each subset  $D_i$  for  $1 \le i \le 2^{n-k}$  is the  $i^{th}$  column in this array (Figure 3.3). The  $2^{n-k}$  rows are known as the *cosets* and the n-tuples  $\mathbf{e_2}$ ,  $\mathbf{e_3}$ , ...,  $\mathbf{e_2}^{n-k}$  are the *coset leaders* for the corresponding rows.  $\mathbf{r}$  is decoded correctly only if the error pattern is a coset leader. All the  $2^k$  n-tuples of any given coset have the same syndrome. The syndromes for different cosets differ.

Summarizing the decoding process for a linear block code: The first step is to compute the syndrome  $\mathbf{s} = \mathbf{r.H}^T$ . This helps to locate the corresponding coset leader, say  $\mathbf{e}_t$ , for this

syndrome. The deduced coset leader is used to decode  $\mathbf{r}$  as  $\mathbf{v} = \mathbf{r} + \mathbf{e_t}$ .  $\mathbf{u}$  is easily obtained from  $\mathbf{v}$  since it is in the systematic form.

#### 3.1.4. Error Detecting and Correcting Capabilities

An important property of a code is the code's minimum *distance*, also known as the minimum *Hamming distance*. *Hamming distance* is the number of positions in which two code words differ. The minimum Hamming distance,  $d_{min}$ , is the least possible distance between a pair of code words for a given code. It determines the error-detecting/correcting capabilities of the code. The rows of generator matrix **G** define a basis for the code vectors. For Hamming codes, the basis (rows of **G**) satisfies even parity conditions. This characterizes  $d_{min}$  (= 3) for a Hamming code.

If a code has minimum distance  $d_{min}$ , no error patterns of  $d_{min} - 1$  or fewer errors can change one code vector into another code vector. Therefore, the random error-detecting capability of a block code with minimum distance  $d_{min}$  is  $d_{min} - 1$ .

Figure 3.4. 2D representation of redundancy around each code vector and the concept of  $d_{min}$

In order to be able to detect and correct an error correctly, the received vector must lie in the space surrounding the corresponding transmitted vector (Figure 3.4). If the received vector differs from the transmitted vector in *t* places (*t* errors); it can be corrected only if

$$t \le \lfloor (d_{min} - 1)/2 \rfloor$$

(3-12)

Where  $\lfloor (d_{min}-1)/2 \rfloor$  denotes the largest integer no greater than  $(d_{min}-1)/2$ .

For a Hamming code  $d_{min}$  = 3. Hence it can detect up to 2 bit errors and can detect and correct a single bit error.

#### 3.1.5. Cyclic Hamming Codes

Cyclic Hamming codes can be represented as a polynomial. For  $\mathbf{v} = (v_0, v_{1_1}, ..., v_{n-1})$ , the code polynomial is

$$\mathbf{v}(X) = \mathbf{v}_0 X^0 + \mathbf{v}_1 X^1 + \mathbf{v}_2 X^2 + \dots + \mathbf{v}_{n-1} X^{n-1}$$

(3-13)

The power of X denotes the position of the code vector component. For example, the vector (1 0 0 1 0 1 1) is represented as  $1 + X^3 + X^5 + X^6$ .

The encoding and decoding circuits of a cyclic code consist of shift registers with feedback connections. The power of X represents the number of serial shifts of the components through the circuit. Due to the cyclic structure of the code, the circuit may be designed to decode the first received bit and decode subsequent bits using the same circuitry. Thus a cyclic code saves hardware but increases the computational delay which is not favorable for NOR Flash. On the other hand, the linear decoding process explained in Section 3.1.3 can be made parallel making the circuit faster. Therefore linear Hamming codes are preferred over cyclic Hamming codes for implementation in NOR Flash devices.

Hamming codes are very simple to understand and implement. They are well-suited when the BER has to be improved from around 10<sup>-10</sup> to 10<sup>-15</sup>. They fail to detect and correct multi bit errors and hence are inefficient as raw BER increases to 10<sup>-6</sup>.

### 3.2. Multi Bit Error Correction: BCH Codes

The Bose-Chaudhuri-Hocquenghem (BCH) codes are a generalized form of Hamming codes for multi bit error detection and correction. They include both binary and multilevel codes. Multi level BCH codes are suitable for correcting burst errors. Since the errors in a Flash device are random, it is convenient to use binary BCH codes for Flash memory.

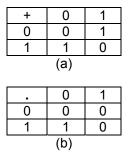

Before evaluating BCH codes, a review of *finite field arithmetic* is required in order to understand and utilize multi bit error correcting codes. Binary arithmetic is a subset of finite field arithmetic. A *finite field* is a set of finite elements over which math operations like addition, subtraction, multiplication and division generate values which belong to the same set. More formally it can be said that addition, subtraction, multiplication and division are *closed* on the field. A finite field is also known as a *Galois field* (GF). A Galois field in which the elements can take q different values is referred to as GF(q) [16]. In GF(p), where p is a prime number, modulo-p arithmetic is used. An example of modulo-2 arithmetic is shown in Figure 3.5.

Figure 3.5. (a) Modulo-2 addition (b) Modulo-2 multiplication

In any prime size field, there is always at least one element whose powers constitute all the nonzero elements of the field [16]. This element is called the *primitive*. For example, in GF(5), the number 3 is primitive because:

$$3^0 = 1$$

$3^1 = 3$

$3^2 = 4$

$3^3 = 2(all modulo-5)$

The pattern repeats for higher powers of 3.

The finite field GF(p) can be extended to a field of  $p^m$  elements where m is any positive integer. The field thus formed,  $GF(p^m)$ , is called an *extension field* of GF(p). For binary BCH codes, GF(2) and its extension field  $GF(2^m)$  are used.

A single bit error detection and correction code like a Hamming code differs from a multi bit error detection and correction code in the manner in which the data bits are utilized to generate redundant space. For a Hamming code there is only one set of linearly independent equations, hence it can detect and correct only single bit errors. On the other hand, if multiple sets of linearly independent equations are superimposed on the same data bits, a code that can correct multiple errors, each corresponding to a linearly independent set of equations is obtained.

#### 3.2.1. The Mechanics

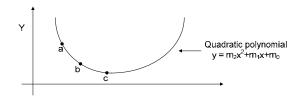

Code vectors in polynomial form can be represented graphically. For example,  $\mathbf{u} = (1\ 1\ 1) \equiv \mathbf{u}(X) = 1 + X + X^2$  is represented as shown in Figure 3.6.

Figure 3.6. Graphical representation of  $\mathbf{u} = (1\ 1\ 1)$

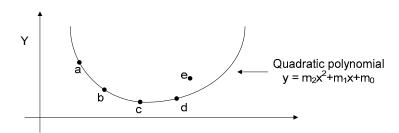

For a polynomial of degree n, n+1 distinct points describe the polynomial completely. The idea behind BCH codes is to store more than n+1 points satisfying the polynomial. This is oversampling the polynomial. While reading out data, as long as any set of n+1 correct points is read out, the information polynomial  $\mathbf{u}(X)$  can be rebuilt.

Figure 3.7. Oversampling polynomial  $\mathbf{u}(X)$

In the above example,  $\mathbf{u}(X)$  is oversampled with 5 points, a, b, c, d and e (Figure 3.7). When these points are transmitted point  $\mathbf{e}$  is disturbed. Polynomials are constructed using all permutations of n + 1 (= 3, here) points. The results are tabulated in Table 3.1.

Table 3.1. Reconstructing the oversampled polynomial u(X)

| Points  | Corresponding polynomial |

|---------|--------------------------|

| a, b, c | u(X)                     |

| a, b, d | u(X)                     |

| a, b, e | u <sub>1</sub> *(X)      |

| a, c, d | u(X)                     |

| a, c, e | u <sub>2</sub> *(X)      |

| a, d, e | u <sub>3</sub> *(X)      |

| b, c, d | u(X)                     |

| b, c, e | u <sub>4</sub> *(X)      |

| b, d, e | u <sub>5</sub> *(X)      |

| c, d, e | u <sub>6</sub> *(X)      |

|         |                          |

$\mathbf{u}(X)$  occurs more frequently than any other polynomial ( $\mathbf{u_i}^*(X)$ ) represents any polynomial other than the correct one). Hence it is assumed that  $\mathbf{u}(X)$  is the information vector that was transmitted. This illustrates how oversampling a polynomial helps to recover the actual data at the receiving end.

### 3.2.2. Encoding

The encoding process for BCH codes can be explained in the following manner: The first step is to oversample  $\mathbf{u}(X)$  which is done by multiplying it with  $\mathbf{g}(X)$ . The code polynomial can be written as  $\mathbf{v}(X) = \mathbf{u}(X).\mathbf{g}(X)$  (Equation 3-5).  $\mathbf{u}$  cannot be assumed to be oversampled since it represents user information which has to be protected. Therefore the only means of

introducing redundancy is via appropriate selection of  $\mathbf{g}$ . The example in Section 3.2.1 showed that for every error to be detected there should be at least two redundant points or samples. Therefore for t errors to be detected  $\mathbf{g}$  should introduce at least 2t redundant samples. This implies  $\mathbf{g}(X)$  should have at least 2t roots.

Consider formulating these statements mathematically, i.e. showing how the 2t roots of  $\mathbf{g}(X)$  help introduce redundancy in  $\mathbf{u}(X)$  by oversampling it.

If n denotes the length of the code word  $\mathbf{v}$  and k is the length of the information vector  $\mathbf{u}$  then n and k are related such that the number of redundant symbols is

$$n - k \le mt$$

[15]

where m is a positive integer ( $m \ge 3$ ) defined in terms of n as  $n = 2^m - 1$  and t is the maximum number of errors that can be corrected ( $t < 2^{m-1}$ ).

The generator polynomial  $\mathbf{g}(X)$  for a binary BCH code is the *lowest degree polynomial* over GF(2) which has  $(\alpha, \alpha^2, \alpha^3, ..., \alpha^{2t})$  as its roots i.e.  $\mathbf{g}(\alpha^i) = 0$  for  $1 \le i \le 2t$  [15]; where  $\alpha$  is a primitive element in GF(2<sup>m</sup>). *Lowest degree polynomial* implies  $\mathbf{g}(X)$  has only  $(\alpha, \alpha^2, \alpha^3, ..., \alpha^{2t})$  as its roots and no roots other than these. Using a binary Galois field is a typical scenario since information is generally represented as a combination of 1's and 0's. An extended binary field GF(2<sup>m</sup>) uses binary symbols of length m.

The 2t roots of  $\mathbf{g}(X)$  indicate that for t bit errors to be detected and corrected at least 2t redundant samples are introduced.  $\mathbf{g}(X)$  can be represented in the factored form. The generic way of doing this is

$$\mathbf{q}(X) = (X + \alpha).(X + \alpha^2).(X + \alpha^3)...(X + \alpha^{2t})$$

(3-14)

However, according to the definition of  $\mathbf{g}(X)$ , its coefficients lie in GF(2). Therefore, equation (3-14) is not the correct definition of  $\mathbf{g}(X)$  in terms of its roots. Instead  $\mathbf{g}(X)$  can be defined in terms of *minimal polynomials* of each of  $(\alpha, \alpha^2, \alpha^3, ..., \alpha^{2t})$ . To include all roots that may have coefficients over GF( $2^m$ ), the following procedure is used:

The minimal polynomial  $\Phi(X)$  of any element  $\beta$  in  $GF(2^m)$  is defined as the polynomial of smallest degree over GF(2) having  $\beta$  as its root, i.e.  $\Phi(\beta) = 0$ . For example, the minimal polynomial of 0 in  $GF(2^m)$  is X and that of 1 is X + 1.

Suppose the minimal polynomial of  $\alpha^i$  for  $1 \le i \le 2t$  is denoted by  $\Phi_i(X)$ . Therefore, the factored form of  $\mathbf{g}(X)$  can be written as

$$\mathbf{g}(X) = LCM\{\Phi_1(X), \Phi_2(X), \dots, \Phi_{2t}(X)\}$$

(3-15)

#### LCM: Least Common Multiple

Equation (3-15) is simplified using the concept of conjugates in a finite field, explained below:

If  $\beta$  is an element in GF(2<sup>m</sup>), then the element  $(\beta)^{p^2}$ , which also belongs to GF(2<sup>m</sup>) satisfies  $[f(\beta)]^{p^2} = f(\beta^{p^2})$ .  $\beta$  and  $(\beta)^{p^2}$  are called conjugates. Conjugates are transparent to the order of equations.

### f(X): polynomial with binary coefficients.

Every even power of  $\alpha$  in GF(2<sup>m</sup>) can be written in terms of an odd power and a power of 2. For example,  $\alpha^{12} = (\alpha^3)^4 = (\alpha^3)^{2^2}$ . Therefore every even power of  $\alpha$  is a conjugate of some preceding odd power of  $\alpha$ . In the above example,  $\alpha^{12}$  is a conjugate of  $\alpha^3$ .

Appendix A shows that a root and its conjugate have the same minimal polynomial. Therefore all roots contained in the even polynomials are contained in the odd polynomials as well. Therefore the even polynomials do not contribute to  $\mathbf{g}(X)$  and can be eliminated. The expression for  $\mathbf{g}(X)$  is reduced to

$$\mathbf{g}(X) = LCM\{ \Phi_1(X), \Phi_3(X), \dots, \Phi_{2t-1}(X) \}$$

(3-16)

This is the generator polynomial for a binary *t*-error-correcting BCH code of length  $2^m - 1$ .

For a single-error-correcting BCH code of length  $2^m - 1$ , the generator matrix is

$$\mathbf{g}(\mathbf{X}) = \Phi_1(\mathbf{X}) \tag{3-17}$$

Since  $\alpha$  is a primitive element of  $GF(2^m)$ ,  $\Phi_1(X)$  is a primitive polynomial of degree m. Therefore, the single-error-correcting BCH code of length  $2^m - 1$  is a Hamming code. [15]

Thus while a single-error-correcting Hamming code is defined by a single primitive polynomial, a *t*-error-correcting BCH code is defined by *t* primitive polynomials as explained in Equation (3-16).

Here is an illustrative example:

For a (15, 5) (= (n, k)) triple-error correcting code. The assumption t = 3 makes the example simpler to understand.

$$n = 15 = 2^m - 1 => m = 4$$

.

Let  $\alpha$  be a primitive element in GF(2<sup>4</sup>). According to the definition;  $\alpha$ ,  $\alpha^2$ ,  $\alpha^3$ ,  $\alpha^4$ ,  $\alpha^5$  and  $\alpha^6$  are the roots of  $\mathbf{g}(X)$  for the this code. The minimal polynomials for  $\alpha$ ,  $\alpha^2$  and  $\alpha^4$  are identical (Appendix A) and

$$\Phi_1(X) = \Phi_2(X) = \Phi_4(X) = 1 + X + X^4$$

(3-18)

The minimal polynomials for  $\alpha^3$  and  $\alpha^6$  are the same,

$$\Phi_3(X) = \Phi_6(X) = 1 + X + X^2 + X^3 + X^4$$

(3-19)

The minimal polynomial for  $\alpha^5$  is,

$$\Phi_5(X) = 1 + X + X^2 \tag{3-20}$$

Taking the LCM, the generator polynomial for the (15, 5) triple-error correcting BCH code is,

$$\mathbf{q}(X) = 1 + X + X^2 + X^4 + X^5 + X^8 + X^{10}$$

The parity-check matrix for BCH codes can be derived from the roots of  $\mathbf{g}(X)$ . Since the code polynomial,  $\mathbf{v}(X) = \mathbf{u}(X) \cdot \mathbf{g}(X)$ ,  $\mathbf{v}(X)$  has  $\alpha$ ,  $\alpha^2$ ,  $\alpha^3$ , ...,  $\alpha^{2t}$  as its roots. Hence, for  $1 \le i \le 2t$ ,

$$\mathbf{v}(\alpha^{i}) = v_0 + v_1 \alpha^{i} + v_2 \alpha^{2i} + \dots + v_{n-1} \alpha^{(n-1)i} = 0$$

(3-21)

This equation can be written as a product of two matrices where each element of the resulting vector equals Equation (3-21) for the corresponding i;  $1 \le i \le 2t$ .

$$(v_0, v_1, ..., v_{n-1}). \begin{bmatrix} 1 & 1 & 1 & .... & 1 \\ \alpha & \alpha^2 & \alpha^3 & .... & \alpha^{2t} \\ \alpha^2 & \alpha^4 & \alpha^6 & .... & \alpha^{4t} \\ \alpha^3 & \alpha^6 & \alpha^9 & & \alpha^{6t} \\ ... & ... & ... & ... \\ \alpha^{n-1} & \alpha^{2(n-1)} & \alpha^{3(n-1)} & .... & \alpha^{2t(n-1)} \end{bmatrix} = 0 = \mathbf{v.M}$$

(3-22)

Comparing this with  $\mathbf{v.H}^{\mathsf{T}} = 0$  (Equation 3-8) the parity-check matrix,  $\mathbf{H} = \mathbf{M}^{\mathsf{T}}$ , for the BCH code:

$$\mathbf{H} = \begin{bmatrix} 1 & \alpha & \alpha^{2} & \alpha^{3} & \dots & \alpha^{n-1} \\ 1 & \alpha^{2} & \alpha^{4} & \alpha^{6} & \dots & \alpha^{2(n-1)} \\ 1 & \alpha^{3} & \alpha^{6} & \alpha^{9} & \dots & \alpha^{3(n-1)} \\ \vdots & \vdots & & & \vdots \\ \vdots & \ddots & & & \ddots \\ 1 & \alpha^{2t} & \alpha^{4t} & \alpha^{6t} & \dots & \alpha^{2t(n-1)} \end{bmatrix}$$

(3-23)

### 3.2.3. Decoding

Decoding BCH codes involves detecting and correcting a larger number of errors as compared with single bit error detection and correction in Hamming codes.

There are two popular approaches, namely, the Standard Algebraic Decoding Method and Massey's Step-by-Step Decoding Algorithm [20]. There are several modifications made to the Step-by-Step algorithm [21- 23]. The basic Step-by-Step algorithm [20] has been analyzed here.

### 3.2.3.1. Standard Algebraic Decoding Method

This method closely emulates the mechanics described earlier (Section 3.2.1). The decoding process has two steps: Error detection and Error Correction.

To detect errors all probable  $n^{th}$  degree information polynomials ( $\mathbf{u}(X)$ ) are constructed using all possible permutations of n+1 points. If the polynomials are not all equal, it implies at least one of the points is disturbed. Errors are corrected by identifying the most frequently occurring polynomial, from amongst those constructed in the previous step, and assuming it to

be the stored information **u**. The point(s) common to the remaining (less frequently occurring, hence assumed to be erroneous) polynomials is/are said to be the disturbed sample(s).

This process can be mathematically formulated in the following manner:

Suppose the code vector stored at a memory location is  $\mathbf{v}(X)$ . If  $\mathbf{r}(X)$  is the vector that is read out and  $\mathbf{e}(X)$  is the error pattern then

$$r(X) = v(X) + e(X)$$

The syndrome **S** is constructed in order to determine the presence or absence of errors. If **S** is non-zero it indicates the presence of errors and vice versa. For a t-error-correcting BCH code, **S** is a 2t-tuple since **H** is a  $2t \times n$  matrix.

$$\mathbf{S} = (S_1, S_2, ..., S_{2t}) = \mathbf{r}.\mathbf{H}^{\mathsf{T}} = \mathbf{e}.\mathbf{H}^{\mathsf{T}}$$

(3-24)

where  $S_i = \mathbf{r}(\alpha^i) = \mathbf{e}(\alpha^i)$  for  $1 \le i \le 2t$ .

Error Correction involves finding the exact locations of disturbed samples and correcting the samples by complementing them. The error-location algorithm for BCH codes is designed to detect locations of multiple-errors. Equation (3-24) shows that  $\bf S$  depends only on the error pattern  $\bf e$ . Suppose  $\bf e(X)$  has  $\bf v$  errors at locations  $\bf X^{j1}, \, \bf X^{j2}, \, ..., \, \bf X^{jv}$ .

$$\mathbf{e}(X) = X^{j1} + X^{j2} + ... + X^{jv}$$

(3-25)

where  $0 \le j_1 < j_2 < ... < j_v \le n$ .

Combining Equations (3-24) and (3-25);

$$S_{1} = \alpha^{j1} + \alpha^{j2} + ... + \alpha^{jv}$$

$$S_{2} = (\alpha^{j1})^{2} + (\alpha^{j2})^{2} + ... + (\alpha^{jv})^{2}$$

$$S_{3} = (\alpha^{j1})^{3} + (\alpha^{j2})^{3} + ... + (\alpha^{jv})^{3}$$

$$.$$

$$.$$

$$S_{2t} = (\alpha^{j1})^{2t} + (\alpha^{j2})^{2t} + ... + (\alpha^{jv})^{2t}$$

where  $\alpha^{j1}$ ,  $\alpha^{j2}$ , ...,  $\alpha^{jv}$  are unknown. Any method for solving these equations is a decoding algorithm for the BCH codes. [15]

Let  $\beta_p = \alpha^{jp}$  for  $1 \le p \le v$ . These are the *error location numbers*. Equation (3-26) is rewritten as

$$S_{1} = \beta_{1} + \beta_{2} + ... + \beta_{v}$$

$$S_{2} = \beta_{1}^{2} + \beta_{2}^{2} + ... + \beta_{v}^{2}$$

$$S_{3} = \beta_{1}^{3} + \beta_{2}^{3} + ... + \beta_{v}^{3}$$

$$\vdots$$

$$S_{2t} = \beta_{1}^{2t} + \beta_{2}^{2t} + ... + \beta_{v}^{2t}$$

(3-27)

The error locator polynomial is defined [15] as:

$$\sigma(X) = (1 + \beta_1 X)(1 + \beta_2 X) \dots (1 + \beta_v X)$$

$$= \sigma_0 + \sigma_1 X + \sigma_2 X^2 + \dots + \sigma_v X^v$$

(3-28)

The roots of this polynomial specify the locations of the errors.  $S_1$ ,  $S_2$ , ...,  $S_{2t}$  can be written in terms of the roots of  $\sigma(X)$ .

For the (15, 5) BCH code example (Section 3.2.2) suppose the received systematic code polynomial is,

$$\mathbf{r}(X) = X^3 + X^5 + X^{12}$$

The syndrome components are remainders when  ${\bf r}(X)$  is divided by  $\Phi_1(X)$ ,  $\Phi_3(X)$ ,  $\Phi_5(X)$  (Equation 3-18, 3-19 and 3-20) successively,

$$\mathbf{b}_{1}(X) = 1,$$

(3-29)

$\mathbf{b}_{3}(X) = 1 + X^{2} + X^{3}$

$\mathbf{b}_{5}(X) = X^{2}$

Using the power and polynomial representations of the elements in GF(2<sup>4</sup>) and substituting  $\alpha$ ,  $\alpha^2$  and  $\alpha^4$  into  $\mathbf{b}_1(X)$ ,

$$S_1 = S_2 = S_4 = 1$$

Substituting  $\alpha^3$  and  $\alpha^6$  into **b**<sub>3</sub>(X),

$$S_3 = 1 + \alpha^6 + \alpha^9 = \alpha^{10}$$

$$S_6 = 1 + \alpha^{12} + \alpha^{18} = \alpha^5$$

Substituting  $\alpha^5$  into **b**<sub>5</sub>(X),

$$S_5 = \alpha^{10}$$

The error locator polynomial is determined by an iterative procedure known as Berlekamp's iterative algorithm. The roots of this polynomial or the error location numbers are found using Peterson's substitution method [18] or Chien's search algorithm [19], the latter preferred because of available optimizations of its hardware implementation. The simplest way to implement Chien's search algorithm is using a look-up table. This is impractical for large block sizes. Another hardware circuit used is called the Chien searcher [21]. The complexity of the circuit increases in proportion to the block length. Hence it too is inefficient for long block codes.

Summarizing standard algebraic decoding method, the first step is to compute the syndrome,  $\mathbf{S} = \mathbf{r}$ .  $\mathbf{H}^T$  in order to detect errors. If  $\mathbf{S}$  is nonzero, which implies there are errors in the received word, then the error location polynomial is determined from the components of  $\mathbf{S}$ . The roots of this polynomial give the error-location numbers. Once the error locations have been identified, correcting these errors is to complement the bit at that position.

The Step-by-Step decoding algorithm (Section 3.2.3.2) proposed by Massey is an efficient alternative to the standard algebraic method.

#### 3.2.3.2. Massey's Step-by-Step Decoding Algorithm

The step-by-step decoding algorithm corrects erroneous bits by checking the impact of changing (complementing) each bit on the total number of errors in the code word. If changing a

bit reduces the number of errors, then the change is retained else the bit is changed back to its original value. This algorithm has been explained by Massey in [27].

It is easier to implement this algorithm since it avoids calculating the coefficients of an error locator polynomial and searching the roots [21]. It exploits the cyclic nature of BCH codes.

## The decoding algorithm is explained below:

Errors are detected by computing the syndrome **S** (Equation 3-10). A nonzero value of the syndrome indicates the presence of errors.

For correcting the errors: The weight of the error pattern  $\mathbf{e}$  indicates the number of errors in  $\mathbf{r}$ . Each bit of  $\mathbf{r}$  is successively complemented (one bit at a time) and the weight of the resulting error pattern is observed. If the weight reduces it implies the bit under consideration was erroneous and has been corrected by complementing it. On the other hand, if the weight increases, it is assumed that the bit is not disturbed and its value should remain unchanged. Since this method involves changing the received symbols one at a time and testing the resultant weight of error pattern, it is called the *step-by-step algorithm*.

To formulate this algorithm mathematically, consider the received vector is  $\mathbf{r}(X)$  which is equal to  $\mathbf{v}(X) + \mathbf{e}(X)$  where  $\mathbf{v}$  is the transmitted (stored) code word and  $\mathbf{e}$  is the error pattern. For a t-error correcting BCH code (Equation 3-24)

$$S = (S_1, S_2, ..., S_{2t}) = r.H^T = e.H^T$$

where  $S_i = \mathbf{r}(\alpha^i) = \mathbf{e}(\alpha^i)$  for  $1 \le i \le 2t$ .

# A non zero value of **S** indicates the presence of errors in **r**.

The total number of non zero elements in **e**, i.e. the Hamming weight of **e**, gives the total number of errors in the received code word. This helps the decoder determine when it should stop complementing the code word bit-by-bit.

Massey defines a procedure [20] to determine the weight of  $\mathbf{e}$ . The total number of errors can be estimated by determining the singularity or non singularity of matrix,  $\mathbf{L}_{j\cdot}$  (Equation 3-30)

The matrix  $\mathbf{L}_{j}$  [20] is defined for any binary BCH code having code length n and any j such that 1  $\leq j \leq n$ -1,  $\mathbf{L}_{j}$  is the  $j \times j$  matrix

$$\mathbf{L}_{j} = \begin{bmatrix} S_{1} & 1 & 0 & 0 & \dots & 0 \\ S_{3} & S_{2} & S_{1} & 1 & \dots & 0 \\ & & \ddots & & & & \\ & & & \ddots & & & \\ S_{2j-1} & S_{2j-2} & S_{2j-3} & S_{2j-4} & \dots & S_{j} \end{bmatrix}$$

(3-30)

$\mathbf{L}_i$  is singular if the weight of  $\mathbf{e}$  is j-1 or less, and is non-singular if the weight of  $\mathbf{e}$  is j or j+1 [20].

Using this property the number of errors can be defined in terms of  $\det(\mathbf{L}_1)$ ,  $\det(\mathbf{L}_2)$ , ...,  $\det(\mathbf{L}_t)$ . For example,  $\det(\mathbf{L}_4) = 0$  implies that the number of errors is three or less. The exact number of errors can be determined in terms of the relations among  $\det(\mathbf{L}_1)$ ,  $\det(\mathbf{L}_2)$ , ...,  $\det(\mathbf{L}_t)$ . For example, if  $\det(\mathbf{L}_1) \neq 0$ ,  $\det(\mathbf{L}_2) \neq 0$ , and  $\det(\mathbf{L}_p) = 0$  for p = 3, 4, ..., t, then two errors have occurred [20]. The only thing that is of consequence here is whether  $\det(\mathbf{L}_p)$  (1  $\leq p \leq t$ ) is equal to zero or not.

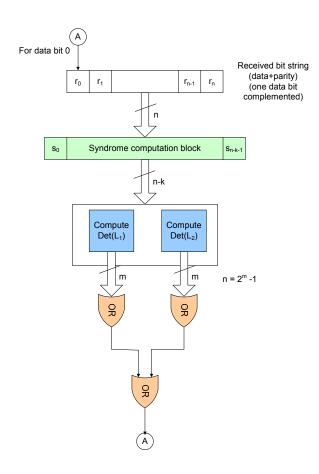

The process of complementing bits and checking the weight of the resulting error pattern against the weight of the actual error pattern can be done by decoders in parallel. This reduces the computational time at a nominal hardware overhead. This makes this algorithm one of the prime choices for use in low latency NOR Flash.

Thus, broadly, there are two error correction codes to choose from – Hamming and BCH. Selecting an appropriate one depends on the current BER of the array and the required BER ( $\sim 10^{-15}$  for NOR). The error correction capacity of the algorithm is a function of these parameters.

# 3.3. Computing Required Error Correction Capacity

The current BER of a memory array can be computed from the voltage distribution curves (Section 2.4).

The current BER for a given memory array is denoted by  $\mathbf{P_e}$  which denotes the probability of one exclusive bit to be in error in the array. Using this, the probability that a single bit is in error in a k-bit block is given by

$$1 - (1-P_e)^k$$

= current BER of the *k*-bit block (3-31)

After using ECC, the size of the encoded block (parity + data) = n (say) and the maximum no. of errors that can be corrected = t

Therefore the probability of an error in a *n*-bit block after applying ECC is given by

# $P(error in a n-bit block after ECC) = P_{ECC}$